# E·XFL

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Active                                                       |

| Number of LABs/CLBs            | 6912                                                         |

| Number of Logic Elements/Cells | 62208                                                        |

| Total RAM Bits                 | 1769472                                                      |

| Number of I/O                  | 633                                                          |

| Number of Gates                | 400000                                                       |

| Voltage - Supply               | 1.14V ~ 1.26V                                                |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                              |

| Package / Case                 | 900-BBGA                                                     |

| Supplier Device Package        | 900-FBGA (31x31)                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc3s4000-4fg900c |

|                                |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Architectural Overview

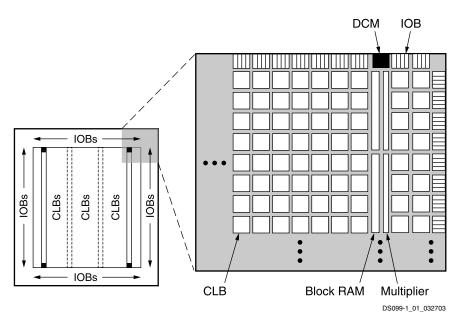

The Spartan-3 family architecture consists of five fundamental programmable functional elements:

- Configurable Logic Blocks (CLBs) contain RAM-based Look-Up Tables (LUTs) to implement logic and storage elements that can be used as flip-flops or latches. CLBs can be programmed to perform a wide variety of logical functions as well as to store data.

- Input/Output Blocks (IOBs) control the flow of data between the I/O pins and the internal logic of the device. Each IOB supports bidirectional data flow plus 3-state operation. Twenty-six different signal standards, including eight high-performance differential standards, are available as shown in Table 2. Double Data-Rate (DDR) registers are included. The Digitally Controlled Impedance (DCI) feature provides automatic on-chip terminations, simplifying board designs.

- Block RAM provides data storage in the form of 18-Kbit dual-port blocks.

- Multiplier blocks accept two 18-bit binary numbers as inputs and calculate the product.

- Digital Clock Manager (DCM) blocks provide self-calibrating, fully digital solutions for distributing, delaying, multiplying, dividing, and phase shifting clock signals.

These elements are organized as shown in Figure 1. A ring of IOBs surrounds a regular array of CLBs. The XC3S50 has a single column of block RAM embedded in the array. Those devices ranging from the XC3S200 to the XC3S2000 have two columns of block RAM. The XC3S4000 and XC3S5000 devices have four RAM columns. Each column is made up of several 18-Kbit RAM blocks; each block is associated with a dedicated multiplier. The DCMs are positioned at the ends of the outer block RAM columns.

The Spartan-3 family features a rich network of traces and switches that interconnect all five functional elements, transmitting signals among them. Each functional element has an associated switch matrix that permits multiple connections to the routing.

# Notes:

1. The two additional block RAM columns of the XC3S4000 and XC3S5000 devices are shown with dashed lines. The XC3S50 has only the block RAM column on the far left.

Figure 1: Spartan-3 Family Architecture

# Configuration

Spartan-3 FPGAs are programmed by loading configuration data into robust reprogrammable static CMOS configuration latches (CCLs) that collectively control all functional elements and routing resources. Before powering on the FPGA, configuration data is stored externally in a PROM or some other nonvolatile medium either on or off the board. After applying

# ESD Protection

Clamp diodes protect all device pads against damage from Electro-Static Discharge (ESD) as well as excessive voltage transients. Each I/O has two clamp diodes: One diode extends P-to-N from the pad to  $V_{CCO}$  and a second diode extends N-to-P from the pad to GND. During operation, these diodes are normally biased in the off state. These clamp diodes are always connected to the pad, regardless of the signal standard selected. The presence of diodes limits the ability of Spartan-3 FPGA I/Os to tolerate high signal voltages. The V<sub>IN</sub> absolute maximum rating in Table 28, page 58 specifies the voltage range that I/Os can tolerate.

# Slew Rate Control and Drive Strength

Two options, FAST and SLOW, control the output slew rate. The FAST option supports output switching at a high rate. The SLOW option reduces bus transients. These options are only available when using one of the LVCMOS or LVTTL standards, which also provide up to seven different levels of current drive strength: 2, 4, 6, 8, 12, 16, and 24 mA. Choosing the appropriate drive strength level is yet another means to minimize bus transients.

Table 7 shows the drive strengths that the LVCMOS and LVTTL standards support.

| Signal Standard | Current Drive (mA) |   |   |   |    |    |    |  |

|-----------------|--------------------|---|---|---|----|----|----|--|

| (IOSTANDARD)    | 2                  | 4 | 6 | 8 | 12 | 16 | 24 |  |

| LVTTL           | 1                  | 1 | 1 | 1 | 1  | 1  | 1  |  |

| LVCMOS33        | 1                  | 1 | 1 | 1 | 1  | 1  | ~  |  |

| LVCMOS25        | 1                  | 1 | 1 | 1 | 1  | 1  | 1  |  |

| LVCMOS18        | 1                  | 1 | 1 | 1 | 1  | 1  | -  |  |

| LVCMOS15        | 1                  | 1 | 1 | 1 | 1  | _  | -  |  |

| LVCMOS12        | 1                  | 1 | 1 | - | -  | -  | -  |  |

Table 7: Programmable Output Drive Current

# **Boundary-Scan Capability**

All Spartan-3 FPGA IOBs support boundary-scan testing compatible with IEEE 1149.1 standards. During boundary- scan operations such as EXTEST and HIGHZ the I/O pull-down resistor is active. For more information, see Boundary-Scan (JTAG) Mode, page 50, and refer to the "Using Boundary-Scan and BSDL Files" chapter in <u>UG331</u>.

# SelectIO Interface Signal Standards

The IOBs support 18 different single-ended signal standards, as listed in Table 8. Furthermore, the majority of IOBs can be used in specific pairs supporting any of eight differential signal standards, as shown in Table 9.

To define the SelectIO<sup>™</sup> interface signaling standard in a design, set the IOSTANDARD attribute to the appropriate setting. Xilinx provides a variety of different methods for applying the IOSTANDARD for maximum flexibility. For a full description of different methods of applying attributes to control IOSTANDARD, refer to the "Using I/O Resources" chapter in <u>UG331</u>.

Together with placing the appropriate I/O symbol, two externally applied voltage levels,  $V_{CCO}$  and  $V_{REF}$ , select the desired signal standard. The  $V_{CCO}$  lines provide current to the output driver. The voltage on these lines determines the output voltage swing for all standards except GTL and GTLP.

All single-ended standards except the LVCMOS, LVTTL, and PCI varieties require a Reference Voltage ( $V_{REF}$ ) to bias the input-switching threshold. Once a configuration data file is loaded into the FPGA that calls for the I/Os of a given bank to use such a signal standard, a few specifically reserved I/O pins on the same bank automatically convert to  $V_{REF}$  inputs. When using one of the LVCMOS standards, these pins remain I/Os because the  $V_{CCO}$  voltage biases the input-switching threshold, so there is no need for  $V_{REF}$ . Select the  $V_{CCO}$  and  $V_{REF}$  levels to suit the desired single-ended standard according to Table 8.

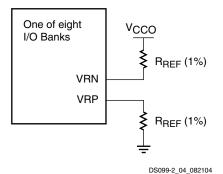

The DCI feature operates independently for each of the device's eight banks. Each bank has an 'N' reference pin (VRN) and a 'P' reference pin, (VRP), to calibrate driver and termination resistance. Only when using a DCI standard on a given bank do these two pins function as VRN and VRP. When not using a DCI standard, the two pins function as user I/Os. As shown in Figure 9, add an external reference resistor to pull the VRN pin up to V<sub>CCO</sub> and another reference resistor to pull the VRP pin down to GND. Also see Figure 42, page 116. Both resistors have the same value—commonly  $50\Omega$ —with one-percent tolerance, which is either the characteristic impedance of the line or twice that, depending on the DCI standard in use. Standards having a symbol name that contains the letters "DV2" use a reference resistor value that is twice the line impedance. DCI adjusts the output driver impedance to match the reference resistors' value or half that, according to the standard. DCI always adjusts the on-chip termination resistors to directly match the reference resistors' value.

Figure 9: Connection of Reference Resistors (R<sub>BFF</sub>)

The rules guiding the use of DCI standards on banks are as follows:

- No more than one DCI I/O standard with a Single Termination is allowed per bank.

- No more than one DCI I/O standard with a Split Termination is allowed per bank.

- Single Termination, Split Termination, Controlled- Impedance Driver, and Controlled-Impedance Driver with Half Impedance can co-exist in the same bank.

See also The Organization of IOBs into Banks, immediately below, and DCI: User I/O or Digitally Controlled Impedance Resistor Reference Input, page 115.

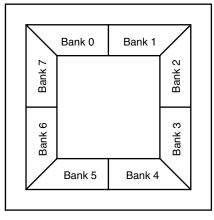

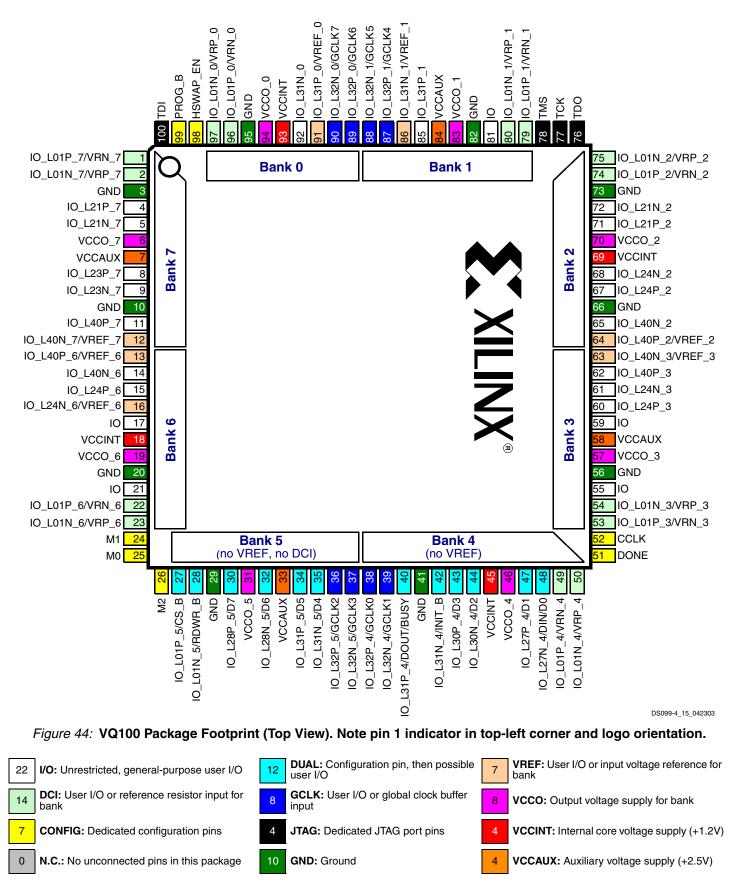

### The Organization of IOBs into Banks

IOBs are allocated among eight banks, so that each side of the device has two banks, as shown in Figure 10. For all packages, each bank has independent  $V_{REF}$  lines. For example,  $V_{REF}$  Bank 3 lines are separate from the  $V_{REF}$  lines going to all other banks.

For the Very Thin Quad Flat Pack (VQ), Plastic Quad Flat Pack (PQ), Fine Pitch Thin Ball Grid Array (FT), and Fine Pitch Ball Grid Array (FG) packages, each bank has dedicated  $V_{CCO}$  lines. For example, the  $V_{CCO}$  Bank 7 lines are separate from the  $V_{CCO}$  lines going to all other banks. Thus, Spartan-3 devices in these packages support eight independent  $V_{CCO}$  supplies.

DS099-2\_03\_082104

Figure 10: Spartan-3 FPGA I/O Banks (Top View)

#### Notes:

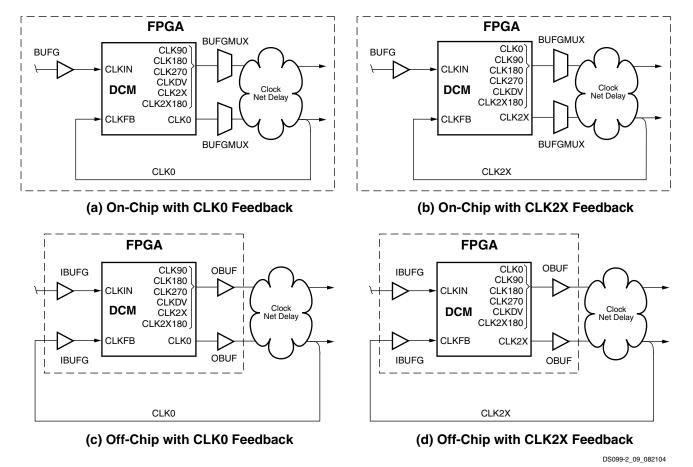

1. In the Low Frequency mode, all seven DLL outputs are available. In the High Frequency mode, only the CLK0, CLK180, and CLKDV outputs are available.

#### Figure 21: Input Clock, Output Clock, and Feedback Connections for the DLL

In the on-chip synchronization case (the [a] and [b] sections of Figure 21), it is possible to connect any of the DLL's seven output clock signals through general routing resources to the FPGA's internal registers. Either a Global Clock Buffer (BUFG) or a BUFGMUX affords access to the global clock network. As shown in the [a] section of Figure 21, the feedback loop is created by routing CLK0 (or CLK2X, in the [b] section) to a global clock net, which in turn drives the CLKFB input.

In the off-chip synchronization case (the [c] and [d] sections of Figure 21), CLK0 (or CLK2X) plus any of the DLL's other output clock signals exit the FPGA using output buffers (OBUF) to drive an external clock network plus registers on the board. As shown in the [c] section of Figure 21, the feedback loop is formed by feeding CLK0 (or CLK2X, in the [d] section) back into the FPGA using an IBUFG, which directly accesses the global clock network, or an IBUF. Then, the global clock net is connected directly to the CLKFB input.

### **DLL Frequency Modes**

The DLL supports two distinct operating modes, High Frequency and Low Frequency, with each specified over a different clock frequency range. The DLL\_FREQUENCY\_MODE attribute chooses between the two modes. When the attribute is set to LOW, the Low Frequency mode permits all seven DLL clock outputs to operate over a low-to-moderate frequency range. When the attribute is set to HIGH, the High Frequency mode allows the CLK0, CLK180 and CLKDV outputs to operate at the highest possible frequencies. The remaining DLL clock outputs are not available for use in High Frequency mode.

### **Accommodating High Input Frequencies**

If the frequency of the CLKIN signal is high such that it exceeds the maximum permitted, divide it down to an acceptable value using the CLKIN\_DIVIDE\_BY\_2 attribute. When this attribute is set to TRUE, the CLKIN frequency is divided by a factor of two just as it enters the DCM.

The output frequency (f<sub>CLKEX</sub>) can be expressed as a function of the incoming clock frequency (f<sub>CLKIN</sub>) as follows:

Regarding the two attributes, it is possible to assign any combination of integer values, provided that two conditions are met:

- The two values fall within their corresponding ranges, as specified in Table 18.

- The f<sub>CLKFX</sub> frequency calculated from the above expression accords with the DCM's operating frequency specifications.

For example, if  $CLKFX_MULTIPLY = 5$  and  $CLKFX_DIVIDE = 3$ , then the frequency of the output clock signal would be 5/3 that of the input clock signal.

### **DFS Frequency Modes**

The DFS supports two operating modes, High Frequency and Low Frequency, with each specified over a different clock frequency range. The DFS\_FREQUENCY\_MODE attribute chooses between the two modes. When the attribute is set to LOW, the Low Frequency mode permits the two DFS outputs to operate over a low-to-moderate frequency range. When the attribute is set to HIGH, the High Frequency mode allows both these outputs to operate at the highest possible frequencies.

### DFS With or Without the DLL

The DFS component can be used with or without the DLL component:

Without the DLL, the DFS component multiplies or divides the CLKIN signal frequency according to the respective CLKFX\_MULTIPLY and CLKFX\_DIVIDE values, generating a clock with the new target frequency on the CLKFX and CLKFX180 outputs. Though classified as belonging to the DLL component, the CLKIN input is shared with the DFS component. This case does not employ feedback loop; therefore, it cannot correct for clock distribution delay.

With the DLL, the DFS operates as described in the preceding case, only with the additional benefit of eliminating the clock distribution delay. In this case, a feedback loop from the CLK0 output to the CLKFB input must be present.

The DLL and DFS components work together to achieve this phase correction as follows: Given values for the CLKFX\_MULTIPLY and CLKFX\_DIVIDE attributes, the DLL selects the delay element for which the output clock edge coincides with the input clock edge whenever mathematically possible. For example, when CLKFX\_MULTIPLY = 5 and CLKFX\_DIVIDE = 3, the input and output clock edges will coincide every three input periods, which is equivalent in time to five output periods.

Smaller CLKFX\_MULTIPLY and CLKFX\_DIVIDE values achieve faster lock times. With no factors common to the two attributes, alignment will occur once with every number of cycles equal to the CLKFX\_DIVIDE value. Therefore, it is recommended that the user reduce these values by factoring wherever possible. For example, given CLKFX\_MULTIPLY = 9 and CLKFX\_DIVIDE = 6, removing a factor of three yields CLKFX\_MULTIPLY = 3 and CLKFX\_DIVIDE = 2. While both value-pairs will result in the multiplication of clock frequency by 3/2, the latter value-pair will enable the DLL to lock more quickly.

#### Table 18: DFS Attributes

| Attribute Description |                                                        | Values               |

|-----------------------|--------------------------------------------------------|----------------------|

| DFS_FREQUENCY_MODE    | Chooses between High Frequency and Low Frequency modes | Low, High            |

| CLKFX_MULTIPLY        | Frequency multiplier constant                          | Integer from 2 to 32 |

| CLKFX_DIVIDE          | Frequency divisor constant                             | Integer from 1 to 32 |

#### Table 19: DFS Signals

| Signal   | Signal Direction Description |                                                                                                                                                   |  |

|----------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CLKFX    | Output                       | Multiplies the CLKIN frequency by the attribute-value ratio (CLKFX_MULTIPLY/CLKFX_DIVIDE) to generate a clock signal with a new target frequency. |  |

| CLKFX180 | Output                       | Generates a clock signal with same frequency as CLKFX, only shifted 180° out-of-phase.                                                            |  |

# Notice of Disclaimer

THE XILINX HARDWARE FPGA AND CPLD DEVICES REFERRED TO HEREIN ("PRODUCTS") ARE SUBJECT TO THE TERMS AND CONDITIONS OF THE XILINX LIMITED WARRANTY WHICH CAN BE VIEWED AT <a href="http://www.xilinx.com/warranty.htm">http://www.xilinx.com/warranty.htm</a>. THIS LIMITED WARRANTY DOES NOT EXTEND TO ANY USE OF PRODUCTS IN AN APPLICATION OR ENVIRONMENT THAT IS NOT WITHIN THE SPECIFICATIONS STATED IN THE XILINX DATA SHEET. ALL SPECIFICATIONS ARE SUBJECT TO CHANGE WITHOUT NOTICE. PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS LIFE-SUPPORT OR SAFETY DEVICES OR SYSTEMS, OR ANY OTHER APPLICATION THAT INVOKES THE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). USE OF PRODUCTS IN CRITICAL APPLICATIONS IS AT THE SOLE RISK OF CUSTOMER, SUBJECT TO APPLICABLE LAWS AND REGULATIONS.

#### **CRITICAL APPLICATIONS DISCLAIMER**

XILINX PRODUCTS (INCLUDING HARDWARE, SOFTWARE AND/OR IP CORES) ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS IN LIFE-SUPPORT OR SAFETY DEVICES OR SYSTEMS, CLASS III MEDICAL DEVICES, NUCLEAR FACILITIES, APPLICATIONS RELATED TO THE DEPLOYMENT OF AIRBAGS, OR ANY OTHER APPLICATIONS THAT COULD LEAD TO DEATH, PERSONAL INJURY OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (INDIVIDUALLY AND COLLECTIVELY, "CRITICAL APPLICATIONS"). FURTHERMORE, XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED FOR USE IN ANY APPLICATIONS THAT AFFECT CONTROL OF A VEHICLE OR AIRCRAFT, UNLESS THERE IS A FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF SOFTWARE IN THE XILINX DEVICE TO IMPLEMENT THE REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE OPERATOR. CUSTOMER AGREES, PRIOR TO USING OR DISTRIBUTING ANY SYSTEMS THAT INCORPORATE XILINX PRODUCTS, TO THOROUGHLY TEST THE SAME FOR SAFETY PURPOSES. TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY USE OF XILINX PRODUCTS IN CRITICAL APPLICATIONS.

#### AUTOMOTIVE APPLICATIONS DISCLAIMER

XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS APPLICATIONS RELATED TO: (I) THE DEPLOYMENT OF AIRBAGS, (II) CONTROL OF A VEHICLE, UNLESS THERE IS A FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF SOFTWARE IN THE XILINX DEVICE TO IMPLEMENT THE REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE OPERATOR, OR (III) USES THAT COULD LEAD TO DEATH OR PERSONAL INJURY. CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY USE OF XILINX PRODUCTS IN SUCH APPLICATIONS.

### Table 43: Propagation Times for the IOB Input Path

|                          | Description                                                          |                                             |          | Speed Grade |      |       |

|--------------------------|----------------------------------------------------------------------|---------------------------------------------|----------|-------------|------|-------|

| Symbol                   |                                                                      | Conditions                                  | Device   | -5          | -4   | Units |

|                          |                                                                      |                                             |          | Max         | Max  |       |

| Propagation <sup>-</sup> | Times                                                                |                                             |          |             |      |       |

| T <sub>IOPLI</sub>       | The time it takes for data to travel                                 | LVCMOS25 <sup>(2)</sup> ,                   | XC3S50   | 2.01        | 2.31 | ns    |

|                          | from the Input pin through the<br>IFF latch to the I output with no  | IOBDELAY = NONE                             | XC3S200  | 1.50        | 1.72 | ns    |

|                          | input delay programmed                                               |                                             | XC3S400  | 1.50        | 1.72 | ns    |

|                          |                                                                      |                                             | XC3S1000 | 2.01        | 2.31 | ns    |

|                          |                                                                      |                                             | XC3S1500 | 2.01        | 2.31 | ns    |

|                          |                                                                      |                                             | XC3S2000 | 2.01        | 2.31 | ns    |

|                          |                                                                      |                                             | XC3S4000 | 2.09        | 2.41 | ns    |

|                          |                                                                      |                                             | XC3S5000 | 2.18        | 2.51 | ns    |

| T <sub>IOPLID</sub>      | The time it takes for data to travel                                 | LVCMOS25 <sup>(2)</sup> ,<br>IOBDELAY = IFD | XC3S50   | 4.75        | 5.46 | ns    |

|                          | from the Input pin through the<br>IFF latch to the I output with the |                                             | XC3S200  | 4.89        | 5.62 | ns    |

|                          | input delay programmed                                               |                                             | XC3S400  | 4.76        | 5.48 | ns    |

|                          |                                                                      |                                             | XC3S1000 | 5.38        | 6.18 | ns    |

|                          |                                                                      |                                             | XC3S1500 | 5.76        | 6.62 | ns    |

|                          |                                                                      |                                             | XC3S2000 | 7.04        | 8.09 | ns    |

|                          |                                                                      |                                             | XC3S4000 | 7.52        | 8.65 | ns    |

|                          |                                                                      |                                             | XC3S5000 | 7.69        | 8.84 | ns    |

#### Notes:

- 1. The numbers in this table are tested using the methodology presented in Table 48 and are based on the operating conditions set forth in Table 32 and Table 35.

- 2. This propagation time requires adjustment whenever a signal standard other than LVCMOS25 is assigned to the data Input. When this is true, *add* the appropriate Input adjustment from Table 44.

#### Table 44: Input Timing Adjustments for IOB

|                                                                                   | Add the Adju | stment Below |    |

|-----------------------------------------------------------------------------------|--------------|--------------|----|

| Convert Input Time from LVCMOS25 to the<br>Following Signal Standard (IOSTANDARD) | Speed        | Units        |    |

|                                                                                   | -5           | -4           |    |

| Single-Ended Standards                                                            |              |              |    |

| GTL, GTL_DCI                                                                      | 0.44         | 0.50         | ns |

| GTLP, GTLP_DCI                                                                    | 0.36         | 0.42         | ns |

| HSLVDCI_15                                                                        | 0.51         | 0.59         | ns |

| HSLVDCI_18                                                                        | 0.29         | 0.33         | ns |

| HSLVDCI_25                                                                        | 0.51         | 0.59         | ns |

| HSLVDCI_33                                                                        | 0.51         | 0.59         | ns |

| HSTL_I, HSTL_I_DCI                                                                | 0.51         | 0.59         | ns |

| HSTL_III, HSTL_III_DCI                                                            | 0.37         | 0.42         | ns |

| HSTL_I_18, HSTL_I_DCI_18                                                          | 0.36         | 0.41         | ns |

| HSTL_II_18, HSTL_II_DCI_18                                                        | 0.39         | 0.45         | ns |

| HSTL_III_18, HSTL_III_DCI_18                                                      | 0.45         | 0.52         | ns |

| LVCMOS12                                                                          | 0.63         | 0.72         | ns |

# Table 47: Output Timing Adjustments for IOB (Cont'd)

|              |                                                                                                                       | Add the Adju | stment Below |             |    |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------|--------------|--------------|-------------|----|--|

|              | Convert Output Time from LVCMOS25 with 12mA Drive and Fast Slew Rate to the<br>Following Signal Standard (IOSTANDARD) |              |              | Speed Grade |    |  |

| . enerni,    | ,                                                                                                                     |              |              |             |    |  |

| LVCMOS18     | Slow                                                                                                                  | 2 mA         | 5.49         | 6.31        | ns |  |

|              |                                                                                                                       | 4 mA         | 3.45         | 3.97        | ns |  |

|              |                                                                                                                       | 6 mA         | 2.84         | 3.26        | ns |  |

|              |                                                                                                                       | 8 mA         | 2.62         | 3.01        | ns |  |

|              |                                                                                                                       | 12 mA        | 2.11         | 2.43        | ns |  |

|              |                                                                                                                       | 16 mA        | 2.07         | 2.38        | ns |  |

|              | Fast                                                                                                                  | 2 mA         | 2.50         | 2.88        | ns |  |

|              |                                                                                                                       | 4 mA         | 1.15         | 1.32        | ns |  |

|              |                                                                                                                       | 6 mA         | 0.96         | 1.10        | ns |  |

|              |                                                                                                                       | 8 mA         | 0.87         | 1.01        | ns |  |

|              |                                                                                                                       | 12 mA        | 0.79         | 0.91        | ns |  |

|              |                                                                                                                       | 16 mA        | 0.76         | 0.87        | ns |  |

| LVDCI_18     |                                                                                                                       | 0.81         | 0.94         | ns          |    |  |

| LVDCI_DV2_18 |                                                                                                                       |              | 0.67         | 0.77        | ns |  |

| LVCMOS25     | Slow                                                                                                                  | 2 mA         | 6.43         | 7.39        | ns |  |

|              |                                                                                                                       | 4 mA         | 4.15         | 4.77        | ns |  |

|              |                                                                                                                       | 6 mA         | 3.38         | 3.89        | ns |  |

|              |                                                                                                                       | 8 mA         | 2.99         | 3.44        | ns |  |

|              |                                                                                                                       | 12 mA        | 2.53         | 2.91        | ns |  |

|              |                                                                                                                       | 16 mA        | 2.50         | 2.87        | ns |  |

|              |                                                                                                                       | 24 mA        | 2.22         | 2.55        | ns |  |

|              | Fast                                                                                                                  | 2 mA         | 3.27         | 3.76        | ns |  |

|              |                                                                                                                       | 4 mA         | 1.87         | 2.15        | ns |  |

|              |                                                                                                                       | 6 mA         | 0.32         | 0.37        | ns |  |

|              |                                                                                                                       | 8 mA         | 0.19         | 0.22        | ns |  |

|              |                                                                                                                       | 12 mA        | 0            | 0           | ns |  |

|              |                                                                                                                       | 16 mA        | -0.02        | -0.01       | ns |  |

|              |                                                                                                                       | 24 mA        | -0.04        | -0.02       | ns |  |

| LVDCI_25     |                                                                                                                       |              | 0.27         | 0.31        | ns |  |

| LVDCI_DV2_25 |                                                                                                                       |              | 0.16         | 0.19        | ns |  |

# Table 56: Block RAM Timing

| Symbol                                                                                                                                         | Description                                                                                                                         | •    | -5                                      | -4   |      | Units |

|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------------------------|------|------|-------|

|                                                                                                                                                |                                                                                                                                     | Min  | Max                                     | Min  | Мах  | _     |

| Clock-to-Output                                                                                                                                | Times                                                                                                                               |      |                                         |      |      |       |

| Т <sub>ВСКО</sub>                                                                                                                              | When reading from the Block RAM,<br>the time from the active transition at<br>the CLK input to data appearing at<br>the DOUT output | -    | 2.09                                    | -    | 2.40 | ns    |

| Setup Times                                                                                                                                    |                                                                                                                                     |      |                                         |      |      |       |

| T <sub>BDCK</sub> Time from the setup of data at the<br>DIN inputs to the active transition at<br>the CLK input of the Block RAM               |                                                                                                                                     | 0.43 | -                                       | 0.49 | _    | ns    |

| Hold Times                                                                                                                                     |                                                                                                                                     |      |                                         |      |      |       |

| T <sub>BCKD</sub> Time from the active transition at the<br>Block RAM's CLK input to the point<br>where data is last held at the DIN<br>inputs |                                                                                                                                     | 0    | -                                       | 0    | -    | ns    |

| Clock Timing                                                                                                                                   |                                                                                                                                     |      |                                         | -    | •    |       |

| T <sub>BPWH</sub>                                                                                                                              | Block RAM CLK signal High pulse width                                                                                               | 1.19 | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | 1.37 | ∞    | ns    |

| T <sub>BPWL</sub> Block RAM CLK signal Low pulse width                                                                                         |                                                                                                                                     | 1.19 | ∞                                       | 1.37 | ∞    | ns    |

#### Notes:

1. The numbers in this table are based on the operating conditions set forth in Table 32.

2. For minimums, use the values reported by the Xilinx timing analyzer.

# **Clock Distribution Switching Characteristics**

### Table 57: Clock Distribution Switching Characteristics

| Description                                                                                                  |                  | Maximum<br>Speed Grade |      | Units |  |

|--------------------------------------------------------------------------------------------------------------|------------------|------------------------|------|-------|--|

|                                                                                                              |                  | -5                     | -4   |       |  |

| Global clock buffer (BUFG, BUFGMUX, BUFGCE) I-input to O-output delay                                        | T <sub>GIO</sub> | 0.36                   | 0.41 | ns    |  |

| Global clock multiplexer (BUFGMUX) select S-input setup to I0- and I1-inputs. Same as BUFGCE enable CE-input | T <sub>GSI</sub> | 0.53                   | 0.60 | ns    |  |

#### Notes:

1. For minimums, use the values reported by the Xilinx timing analyzer.

| Date     | Version | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 05/25/07 | 2.2     | Improved absolute maximum voltage specifications in Table 28, providing additional overshoot allowance.<br>Improved XC3S50 HBM ESD to 2000V in Table 28. Based on extensive 90 nm production data, improved (reduced) the maximum quiescent current limits for the I <sub>CCINTQ</sub> and I <sub>CCOQ</sub> specifications in Table 34.<br>Widened the recommended voltage range for the PCI standard and clarified the hysteresis footnote in Table 35. Noted restriction on combining differential outputs in Table 38. Updated footnote 1 in Table 64.                                                                                                                                                                                                                                                                                               |

| 11/30/07 | 2.3     | Updated 3.3V VCCO max from 3.45V to 3.465V in Table 32 and elsewhere. Reduced $t_{ICCK}$ minimum from 0.50 $\mu$ s to 0.25 $\mu$ s in Table 65. Updated links to technical documentation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 06/25/08 | 2.4     | Clarified dual marking. Added Mask and Fab Revisions. Added references to <u>XAPP459</u> in Table 28 and Table 32. Removed absolute minimum and added footnote referring to timing analyzer for minimum delay values. Added HSLVDCI to Table 48 and Table 50. Updated t <sub>DICK</sub> in Table 51 to match largest possible value in speed file. Updated formatting and links.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 12/04/09 | 2.5     | Updated notes 2 and 3 in Table 28. Removed silicon process specific information and revised notes in Table 30. Updated note 3 in Table 32. Updated note 3 in Table 34. Updated note 5 in Table 35. Updated $V_{OL}$ max and $V_{OH}$ min for SSTL2_II in Table 36. Updated note 5 in Table 36. Updated JTAG Waveforms in Figure 39. Updated $V_{ICM}$ max for LVPECL_25 in Table 37. Updated RT and VT for LVDS_25_DCI in Table 48. Updated Simultaneously Switching Output Guidelines. Noted that the CP132 package is being discontinued in Table 49. Removed minimum values for $T_{MULTCK}$ clock-to-output times in Table 54. Updated footnote 3 in Table 58. Removed minimum values for T <sub>MULTCK</sub> propagation times in Table 55. Removed silicon process specific information and revised notes in Table 61. Updated Phase Shifter (PS). |

| 10/29/12 | 3.0     | Added Notice of Disclaimer. Per <u>XCN07022</u> , updated the discontinued FG1156 and FGG1156 package discussion throughout document. Per <u>XCN08011</u> , updated the discontinued CP132 and CPG132 package discussion throughout document. Revised description of V <sub>IN</sub> in Table 32 and added note 7. Added note 4 to Table 33. This product is not recommended for new designs.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

#### Table 69: Types of Pins on Spartan-3 FPGAs (Cont'd)

| Pin Type/<br>Color Code | Description                                                                                                                                                                                                                                                       | Pin Name                                                                                                                                                    |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VREF                    | Dual-purpose pin that is either a user-I/O pin or, along with all other VREF pins in the same bank, provides a reference voltage input for certain I/O standards. If used for a reference voltage within a bank, all VREF pins within the bank must be connected. | IO/VREF_#<br>IO_Lxxy_#/VREF_#                                                                                                                               |

| GND                     | Dedicated ground pin. The number of GND pins depends on the package used. All must be connected.                                                                                                                                                                  | GND                                                                                                                                                         |

| VCCAUX                  | Dedicated auxiliary power supply pin. The number of VCCAUX pins depends on the package used. All must be connected to +2.5V.                                                                                                                                      | VCCAUX                                                                                                                                                      |

| VCCINT                  | Dedicated internal core logic power supply pin. The number of VCCINT pins depends on the package used. All must be connected to +1.2V.                                                                                                                            | VCCINT                                                                                                                                                      |

| VCCO                    | Dedicated I/O bank, output buffer power supply pin. Along with other VCCO pins in the same bank, this pin supplies power to the output buffers within the I/O bank and sets the input threshold voltage for some I/O standards.                                   | VCCO_#<br>CP132 and TQ144 Packages Only:<br>VCCO_LEFT, VCCO_TOP,<br>VCCO_RIGHT, VCCO_BOTTOM                                                                 |

| GCLK                    | Dual-purpose pin that is either a user-I/O pin or an input to a specific global buffer input. Every package has eight dedicated GCLK pins.                                                                                                                        | IO_Lxxy_#/GCLK0,<br>IO_Lxxy_#/GCLK1,<br>IO_Lxxy_#/GCLK2,<br>IO_Lxxy_#/GCLK3,<br>IO_Lxxy_#/GCLK4,<br>IO_Lxxy_#/GCLK5,<br>IO_Lxxy_#/GCLK6,<br>IO_Lxxy_#/GCLK7 |

| N.C.                    | This package pin is not connected in this specific device/package combination but may be connected in larger devices in the same package.                                                                                                                         | N.C.                                                                                                                                                        |

#### Notes:

1. # = I/O bank number, an integer between 0 and 7.

I/Os with Lxxy\_# are part of a differential output pair. 'L' indicates differential output capability. The "xx" field is a two-digit integer, unique to each bank that identifies a differential pin-pair. The 'y' field is either 'P' for the true signal or 'N' for the inverted signal in the differential pair. The '#' field is the I/O bank number.

# **Pin Definitions**

Table 70 provides a brief description of each pin listed in the Spartan-3 FPGA pinout tables and package footprint diagrams. Pins are categorized by their pin type, as listed in Table 69. See Detailed, Functional Pin Descriptions for more information.

| Pin Name | Direction                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIN      | Input                         | Serial Data Input:<br>During the Master or Slave Serial configuration modes, DIN is the serial configuration data input, and<br>all data is synchronized to the rising CCLK edge. After configuration, this pin is available as a user I/O.<br>This signal is located in Bank 4 and its output voltage determined by VCCO_4.<br>The BitGen option <i>Persist</i> permits this pin to retain its configuration function in the User mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DOUT     | Output                        | Serial Data Output:<br>In a multi-FPGA design where all the FPGAs use serial mode, connect the DOUT output of one<br>FPGA—in either Master or Slave Serial mode—to the DIN input of the next FPGA—in Slave Serial<br>mode—so that configuration data passes from one to the next, in daisy-chain fashion. This "daisy<br>chain" permits sequential configuration of multiple FPGAs.<br>This signal is located in Bank 4 and its output voltage determined by VCCO_4.<br>The BitGen option <i>Persist</i> permits this pin to retain its configuration function in the User mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| INIT_B   | Bidirectional<br>(open-drain) | Initializing Configuration Memory/Configuration Error:<br>Just after power is applied, the FPGA produces a Low-to-High transition on this pin indicating that<br>initialization ( <i>i.e.</i> , clearing) of the configuration memory has finished. Before entering the User mode,<br>this pin functions as an open-drain output, which requires a pull-up resistor in order to produce a High<br>logic level. In a multi-FPGA design, tie (wire AND) the INIT_B pins from all FPGAs together so that the<br>common node transitions High only after all of the FPGAs have been successfully initialized.<br>Externally holding this pin Low beyond the initialization phase delays the start of configuration. This<br>action stalls the FPGA at the configuration step just before the mode select pins are sampled.<br>During configuration, the FPGA indicates the occurrence of a data (i.e., CRC) error by asserting<br>INIT_B Low.<br>This signal is located in Bank 4 and its output voltage determined by VCCO_4.<br>The BitGen option <i>Persist</i> permits this pin to retain its configuration function in the User mode. |

### Table 71: Dual-Purpose Pins Used in Master or Slave Serial Mode

# Parallel Configuration Modes (SelectMAP)

This section describes the dual-purpose configuration pins used during the Master and Slave Parallel configuration modes, sometimes also called the SelectMAP modes. In both Master and Slave Parallel configuration modes, D0-D7 form the byte-wide configuration data input. See Table 75 for Mode Select pin settings required for Parallel modes.

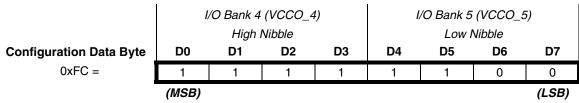

As shown in Figure 41, D0 is the most-significant bit while D7 is the least-significant bit. Bits D0-D3 form the high nibble of the byte and bits D4-D7 form the low nibble.

In the Parallel configuration modes, both the VCCO\_4 and VCCO\_5 voltage supplies are required and must both equal the voltage of the attached configuration device, typically either 2.5V or 3.3V.

Assert Low both the chip-select pin, CS\_B, and the read/write control pin, RDWR\_B, to write the configuration data byte presented on the D0-D7 pins to the FPGA on a rising-edge of the configuration clock, CCLK. The order of CS\_B and RDWR\_B does not matter, although RDWR\_B must be asserted throughout the configuration process. If RDWR\_B is de-asserted during configuration, the FPGA aborts the configuration operation.

After configuration, these pins are available as general-purpose user I/O. However, the SelectMAP configuration interface is optionally available for debugging and dynamic reconfiguration. To use these SelectMAP pins after configuration, set the Persist bitstream generation option.

The Readback debugging option, for example, requires the Persist bitstream generation option. During Readback mode, assert CS\_B Low, along with RDWR\_B High, to read a configuration data byte from the FPGA to the D0-D7 bus on a rising CCLK edge. During Readback mode, D0-D7 are output pins.

In all the cases, the configuration data and control signals are synchronized to the rising edge of the CCLK clock signal.

Once the FPGA enters User mode after completing configuration, the DONE pin no longer drives the DONE pin Low. The bitstream generator option DonePin determines whether or not a pull-up resistor is present on the DONE pin to pull the pin to VCCAUX. If the pull-up resistor is eliminated, then the DONE pin must be pulled High using an external pull-up resistor or one of the FPGAs in the design must actively drive the DONE pin High via the DriveDone bitstream generator option.

The bitstream generator option DriveDone causes the FPGA to actively drive the DONE output High after configuration. This option should only be used in single-FPGA designs or on the last FPGA in a multi-FPGA daisy-chain.

By default, the bitstream generator software retains the pull-up resistor and does not actively drive the DONE pin as highlighted in Table 74, which shows the interaction of these bitstream options in single- and multi-FPGA designs.

| DonePin  | DriveDone | Single- or Multi-<br>FPGA Design | Comments                                                                                                                         |  |

|----------|-----------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--|

| Pullnone | No        | Single                           | External pull-up resistor, with value between $330\Omega$ to $3.3k\Omega$ , required on DONE.                                    |  |

| Pullnone | No        | Multi                            | External pull-up resistor, with value between $330\Omega$ to $3.3k\Omega$ , required on common node connecting to all DONE pins. |  |

| Pullnone | Yes       | Single                           | OK, no external requirements.                                                                                                    |  |

| Pullnone | Yes       | Multi                            | DriveDone on last device in daisy-chain only. No external requirements.                                                          |  |

| Pullup   | No        | Single                           | OK, but pull-up on DONE pin has slow rise time. May require $330\Omega$ pull-up resistor for high CCLK frequencies.              |  |

| Pullup   | No        | Multi                            | External pull-up resistor, with value between $330\Omega$ to $3.3k\Omega$ , required on commonode connecting to all DONE pins.   |  |

| Pullup   | Yes       | Single                           | OK, no external requirements.                                                                                                    |  |

| Pullup   | Yes       | Multi                            | DriveDone on last device in daisy-chain only. No external requirements.                                                          |  |

Table 74: DonePin and DriveDone Bitstream Option Interaction

# M2, M1, M0: Configuration Mode Selection

The M2, M1, and M0 inputs select the FPGA configuration mode, as described in Table 75. The logic levels applied to the mode pins are sampled on the rising edge of INIT\_B.

| Configuration Mode  | M2 | M1 | MO |

|---------------------|----|----|----|

| Master Serial       | 0  | 0  | 0  |

| Slave Serial        | 1  | 1  | 1  |

| Master Parallel     | 0  | 1  | 1  |

| Slave Parallel      | 1  | 1  | 0  |

| JTAG                | 1  | 0  | 1  |

| Reserved            | 0  | 0  | 1  |

| Reserved            | 0  | 1  | 0  |

| Reserved            | 1  | 0  | 0  |

| After Configuration | Х  | Х  | Х  |

Table 75: Spartan-3 FPGA Mode Select Settings

# Notes:

1. X =don't care, either 0 or 1.

Before and during configuration, the mode pins have an internal pull-up resistor to VCCAUX, regardless of the HSWAP\_EN pin. If the mode pins are unconnected, then the FPGA defaults to the Slave Serial configuration mode. After configuration successfully completes, any levels applied to these input are ignored. Furthermore, the bitstream generator options M0Pin, M1Pin, and M2Pin determines whether a pull-up resistor, pull-down resistor, or no resistor is present on its respective mode pin, M0, M1, or M2.

### Table 80: Bitstream Options Affecting Spartan-3 Device Pins (Cont'd)

| Affected Pin Name(s) | Bitstream Generation Function                                                                                                                                                                                                                                  | Option<br>Variable<br>Name | Values<br>( <u>Default</u> )                                          |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------------------------------------------|

| CCLK                 | After configuration, this bitstream option either pulls CCLK to VCCAUX via a pull-up resistor, or allows CCLK to float.                                                                                                                                        | CclkPin                    | <ul><li><u>Pullup</u></li><li>Pullnone</li></ul>                      |

| CCLK                 | For Master configuration modes, this option sets the approximate frequency, in MHz, for the internal silicon oscillator.                                                                                                                                       | ConfigRate                 | • 3, <u>6</u> , 12, 25, 50                                            |

| PROG_B               | A pull-up resistor to VCCAUX exists on PROG_B during configuration.<br>After configuration, this bitstream option either pulls PROG_B to VCCAUX via a pull-up resistor, or allows PROG_B to float.                                                             | ProgPin                    | <ul><li><u>Pullup</u></li><li>Pullnone</li></ul>                      |

| DONE                 | After configuration, this bitstream option either pulls DONE to VCCAUX via a pull-up resistor, or allows DONE to float. See also DriveDone option.                                                                                                             | DonePin                    | <ul><li><u>Pullup</u></li><li>Pullnone</li></ul>                      |

| DONE                 | If set to Yes, this option allows the FPGA's DONE pin to drive High when configuration completes. By default, the DONE is an open-drain output and can only drive Low. Only single FPGAs and the last FPGA in a multi-FPGA daisy-chain should use this option. | DriveDone                  | • <u>No</u><br>• Yes                                                  |

| M2                   | After configuration, this bitstream option either pulls M2 to VCCAUX via a pull-up resistor, to ground via a pull-down resistor, or allows M2 to float.                                                                                                        | M2Pin                      | <ul><li><u>Pullup</u></li><li>Pulldown</li><li>Pullnone</li></ul>     |

| M1                   | After configuration, this bitstream option either pulls M1 to VCCAUX via a pull-up resistor, to ground via a pull-down resistor, or allows M1 to float.                                                                                                        | M1Pin                      | <ul><li><u>Pullup</u></li><li>Pulldown</li><li>Pullnone</li></ul>     |

| MO                   | After configuration, this bitstream option either pulls M0 to VCCAUX via a pull-up resistor, to ground via a pull-down resistor, or allows M0 to float.                                                                                                        | M0Pin                      | <ul> <li><u>Pullup</u></li> <li>Pulldown</li> <li>Pullnone</li> </ul> |

| HSWAP_EN             | After configuration, this bitstream option either pulls HSWAP_EN to VCCAUX via a pull-up resistor, to ground via a pull-down resistor, or allows HSWAP_EN to float.                                                                                            | HswapenPin                 | <ul><li><u>Pullup</u></li><li>Pulldown</li><li>Pullnone</li></ul>     |

| TDI                  | After configuration, this bitstream option either pulls TDI to VCCAUX via a pull-up resistor, to ground via a pull-down resistor, or allows TDI to float.                                                                                                      | TdiPin                     | <ul><li><u>Pullup</u></li><li>Pulldown</li><li>Pullnone</li></ul>     |

| TMS                  | After configuration, this bitstream option either pulls TMS to VCCAUX via a pull-up resistor, to ground via a pull-down resistor, or allows TMS to float.                                                                                                      | TmsPin                     | <ul> <li><u>Pullup</u></li> <li>Pulldown</li> <li>Pullnone</li> </ul> |

| ТСК                  | After configuration, this bitstream option either pulls TCK to VCCAUX via a pull-up resistor, to ground via a pull-down resistor, or allows TCK to float.                                                                                                      | TckPin                     | <ul> <li><u>Pullup</u></li> <li>Pulldown</li> <li>Pullnone</li> </ul> |

| TDO                  | After configuration, this bitstream option either pulls TDO to VCCAUX via a pull-up resistor, to ground via a pull-down resistor, or allows TDO to float.                                                                                                      | TdoPin                     | <ul><li><u>Pullup</u></li><li>Pulldown</li><li>Pullnone</li></ul>     |

# **Setting Bitstream Generator Options**

Refer to the "BitGen" chapter in the Xilinx ISE® software documentation.

# **EXILINX**

# VQ100 Footprint

# Table 93: PQ208 Package Pinout (Cont'd)

| Bank | XC3S50<br>Pin Name  | XC3S200, XC3S400<br>Pin Names | PQ208 Pin<br>Number | Туре |

|------|---------------------|-------------------------------|---------------------|------|

| 3    | IO_L20P_3           | IO_L20P_3                     | P114                | I/O  |

| 3    | IO_L21N_3           | IO_L21N_3                     | P117                | I/O  |

| 3    | IO_L21P_3           | IO_L21P_3                     | P116                | I/O  |

| 3    | IO_L22N_3           | IO_L22N_3                     | P120                | I/O  |

| 3    | IO_L22P_3           | IO_L22P_3                     | P119                | I/O  |

| 3    | IO_L23N_3           | IO_L23N_3                     | P123                | I/O  |

| 3    | IO_L23P_3/VREF_3    | IO_L23P_3/VREF_3              | P122                | VREF |

| 3    | IO_L24N_3           | IO_L24N_3                     | P125                | I/O  |

| 3    | IO_L24P_3           | IO_L24P_3                     | P124                | I/O  |

| 3    | N.C. (�)            | IO_L39N_3                     | P128                | I/O  |

| 3    | N.C. (�)            | IO_L39P_3                     | P126                | I/O  |

| 3    | IO_L40N_3/VREF_3    | IO_L40N_3/VREF_3              | P131                | VREF |

| 3    | IO_L40P_3           | IO_L40P_3                     | P130                | I/O  |

| 3    | VCCO_3              | VCCO_3                        | P110                | VCCO |

| 3    | VCCO_3              | VCCO_3                        | P127                | VCCO |

| 4    | 10                  | 10                            | P93                 | I/O  |

| 4    | N.C. (�)            | 10                            | P97                 | I/O  |

| 4    | IO/VREF_4           | IO/VREF_4                     | P85                 | VREF |

| 4    | N.C. (�)            | IO/VREF_4                     | P96                 | VREF |

| 4    | IO/VREF_4           | IO/VREF_4                     | P102                | VREF |

| 4    | IO_L01N_4/VRP_4     | IO_L01N_4/VRP_4               | P101                | DCI  |

| 4    | IO_L01P_4/VRN_4     | IO_L01P_4/VRN_4               | P100                | DCI  |

| 4    | IO_L25N_4           | IO_L25N_4                     | P95                 | I/O  |

| 4    | IO_L25P_4           | IO_L25P_4                     | P94                 | I/O  |

| 4    | IO_L27N_4/DIN/D0    | IO_L27N_4/DIN/D0              | P92                 | DUAL |

| 4    | IO_L27P_4/D1        | IO_L27P_4/D1                  | P90                 | DUAL |

| 4    | IO_L30N_4/D2        | IO_L30N_4/D2                  | P87                 | DUAL |

| 4    | IO_L30P_4/D3        | IO_L30P_4/D3                  | P86                 | DUAL |

| 4    | IO_L31N_4/INIT_B    | IO_L31N_4/INIT_B              | P83                 | DUAL |

| 4    | IO_L31P_4/DOUT/BUSY | IO_L31P_4/DOUT/BUSY           | P81                 | DUAL |

| 4    | IO_L32N_4/GCLK1     | IO_L32N_4/GCLK1               | P80                 | GCLK |

| 4    | IO_L32P_4/GCLK0     | IO_L32P_4/GCLK0               | P79                 | GCLK |

| 4    | VCCO_4              | VCCO_4                        | P84                 | VCCO |

| 4    | VCCO_4              | VCCO_4                        | P98                 | VCCO |

| 5    | IO                  | IO                            | P63                 | I/O  |

| 5    | IO                  | IO                            | P71                 | I/O  |

| 5    | IO/VREF_5           | IO/VREF_5                     | P78                 | VREF |

| 5    | IO_L01N_5/RDWR_B    | IO_L01N_5/RDWR_B              | P58                 | DUAL |

| 5    | IO_L01P_5/CS_B      | IO_L01P_5/CS_B                | P57                 | DUAL |

| 5    | IO_L10N_5/VRP_5     | IO_L10N_5/VRP_5               | P62                 | DCI  |

# Table 96: FT256 Package Pinout (Cont'd)

| Bank | XC3S200, XC3S400, XC3S1000<br>Pin Name | FT256 Pin<br>Number | Туре |

|------|----------------------------------------|---------------------|------|

| 4    | IO_L28N_4                              | P11                 | I/O  |

| 4    | IO_L28P_4                              | R11                 | I/O  |

| 4    | IO_L29N_4                              | M10                 | I/O  |

| 4    | IO_L29P_4                              | N10                 | I/O  |

| 4    | IO_L30N_4/D2                           | P10                 | DUAL |

| 4    | IO_L30P_4/D3                           | R10                 | DUAL |

| 4    | IO_L31N_4/INIT_B                       | N9                  | DUAL |

| 4    | IO_L31P_4/DOUT/BUSY                    | P9                  | DUAL |

| 4    | IO_L32N_4/GCLK1                        | R9                  | GCLK |

| 4    | IO_L32P_4/GCLK0                        | Т9                  | GCLK |

| 4    | VCCO_4                                 | L9                  | VCCO |

| 4    | VCCO_4                                 | L10                 | VCCO |

| 4    | VCCO_4                                 | M9                  | VCCO |

| 5    | ю                                      | N5                  | I/O  |

| 5    | IO                                     | P7                  | I/O  |

| 5    | IO                                     | T5                  | I/O  |

| 5    | IO/VREF_5                              | Т8                  | VREF |

| 5    | IO_L01N_5/RDWR_B                       | Т3                  | DUAL |

| 5    | IO_L01P_5/CS_B                         | R3                  | DUAL |

| 5    | IO_L10N_5/VRP_5                        | T4                  | DCI  |

| 5    | IO_L10P_5/VRN_5                        | R4                  | DCI  |

| 5    | IO_L27N_5/VREF_5                       | R5                  | VREF |

| 5    | IO_L27P_5                              | P5                  | I/O  |

| 5    | IO_L28N_5/D6                           | N6                  | DUAL |

| 5    | IO_L28P_5/D7                           | M6                  | DUAL |

| 5    | IO_L29N_5                              | R6                  | I/O  |

| 5    | IO_L29P_5/VREF_5                       | P6                  | VREF |

| 5    | IO_L30N_5                              | N7                  | I/O  |

| 5    | IO_L30P_5                              | M7                  | I/O  |

| 5    | IO_L31N_5/D4                           | T7                  | DUAL |

| 5    | IO_L31P_5/D5                           | R7                  | DUAL |

| 5    | IO_L32N_5/GCLK3                        | P8                  | GCLK |

| 5    | IO_L32P_5/GCLK2                        | N8                  | GCLK |

| 5    | VCCO_5                                 | L7                  | VCCO |

| 5    | VCCO_5                                 | L8                  | VCCO |

| 5    | VCCO_5                                 | M8                  | VCCO |

| 6    | IO                                     | K1                  | I/O  |

| 6    | IO_L01N_6/VRP_6                        | R1                  | DCI  |

| 6    | IO_L01P_6/VRN_6                        | P1                  | DCI  |

| 6    | IO_L16N_6                              | P2                  | I/O  |

# Table 107: FG900 Package Pinout (Cont'd)

| Bank | XC3S2000<br>Pin Name | XC3S4000, XC3S5000<br>Pin Name | FG900 Pin<br>Number | Туре |

|------|----------------------|--------------------------------|---------------------|------|

| N/A  | GND                  | GND                            | R17                 | GND  |

| N/A  | GND                  | GND                            | T17                 | GND  |

| N/A  | GND                  | GND                            | U17                 | GND  |

| N/A  | GND                  | GND                            | V17                 | GND  |

| N/A  | GND                  | GND                            | AC17                | GND  |

| N/A  | GND                  | GND                            | AF17                | GND  |

| N/A  | GND                  | GND                            | AK17                | GND  |

| N/A  | GND                  | GND                            | N18                 | GND  |

| N/A  | GND                  | GND                            | P18                 | GND  |

| N/A  | GND                  | GND                            | R18                 | GND  |

| N/A  | GND                  | GND                            | T18                 | GND  |

| N/A  | GND                  | GND                            | U18                 | GND  |

| N/A  | GND                  | GND                            | V18                 | GND  |

| N/A  | GND                  | GND                            | R19                 | GND  |

| N/A  | GND                  | GND                            | T19                 | GND  |

| N/A  | GND                  | GND                            | A21                 | GND  |

| N/A  | GND                  | GND                            | E21                 | GND  |

| N/A  | GND                  | GND                            | H21                 | GND  |

| N/A  | GND                  | GND                            | AC21                | GND  |

| N/A  | GND                  | GND                            | AF21                | GND  |

| N/A  | GND                  | GND                            | AK21                | GND  |

| N/A  | GND                  | GND                            | K23                 | GND  |

| N/A  | GND                  | GND                            | P23                 | GND  |

| N/A  | GND                  | GND                            | U23                 | GND  |

| N/A  | GND                  | GND                            | AA23                | GND  |

| N/A  | GND                  | GND                            | A25                 | GND  |

| N/A  | GND                  | GND                            | AK25                | GND  |

| N/A  | GND                  | GND                            | E26                 | GND  |

| N/A  | GND                  | GND                            | K26                 | GND  |