Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 192                                                        |

| Number of Logic Elements/Cells | 1728                                                       |

| Total RAM Bits                 | 73728                                                      |

| Number of I/O                  | 124                                                        |

| Number of Gates                | 50000                                                      |

| Voltage - Supply               | 1.14V ~ 1.26V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 208-BFQFP                                                  |

| Supplier Device Package        | 208-PQFP (28x28)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc3s50-4pq208c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table 9: Differential I/O Standards

| Signal Standard   | V <sub>cco</sub> | V for Inputs (Volts) |                                     |  |

|-------------------|------------------|----------------------|-------------------------------------|--|

| (IOSTANDARD)      | For Outputs      | For Inputs           | V <sub>REF</sub> for Inputs (Volts) |  |

| LDT_25 (ULVDS_25) | 2.5              | -                    | -                                   |  |

| LVDS_25           | 2.5              | -                    | -                                   |  |

| BLVDS_25          | 2.5              | -                    | -                                   |  |

| LVDSEXT_25        | 2.5              | -                    | -                                   |  |

| LVPECL_25         | 2.5              | -                    | -                                   |  |

| RSDS_25           | 2.5              | -                    | -                                   |  |

| DIFF_HSTL_II_18   | 1.8              | -                    | -                                   |  |

| DIFF_SSTL2_II     | 2.5              | -                    | -                                   |  |

#### Notes:

The need to supply  $V_{REF}$  and  $V_{CCO}$  imposes constraints on which standards can be used in the same bank. See The Organization of IOBs into Banks section for additional guidelines concerning the use of the  $V_{CCO}$  and  $V_{REF}$  lines.

# **Digitally Controlled Impedance (DCI)**

When the round-trip delay of an output signal—i.e., from output to input and back again—exceeds rise and fall times, it is common practice to add termination resistors to the line carrying the signal. These resistors effectively match the impedance of a device's I/O to the characteristic impedance of the transmission line, thereby preventing reflections that adversely affect signal integrity. However, with the high I/O counts supported by modern devices, adding resistors requires significantly more components and board area. Furthermore, for some packages—e.g., ball grid arrays—it may not always be possible to place resistors close to pins.

DCI answers these concerns by providing two kinds of on-chip terminations: Parallel terminations make use of an integrated resistor network. Series terminations result from controlling the impedance of output drivers. DCI actively adjusts both parallel and series terminations to accurately match the characteristic impedance of the transmission line. This adjustment process compensates for differences in I/O impedance that can result from normal variation in the ambient temperature, the supply voltage and the manufacturing process. When the output driver turns off, the series termination, by definition, approaches a very high impedance; in contrast, parallel termination resistors remain at the targeted values.

DCI is available only for certain I/O standards, as listed in Table 10. DCI is selected by applying the appropriate I/O standard extensions to symbols or components. There are five basic ways to configure terminations, as shown in Table 11. The DCI I/O standard determines which of these terminations is put into effect.

HSTL\_I\_DCI-, HSTL\_III\_DCI-, and SSTL2\_I\_DCI-type outputs do not require the VRN and VRP reference resistors. Likewise, LVDCI-type inputs do not require the VRN and VRP reference resistors. In a bank without any DCI I/O or a bank containing non-DCI I/O and purely HSTL\_I\_DCI- or HSTL\_III\_DCI-type outputs, or SSTL2\_I\_DCI-type outputs or LVDCI-type inputs, the associated VRN and VRP pins can be used as general-purpose I/O pins.

The HSLVDCI (High-Speed LVDCI) standard is intended for bidirectional use. The driver is identical to LVDCI, while the input is identical to HSTL. By using a  $V_{REF}$ -referenced input, HSLVDCI allows greater input sensitivity at the receiver than when using a single-ended LVCMOS-type receiver.

<sup>1.</sup> See Table 10 for a listing of the differential DCI standards.

#### Notes:

In the Low Frequency mode, all seven DLL outputs are available. In the High Frequency mode, only the CLK0, CLK180, and CLKDV outputs are available.

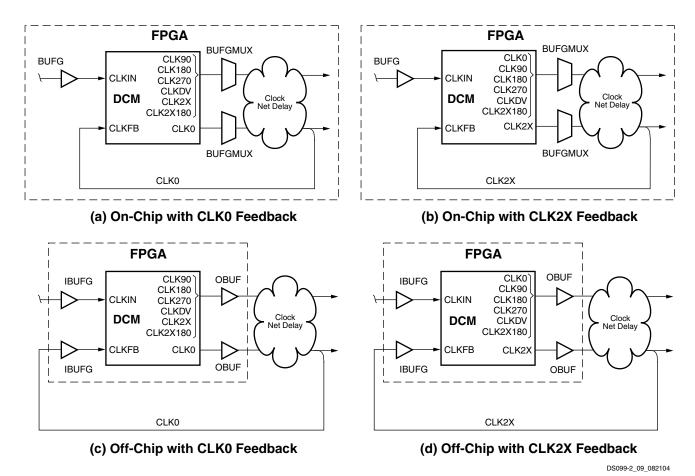

Figure 21: Input Clock, Output Clock, and Feedback Connections for the DLL

In the on-chip synchronization case (the [a] and [b] sections of Figure 21), it is possible to connect any of the DLL's seven output clock signals through general routing resources to the FPGA's internal registers. Either a Global Clock Buffer (BUFG) or a BUFGMUX affords access to the global clock network. As shown in the [a] section of Figure 21, the feedback loop is created by routing CLK0 (or CLK2X, in the [b] section) to a global clock net, which in turn drives the CLKFB input.

In the off-chip synchronization case (the [c] and [d] sections of Figure 21), CLK0 (or CLK2X) plus any of the DLL's other output clock signals exit the FPGA using output buffers (OBUF) to drive an external clock network plus registers on the board. As shown in the [c] section of Figure 21, the feedback loop is formed by feeding CLK0 (or CLK2X, in the [d] section) back into the FPGA using an IBUFG, which directly accesses the global clock network, or an IBUF. Then, the global clock net is connected directly to the CLKFB input.

#### **DLL Frequency Modes**

The DLL supports two distinct operating modes, High Frequency and Low Frequency, with each specified over a different clock frequency range. The DLL\_FREQUENCY\_MODE attribute chooses between the two modes. When the attribute is set to LOW, the Low Frequency mode permits all seven DLL clock outputs to operate over a low-to-moderate frequency range. When the attribute is set to HIGH, the High Frequency mode allows the CLKO, CLK180 and CLKDV outputs to operate at the highest possible frequencies. The remaining DLL clock outputs are not available for use in High Frequency mode.

#### **Accommodating High Input Frequencies**

If the frequency of the CLKIN signal is high such that it exceeds the maximum permitted, divide it down to an acceptable value using the CLKIN\_DIVIDE\_BY\_2 attribute. When this attribute is set to TRUE, the CLKIN frequency is divided by a factor of two just as it enters the DCM.

#### Notes:

1. There are two ways to use the DONE line. First, one may set the BitGen option DriveDone to "Yes" only for the last FPGA to be configured in the chain shown above (or for the single FPGA as may be the case). This enables the DONE pin to drive High; thus, no pull-up resistor is necessary. DriveDone is set to "No" for the remaining FPGAs in the chain. Second, DriveDone can be set to "No" for all FPGAs. Then all DONE lines are open-drain and require the pull-up resistor shown in grey. In most cases, a value between  $3.3K\Omega$  to  $4.7K\Omega$  is sufficient. However, when using DONE synchronously with a long chain of FPGAs, cumulative capacitance may necessitate lower resistor values (e.g. down to  $330\Omega$ ) in order to ensure a rise time within one clock cycle.

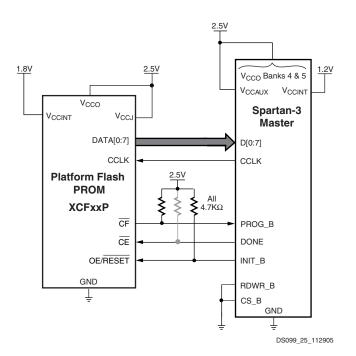

Figure 28: Connection Diagram for Master Parallel Configuration

#### **Master Parallel Mode**

In this mode, the FPGA configures from byte-wide data, and the FPGA supplies the CCLK configuration clock. In Master configuration modes, CCLK behaves as a bidirectional I/O pin. Timing is similar to the Slave Parallel mode except that CCLK is supplied by the FPGA. The device connections are shown in Figure 28.

## **Boundary-Scan (JTAG) Mode**

In Boundary-Scan mode, dedicated pins are used for configuring the FPGA. The configuration is done entirely through the IEEE 1149.1 Test Access Port (TAP). FPGA configuration using the Boundary-Scan mode is compatible with the IEEE Std 1149.1-1993 standard and IEEE Std 1532 for In-System Configurable (ISC) devices.

Configuration through the boundary-scan port is always available, regardless of the selected configuration mode. In some cases, however, the mode pin setting may affect proper programming of the device due to various interactions. For example, if the mode pins are set to Master Serial or Master Parallel mode, and the associated PROM is already programmed with a valid configuration image, then there is potential for configuration interference between the JTAG and PROM data. Selecting the Boundary-Scan mode disables the other modes and is the most reliable mode when programming via JTAG.

## **Configuration Sequence**

The configuration of Spartan-3 devices is a three-stage process that occurs after Power-On Reset or the assertion of PROG\_B. POR occurs after the  $V_{CCINT}$ ,  $V_{CCAUX}$ , and  $V_{CCO}$  Bank 4 supplies have reached their respective maximum input threshold levels (see Table 29, page 59). After POR, the three-stage process begins.

First, the configuration memory is cleared. Next, configuration data is loaded into the memory, and finally, the logic is activated by a start-up process. A flow diagram for the configuration sequence of the Serial and Parallel modes is shown in Figure 29. The flow diagram for the Boundary-Scan configuration sequence appears in Figure 30.

# **Revision History**

| Date     | Version No. | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 04/11/03 | 1.0         | Initial Xilinx release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 05/19/03 | 1.1         | Added Block RAM column, DCMs, and multipliers to XC3S50 descriptions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 07/11/03 | 1.2         | Explained the configuration port <i>Persist</i> option in Slave Parallel Mode (SelectMAP) section. Updated Figure 8 and Double-Data-Rate Transmission section to indicate that DDR clocking for the XC3S50 is the same as that for all other Spartan-3 devices. Updated description of I/O voltage tolerance in ESD Protection section. In Table 10, changed input termination type for DCI version of the LVCMOS standard to <i>None</i> . Added additional flexibility for making DLL connections in Figure 21 and accompanying text. In the Configuration section, inserted an explanation of how to choose power supplies for the configuration interface, including guidelines for achieving 3.3V-tolerance. |

| 08/24/04 | 1.3         | Showed inversion of 3-state signal (Figure 7). Clarified description of pull-up and pull-down resistors (Table 6 and page 13). Added information on operating block RAM with multipliers to page 26. Corrected output buffer name in Figure 21. Corrected description of how DOUT is synchronized to CCLK (page 47).                                                                                                                                                                                                                                                                                                                                                                                              |

| 08/19/05 | 1.4         | Corrected description of WRITE_FIRST and READ_FIRST in Table 13. Added note regarding address setup and hold time requirements whenever a block RAM port is enabled (Table 13). Added information in the maximum length of a Configuration daisy-chain. Added reference to <a href="XAPP453">XAPP453</a> in 3.3V-Tolerant Configuration Interface section. Added information on the STATUS[2] DCM output (Table 23). Added information on CCLK behavior and termination recommendations to Configuration. Added Additional Configuration Details section. Added Powering Spartan-3 FPGAs section. Removed GSR from Figure 31 because its timing is not programmable.                                              |

| 04/03/06 | 2.0         | Updated Figure 7. Updated Figure 14. Updated Table 10. Updated Figure 22. Corrected Platform Flash supply voltage name and value in Figure 26 and Figure 28. Added No Internal Charge Pumps or Free-Running Oscillators. Corrected a few minor typographical errors.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 04/26/06 | 2.1         | Added more information on the pull-up resistors that are active during configuration to Configuration.  Added information to Boundary-Scan (JTAG) Mode about potential interactions when configuring via JTAG if the mode select pins are set for other than JTAG.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 05/25/07 | 2.2         | Added Spartan-3 FPGA Design Documentation. Noted SSTL2_I_DCI 25-Ohm driver in Table 10 and Table 11. Added note that pull-down is active during boundary scan tests.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 11/30/07 | 2.3         | Updated links to documentation on xilinx.com.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 06/25/08 | 2.4         | Added HSLVDCI to Table 10. Updated formatting and links.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 12/04/09 | 2.5         | Updated HSLVDCI description in Digitally Controlled Impedance (DCI). Updated the low-voltage differential signaling V <sub>CCO</sub> values in Table 10. Noted that the CP132 package is being discontinued in The Organization of IOBs into Banks. Updated rule 4 in Rules Concerning Banks. Added software version requirement in The Fixed Phase Mode.                                                                                                                                                                                                                                                                                                                                                         |

| 10/29/12 | 3.0         | Added Notice of Disclaimer. Per XCN07022, updated the discontinued FG1156 and FGG1156 package discussion throughout document. Per XCN08011, updated the discontinued CP132 and CPG132 package discussion throughout document. This product is not recommended for new designs.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Spartan-3 FPGA Family: DC and Switching Characteristics

## Table 28: Absolute Maximum Ratings (Cont'd)

| Symbol           | Description                                   | Conditions                                                                        | Min | Max   | Units |

|------------------|-----------------------------------------------|-----------------------------------------------------------------------------------|-----|-------|-------|

| I <sub>IK</sub>  | Input clamp current per I/O pin               | $-0.5 \text{ V} < \text{V}_{\text{IN}} < (\text{V}_{\text{CCO}} + 0.5 \text{ V})$ | _   | ±100  | mA    |

| V <sub>ESD</sub> | Electrostatic Discharge Voltage pins relative | Human body model                                                                  | _   | ±2000 | V     |

|                  | to GND                                        | Charged device model                                                              | _   | ±500  | V     |

|                  |                                               | Machine model                                                                     | -   | ±200  | V     |

| TJ               | Junction temperature                          |                                                                                   | -   | 125   | °C    |

| T <sub>SOL</sub> | Soldering temperature <sup>(4)</sup>          |                                                                                   | _   | 220   | °C    |

| T <sub>STG</sub> | Storage temperature                           |                                                                                   | -65 | 150   | °C    |

#### Notes:

- Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only; functional operation of the device at these or any other conditions beyond those listed under the Recommended Operating Conditions is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods of time adversely affects device reliability.

- All User I/O and Dual-Purpose pins (DIN/D0, D1–D7, CS\_B, RDWR\_B, BUSY/DOUT, and INIT\_B) draw power from the V<sub>CCO</sub> power rail of the associated bank. Keeping VIN within 500 mV of the associated V<sub>CCO</sub> rails or ground rail ensures that the internal diode junctions that exist between each of these pins and the V<sub>CCO</sub> and GND rails do not turn on. Table 32 specifies the V<sub>CCO</sub> range used to determine the max limit. Input voltages outside the –0.5V to V<sub>CCO</sub>+0.5V voltage range are permissible provided that the I<sub>IK</sub> input clamp diode rating is met and no more than 100 pins exceed the range simultaneously. Prolonged exposure to such current may compromise device reliability. A sustained current of 10 mA will not compromise device reliability. See XAPP459, Eliminating I/O Coupling Effects when Interfacing Large-Swing Single-Ended Signals to User I/O Pins on Spartan-3 Generation FPGAs for more details. The VIN limits apply to both the DC and AC components of signals. Simple application solutions are available that show how to handle overshoot/undershoot as well as achieve PCI compliance. Refer to the following application notes: XAPP457, Powering and Configuring Spartan-3 Generation FPGAs in Compliant PCI Applications and XAPP659, Virtex®-II Pro X 3.3V I/O Design Guidelines.

- All Dedicated pins (M0–M2, CCLK, PROG\_B, DONE, HSWAP\_EN, TCK, TDI, TDO, and TMS) draw power from the  $V_{CCAUX}$  rail (2.5V). Meeting the  $V_{IN}$  max limit ensures that the internal diode junctions that exist between each of these pins and the  $V_{CCAUX}$  rail do not turn on. Table 32 specifies the  $V_{CCAUX}$  range used to determine the max limit. When  $V_{CCAUX}$  is at its maximum recommended operating level (2.625V),  $V_{IN}$  max < 3.125V. As long as the  $V_{IN}$  max specification is met, oxide stress is not possible. For information concerning the use of 3.3V signals, see the 3.3V-Tolerant Configuration Interface, page 47. See also XAPP459

- For soldering guidelines, see UG112, Device Packaging and Thermal Characteristics and XAPP427, Implementation and Solder Reflow Guidelines for Pb-Free Packages.

#### Table 29: Supply Voltage Thresholds for Power-On Reset

| Symbol              | Description                                      | Min | Max | Units |

|---------------------|--------------------------------------------------|-----|-----|-------|

| V <sub>CCINTT</sub> | Threshold for the V <sub>CCINT</sub> supply      | 0.4 | 1.0 | V     |

| V <sub>CCAUXT</sub> | Threshold for the V <sub>CCAUX</sub> supply      | 0.8 | 2.0 | V     |

| V <sub>CCO4T</sub>  | Threshold for the V <sub>CCO</sub> Bank 4 supply | 0.4 | 1.0 | V     |

#### Notes:

- $V_{CCINT}$ ,  $V_{CCAUX}$ , and  $V_{CCO}$  supplies may be applied in any order. When applying  $V_{CCINT}$  power before  $V_{CCAUX}$  power, the FPGA may draw a *surplus* current in addition to the quiescent current levels specified in Table 34. Applying  $V_{CCAUX}$  eliminates the surplus current. The FPGA does not use any of the surplus current for the power-on process. For this power sequence, make sure that regulators with foldback features will not shut down inadvertently.

- To ensure successful power-on, V<sub>CCINT</sub>, V<sub>CCO</sub> Bank 4, and V<sub>CCAUX</sub> supplies must rise through their respective threshold-voltage ranges 2. with no dips at any point.

- If a brown-out condition occurs where  $V_{CCAUX}$  or  $V_{CCINT}$  drops below the retention voltage indicated in Table 31, then  $V_{CCAUX}$  or  $V_{CCINT}$  must drop below the minimum power-on reset voltage in order to clear out the device configuration content.

Table 50: Recommended Number of Simultaneously Switching Outputs per V<sub>CCO</sub>/GND Pair (Cont'd)

| Cianal Standard                 |      |    | Package |       |       |       |                                              |  |  |

|---------------------------------|------|----|---------|-------|-------|-------|----------------------------------------------|--|--|

| Signal Standard<br>(IOSTANDARD) |      |    | VQ100   | TQ144 | PQ208 | CP132 | FT256, FG320, FG456,<br>FG676, FG900, FG1156 |  |  |

| LVCMOS33                        | Slow | 2  | 34      | 24    | 24    | 52    | 76                                           |  |  |

|                                 |      | 4  | 17      | 14    | 14    | 26    | 46                                           |  |  |

|                                 |      | 6  | 17      | 11    | 11    | 26    | 27                                           |  |  |

|                                 |      | 8  | 10      | 10    | 10    | 13    | 20                                           |  |  |

|                                 |      | 12 | 9       | 9     | 9     | 13    | 13                                           |  |  |

|                                 |      | 16 | 8       | 8     | 8     | 8     | 10                                           |  |  |

|                                 |      | 24 | 8       | 8     | 8     | 8     | 9                                            |  |  |

|                                 | Fast | 2  | 20      | 20    | 20    | 26    | 44                                           |  |  |

|                                 |      | 4  | 15      | 15    | 15    | 15    | 26                                           |  |  |

|                                 |      | 6  | 11      | 11    | 11    | 13    | 16                                           |  |  |

|                                 |      | 8  | 10      | 10    | 10    | 10    | 12                                           |  |  |

|                                 |      | 12 | 8       | 8     | 8     | 8     | 10                                           |  |  |

|                                 |      | 16 | 8       | 8     | 8     | 8     | 8                                            |  |  |

|                                 |      | 24 | 7       | 7     | 7     | 7     | 7                                            |  |  |

| LVDCI_33                        | +    | -  | 10      | 10    | 10    | 10    | 10                                           |  |  |

| LVDCI_DV2_33                    |      |    | 10      | 10    | 10    | 10    | 10                                           |  |  |

| HSLVDCI_33                      |      |    | 10      | 10    | 10    | 10    | 10                                           |  |  |

| LVTTL                           | Slow | 2  | 34      | 25    | 25    | 52    | 60                                           |  |  |

|                                 |      | 4  | 17      | 16    | 16    | 26    | 41                                           |  |  |

|                                 |      | 6  | 17      | 15    | 15    | 26    | 29                                           |  |  |

|                                 |      | 8  | 12      | 12    | 12    | 13    | 22                                           |  |  |

|                                 |      | 12 | 10      | 10    | 10    | 13    | 13                                           |  |  |

|                                 |      | 16 | 10      | 10    | 10    | 10    | 11                                           |  |  |

|                                 |      | 24 | 8       | 8     | 8     | 8     | 9                                            |  |  |

|                                 | Fast | 2  | 20      | 20    | 20    | 26    | 34                                           |  |  |

|                                 |      | 4  | 13      | 13    | 13    | 13    | 20                                           |  |  |

|                                 |      | 6  | 11      | 11    | 11    | 13    | 15                                           |  |  |

|                                 |      | 8  | 10      | 10    | 10    | 10    | 12                                           |  |  |

|                                 |      | 12 | 9       | 9     | 9     | 9     | 10                                           |  |  |

|                                 |      | 16 | 8       | 8     | 8     | 8     | 9                                            |  |  |

|                                 |      | 24 | 7       | 7     | 7     | 7     | 7                                            |  |  |

Spartan-3 FPGA Family: DC and Switching Characteristics

## **Digital Clock Manager (DCM) Timing**

For specification purposes, the DCM consists of three key components: the Delay-Locked Loop (DLL), the Digital Frequency Synthesizer (DFS), and the Phase Shifter (PS).

Aspects of DLL operation play a role in all DCM applications. All such applications inevitably use the CLKIN and the CLKFB inputs connected to either the CLK0 or the CLK2X feedback, respectively. Thus, specifications in the DLL tables (Table 58 and Table 59) apply to any application that only employs the DLL component. When the DFS and/or the PS components are used together with the DLL, then the specifications listed in the DFS and PS tables (Table 60 through Table 63) supersede any corresponding ones in the DLL tables. DLL specifications that do not change with the addition of DFS or PS functions are presented in Table 58 and Table 59.

Period jitter and cycle-cycle jitter are two (of many) different ways of characterizing clock jitter. Both specifications describe statistical variation from a mean value.

Period jitter is the worst-case deviation from the average clock period of all clock cycles in the collection of clock periods sampled (usually from 100,000 to more than a million samples for specification purposes). In a histogram of period jitter, the mean value is the clock period.

Cycle-cycle jitter is the worst-case difference in clock period between adjacent clock cycles in the collection of clock periods sampled. In a histogram of cycle-cycle jitter, the mean value is zero.

## **Delay-Locked Loop (DLL)**

Table 58: Recommended Operating Conditions for the DLL

|                       |                           |                                                                                       |                                             |                   | Speed              | d Grade           |                       |       |

|-----------------------|---------------------------|---------------------------------------------------------------------------------------|---------------------------------------------|-------------------|--------------------|-------------------|-----------------------|-------|

| Symbol                |                           | Description                                                                           | Frequency Mode/<br>F <sub>CLKIN</sub> Range | -5                |                    | -4                |                       | Units |

|                       |                           |                                                                                       | · CLKIN · · · · · · · · · ·                 | Min               | Max                | Min               | Max                   |       |

| Input Fi              | requency Ranges           |                                                                                       |                                             |                   |                    |                   |                       |       |

| F <sub>CLKIN</sub>    | CLKIN_FREQ_DLL_LF         | Frequency for the CLKIN input                                                         | Low                                         | 18 <sup>(2)</sup> | 167 <sup>(3)</sup> | 18 <sup>(2)</sup> | 167 <sup>(3)</sup>    | MHz   |

|                       | CLKIN_FREQ_DLL_HF         |                                                                                       | High                                        | 48                | 280 <sup>(3)</sup> | 48                | 280 <sup>(3)(4)</sup> | MHz   |

| Input P               | ulse Requirements         |                                                                                       | ,                                           |                   | 1                  |                   |                       |       |

| CLKIN_                | PULSE                     | CLKIN pulse width as a                                                                | F <sub>CLKIN</sub> ≤ 100 MHz                | 40%               | 60%                | 40%               | 60%                   | -     |

|                       |                           | percentage of the CLKIN period                                                        | F <sub>CLKIN</sub> > 100 MHz                | 45%               | 55%                | 45%               | 55%                   | -     |

| Input C               | lock Jitter Tolerance and | Delay Path Variation <sup>(5)</sup>                                                   |                                             |                   |                    |                   |                       |       |

| CLKIN_                | CYC_JITT_DLL_LF           | Cycle-to-cycle jitter at the CLKIN                                                    | Low                                         | -                 | ±300               | -                 | ±300                  | ps    |

| CLKIN_                | CYC_JITT_DLL_HF           | input                                                                                 | High                                        | -                 | ±150               | -                 | ±150                  | ps    |

| CLKIN_                | PER_JITT_DLL_LF           | Period jitter at the CLKIN input                                                      | All                                         | -                 | ±1                 | -                 | ±1                    | ns    |

| CLKIN_PER_JITT_DLL_HF |                           |                                                                                       |                                             | -                 |                    | -                 | 1                     |       |

| CLKFB_                | _DELAY_VAR_EXT            | Allowable variation of off-chip feedback delay from the DCM output to the CLKFB input | All                                         | -                 | ±1                 | -                 | ±1                    | ns    |

#### Notes:

- 1. DLL specifications apply when any of the DLL outputs (CLK0, CLK90, CLK180, CLK270, CLK2X, CLK2X180, or CLKDV) are in use.

- 2. The DFS, when operating independently of the DLL, supports lower F<sub>CI KIN</sub> frequencies. See Table 60.

- The CLKIN\_DIVIDE\_BY\_2 attribute can be used to increase the effective input frequency range up to F<sub>BUFG</sub>. When set to TRUE, CLKIN\_DIVIDE\_BY\_2 divides the incoming clock frequency by two as it enters the DCM.

- 4. Industrial temperature range devices have additional requirements for continuous clocking, as specified in Table 64.

- 5. CLKIN input jitter beyond these limits may cause the DCM to lose lock. See UG331 for more details.

Table 59: Switching Characteristics for the DLL

|                                  |                                                                        | E /                           |          | Speed Grade |      |       |      |       |

|----------------------------------|------------------------------------------------------------------------|-------------------------------|----------|-------------|------|-------|------|-------|

| Symbol                           | Description                                                            | Frequency Mode / FCLKIN Range | Device   | -5          |      | -4    |      | Units |

|                                  |                                                                        | . •=                          |          | Min         | Max  | Min   | Max  |       |

| Output Frequency Ranges          |                                                                        |                               |          |             |      |       |      |       |

| CLKOUT_FREQ_1X_LF                | Frequency for the CLK0,<br>CLK90, CLK180, and CLK270<br>outputs        | Low                           | All      | 18          | 167  | 18    | 167  | MHz   |

| CLKOUT_FREQ_1X_HF                | Frequency for the CLK0 and CLK180 outputs                              | High                          |          | 48          | 280  | 48    | 280  | MHz   |

| CLKOUT_FREQ_2X_LF <sup>(3)</sup> | Frequency for the CLK2X and CLK2X180 outputs                           | Low                           |          | 36          | 334  | 36    | 334  | MHz   |

| CLKOUT_FREQ_DV_LF                | Frequency for the CLKDV                                                | Low                           |          | 1.125       | 110  | 1.125 | 110  | MHz   |

| CLKOUT_FREQ_DV_HF                | output                                                                 | High                          |          | 3           | 185  | 3     | 185  | MHz   |

| Output Clock Jitter(4)           |                                                                        |                               | -        |             |      |       |      |       |

| CLKOUT_PER_JITT_0                | Period jitter at the CLK0 output                                       | All                           | All      | -           | ±100 | -     | ±100 | ps    |

| CLKOUT_PER_JITT_90               | Period jitter at the CLK90 output                                      |                               |          | -           | ±150 | -     | ±150 | ps    |

| CLKOUT_PER_JITT_180              | Period jitter at the CLK180 output                                     |                               |          | -           | ±150 | -     | ±150 | ps    |

| CLKOUT_PER_JITT_270              | Period jitter at the CLK270 output                                     |                               |          | -           | ±150 | -     | ±150 | ps    |

| CLKOUT_PER_JITT_2X               | Period jitter at the CLK2X and CLK2X180 outputs                        |                               |          | ı           | ±200 | -     | ±200 | ps    |

| CLKOUT_PER_JITT_DV1              | Period jitter at the CLKDV output when performing integer division     |                               |          | -           | ±150 | -     | ±150 | ps    |

| CLKOUT_PER_JITT_DV2              | Period jitter at the CLKDV output when performing non-integer division |                               |          | -           | ±300 | -     | ±300 | ps    |

| <b>Duty Cycle</b>                | <u> </u>                                                               |                               | - 11     |             |      |       |      |       |

| CLKOUT_DUTY_CYCLE_DLL(5)         | Duty cycle variation for the                                           | All                           | XC3S50   | _           | ±150 | _     | ±150 | ps    |

|                                  | CLK0, CLK90, CLK180,<br>CLK270, CLK2X, CLK2X180,                       |                               | XC3S200  | _           | ±150 | _     | ±150 | ps    |

|                                  | and CLKDV outputs                                                      |                               | XC3S400  | _           | ±250 | _     | ±250 | ps    |

|                                  |                                                                        |                               | XC3S1000 | _           | ±400 | _     | ±400 | ps    |

|                                  |                                                                        |                               | XC3S1500 | _           | ±400 | _     | ±400 | ps    |

|                                  |                                                                        |                               | XC3S2000 | _           | ±400 | _     | ±400 | ps    |

|                                  |                                                                        |                               | XC3S4000 | _           | ±400 | _     | ±400 | ps    |

|                                  |                                                                        |                               | XC3S5000 | _           | ±400 | _     | ±400 | ps    |

| Phase Alignment                  | <u> </u>                                                               |                               |          |             |      |       | 1    | I     |

| CLKIN_CLKFB_PHASE                | Phase offset between the CLKIN and CLKFB inputs                        | All                           | All      | -           | ±150 | -     | ±150 | ps    |

| CLKOUT_PHASE                     | Phase offset between any two DLL outputs (except CLK2X and CLK0)       |                               |          | -           | ±140 | -     | ±140 | ps    |

|                                  | Phase offset between the CLK2X and CLK0 outputs                        |                               |          | -           | ±250 | _     | ±250 | ps    |

Table 71: Dual-Purpose Pins Used in Master or Slave Serial Mode

| Pin Name | Direction     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIN      | Input         | Serial Data Input:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|          |               | During the Master or Slave Serial configuration modes, DIN is the serial configuration data input, and all data is synchronized to the rising CCLK edge. After configuration, this pin is available as a user I/O.                                                                                                                                                                                                                                                                                                                  |

|          |               | This signal is located in Bank 4 and its output voltage determined by VCCO_4.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|          |               | The BitGen option <i>Persist</i> permits this pin to retain its configuration function in the User mode.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| DOUT     | Output        | Serial Data Output:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|          |               | In a multi-FPGA design where all the FPGAs use serial mode, connect the DOUT output of one FPGA—in either Master or Slave Serial mode—to the DIN input of the next FPGA—in Slave Serial mode—so that configuration data passes from one to the next, in daisy-chain fashion. This "daisy chain" permits sequential configuration of multiple FPGAs.                                                                                                                                                                                 |

|          |               | This signal is located in Bank 4 and its output voltage determined by VCCO_4.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|          |               | The BitGen option <i>Persist</i> permits this pin to retain its configuration function in the User mode.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| INIT_B   | Bidirectional | Initializing Configuration Memory/Configuration Error:                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|          | (open-drain)  | Just after power is applied, the FPGA produces a Low-to-High transition on this pin indicating that initialization ( <i>i.e.</i> , clearing) of the configuration memory has finished. Before entering the User mode, this pin functions as an open-drain output, which requires a pull-up resistor in order to produce a High logic level. In a multi-FPGA design, tie (wire AND) the INIT_B pins from all FPGAs together so that the common node transitions High only after all of the FPGAs have been successfully initialized. |

|          |               | Externally holding this pin Low beyond the initialization phase delays the start of configuration. This action stalls the FPGA at the configuration step just before the mode select pins are sampled.                                                                                                                                                                                                                                                                                                                              |

|          |               | During configuration, the FPGA indicates the occurrence of a data (i.e., CRC) error by asserting INIT_B Low.                                                                                                                                                                                                                                                                                                                                                                                                                        |

|          |               | This signal is located in Bank 4 and its output voltage determined by VCCO_4.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|          |               | The BitGen option <i>Persist</i> permits this pin to retain its configuration function in the User mode.                                                                                                                                                                                                                                                                                                                                                                                                                            |

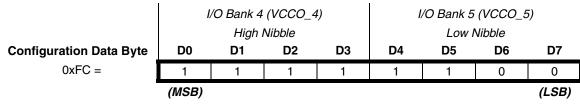

Figure 41: Configuration Data Byte Mapping to D0-D7 Bits

## Parallel Configuration Modes (SelectMAP)

This section describes the dual-purpose configuration pins used during the Master and Slave Parallel configuration modes, sometimes also called the SelectMAP modes. In both Master and Slave Parallel configuration modes, D0-D7 form the byte-wide configuration data input. See Table 75 for Mode Select pin settings required for Parallel modes.

As shown in Figure 41, D0 is the most-significant bit while D7 is the least-significant bit. Bits D0-D3 form the high nibble of the byte and bits D4-D7 form the low nibble.

In the Parallel configuration modes, both the VCCO\_4 and VCCO\_5 voltage supplies are required and must both equal the voltage of the attached configuration device, typically either 2.5V or 3.3V.

Assert Low both the chip-select pin, CS\_B, and the read/write control pin, RDWR\_B, to write the configuration data byte presented on the D0-D7 pins to the FPGA on a rising-edge of the configuration clock, CCLK. The order of CS\_B and RDWR\_B does not matter, although RDWR\_B must be asserted throughout the configuration process. If RDWR\_B is de-asserted during configuration, the FPGA aborts the configuration operation.

After configuration, these pins are available as general-purpose user I/O. However, the SelectMAP configuration interface is optionally available for debugging and dynamic reconfiguration. To use these SelectMAP pins after configuration, set the Persist bitstream generation option.

The Readback debugging option, for example, requires the Persist bitstream generation option. During Readback mode, assert CS\_B Low, along with RDWR\_B High, to read a configuration data byte from the FPGA to the D0-D7 bus on a rising CCLK edge. During Readback mode, D0-D7 are output pins.

In all the cases, the configuration data and control signals are synchronized to the rising edge of the CCLK clock signal.

The 1% precision impedance-matching resistor attached to the VRN\_# pin controls the pull-down impedance of NMOS transistor in the input or output buffer. Consequently, the VRN\_# pin must connect to VCCO. The 'N' character in "VRN" indicates that this pin controls the I/O buffer's NMOS transistor impedance. The VRN\_# pin is only used for split termination.

Each VRN or VRP reference input requires its own resistor. A single resistor cannot be shared between VRN or VRP pins associated with different banks.

During configuration, these pins behave exactly like user-I/O pins. The associated DCI behavior is not active or valid until after configuration completes.

Also see Digitally Controlled Impedance (DCI), page 16.

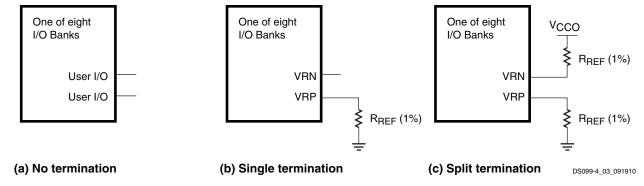

## **DCI Termination Types**

If the I/O in an I/O bank do not use the DCI feature, then no external resistors are required and both the VRP\_# and VRN\_# pins are available for user I/O, as shown in section [a] of Figure 42.

If the I/O standards within the associated I/O bank require single termination—such as GTL\_DCI, GTLP\_DCI, or HSTL\_III\_DCI—then only the VRP\_# signal connects to a 1% precision impedance-matching resistor, as shown in section [b] of Figure 42. A resistor is not required for the VRN\_# pin.

Finally, if the I/O standards with the associated I/O bank require split termination—such as HSTL\_I\_DCI, SSTL2\_I\_DCI, SSTL2\_I\_DCI, or LVDS\_25\_DCI and LVDSEXT\_25\_DCI receivers—then both the VRP\_# and VRN\_# pins connect to separate 1% precision impedance-matching resistors, as shown in section [c] of Figure 42. Neither pin is available for user I/O.

Figure 42: DCI Termination Types

# GCLK: Global Clock Buffer Inputs or General-Purpose I/O Pins

These pins are user-I/O pins unless they specifically connect to one of the eight low-skew global clock buffers on the device, specified using the IBUFG primitive.

There are eight GCLK pins per device and two each appear in the top-edge banks, Bank 0 and 1, and the bottom-edge banks, Banks 4 and 5. See Figure 40 for a picture of bank labeling.

During configuration, these pins behave exactly like user-I/O pins.

Also see Global Clock Network, page 42.

# **CONFIG: Dedicated Configuration Pins**

The dedicated configuration pins control the configuration process and are not available as user-I/O pins. Every package has seven dedicated configuration pins. All CONFIG-type pins are powered by the +2.5V VCCAUX supply.

Also see Configuration, page 46.

## **CCLK: Configuration Clock**

The configuration clock signal on this pin synchronizes the reading or writing of configuration data. The CCLK pin is an input-only pin for the Slave Serial and Slave Parallel configuration modes. In the Master Serial and Master Parallel configuration modes, the FPGA drives the CCLK pin and CCLK should be treated as a full bidirectional I/O pin for signal integrity analysis.

Although the CCLK frequency is relatively low, Spartan-3 FPGA output edge rates are fast. Any potential signal integrity problems on the CCLK board trace can cause FPGA configuration to fail. Therefore, pay careful attention to the CCLK signal integrity on the printed circuit board. Signal integrity simulation with IBIS is recommended. For all configuration modes except JTAG, consider the signal integrity at every CCLK trace destination, including the FPGA's CCLK pin. For more details on CCLK design considerations, see Chapter 2 of UG332, Spartan-3 Generation Configuration User Guide.

During configuration, the CCLK pin has a pull-up resistor to VCCAUX, regardless of the HSWAP\_EN pin. After configuration, the CCLK pin is pulled High to VCCAUX by default as defined by the CclkPin bitstream selection, although this behavior is programmable. Any clocks applied to CCLK after configuration are ignored unless the bitstream option *Persist* is set to *Yes*, which retains the configuration interface. *Persist* is set to *No* by default. However, if *Persist* is set to *Yes*, then all clock edges are potentially active events, depending on the other configuration control signals.

The bitstream generator option *ConfigRate* determines the frequency of the internally-generated CCLK oscillator required for the Master configuration modes. The actual frequency is approximate due to the characteristics of the silicon oscillator and varies by up to 50% over the temperature and voltage range. By default, CCLK operates at approximately 6 MHz. Via the *ConfigRate* option, the oscillator frequency is set at approximately 3, 6, 12, 25, or 50 MHz. At power-on, CCLK always starts operation at its lowest frequency. The device does not start operating at the higher frequency until the ConfigRate control bits are loaded during the configuration process.

## PROG\_B: Program/Configure Device

This asynchronous pin initiates the configuration or re-configuration processes. A Low-going pulse resets the configuration logic, initializing the configuration memory. This initialization process cannot finish until PROG B returns High. Asserting PROG B Low for an extended period delays the configuration process. At power-up, there is always a pull-up resistor to VCCAUX on this pin, regardless of the HSWAP EN input. After configuration, the bitstream generator option *ProgPin* determines whether or not the pull-up resistor is present. By default, the *ProgPin* option retains the pull-up resistor.

After configuration, hold the PROG\_B input High. Any Low-going pulse on PROG\_B lasting 300 ns or longer restarts the configuration process.

Table 73: PROG\_B Operation

| PROG_B Input    | Response                                                                                                                                           |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Power-up        | Automatically initiates configuration process.                                                                                                     |

| Low-going pulse | Initiate (re-)configuration process and continue to completion.                                                                                    |

| Extended Low    | Initiate (re-)configuration process and stall process at step where configuration memory is cleared. Process is stalled until PROG_B returns High. |

| 1               | If the configuration process is started, continue to completion. If configuration process is complete, stay in User mode.                          |

## **DONE: Configuration Done, Delay Start-Up Sequence**

The FPGA produces a Low-to-High transition on this pin indicating that the configuration process is complete. The bitstream generator option *DriveDone* determines whether this pin functions as a totem-pole output that can drive High or as an open-drain output. If configured as an open-drain output—which is the default behavior—then a pull-up resistor is required to produce a High logic level. There is a bitstream option that provides an internal pull-up resistor, otherwise an external pull-up resistor is required.

The open-drain option permits the DONE lines of multiple FPGAs to be tied together, so that the common node transitions High only after all of the FPGAs have completed configuration. Externally holding the open-drain DONE pin Low delays the start-up sequence, which marks the transition to user mode.

Spartan-3 FPGA Family: Pinout Descriptions

118

Once the FPGA enters User mode after completing configuration, the DONE pin no longer drives the DONE pin Low. The bitstream generator option DonePin determines whether or not a pull-up resistor is present on the DONE pin to pull the pin to VCCAUX. If the pull-up resistor is eliminated, then the DONE pin must be pulled High using an external pull-up resistor or one of the FPGAs in the design must actively drive the DONE pin High via the DriveDone bitstream generator option.

The bitstream generator option DriveDone causes the FPGA to actively drive the DONE output High after configuration. This option should only be used in single-FPGA designs or on the last FPGA in a multi-FPGA daisy-chain.

By default, the bitstream generator software retains the pull-up resistor and does not actively drive the DONE pin as highlighted in Table 74, which shows the interaction of these bitstream options in single- and multi-FPGA designs.

Table 74: DonePin and DriveDone Bitstream Option Interaction

| DonePin  | DriveDone | Single- or Multi-<br>FPGA Design | Comments                                                                                                                           |

|----------|-----------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Pullnone | No        | Single                           | External pull-up resistor, with value between 330 $\Omega$ to 3.3k $\Omega$ , required on DONE.                                    |

| Pullnone | No        | Multi                            | External pull-up resistor, with value between 330 $\Omega$ to 3.3k $\Omega$ , required on common node connecting to all DONE pins. |

| Pullnone | Yes       | Single                           | OK, no external requirements.                                                                                                      |

| Pullnone | Yes       | Multi                            | DriveDone on last device in daisy-chain only. No external requirements.                                                            |

| Pullup   | No        | Single                           | OK, but pull-up on DONE pin has slow rise time. May require $330\Omega$ pull-up resistor for high CCLK frequencies.                |

| Pullup   | No        | Multi                            | External pull-up resistor, with value between 330 $\Omega$ to 3.3k $\Omega$ , required on common node connecting to all DONE pins. |

| Pullup   | Yes       | Single                           | OK, no external requirements.                                                                                                      |

| Pullup   | Yes       | Multi                            | DriveDone on last device in daisy-chain only. No external requirements.                                                            |

## M2, M1, M0: Configuration Mode Selection

The M2, M1, and M0 inputs select the FPGA configuration mode, as described in Table 75. The logic levels applied to the mode pins are sampled on the rising edge of INIT B.

Table 75: Spartan-3 FPGA Mode Select Settings

| Configuration Mode  | M2 | M1 | МО |

|---------------------|----|----|----|

| Master Serial       | 0  | 0  | 0  |

| Slave Serial        | 1  | 1  | 1  |

| Master Parallel     | 0  | 1  | 1  |

| Slave Parallel      | 1  | 1  | 0  |

| JTAG                | 1  | 0  | 1  |

| Reserved            | 0  | 0  | 1  |

| Reserved            | 0  | 1  | 0  |

| Reserved            | 1  | 0  | 0  |

| After Configuration | Х  | Х  | Х  |

#### Notes:

X = don't care, either 0 or 1.

Before and during configuration, the mode pins have an internal pull-up resistor to VCCAUX, regardless of the HSWAP\_EN pin. If the mode pins are unconnected, then the FPGA defaults to the Slave Serial configuration mode. After configuration successfully completes, any levels applied to these input are ignored. Furthermore, the bitstream generator options M0Pin, M1Pin, and M2Pin determines whether a pull-up resistor, pull-down resistor, or no resistor is present on its respective mode pin, M0, M1, or M2.

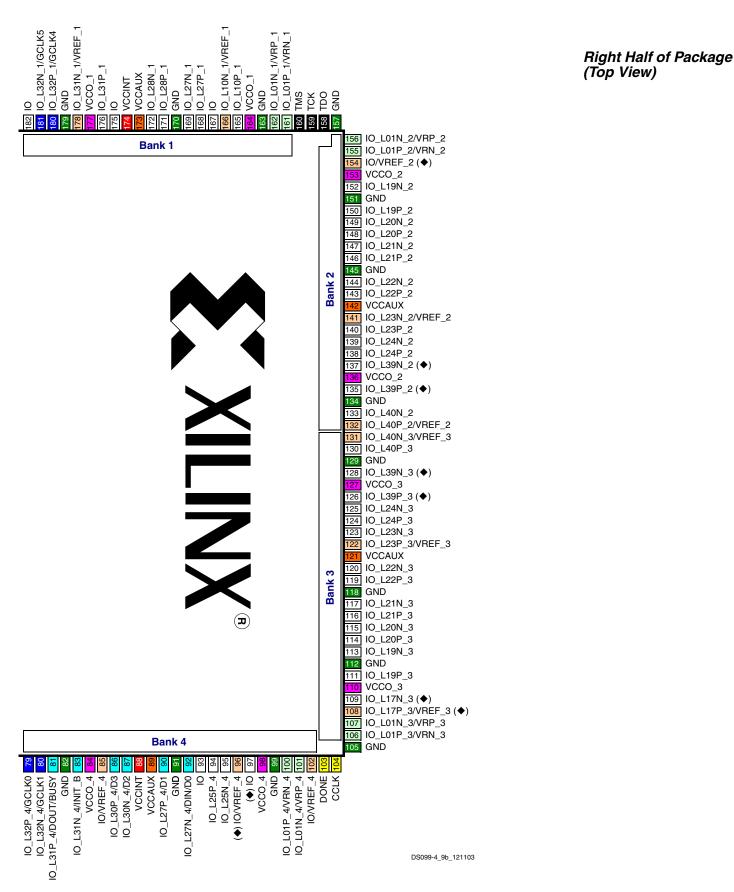

Table 93: PQ208 Package Pinout (Cont'd)

| Bank | XC3S50<br>Pin Name  | XC3S200, XC3S400<br>Pin Names | PQ208 Pin<br>Number | Туре |

|------|---------------------|-------------------------------|---------------------|------|

| 3    | IO_L20P_3           | IO_L20P_3                     | P114                | I/O  |

| 3    | IO_L21N_3           | IO_L21N_3                     | P117                | I/O  |

| 3    | IO_L21P_3           | IO_L21P_3                     | P116                | I/O  |

| 3    | IO_L22N_3           | IO_L22N_3                     | P120                | I/O  |

| 3    | IO_L22P_3           | IO_L22P_3                     | P119                | I/O  |

| 3    | IO_L23N_3           | IO_L23N_3                     | P123                | I/O  |

| 3    | IO_L23P_3/VREF_3    | IO_L23P_3/VREF_3              | P122                | VREF |

| 3    | IO_L24N_3           | IO_L24N_3                     | P125                | I/O  |

| 3    | IO_L24P_3           | IO_L24P_3                     | P124                | I/O  |

| 3    | N.C. (♠)            | IO_L39N_3                     | P128                | I/O  |

| 3    | N.C. (♦)            | IO_L39P_3                     | P126                | I/O  |

| 3    | IO_L40N_3/VREF_3    | IO_L40N_3/VREF_3              | P131                | VREF |

| 3    | IO_L40P_3           | IO_L40P_3                     | P130                | I/O  |

| 3    | VCCO_3              | VCCO_3                        | P110                | VCCO |

| 3    | VCCO_3              | VCCO_3                        | P127                | VCCO |

| 4    | Ю                   | Ю                             | P93                 | I/O  |

| 4    | N.C. (♠)            | Ю                             | P97                 | I/O  |

| 4    | IO/VREF_4           | IO/VREF_4                     | P85                 | VREF |

| 4    | N.C. (♦)            | IO/VREF_4                     | P96                 | VREF |

| 4    | IO/VREF_4           | IO/VREF_4                     | P102                | VREF |

| 4    | IO_L01N_4/VRP_4     | IO_L01N_4/VRP_4               | P101                | DCI  |

| 4    | IO_L01P_4/VRN_4     | IO_L01P_4/VRN_4               | P100                | DCI  |

| 4    | IO_L25N_4           | IO_L25N_4                     | P95                 | I/O  |

| 4    | IO_L25P_4           | IO_L25P_4                     | P94                 | I/O  |

| 4    | IO_L27N_4/DIN/D0    | IO_L27N_4/DIN/D0              | P92                 | DUAL |

| 4    | IO_L27P_4/D1        | IO_L27P_4/D1                  | P90                 | DUAL |

| 4    | IO_L30N_4/D2        | IO_L30N_4/D2                  | P87                 | DUAL |

| 4    | IO_L30P_4/D3        | IO_L30P_4/D3                  | P86                 | DUAL |

| 4    | IO_L31N_4/INIT_B    | IO_L31N_4/INIT_B              | P83                 | DUAL |

| 4    | IO_L31P_4/DOUT/BUSY | IO_L31P_4/DOUT/BUSY           | P81                 | DUAL |

| 4    | IO_L32N_4/GCLK1     | IO_L32N_4/GCLK1               | P80                 | GCLK |

| 4    | IO_L32P_4/GCLK0     | IO_L32P_4/GCLK0               | P79                 | GCLK |

| 4    | VCCO_4              | VCCO_4                        | P84                 | VCCO |

| 4    | VCCO_4              | VCCO_4                        | P98                 | VCCO |

| 5    | Ю                   | Ю                             | P63                 | I/O  |

| 5    | Ю                   | Ю                             | P71                 | I/O  |

| 5    | IO/VREF_5           | IO/VREF_5                     | P78                 | VREF |

| 5    | IO_L01N_5/RDWR_B    | IO_L01N_5/RDWR_B              | P58                 | DUAL |

| 5    | IO_L01P_5/CS_B      | IO_L01P_5/CS_B                | P57                 | DUAL |

| 5    | IO_L10N_5/VRP_5     | IO_L10N_5/VRP_5               | P62                 | DCI  |

Figure 48: PQ208 Package Footprint (Top View) Continued

Table 100: FG456 Package Pinout (Cont'd)

| Bank 3S400 3S10<br>Pin Name |                  | 3S1000, 3S1500, 3S2000<br>Pin Name | FG456<br>Pin Number | Туре |  |

|-----------------------------|------------------|------------------------------------|---------------------|------|--|

| 5                           | IO_L27N_5/VREF_5 | IO_L27N_5/VREF_5                   | W9                  | VREF |  |

| 5                           | IO_L27P_5        | IO_L27P_5                          | IO_L27P_5 V9        |      |  |

| 5                           | IO_L28N_5/D6     | IO_L28N_5/D6                       | AB9                 | DUAL |  |

| 5                           | IO_L28P_5/D7     | IO_L28P_5/D7                       | AA9                 | DUAL |  |

| 5                           | IO_L29N_5        | IO_L29N_5                          | Y10                 | I/O  |  |

| 5                           | IO_L29P_5/VREF_5 | IO_L29P_5/VREF_5                   | W10                 | VREF |  |

| 5                           | IO_L30N_5        | IO_L30N_5                          | AB10                | I/O  |  |

| 5                           | IO_L30P_5        | IO_L30P_5                          | AA10                | I/O  |  |

| 5                           | IO_L31N_5/D4     | IO_L31N_5/D4                       | W11                 | DUAL |  |

| 5                           | IO_L31P_5/D5     | IO_L31P_5/D5                       | V11                 | DUAL |  |

| 5                           | IO_L32N_5/GCLK3  | IO_L32N_5/GCLK3                    | AA11                | GCLK |  |

| 5                           | IO_L32P_5/GCLK2  | IO_L32P_5/GCLK2                    | Y11                 | GCLK |  |

| 5                           | VCCO_5           | VCCO_5                             | Т9                  | VCCO |  |

| 5                           | VCCO_5           | VCCO_5                             | T10                 | VCCO |  |

| 5                           | VCCO_5           | VCCO_5                             | T11                 | VCCO |  |

| 5                           | VCCO_5           | VCCO_5                             | U8                  | VCCO |  |

| 5                           | VCCO_5           | VCCO_5                             | Y8                  | VCCO |  |

| 6                           | IO               | IO                                 | Y1                  | I/O  |  |

| 6                           | IO_L01N_6/VRP_6  | IO_L01N_6/VRP_6                    | Y3                  | DCI  |  |

| 6                           | IO_L01P_6/VRN_6  | IO_L01P_6/VRN_6                    | Y2                  | DCI  |  |

| 6                           | IO_L16N_6        | IO_L16N_6                          | W4                  | I/O  |  |

| 6                           | IO_L16P_6        | IO_L16P_6                          | W3                  | I/O  |  |

| 6                           | IO_L17N_6        | IO_L17N_6                          | W2                  | I/O  |  |

| 6                           | IO_L17P_6/VREF_6 | IO_L17P_6/VREF_6                   | W1                  | VREF |  |

| 6                           | IO_L19N_6        | IO_L19N_6                          | V5                  | I/O  |  |

| 6                           | IO_L19P_6        | IO_L19P_6                          | U5                  | I/O  |  |

| 6                           | IO_L20N_6        | IO_L20N_6                          | V4                  | I/O  |  |

| 6                           | IO_L20P_6        | IO_L20P_6                          | V3                  | I/O  |  |

| 6                           | IO_L21N_6        | IO_L21N_6                          | V2                  | I/O  |  |

| 6                           | IO_L21P_6        | IO_L21P_6                          | V1                  | I/O  |  |

| 6                           | IO_L22N_6        | IO_L22N_6                          | T6                  | I/O  |  |

| 6                           | IO_L22P_6        | IO_L22P_6                          | T5                  | I/O  |  |

| 6                           | IO_L23N_6        | IO_L23N_6                          | U4                  | I/O  |  |

| 6                           | IO_L23P_6        | IO_L23P_6                          | T4                  | I/O  |  |

| 6                           | IO_L24N_6/VREF_6 | IO_L24N_6/VREF_6                   | U3                  | VREF |  |

| 6                           | IO_L24P_6        | IO_L24P_6                          | U2                  | I/O  |  |

| 6                           | N.C. (♠)         | IO_L26N_6                          | Т3                  | I/O  |  |

| 6                           | N.C. (♦)         | IO_L26P_6                          | R4                  | I/O  |  |

| 6                           | IO_L27N_6        | IO_L27N_6                          | T2                  | I/O  |  |

| 6                           | IO_L27P_6        | IO_L27P_6                          | T1                  | I/O  |  |

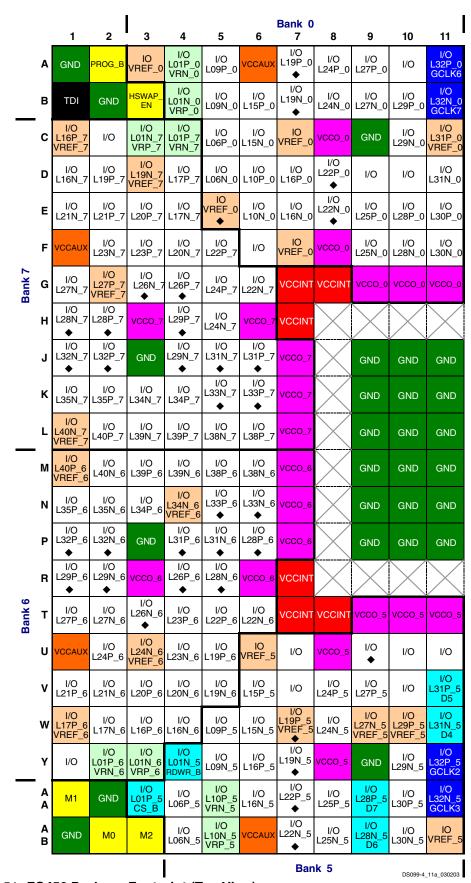

## FG456 Footprint

## Left Half of FG456 Package (Top View)

## XC3S400

(264 max. user I/O)

- 196 I/O: Unrestricted, general-purpose user I/O

- 32 VREF: User I/O or input voltage reference for bank

- 69 N.C.: Unconnected pins for XC3S400 (♠)

#### XC3S1000, XC3S1500, XC3S2000 (333 max user I/O)

- 261 **I/O:** Unrestricted, general-purpose user I/O

- VREF: User I/O or input voltage reference for bank

- N.C.: No unconnected pins in this package

#### All devices

- 12 DUAL: Configuration pin, then possible user I/O

- 8 GCLK: User I/O or global clock buffer input

- DCI: User I/O or reference resistor input for bank

- 7 CONFIG: Dedicated configuration pins

- JTAG: Dedicated JTAG port pins

- 12 VCCINT: Internal core voltage supply (+1.2V)

- 40 VCCO: Output voltage supply for bank

- 8 VCCAUX: Auxiliary voltage supply (+2.5V)

- 52 **GND**: Ground

Figure 51: FG456 Package Footprint (Top View)

## Table 103: FG676 Package Pinout (Cont'd)

| Bank       | XC3S1000<br>Pin Name | XC3S1500<br>Pin Name | XC3S2000<br>Pin Name | XC3S4000<br>Pin Name | XC3S5000<br>Pin Name | FG676 Pin<br>Number | Туре   |

|------------|----------------------|----------------------|----------------------|----------------------|----------------------|---------------------|--------|