Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 100MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | DMA, PWM, WDT                                                           |

| Number of I/O              | 35                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 16K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                            |

| Data Converters            | A/D 2x16b; D/A 1x12b                                                    |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 48-LQFP                                                                 |

| Supplier Device Package    | 48-LQFP (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mkv30f128vlf10p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Implements Field Orient Control (FOC) using Back EMF to improve motor efficiency

- Utilizes SpinTAC control theory that improves overall system performance and reliability

#### Ordering Information

| Part Number                 | Me         | mory      | Number of GPIOs |

|-----------------------------|------------|-----------|-----------------|

|                             | Flash (KB) | SRAM (KB) |                 |

| MKV30F128VLH10              | 128        | 16        | 46              |

| MKV30F128VLF10              | 128        | 16        | 35              |

| MKV30F128VFM10              | 128        | 16        | 26              |

| MKV30F64VLH10               | 64         | 16        | 46              |

| MKV30F64VLF10               | 64         | 16        | 35              |

| MKV30F64VFM10               | 64         | 16        | 26              |

| MKV30F128VLF10P             | 120        | 16        | 35              |

| MKV30F64VLH10P <sup>1</sup> | 56         | 16        | 46              |

| MKV30F64VLF10P <sup>1</sup> | 56         | 16        | 35              |

#### 1. This part number is subject to removal

#### **Related Resources**

| Туре                           | Description                                                                                                                                                                  | Resource                                                                                                                                 |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Selector<br>Guide              | The Freescale Solution Advisor is a web-based tool that features interactive application wizards and a dynamic product selector.                                             | Product Selector                                                                                                                         |

| Product Brief                  | The Product Brief contains concise overview/summary information to enable quick evaluation of a device for design suitability.                                               | KV30FKV31FPB                                                                                                                             |

| Reference<br>Manual            | The Reference Manual contains a comprehensive description of the structure and function (operation) of a device.                                                             | KV30P64M100SFARM                                                                                                                         |

| Data Sheet                     | The Data Sheet includes electrical characteristics and signal connections.                                                                                                   | This document.                                                                                                                           |

| KMS User<br>Guide              | The KMS User Guide provides a comprehensive description of the features and functions of the Kinetis Motor Suite solution.                                                   | Kinetis Motor Suite User's Guide (KMS100UG) <sup>1</sup>                                                                                 |

| KMS API<br>Reference<br>Manual | The KMS API reference manual provides a comprehensive description of the API of the Kinetis Motor Suite function blocks.                                                     | Kinetis Motor Suite API<br>Reference Manual<br>(KMS100RM) <sup>1</sup>                                                                   |

| Chip Errata                    | The chip mask set Errata provides additional or corrective information for a particular device mask set.                                                                     | Kinetis_V_0N36M                                                                                                                          |

| Package<br>drawing             | Package dimensions are provided by the part number:<br>• MKV30F64VLF10P<br>• MKV30F64VLH10P<br>• MKV30F128VLH10<br>• MKV30F128VLF10<br>• MKV30F128VFM10<br>• MKV30F128VLF10P | <ul> <li>98ASH00962A</li> <li>98ASS23234W</li> <li>98ASS23234W</li> <li>98ASH00962A</li> <li>98ARE10566D</li> <li>98ASH00962A</li> </ul> |

1. To find the associated resource, go to freescale.com and perform a search using Document ID

| Symbol           | Description                                                    | Min.                  | Max.                  | Unit |

|------------------|----------------------------------------------------------------|-----------------------|-----------------------|------|

| V <sub>DD</sub>  | Digital supply voltage                                         | -0.3                  | 3.8                   | V    |

| I <sub>DD</sub>  | Digital supply current                                         | _                     | 145                   | mA   |

| V <sub>DIO</sub> | Digital input voltage                                          | -0.3                  | V <sub>DD</sub> + 0.3 | V    |

| V <sub>AIO</sub> | Analog <sup>1</sup>                                            | -0.3                  | V <sub>DD</sub> + 0.3 | V    |

| Ι <sub>D</sub>   | Maximum current single pin limit (applies to all digital pins) | -25                   | 25                    | mA   |

| V <sub>DDA</sub> | Analog supply voltage                                          | V <sub>DD</sub> – 0.3 | V <sub>DD</sub> + 0.3 | V    |

1. Analog pins are defined as pins that do not have an associated general purpose I/O port function.

## 2 General

### 2.1 AC electrical characteristics

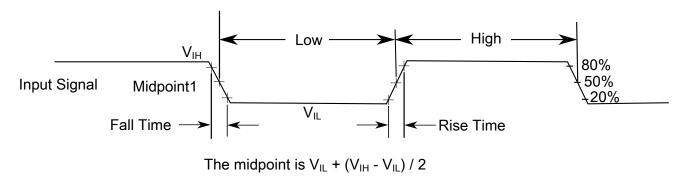

Unless otherwise specified, propagation delays are measured from the 50% to the 50% point, and rise and fall times are measured at the 20% and 80% points, as shown in the following figure.

### 2.2 Nonswitching electrical specifications

### 2.2.1 Voltage and current operating requirements

Table 1. Voltage and current operating requirements

| Symbol   | Description    | Min. | Max. | Unit | Notes |

|----------|----------------|------|------|------|-------|

| $V_{DD}$ | Supply voltage | 1.71 | 3.6  | V    |       |

Table continues on the next page...

| Symbol              | Description                                                                                                                                                        | Min.                 | Max.                 | Unit | Notes |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|------|-------|

| V <sub>DDA</sub>    | Analog supply voltage                                                                                                                                              | 1.71                 | 3.6                  | V    |       |

| $V_{DD} - V_{DDA}$  | V <sub>DD</sub> -to-V <sub>DDA</sub> differential voltage                                                                                                          | -0.1                 | 0.1                  | V    |       |

| $V_{SS} - V_{SSA}$  | V <sub>SS</sub> -to-V <sub>SSA</sub> differential voltage                                                                                                          | -0.1                 | 0.1                  | V    |       |

| V <sub>IH</sub>     | Input high voltage                                                                                                                                                 | $0.7 \times V_{DD}$  | _                    | V    |       |

|                     | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V                                                                                                                        | $0.75 \times V_{DD}$ | _                    | V    |       |

|                     | • $1.7 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}$                                                                                                       |                      |                      |      |       |

| V <sub>IL</sub>     | Input low voltage                                                                                                                                                  |                      | $0.35 \times V_{DD}$ | V    |       |

|                     | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V                                                                                                                        | _                    | $0.3 \times V_{DD}$  | V    |       |

|                     | • $1.7 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}$                                                                                                       |                      |                      |      |       |

| V <sub>HYS</sub>    | Input hysteresis                                                                                                                                                   | $0.06 \times V_{DD}$ |                      | V    |       |

| I <sub>ICIO</sub>   | Analog and I/O pin DC injection current — single pin                                                                                                               |                      |                      |      | 1     |

|                     | • $V_{IN} < V_{SS}$ -0.3V (Negative current injection)                                                                                                             | -3                   | —                    | mA   |       |

| I <sub>ICcont</sub> | Contiguous pin DC injection current —regional limit,<br>includes sum of negative injection currents or sum of<br>positive injection currents of 16 contiguous pins |                      |                      |      |       |

|                     | Negative current injection                                                                                                                                         | -25                  | _                    | mA   |       |

| V <sub>ODPU</sub>   | Open drain pullup voltage level                                                                                                                                    | V <sub>DD</sub>      | V <sub>DD</sub>      | V    | 2     |

| V <sub>RAM</sub>    | V <sub>DD</sub> voltage required to retain RAM                                                                                                                     | 1.2                  | —                    | V    |       |

Table 1. Voltage and current operating requirements (continued)

All analog and I/O pins are internally clamped to V<sub>SS</sub> through ESD protection diodes. If V<sub>IN</sub> is less than V<sub>IO\_MIN</sub> or greater than V<sub>IO\_MAX</sub>, a current limiting resistor is required. The negative DC injection current limiting resistor is calculated as R=(V<sub>IO\_MIN</sub>-V<sub>IN</sub>)/II<sub>ICIO</sub>I.

2. Open drain outputs must be pulled to VDD.

# 2.2.2 LVD and POR operating requirements

Table 2. V<sub>DD</sub> supply LVD and POR operating requirements

| Symbol             | Description                                                 | Min. | Тур. | Max. | Unit | Notes |

|--------------------|-------------------------------------------------------------|------|------|------|------|-------|

| V <sub>POR</sub>   | Falling VDD POR detect voltage                              | 0.8  | 1.1  | 1.5  | V    |       |

| $V_{LVDH}$         | Falling low-voltage detect threshold — high range (LVDV=01) | 2.48 | 2.56 | 2.64 | V    |       |

|                    | Low-voltage warning thresholds — high range                 |      |      |      |      | 1     |

| $V_{LVW1H}$        | Level 1 falling (LVWV=00)                                   | 2.62 | 2.70 | 2.78 | V    |       |

| $V_{LVW2H}$        | Level 2 falling (LVWV=01)                                   | 2.72 | 2.80 | 2.88 | V    |       |

| V <sub>LVW3H</sub> | Level 3 falling (LVWV=10)                                   | 2.82 | 2.90 | 2.98 | V    |       |

| $V_{LVW4H}$        | Level 4 falling (LVWV=11)                                   | 2.92 | 3.00 | 3.08 | V    |       |

Table continues on the next page ...

7

| Symbol | Description                     | Min. | Тур. | Max. | Unit | Notes |

|--------|---------------------------------|------|------|------|------|-------|

|        | <ul> <li>VLLS3 → RUN</li> </ul> |      |      |      |      |       |

|        |                                 | _    | _    | 75   | μs   |       |

|        | VLPS → RUN                      |      |      |      |      |       |

|        |                                 | —    | —    | 5.7  | μs   |       |

|        | STOP → RUN                      |      |      |      |      |       |

|        |                                 | —    | _    | 5.7  | μs   |       |

Table 4. Power mode transition operating behaviors (continued)

1. Normal boot (FTFA\_OPT[LPBOOT]=1)

### 2.2.5 Power consumption operating behaviors

The current parameters in the table below are derived from code executing a while(1) loop from flash, unless otherwise noted.

The IDD typical values represent the statistical mean at 25°C, and the IDD maximum values for RUN, WAIT, VLPR, and VLPW represent data collected at 125°C junction temperature unless otherwise noted. The maximum values represent characterized results equivalent to the mean plus three times the standard deviation (mean + 3 sigma).

| Symbol                | Description                                                                                                      | Min. | Тур.  | Max.     | Unit | Notes   |

|-----------------------|------------------------------------------------------------------------------------------------------------------|------|-------|----------|------|---------|

| I <sub>DDA</sub>      | Analog supply current                                                                                            | _    | _     | See note | mA   | 1       |

| I <sub>DD_HSRUN</sub> | High Speed Run mode current - all peripheral<br>clocks disabled, CoreMark benchmark code<br>executing from flash |      |       |          |      |         |

|                       | @ 1.8V                                                                                                           | —    | 18.70 | 19.37    | mA   | 2, 3, 4 |

|                       | @ 3.0V                                                                                                           | —    | 18.71 | 19.38    | mA   |         |

| I <sub>DD_HSRUN</sub> | High Speed Run mode current - all peripheral clocks disabled, code executing from flash                          |      |       |          |      |         |

|                       | @ 1.8V                                                                                                           | —    | 18.13 | 18.80    | mA   | 4       |

|                       | @ 3.0V                                                                                                           | —    | 18.19 | 18.86    | mA   |         |

| I <sub>DD_HSRUN</sub> | High Speed Run mode current — all peripheral clocks enabled, code executing from flash                           |      |       |          |      |         |

|                       | @ 1.8V                                                                                                           | —    | 22.2  | 22.87    | mA   | 5       |

|                       | @ 3.0V                                                                                                           | —    | 22.4  | 23.07    | mA   |         |

| I <sub>DD_RUN</sub>   | Run mode current in Compute operation —<br>CoreMark benchmark code executing from flash                          |      |       |          |      |         |

|                       | @ 1.8V                                                                                                           |      | 12.74 | 13.41    | mA   | 2, 3, 6 |

|                       | @ 3.0V                                                                                                           | _    | 12.82 | 13.49    | mA   |         |

Table 5. Power consumption operating behaviors

Table continues on the next page...

#### Table 5. Power consumption operating behaviors (continued)

| Symbo | Description | Min. | Тур. | Max. | Unit | Notes |

|-------|-------------|------|------|------|------|-------|

|       | @ 105°C     | —    | 6.9  | 8.25 | μA   |       |

- 1. The analog supply current is the sum of the active or disabled current for each of the analog modules on the device. See each module's specification for its supply current.

- 2. Cache on and prefetch on, low compiler optimization

- 3. CoreMark benchmark compiled using IAR 7.2 with optimization level low

- 4. 100 MHz core and system clock, 50 MHz bus clock, and 25 MHz flash clock. MCG configured for FEE mode. All peripheral clocks disabled.

- 5. 100 MHz core and system clock, 50 MHz bus clock, and 25 MHz flash clock. MCG configured for FEI mode. All peripheral clocks enabled.

- 6. 72 MHz core and system clock, 36 MHz bus clock and 24 MHz flash clock. MCG configured for FEE mode. All peripheral clocks disabled. Compute operation.

- 7. 72 MHz core and system clock, 36 MHz bus clock, and 24 MHz flash clock. MCG configured for FEI mode. All peripheral clocks disabled.

- 8. 72 MHz core and system clock, 36 MHz bus clock, and 24 MHz flash clock. MCG configured for FEI mode. All peripheral clocks enabled.

- 9. 72MHz core and system clock, 36MHz bus clock, and 24MHz flash clock. MCG configured for FEI mode. Compute operation.

- 10. 25 MHz core and system clock, 25 MHz bus clock, and 25 MHz flash clock. MCG configured for FEI mode.

- 11. 4 MHz core, system, and bus clock, and 1 MHz flash clock. MCG configured for BLPE mode. Compute operation. Code executing from flash.

- 12. 4 MHz core, system, and bus clock, and 1 MHz flash clock. MCG configured for BLPE mode. All peripheral clocks disabled. Code executing from flash.

- 13. 4 MHz core, system, and bus clock, and 1 MHz flash clock. MCG configured for BLPE mode. All peripheral clocks enabled, but peripherals are not in active operation. Code executing from flash.

- 14. 4 MHz core, system, and bus clock, and 1 MHz flash clock. MCG configured for BLPE mode. All peripheral clocks disabled.

| Symbol        | Description                                                                                                                                                   |     | ٦   | <b>Fempera</b> | ature (°C | Temperature (°C) |     |    |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|----------------|-----------|------------------|-----|----|--|--|

|               |                                                                                                                                                               | -40 | 25  | 50             | 70        | 85               | 105 |    |  |  |

| IIREFSTEN4MHz | 4 MHz internal reference clock (IRC)<br>adder. Measured by entering STOP or<br>VLPS mode with 4 MHz IRC enabled.                                              | 56  | 56  | 56             | 56        | 56               | 56  | μA |  |  |

| IREFSTEN32KHz | 32 kHz internal reference clock (IRC)<br>adder. Measured by entering STOP<br>mode with the 32 kHz IRC enabled.                                                | 52  | 52  | 52             | 52        | 52               | 52  | μA |  |  |

| IEREFSTEN4MHz | External 4 MHz crystal clock adder.<br>Measured by entering STOP or VLPS<br>mode with the crystal enabled.                                                    | 206 | 228 | 237            | 245       | 251              | 258 | uA |  |  |

| EREFSTEN32KHz | External 32 kHz crystal clock adder by<br>means of the OSC0_CR[EREFSTEN<br>and EREFSTEN] bits. Measured by<br>entering all modes with the crystal<br>enabled. |     |     |                |           |                  |     |    |  |  |

|               | VLLS1                                                                                                                                                         | 440 | 490 | 540            | 560       | 570              | 580 | nA |  |  |

|               | VLLS3                                                                                                                                                         | 440 | 490 | 540            | 560       | 570              | 580 |    |  |  |

|               | LLS                                                                                                                                                           | 490 | 490 | 540            | 560       | 570              | 680 |    |  |  |

Table 6. Low power mode peripheral adders—typical value

Table continues on the next page...

#### General

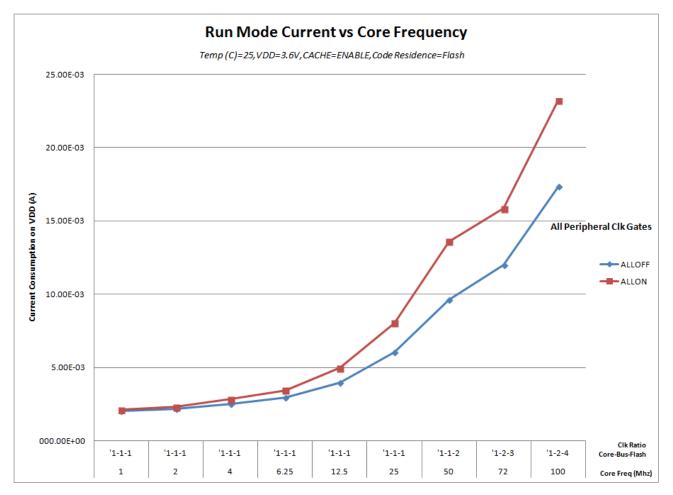

Figure 3. Run mode supply current vs. core frequency

### 2.4.1 Thermal operating requirements

Table 11. Thermal operating requirements

| Symbol         | Description              | Min. | Max. | Unit | Notes |

|----------------|--------------------------|------|------|------|-------|

| TJ             | Die junction temperature | -40  | 125  | °C   |       |

| T <sub>A</sub> | Ambient temperature      | -40  | 105  | °C   | 1     |

1. Maximum  $T_A$  can be exceeded only if the user ensures that  $T_J$  does not exceed maximum  $T_J$ . The simplest method to determine  $T_J$  is:  $T_J = T_A + R_{\Theta JA} \times$  chip power dissipation.

### 2.4.2 Thermal attributes

| Board type           | Symbol            | Descriptio<br>n                                                                 | 64 LQFP | 48 LQFP | 32 QFN | Unit | Notes |

|----------------------|-------------------|---------------------------------------------------------------------------------|---------|---------|--------|------|-------|

| Single-layer<br>(1s) | R <sub>θJA</sub>  | Thermal<br>resistance,<br>junction to<br>ambient<br>(natural<br>convection)     | 66      | 79      | 97     | °C/W | 1     |

| Four-layer<br>(2s2p) | R <sub>θJA</sub>  | Thermal<br>resistance,<br>junction to<br>ambient<br>(natural<br>convection)     | 48      | 55      | 33     | °C/W | 1     |

| Single-layer<br>(1s) | R <sub>ejma</sub> | Thermal<br>resistance,<br>junction to<br>ambient (200<br>ft./min. air<br>speed) | 54      | 67      | 81     | °C/W | 1     |

| Four-layer<br>(2s2p) | R <sub>ejma</sub> | Thermal<br>resistance,<br>junction to<br>ambient (200<br>ft./min. air<br>speed) | 41      | 49      | 28     | °C/W | 1     |

| _                    | R <sub>θJB</sub>  | Thermal<br>resistance,<br>junction to<br>board                                  | 30      | 33      | 13     | °C/W | 2     |

| _                    | R <sub>0JC</sub>  | Thermal<br>resistance,<br>junction to<br>case                                   | 17      | 23      | 2.0    | °C/W | 3     |

Table continues on the next page ...

### 3.3.1 MCG specifications

| Symbol                  | Description                                                                                                          |                                                                                       | Min.                            | Тур.      | Max.    | Unit                  | Notes |

|-------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------|-----------|---------|-----------------------|-------|

| f <sub>ints_ft</sub>    |                                                                                                                      | frequency (slow clock) —<br>t nominal VDD and 25 °C                                   |                                 | 32.768    | —       | kHz                   |       |

| $\Delta f_{ints_t}$     |                                                                                                                      | internal reference frequency voltage and temperature                                  | —                               | +0.5/-0.7 | ± 2     | %                     |       |

| $f_{ints\_t}$           | Internal reference<br>user trimmed                                                                                   | frequency (slow clock) —                                                              | 31.25                           | —         | 39.0625 | kHz                   |       |

| $\Delta_{fdco\_res\_t}$ | Resolution of trimmed average DCO output<br>frequency at fixed voltage and temperature —<br>using SCTRIM and SCFTRIM |                                                                                       | _                               | ± 0.3     | ± 0.6   | %f <sub>dco</sub>     | 1     |

| $\Delta f_{dco_t}$      |                                                                                                                      | trimmed average DCO output<br>Itage and temperature                                   | —                               | +0.5/-0.7 | ± 2     | %f <sub>dco</sub>     | 1, 2  |

| $\Delta f_{dco_t}$      |                                                                                                                      | trimmed average DCO output<br>ed voltage and temperature                              | _                               | ± 0.3     | ± 1.5   | %f <sub>dco</sub>     | 1     |

| f <sub>intf_ft</sub>    |                                                                                                                      | frequency (fast clock) —<br>t nominal VDD and 25°C                                    | _                               | 4         | —       | MHz                   |       |

| ∆f <sub>intf_ft</sub>   | (fast clock) over te                                                                                                 | on of internal reference clock<br>emperature and voltage —<br>t nominal VDD and 25 °C | _                               | +1/-2     | ± 5     | %f <sub>intf_ft</sub> |       |

| f <sub>intf_t</sub>     |                                                                                                                      | frequency (fast clock) —<br>ominal VDD and 25 °C                                      | 3                               | —         | 5       | MHz                   |       |

| f <sub>loc_low</sub>    | Loss of external c<br>RANGE = 00                                                                                     | lock minimum frequency —                                                              | (3/5) x<br>f <sub>ints_t</sub>  | —         | —       | kHz                   |       |

| f <sub>loc_high</sub>   | Loss of external c<br>RANGE = 01, 10,                                                                                | lock minimum frequency —<br>or 11                                                     | (16/5) x<br>f <sub>ints_t</sub> | —         | —       | kHz                   |       |

|                         |                                                                                                                      | FL                                                                                    | L                               |           |         |                       |       |

| f <sub>fll_ref</sub>    | FLL reference free                                                                                                   | quency range                                                                          | 31.25                           | —         | 39.0625 | kHz                   |       |

| f <sub>dco</sub>        | DCO output<br>frequency range                                                                                        | Low range (DRS=00)<br>640 × f <sub>fll_ref</sub>                                      | 20                              | 20.97     | 25      | MHz                   | 3, 4  |

|                         |                                                                                                                      | Mid range (DRS=01)<br>1280 × f <sub>fll_ref</sub>                                     | 40                              | 41.94     | 50      | MHz                   |       |

|                         |                                                                                                                      | Mid-high range (DRS=10)<br>1920 × f <sub>fll_ref</sub>                                | 60                              | 62.91     | 75      | MHz                   |       |

|                         |                                                                                                                      | High range (DRS=11)<br>2560 × $f_{fll ref}$                                           | 80                              | 83.89     | 100     | MHz                   |       |

| dco_t_DMX3<br>2         | DCO output<br>frequency                                                                                              | Low range (DRS=00)<br>732 × f <sub>fll_ref</sub>                                      |                                 | 23.99     |         | MHz                   | 5, 6  |

|                         |                                                                                                                      | Mid range (DRS=01)<br>1464 × f <sub>fll_ref</sub>                                     |                                 | 47.97     |         | MHz                   |       |

|                         | 1                                                                                                                    |                                                                                       |                                 | 1         |         |                       |       |

### Table 15. MCG specifications

Table continues on the next page...

| Symbol                   | Description               |                            | Min. | Тур.  | Max. | Unit | Notes |

|--------------------------|---------------------------|----------------------------|------|-------|------|------|-------|

|                          |                           | $2197 \times f_{fll\_ref}$ |      |       |      |      |       |

|                          |                           | High range (DRS=11)        | —    | 95.98 | —    | MHz  |       |

|                          |                           | $2929 \times f_{fll\_ref}$ |      |       |      |      |       |

| J <sub>cyc_fll</sub>     | FLL period jitter         |                            | _    | _     | _    | ps   |       |

|                          | • f <sub>VCO</sub> = 48 M |                            | _    | 180   | _    |      |       |

|                          | • f <sub>VCO</sub> = 98 M | Hz                         |      | 150   |      |      |       |

| t <sub>fll_acquire</sub> | FLL target freque         | ncy acquisition time       | —    |       | 1    | ms   | 7     |

- 1. This parameter is measured with the internal reference (slow clock) being used as a reference to the FLL (FEI clock mode).

- 2. 2.0 V <= VDD <= 3.6 V.

- 3. These typical values listed are with the slow internal reference clock (FEI) using factory trim and DMX32=0.

- The resulting system clock frequencies should not exceed their maximum specified values. The DCO frequency deviation (Δf<sub>dco\_t</sub>) over voltage and temperature should be considered.

- 5. These typical values listed are with the slow internal reference clock (FEI) using factory trim and DMX32=1.

- 6. The resulting clock frequency must not exceed the maximum specified clock frequency of the device.

- 7. This specification applies to any time the FLL reference source or reference divider is changed, trim value is changed, DMX32 bit is changed, DRS bits are changed, or changing from FLL disabled (BLPE, BLPI) to FLL enabled (FEI, FEE, FBE, FBI). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

## 3.3.2 IRC48M specifications

#### Table 16. IRC48M specifications

| Symbol                  | Description                                                                                | Min. | Тур.  | Max.  | Unit                 | Notes |

|-------------------------|--------------------------------------------------------------------------------------------|------|-------|-------|----------------------|-------|

| V <sub>DD</sub>         | Supply voltage                                                                             | 1.71 | —     | 3.6   | V                    |       |

| I <sub>DD48M</sub>      | Supply current                                                                             | —    | 400   | 500   | μA                   |       |

| f <sub>irc48m</sub>     | Internal reference frequency                                                               | —    | 48    | —     | MHz                  |       |

| Δf <sub>irc48m_hv</sub> | Total deviation of IRC48M frequency at high voltage (VDD=1.89V-3.6V) over full temperature | _    | ± 0.5 | ± 1.5 | %f <sub>irc48m</sub> |       |

| Δf <sub>irc48m_hv</sub> | Total deviation of IRC48M frequency at high voltage (VDD=1.89V-3.6V) over -40°C to 85°C    | _    | ± 0.5 | ± 1.0 | %f <sub>irc48m</sub> |       |

| ∆f <sub>irc48m_lv</sub> | Total deviation of IRC48M frequency at low voltage (VDD=1.71V-1.89V) over full temperature | _    | ± 0.5 | ± 2.0 | %f <sub>irc48m</sub> |       |

| J <sub>cyc_irc48m</sub> | Period Jitter (RMS)                                                                        | _    | 35    | 150   | ps                   |       |

| t <sub>irc48mst</sub>   | Startup time                                                                               |      | 2     | 3     | μs                   | 1     |

1. IRC48M startup time is defined as the time between clock enablement and clock availability for system use. Enable the clock by one of the following settings:

- MCG operating in an external clocking mode and MCG\_C7[OSCSEL]=10 or MCG\_C5[PLLCLKEN0]=1, or

- SIM\_SOPT2[PLLFLLSEL]=11

| Symbol                       | Description                                                                                            | Min. | Тур.            | Max. | Unit | Notes |

|------------------------------|--------------------------------------------------------------------------------------------------------|------|-----------------|------|------|-------|

| V <sub>pp</sub> <sup>5</sup> | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — low-frequency, low-power mode<br>(HGO=0)  | _    | 0.6             | _    | V    |       |

|                              | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — low-frequency, high-gain mode<br>(HGO=1)  | _    | V <sub>DD</sub> | _    | V    |       |

|                              | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — high-frequency, low-power mode<br>(HGO=0) | _    | 0.6             | _    | V    |       |

|                              | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — high-frequency, high-gain mode<br>(HGO=1) | _    | V <sub>DD</sub> | _    | V    |       |

Table 17. Oscillator DC electrical specifications (continued)

1. V<sub>DD</sub>=3.3 V, Temperature =25  $^{\circ}$ C

2. See crystal or resonator manufacturer's recommendation

3.  $C_x$  and  $C_y$  can be provided by using either integrated capacitors or external components.

4. When low-power mode is selected, R<sub>F</sub> is integrated and must not be attached externally.

5. The EXTAL and XTAL pins should only be connected to required oscillator components and must not be connected to any other device.

### 3.3.3.2 Oscillator frequency specifications

### Table 18. Oscillator frequency specifications

| Symbol                | Description                                                                                           | Min. | Тур. | Max. | Unit | Notes |

|-----------------------|-------------------------------------------------------------------------------------------------------|------|------|------|------|-------|

| f <sub>osc_lo</sub>   | Oscillator crystal or resonator frequency — low-<br>frequency mode (MCG_C2[RANGE]=00)                 | 32   | _    | 40   | kHz  |       |

| f <sub>osc_hi_1</sub> | Oscillator crystal or resonator frequency — high-<br>frequency mode (low range)<br>(MCG_C2[RANGE]=01) | 3    | _    | 8    | MHz  |       |

| f <sub>osc_hi_2</sub> | Oscillator crystal or resonator frequency — high<br>frequency mode (high range)<br>(MCG_C2[RANGE]=1x) | 8    | _    | 32   | MHz  |       |

| f <sub>ec_extal</sub> | Input clock frequency (external clock mode)                                                           |      | _    | 50   | MHz  | 1, 2  |

| t <sub>dc_extal</sub> | Input clock duty cycle (external clock mode)                                                          | 40   | 50   | 60   | %    |       |

| t <sub>cst</sub>      | Crystal startup time — 32 kHz low-frequency, low-power mode (HGO=0)                                   | —    | 750  |      | ms   | 3, 4  |

|                       | Crystal startup time — 32 kHz low-frequency,<br>high-gain mode (HGO=1)                                | —    | 250  |      | ms   |       |

|                       | Crystal startup time — 8 MHz high-frequency<br>(MCG_C2[RANGE]=01), low-power mode<br>(HGO=0)          | _    | 0.6  | _    | ms   |       |

|                       | Crystal startup time — 8 MHz high-frequency<br>(MCG_C2[RANGE]=01), high-gain mode<br>(HGO=1)          | _    | 1    | _    | ms   |       |

1. Other frequency limits may apply when external clock is being used as a reference for the FLL

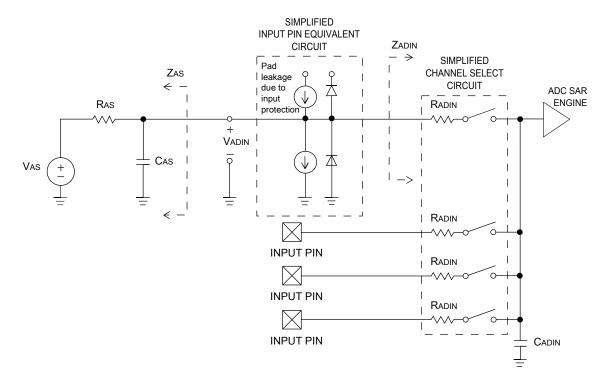

Figure 11. ADC input impedance equivalency diagram

### 3.6.1.2 16-bit ADC electrical characteristics

|                      |                        |                                      |              | DDA,              |                        | 33A/             |                         |

|----------------------|------------------------|--------------------------------------|--------------|-------------------|------------------------|------------------|-------------------------|

| Symbol               | Description            | Conditions <sup>1</sup>              | Min.         | Typ. <sup>2</sup> | Max.                   | Unit             | Notes                   |

| I <sub>DDA_ADC</sub> | Supply current         |                                      | 0.215        | —                 | 1.7                    | mA               | 3                       |

|                      | ADC asynchronous       | • ADLPC = 1, ADHSC = 0               | 1.2          | 2.4               | 3.9                    | MHz              | t <sub>ADACK</sub> = 1/ |

|                      | clock source           | • ADLPC = 1, ADHSC = 1               | 2.4          | 4.0               | 6.1                    | MHz              | f <sub>ADACK</sub>      |

| f <sub>ADACK</sub>   |                        | • ADLPC = 0, ADHSC = 0               | 3.0          | 5.2               | 7.3                    | MHz              |                         |

|                      |                        | • ADLPC = 0, ADHSC = 1               | 4.4          | 6.2               | 9.5                    | MHz              |                         |

|                      | Sample Time            | See Reference Manual chapter         | for sample t | imes              |                        |                  |                         |

| TUE                  | Total unadjusted       | 12-bit modes                         | _            | ±4                | ±6.8                   | LSB <sup>4</sup> | 5                       |

|                      | error                  | <ul> <li>&lt;12-bit modes</li> </ul> | —            | ±1.4              | ±2.1                   |                  |                         |

| DNL                  | Differential non-      | 12-bit modes                         |              | ±0.7              | -1.1 to                | LSB <sup>4</sup> | 5                       |

|                      | linearity              | <ul> <li>&lt;12-bit modes</li> </ul> | _            | ±0.2              | +1.9<br>-0.3 to<br>0.5 |                  |                         |

| INL                  | Integral non-linearity | 12-bit modes                         | —            | ±1.0              | –2.7 to<br>+1.9        | LSB <sup>4</sup> | 5                       |

| Table 24. | 16-bit ADC | characteristics | (V <sub>REFH</sub> = | $V_{DDA}$ , | V <sub>REFL</sub> = | V <sub>SSA</sub> ) |

|-----------|------------|-----------------|----------------------|-------------|---------------------|--------------------|

|-----------|------------|-----------------|----------------------|-------------|---------------------|--------------------|

Table continues on the next page ...

| Symbol              | Description                     | Conditions <sup>1</sup>                         | Min.   | Typ. <sup>2</sup>      | Max.            | Unit             | Notes                                                                  |

|---------------------|---------------------------------|-------------------------------------------------|--------|------------------------|-----------------|------------------|------------------------------------------------------------------------|

|                     |                                 | • <12-bit modes                                 | —      | ±0.5                   | -0.7 to<br>+0.5 |                  |                                                                        |

| E <sub>FS</sub>     | Full-scale error                | 12-bit modes                                    | _      | -4                     | -5.4            | LSB <sup>4</sup> | $V_{ADIN} = V_{DDA}^5$                                                 |

|                     |                                 | <li>&lt;12-bit modes</li>                       | _      | -1.4                   | -1.8            |                  |                                                                        |

| EQ                  | Quantization error              | 16-bit modes                                    | _      | -1 to 0                |                 | LSB <sup>4</sup> |                                                                        |

|                     |                                 | • ≤13-bit modes                                 | _      | -                      | ±0.5            |                  |                                                                        |

| ENOB                | Effective number of             | 16-bit differential mode                        |        |                        |                 |                  | 6                                                                      |

|                     | bits                            | • Avg = 32                                      | 12.8   | 14.5                   | _               | bits             |                                                                        |

|                     |                                 | • Avg = 4                                       | 11.9   | 13.8                   | _               | bits             |                                                                        |

|                     |                                 | 16-bit single-ended mode                        |        |                        |                 |                  |                                                                        |

|                     |                                 | • Avg = 32                                      | 12.2   | 13.9                   | _               | h. it            |                                                                        |

|                     |                                 | • Avg = 4                                       | 11.4   | 13.1                   |                 | bits             |                                                                        |

|                     |                                 | -                                               |        |                        | _               | bits             |                                                                        |

| SINAD               | Signal-to-noise plus distortion | See ENOB                                        | 6.02 × | ENOB +                 | 1.76            | dB               |                                                                        |

| THD                 | Total harmonic                  | 16-bit differential mode                        |        |                        |                 | dB               | 7                                                                      |

|                     | distortion                      | • Avg = 32                                      | —      | -94                    | _               | dB               |                                                                        |

|                     |                                 | 16-bit single-ended mode                        |        | 05                     |                 | üD               |                                                                        |

|                     |                                 | • Avg = 32                                      | _      | -85                    | _               |                  |                                                                        |

| SFDR                | Spurious free                   | 16-bit differential mode                        |        | 0.5                    |                 | dB               | 7                                                                      |

|                     | dynamic range                   | • Avg = 32                                      | 82     | 95                     |                 | ٩D               |                                                                        |

|                     |                                 | 16-bit single-ended mode                        | 78     | 90                     |                 | dB               |                                                                        |

|                     |                                 | <ul> <li>Avg = 32</li> </ul>                    | 70     | 90                     |                 |                  |                                                                        |

|                     |                                 | - Avg - 52                                      |        |                        |                 |                  |                                                                        |

| EIL                 | Input leakage error             |                                                 |        | $I_{In} \times R_{AS}$ |                 | mV               | I <sub>In</sub> = leakage<br>current                                   |

|                     |                                 |                                                 |        |                        |                 |                  | (refer to the<br>MCU's voltage<br>and current<br>operating<br>ratings) |

|                     | Temp sensor slope               | Across the full temperature range of the device | 1.55   | 1.62                   | 1.69            | mV/°C            | 8                                                                      |

| V <sub>TEMP25</sub> | Temp sensor voltage             | 25 °C                                           | 706    | 716                    | 726             | mV               | 8                                                                      |

Table 24. 16-bit ADC characteristics ( $V_{REFH} = V_{DDA}$ ,  $V_{REFL} = V_{SSA}$ ) (continued)

1. All accuracy numbers assume the ADC is calibrated with  $V_{\mathsf{REFH}}$  =  $V_{\mathsf{DDA}}$

Typical values assume V<sub>DDA</sub> = 3.0 V, Temp = 25 °C, f<sub>ADCK</sub> = 2.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

3. The ADC supply current depends on the ADC conversion clock speed, conversion rate and ADC\_CFG1[ADLPC] (low power). For lowest power operation, ADC\_CFG1[ADLPC] must be set, the ADC\_CFG2[ADHSC] bit must be clear with 1 MHz ADC conversion clock speed.

33

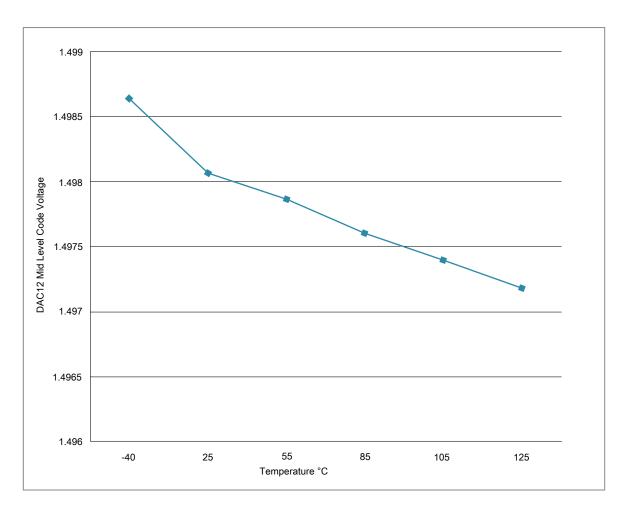

Figure 17. Offset at half scale vs. temperature

## 3.6.4 Voltage reference electrical specifications

| Table 28. | VREF full-range | operating | requirements |

|-----------|-----------------|-----------|--------------|

|-----------|-----------------|-----------|--------------|

| Symbol           | Description             | Min. Max.                                 |  | Unit | Notes |

|------------------|-------------------------|-------------------------------------------|--|------|-------|

| V <sub>DDA</sub> | Supply voltage          | 1.71 3.6                                  |  | V    |       |

| T <sub>A</sub>   | Temperature             | Operating temperature range of the device |  | °C   |       |

| CL               | Output load capacitance | 100                                       |  | nF   | 1, 2  |

1. C<sub>L</sub> must be connected to VREF\_OUT if the VREF\_OUT functionality is being used for either an internal or external reference.

The load capacitance should not exceed +/-25% of the nominal specified C<sub>L</sub> value over the operating temperature range of the device.

| Symbol                   | Description                                                                                 | Min.   | Тур.   | Max.   | Unit | Notes |

|--------------------------|---------------------------------------------------------------------------------------------|--------|--------|--------|------|-------|

| V <sub>out</sub>         | Voltage reference output with factory trim at nominal V <sub>DDA</sub> and temperature=25°C | 1.1920 | 1.1950 | 1.1980 | V    | 1     |

| V <sub>out</sub>         | Voltage reference output with user trim at nominal V <sub>DDA</sub> and temperature=25°C    | 1.1945 | 1.1950 | 1.1955 | V    | 1     |

| V <sub>step</sub>        | Voltage reference trim step                                                                 | —      | 0.5    | —      | mV   | 1     |

| V <sub>tdrift</sub>      | Temperature drift (Vmax -Vmin across the full temperature range)                            | —      | _      | 15     | mV   | 1     |

| I <sub>bg</sub>          | Bandgap only current                                                                        | _      | —      | 80     | μA   |       |

| I <sub>lp</sub>          | Low-power buffer current                                                                    | —      | —      | 360    | uA   | 1     |

| I <sub>hp</sub>          | High-power buffer current                                                                   | _      | —      | 1      | mA   | 1     |

| $\Delta V_{LOAD}$        | Load regulation                                                                             |        |        |        | μV   | 1, 2  |

|                          | • current = ± 1.0 mA                                                                        | -      | 200    | _      |      |       |

| T <sub>stup</sub>        | Buffer startup time                                                                         | _      | —      | 100    | μs   |       |

| T <sub>chop_osc_st</sub> | <sub>sc_st</sub> Internal bandgap start-up delay with chop oscillator enabled               |        | -      | 35     | ms   |       |

| V <sub>vdrift</sub>      | Voltage drift (Vmax -Vmin across the full voltage range)                                    | -      | 2      | —      | mV   | 1     |

| Table 29. | VREF full-range operating behaviors |

|-----------|-------------------------------------|

|-----------|-------------------------------------|

1. See the chip's Reference Manual for the appropriate settings of the VREF Status and Control register.

2. Load regulation voltage is the difference between the VREF\_OUT voltage with no load vs. voltage with defined load

#### Table 30. VREF limited-range operating requirements

| Symbol         | Description | Min. | Max. | Unit | Notes |

|----------------|-------------|------|------|------|-------|

| T <sub>A</sub> | Temperature | 0    | 70   | °C   |       |

#### Table 31. VREF limited-range operating behaviors

| Symbol              | Description                                                                   | Min. | Max. | Unit | Notes |

|---------------------|-------------------------------------------------------------------------------|------|------|------|-------|

| V <sub>tdrift</sub> | Temperature drift ( $V_{max} - V_{min}$ across the limited temperature range) | —    | 10   | mV   |       |

### 3.7 Timers

See General switching specifications.

### 3.8 Communication interfaces

### 3.8.1 DSPI switching specifications (limited voltage range)

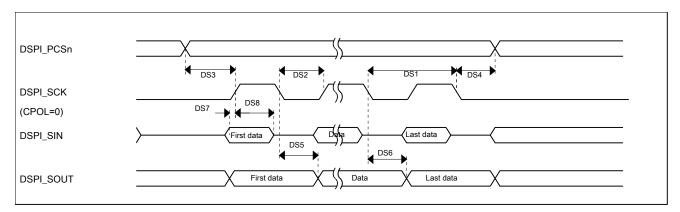

The Deserial Serial Peripheral Interface (DSPI) provides a synchronous serial bus with master and slave operations. Many of the transfer attributes are programmable. The tables below provide DSPI timing characteristics for classic SPI timing modes. Refer to the SPI chapter of the Reference Manual for information on the modified transfer formats used for communicating with slower peripheral devices.

| Num | Description                         | Min.                          | Max.                      | Unit | Notes |

|-----|-------------------------------------|-------------------------------|---------------------------|------|-------|

|     | Operating voltage                   | 2.7                           | 3.6                       | V    |       |

|     | Frequency of operation              | —                             | 25                        | MHz  |       |

| DS1 | DSPI_SCK output cycle time          | 2 x t <sub>BUS</sub>          | —                         | ns   |       |

| DS2 | DSPI_SCK output high/low time       | (t <sub>SCK</sub> /2) – 2     | (t <sub>SCK</sub> /2) + 2 | ns   |       |

| DS3 | DSPI_PCSn valid to DSPI_SCK delay   | (t <sub>BUS</sub> x 2) –<br>2 | _                         | ns   | 1     |

| DS4 | DSPI_SCK to DSPI_PCSn invalid delay | (t <sub>BUS</sub> x 2) –<br>2 | _                         | ns   | 2     |

| DS5 | DSPI_SCK to DSPI_SOUT valid         | _                             | 8.5                       | ns   |       |

| DS6 | DSPI_SCK to DSPI_SOUT invalid       | -2                            | —                         | ns   |       |

| DS7 | DSPI_SIN to DSPI_SCK input setup    | 16.2                          | —                         | ns   |       |

| DS8 | DSPI_SCK to DSPI_SIN input hold     | 0                             | —                         | ns   |       |

Table 32. Master mode DSPI timing (limited voltage range)

1. The delay is programmable in SPIx\_CTARn[PSSCK] and SPIx\_CTARn[CSSCK].

2. The delay is programmable in SPIx\_CTARn[PASC] and SPIx\_CTARn[ASC].

### Figure 18. DSPI classic SPI timing — master mode

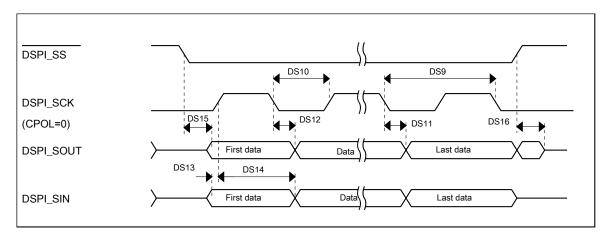

| Num  | Description                              | Min.                      | Max.                      | Unit | Notes |

|------|------------------------------------------|---------------------------|---------------------------|------|-------|

|      | Operating voltage                        | 2.7                       | 3.6                       | V    |       |

|      | Frequency of operation                   | —                         | 12.5                      | MHz  | 1     |

| DS9  | DSPI_SCK input cycle time                | 4 x t <sub>BUS</sub>      | _                         | ns   |       |

| DS10 | DSPI_SCK input high/low time             | (t <sub>SCK</sub> /2) – 2 | (t <sub>SCK</sub> /2) + 2 | ns   |       |

| DS11 | DSPI_SCK to DSPI_SOUT valid              | —                         | 21.4                      | ns   |       |

| DS12 | DSPI_SCK to DSPI_SOUT invalid            | 0                         | _                         | ns   |       |

| DS13 | DSPI_SIN to DSPI_SCK input setup         | 2.6                       | _                         | ns   |       |

| DS14 | DSPI_SCK to DSPI_SIN input hold          | 7                         | —                         | ns   |       |

| DS15 | DSPI_SS active to DSPI_SOUT driven       | —                         | 17                        | ns   |       |

| DS16 | DSPI_SS inactive to DSPI_SOUT not driven | _                         | 17                        | ns   |       |

Table 33. Slave mode DSPI timing (limited voltage range)

1. The maximum operating frequency is measured with noncontinuous CS and SCK. When DSPI is configured with continuous CS and SCK, the SPI clock must not be greater than 1/6 of the bus clock. For example, when the bus clock is 60 MHz, the SPI clock must not be greater than 10 MHz.

Figure 19. DSPI classic SPI timing — slave mode

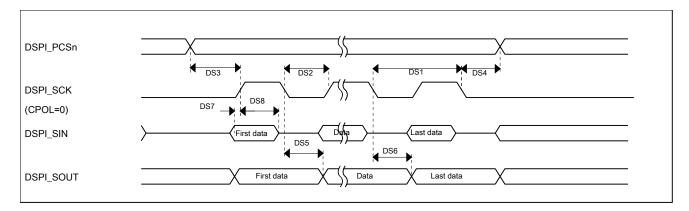

## 3.8.2 DSPI switching specifications (full voltage range)

The Deserial Serial Peripheral Interface (DSPI) provides a synchronous serial bus with master and slave operations. Many of the transfer attributes are programmable. The tables below provides DSPI timing characteristics for classic SPI timing modes. Refer to the SPI chapter of the Reference Manual for information on the modified transfer formats used for communicating with slower peripheral devices.

| Num | Description                         | Min.                          | Max.                     | Unit | Notes |

|-----|-------------------------------------|-------------------------------|--------------------------|------|-------|

|     | Operating voltage                   | 1.71                          | 3.6                      | V    | 1     |

|     | Frequency of operation              | _                             | 12.5                     | MHz  |       |

| DS1 | DSPI_SCK output cycle time          | 4 x t <sub>BUS</sub>          | _                        | ns   |       |

| DS2 | DSPI_SCK output high/low time       | (t <sub>SCK</sub> /2) - 4     | (t <sub>SCK/2)</sub> + 4 | ns   |       |

| DS3 | DSPI_PCSn valid to DSPI_SCK delay   | (t <sub>BUS</sub> x 2) –<br>4 | _                        | ns   | 2     |

| DS4 | DSPI_SCK to DSPI_PCSn invalid delay | (t <sub>BUS</sub> x 2) –<br>4 | _                        | ns   | 3     |

| DS5 | DSPI_SCK to DSPI_SOUT valid         | _                             | 10                       | ns   |       |

| DS6 | DSPI_SCK to DSPI_SOUT invalid       | -4.5                          | —                        | ns   |       |

| DS7 | DSPI_SIN to DSPI_SCK input setup    | 24.6                          | —                        | ns   |       |

| DS8 | DSPI_SCK to DSPI_SIN input hold     | 0                             | —                        | ns   |       |

1. The DSPI module can operate across the entire operating voltage for the processor, but to run across the full voltage range the maximum frequency of operation is reduced.

- 2. The delay is programmable in SPIx\_CTARn[PSSCK] and SPIx\_CTARn[CSSCK].

- 3. The delay is programmable in SPIx\_CTARn[PASC] and SPIx\_CTARn[ASC].

### Figure 20. DSPI classic SPI timing — master mode

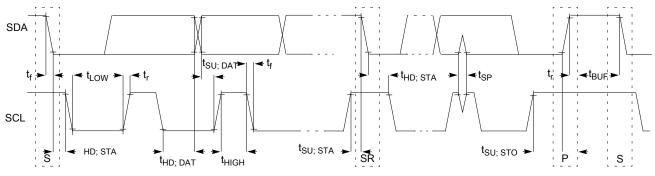

| Characteristic                                                       | Symbol                | Standa           | rd Mode           | Fast Mode                          |                  | Unit |  |

|----------------------------------------------------------------------|-----------------------|------------------|-------------------|------------------------------------|------------------|------|--|

|                                                                      |                       | Minimum          | Maximum           | Minimum                            | Maximum          |      |  |

| Data hold time for I <sup>2</sup> C bus devices                      | t <sub>HD</sub> ; DAT | 0 <sup>2</sup>   | 3.45 <sup>3</sup> | 04                                 | 0.9 <sup>2</sup> | μs   |  |

| Data set-up time                                                     | t <sub>SU</sub> ; DAT | 250 <sup>5</sup> | _                 | 100 <sup>3, 6</sup>                | —                | ns   |  |

| Rise time of SDA and SCL signals                                     | t <sub>r</sub>        | _                | 1000              | 20 +0.1C <sub>b</sub> <sup>7</sup> | 300              | ns   |  |

| Fall time of SDA and SCL signals                                     | t <sub>f</sub>        | _                | 300               | 20 +0.1C <sub>b</sub> <sup>6</sup> | 300              | ns   |  |

| Set-up time for STOP condition                                       | t <sub>SU</sub> ; STO | 4                | _                 | 0.6                                | —                | μs   |  |

| Bus free time between STOP and<br>START condition                    | t <sub>BUF</sub>      | 4.7              | —                 | 1.3                                | —                | μs   |  |

| Pulse width of spikes that must be<br>suppressed by the input filter | t <sub>SP</sub>       | N/A              | N/A               | 0                                  | 50               | ns   |  |

### Table 36. I <sup>2</sup>C timing (continued)

1. The maximum SCL Clock Frequency in Fast mode with maximum bus loading can only be achieved when using the High drive pins across the full voltage range and when using the Normal drive pins and VDD ≥ 2.7 V.

The master mode I<sup>2</sup>C deasserts ACK of an address byte simultaneously with the falling edge of SCL. If no slaves

acknowledge this address byte, then a negative hold time can result, depending on the edge rates of the SDA and SCL

lines.

3. The maximum tHD; DAT must be met only if the device does not stretch the LOW period (tLOW) of the SCL signal.

- 4. Input signal Slew = 10 ns and Output Load = 50 pF

- 5. Set-up time in slave-transmitter mode is 1 IPBus clock period, if the TX FIFO is empty.

- 6. A Fast mode I<sup>2</sup>C bus device can be used in a Standard mode I2C bus system, but the requirement t<sub>SU; DAT</sub> ≥ 250 ns must then be met. This is automatically the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, then it must output the next data bit to the SDA line t<sub>rmax</sub> + t<sub>SU; DAT</sub> = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification) before the SCL line is released.

- 7.  $C_b$  = total capacitance of the one bus line in pF.

| Characteristic                                                                               | Symbol                | Minimum                              | Maximum        | Unit |

|----------------------------------------------------------------------------------------------|-----------------------|--------------------------------------|----------------|------|

| SCL Clock Frequency                                                                          | f <sub>SCL</sub>      | 0                                    | 1 <sup>1</sup> | MHz  |

| Hold time (repeated) START condition. After this period, the first clock pulse is generated. | t <sub>HD</sub> ; STA | 0.26                                 | _              | μs   |

| LOW period of the SCL clock                                                                  | t <sub>LOW</sub>      | 0.5                                  | —              | μs   |

| HIGH period of the SCL clock                                                                 | t <sub>HIGH</sub>     | 0.26                                 | —              | μs   |

| Set-up time for a repeated START condition                                                   | t <sub>SU</sub> ; STA | 0.26                                 | _              | μs   |

| Data hold time for $I_2C$ bus devices                                                        | t <sub>HD</sub> ; DAT | 0                                    | —              | μs   |

| Data set-up time                                                                             | t <sub>SU</sub> ; DAT | 50                                   | —              | ns   |

| Rise time of SDA and SCL signals                                                             | t <sub>r</sub>        | 20 +0.1C <sub>b</sub> <sup>, 2</sup> | 120            | ns   |

| Fall time of SDA and SCL signals                                                             | t <sub>f</sub>        | 20 +0.1C <sub>b</sub> <sup>2</sup>   | 120            | ns   |

| Set-up time for STOP condition                                                               | t <sub>SU</sub> ; STO | 0.26                                 | —              | μs   |

| Bus free time between STOP and START condition                                               | t <sub>BUF</sub>      | 0.5                                  | —              | μs   |

| Pulse width of spikes that must be suppressed by the input filter                            | t <sub>SP</sub>       | 0                                    | 50             | ns   |

### Table 37. I <sup>2</sup>C 1 Mbps timing

1. The maximum SCL clock frequency of 1 Mbps can support maximum bus loading when using the High drive pins across the full voltage range.

2.  $C_b$  = total capacitance of the one bus line in pF.

46

Figure 22. Timing definition for devices on the I<sup>2</sup>C bus

## 3.8.4 UART switching specifications

See General switching specifications.

### 3.9 Kinetis Motor Suite

Kinetis Motor Suite is a bundled software solution that enables the rapid configuration of motor drive systems, and accelerates development of the final motor drive application.

Several members of the KV3x family are enabled with Kinetis motor suite. The enabled devices can be identified within the orderable part numbers in this table. For more information refer to Kinetis Motor Suite User's Guide (KMS100UG) and Kinetis Motor Suite API Reference Manual (KMS100RM).

### NOTE

To find the associated resource, go to freescale.com and perform a search using Document ID.

# 4 Dimensions

## 4.1 Obtaining package dimensions

Package dimensions are provided in package drawings.

To find a package drawing, go to freescale.com and perform a keyword search for the drawing's document number:

| Rev. No. | Date   | Substantial Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |        | <ul> <li>In "Slave mode DSPI timing (limited voltage range)" table, added footnote regarding maximum frequency of operation</li> <li>Added new section, "Recommended connections for unused analog and digital pins"</li> <li>Added Terminology and Guidelines section</li> <li>Updated Thermal Attributes value for 48LQFP</li> <li>Added KMS related information in front matter</li> <li>Added Kinetis Motor Suite section</li> <li>Added "S" in Format and Part Identification table</li> <li>Updated the Part Number Example</li> <li>Deleted Package Your Way footnote attached to 48 LQFP</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |