Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 16                                                                      |

| Program Memory Size        | 7KB (4K x 14)                                                           |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 256 x 8                                                                 |

| RAM Size                   | 368 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                               |

| Data Converters            | -                                                                       |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                          |

| Supplier Device Package    | 18-SOIC                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f87-e-so |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.2.2.1 STATUS Register

The STATUS register, shown in Register 2-1, contains the arithmetic status of the ALU, the Reset status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as '000u uluu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register because these instructions do not affect the Z, C or DC bits from the STATUS register. For other instructions not affecting any Status bits, see Section 16.0 "Instruction Set Summary".

Note: The C and DC bits operate as a borrow and digit borrow bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

#### REGISTER 2-1: STATUS: ARITHMETIC STATUS REGISTER (ADDRESS 03h, 83h, 103h, 183h)

|         | R/W-0                                                                                                                                | R/W-0                                                     | R/W-0         | R-1            | R-1           | R/W-x                     | R/W-x          | R/W-x     |  |  |  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|---------------|----------------|---------------|---------------------------|----------------|-----------|--|--|--|

|         | IRP                                                                                                                                  | RP1                                                       | RP0           | TO             | PD            | Z                         | DC             | С         |  |  |  |

|         | bit 7                                                                                                                                |                                                           |               |                |               |                           |                | bit 0     |  |  |  |

| bit 7   | 1 = Bank                                                                                                                             | ster Bank Sel<br>2, 3 (100h-1F<br>0, 1 (00h-FFt           | Fh)           | for indirect a | ddressing)    |                           |                |           |  |  |  |

| bit 6-5 | 11 <b>= Bank</b>                                                                                                                     | Register Ban<br>3 (180h-1FF                               | h)            | (used for dir  | ect address   | sing)                     |                |           |  |  |  |

|         | 01 = Bank<br>00 = Bank                                                                                                               | 2 (100h-17F<br>1 (80h-FFh)<br>0 (00h-7Fh)<br>is 128 bytes |               |                |               |                           |                |           |  |  |  |

| bit 4   | TO: Time-                                                                                                                            | out bit                                                   |               |                |               |                           |                |           |  |  |  |

|         |                                                                                                                                      | power-up, CL                                              |               | tion or SLEE   | P instruction | n                         |                |           |  |  |  |

| bit 3   | PD: Power-Down bit                                                                                                                   |                                                           |               |                |               |                           |                |           |  |  |  |

|         |                                                                                                                                      | power-up or b<br>ecution of the                           |               |                |               |                           |                |           |  |  |  |

| bit 2   | Z: Zero bit                                                                                                                          | t                                                         |               |                |               |                           |                |           |  |  |  |

|         |                                                                                                                                      | esult of an ari<br>esult of an ari                        |               |                |               |                           |                |           |  |  |  |

| bit 1   | DC: Digit                                                                                                                            | carry/borrow b                                            | oit (Addwf, A | DDLW, SUBLI    | and SUBW      | F instructio              | ns) <b>(1)</b> |           |  |  |  |

|         |                                                                                                                                      | ry-out from the<br>arry-out from t                        |               |                |               | red                       |                |           |  |  |  |

| bit 0   | C: Carry/b                                                                                                                           | orrow bit (AD                                             | DWF, ADDLW,   | SUBLW and      | SUBWF instr   | uctions) <sup>(1,2)</sup> | )              |           |  |  |  |

|         |                                                                                                                                      | ry-out from the                                           | 0             |                |               |                           |                |           |  |  |  |

|         | <b>Note 1:</b> For borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. |                                                           |               |                |               |                           |                |           |  |  |  |

|         | 2:                                                                                                                                   | For rotate (R:<br>bit of the sou                          |               | ructions, this | bit is loade  | d with eithe              | r the high or  | low-order |  |  |  |

|         | Logondy                                                                                                                              |                                                           |               |                |               |                           |                |           |  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

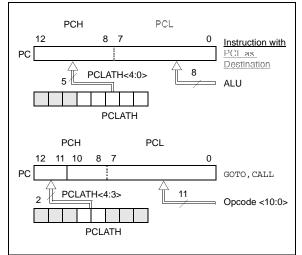

## 2.3 PCL and PCLATH

The Program Counter (PC) is 13 bits wide. The low byte comes from the PCL register which is a readable and writable register. The upper bits (PC<12:8>) are not readable but are indirectly writable through the PCLATH register. On any Reset, the upper bits of the PC will be cleared. Figure 2-4 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### FIGURE 2-4: LOADING OF PC IN DIFFERENT SITUATIONS

#### 2.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to the application note, *AN556, "Implementing a Table Read*".

## 2.3.2 STACK

The PIC16F87/88 family has an 8-level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the Stack Pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- **Note 1:** There are no status bits to indicate stack overflow or stack underflow conditions.

- 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions, or the vectoring to an interrupt address.

## 2.4 Program Memory Paging

All PIC16F87/88 devices are capable of addressing a continuous 8K word block of program memory. The CALL and GOTO instructions provide only 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction, the upper 2 bits of the address are provided by PCLATH<4:3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bits are programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is popped off the stack. Therefore, manipulation of the PCLATH<4:3> bits is not required for the RETURN instructions (which POPs the address from the stack).

| Note: | The contents of the PCLATH register are    |  |  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|--|--|

|       | unchanged after a RETURN or RETFIE         |  |  |  |  |  |  |  |  |  |

|       | instruction is executed. The user must     |  |  |  |  |  |  |  |  |  |

|       | rewrite the contents of the PCLATH regis-  |  |  |  |  |  |  |  |  |  |

|       | ter for any subsequent subroutine calls or |  |  |  |  |  |  |  |  |  |

|       | GOTO instructions.                         |  |  |  |  |  |  |  |  |  |

Example 2-1 shows the calling of a subroutine in page 1 of the program memory. This example assumes that PCLATH is saved and restored by the Interrupt Service Routine (if interrupts are used).

#### EXAMPLE 2-1: CALL OF A SUBROUTINE IN PAGE 1 FROM PAGE 0

|         | ORG 0x500<br>BCF PCLATH, 4 |                                |

|---------|----------------------------|--------------------------------|

|         | BSF PCLATH, 3              | ;Select page 1<br>;(800h-FFFh) |

|         | CALL SUB1_P1               | ;Call subroutine in            |

|         | :                          | ;page 1 (800h-FFFh)            |

|         | :                          |                                |

|         | ORG 0x900                  | ;page 1 (800h-FFFh)            |

| SUB1_P1 |                            |                                |

|         | :                          | ;called subroutine             |

|         |                            | ;page 1 (800h-FFFh)            |

|         | :                          |                                |

|         | RETURN                     | ;return to                     |

|         |                            | ;Call subroutine               |

|         |                            | ; in page 0                    |

|         |                            | ;(000h-7FFh)                   |

|         |                            |                                |

An example of the complete four-word write sequence is shown in Example 3-5. The initial address is loaded into the EEADRH:EEADR register pair; the four words of data are loaded using indirect addressing, assuming that a row erase sequence has already been performed.

#### EXAMPLE 3-5: WRITING TO FLASH PROGRAM MEMORY

; This write routine assumes the following: ; 1. The 32 words in the erase block have already been erased. ; 2. A valid starting address (the least significant bits = '00') is loaded into EEADRH:EEADR ; 3. This example is starting at 0x100, this is an application dependent setting. ; 4. The 8 bytes (4 words) of data are loaded, starting at an address in RAM called ARRAY. ; 5. This is an example only, location of data to program is application dependent. ; 6. word block is located in data memory. BANKSEL EECON1 ;prepare for WRITE procedure EECON1, EEPGD BSF ; point to program memory EECON1, WREN BSF ;allow write cycles BCF EECON1, FREE ;perform write only BANKSEL word block MOVLW .4 MOVWF word block ;prepare for 4 words to be written BANKSEL EEADRH ;Start writing at 0x100 MOVLW  $0 \times 01$ MOVWF ;load HIGH address EEADRH MOVLW 0x00 MOVWF ;load LOW address EEADR BANKSEL ARRAY MOVLW ARRAY ; initialize FSR to start of data MOVWF FSR LOOP BANKSEL EEDATA MOVF INDF, W ; indirectly load EEDATA MOVWF EEDATA INCF FSR, F ; increment data pointer MOVF INDF, W ; indirectly load EEDATH MOVWF EEDATH INCF FSR, F ; increment data pointer BANKSEL EECON1 MOVLW 0x55 ;required sequence MOVWF EECON2 MOVIW 0xAA MOVWF EECON2 BSF EECON1, WR ;set WR bit to begin write NOP ; instructions here are ignored as processor NOP BANKSEL EEADR INCF EEADR, f ;load next word address word\_block BANKSEL word block, f DECFSZ ;have 4 words been written? GOTO loop ;NO, continue with writing BANKSEL EECON1 BCF EECON1, WREN ;YES, 4 words complete, disable writes BSF INTCON,GIE ;enable interrupts

#### EXAMPLE 6-1: CHANGING THE PRESCALER ASSIGNMENT FROM WDT TO TIMER0

| CLRWDT  |             | ; Clear WDT and prescaler   |

|---------|-------------|-----------------------------|

| BANKSEL | OPTION_REG  | ; Select Bank of OPTION_REG |

| MOVLW   | b'xxxx0xxx' | ; Select TMR0, new prescale |

| MOVWF   | OPTION_REG  | ; value and clock source    |

#### TABLE 6-1: REGISTERS ASSOCIATED WITH TIMER0

| Address               | Name       | Bit 7     | Bit 6      | Bit 5  | Bit 4     | Bit 3     | Bit 2  | Bit 1  | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|-----------------------|------------|-----------|------------|--------|-----------|-----------|--------|--------|-------|----------------------|---------------------------------|

| 01h,101h              | TMR0       | Timer0 Mo | dule Regis |        | xxxx xxxx | uuuu uuuu |        |        |       |                      |                                 |

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON     | GIE       | PEIE       | TMR0IE | INTOIE    | RBIE      | TMR0IF | INT0IF | RBIF  | 0000 000x            | 0000 000u                       |

| 81h,181h              | OPTION_REG | RBPU      | INTEDG     | TOCS   | TOSE      | PSA       | PS2    | PS1    | PS0   | 1111 1111            | 1111 1111                       |

Legend: x = unknown, u = unchanged. Shaded cells are not used by Timer0.

| REGISTER 7-1: | T1CON: T                                                                                                                                                                                                | IMER1 CC                        | NTROL RE       | EGISTER (A      | DDRESS 1      | 0h)         |                |        |  |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|----------------|-----------------|---------------|-------------|----------------|--------|--|--|--|--|

|               | U-0                                                                                                                                                                                                     | R-0                             | R/W-0          | R/W-0           | R/W-0         | R/W-0       | R/W-0          | R/W-0  |  |  |  |  |

|               | _                                                                                                                                                                                                       | T1RUN                           | T1CKPS1        | T1CKPS0         | T1OSCEN       | T1SYNC      | TMR1CS         | TMR10N |  |  |  |  |

|               | bit 7                                                                                                                                                                                                   |                                 |                |                 |               |             |                | bit 0  |  |  |  |  |

| bit 7         | Unimplom                                                                                                                                                                                                | ented: Read                     |                |                 |               |             |                |        |  |  |  |  |

| bit 6         | -                                                                                                                                                                                                       |                                 |                | ic hit          |               |             |                |        |  |  |  |  |

| bit 0         | <b>T1RUN</b> : Timer1 System Clock Status bit<br>1 = System clock is derived from Timer1 oscillator<br>0 = System clock is derived from another source                                                  |                                 |                |                 |               |             |                |        |  |  |  |  |

| bit 5-4       | bit 5-4 T1CKPS<1:0>: Timer1 Input Clock Prescale Select bits                                                                                                                                            |                                 |                |                 |               |             |                |        |  |  |  |  |

|               | 11 = 1:8 Prescale value<br>10 = 1:4 Prescale value<br>01 = 1:2 Prescale value<br>00 = 1:1 Prescale value                                                                                                |                                 |                |                 |               |             |                |        |  |  |  |  |

| bit 3         | T1OSCEN:                                                                                                                                                                                                | : Timer1 Os                     | cillator Enabl | e Control bit   |               |             |                |        |  |  |  |  |

|               |                                                                                                                                                                                                         | tor is enable<br>tor is shut of | -              | tor inverter is | turned off to | eliminate p | ower drain)    | )      |  |  |  |  |

| bit 2         | T1SYNC: 1                                                                                                                                                                                               | Fimer1 Exter                    | nal Clock Inp  | out Synchroni   | zation Contr  | ol bit      |                |        |  |  |  |  |

|               | <u>TMR1CS = 1:</u><br>1 = Do not synchronize external clock input<br>0 = Synchronize external clock input<br><u>TMR1CS = 0:</u><br>This bit is ignored. Timer1 uses the internal clock when TMR1CS = 0. |                                 |                |                 |               |             |                |        |  |  |  |  |

| bit 1         | TMR1CS:                                                                                                                                                                                                 | Timer1 Cloc                     | k Source Sel   | ect bit         |               |             |                |        |  |  |  |  |

|               | <ul> <li>1 = External clock from pin RB6/AN5<sup>(1)</sup>/PGC/T1OSO/T1CKI (on the rising edge)</li> <li>0 = Internal clock (Fosc/4)</li> </ul>                                                         |                                 |                |                 |               |             |                |        |  |  |  |  |

|               | Note 1:                                                                                                                                                                                                 | Available o                     | n PIC16F88     | devices only.   |               |             |                |        |  |  |  |  |

| bit 0         | <b>TMR1ON:</b><br>1 = Enable<br>0 = Stops                                                                                                                                                               |                                 | bit            |                 |               |             |                |        |  |  |  |  |

|               | <b>Legend:</b><br>R = Reada                                                                                                                                                                             | able bit                        | W = W          | /ritable bit    | U = Unimp     | lemented b  | bit, read as ' | ·0'    |  |  |  |  |

'1' = Bit is set

'0' = Bit is cleared

-n = Value at POR

x = Bit is unknown

| RTCinit | BANKSEL | TMR1H        |                                               |

|---------|---------|--------------|-----------------------------------------------|

|         | MOVLW   | 0x80         | ; Preload TMR1 register pair                  |

|         | MOVWF   | TMR1H        | ; for 1 second overflow                       |

|         | CLRF    | TMR1L        |                                               |

|         | MOVLW   | b'00001111'  | ; Configure for external clock,               |

|         | MOVWF   | T1CON        | ; Asynchronous operation, external oscillator |

|         | CLRF    | secs         | ; Initialize timekeeping registers            |

|         | CLRF    | mins         |                                               |

|         | MOVLW   | .12          |                                               |

|         | MOVWF   | hours        |                                               |

|         | BANKSEL | PIE1         |                                               |

|         | BSF     | PIE1, TMR1IE | ; Enable Timer1 interrupt                     |

|         | RETURN  |              |                                               |

| RTCisr  | BANKSEL | TMR1H        |                                               |

|         | BSF     | TMR1H, 7     | ; Preload for 1 sec overflow                  |

|         | BCF     | PIR1, TMR1IF | ; Clear interrupt flag                        |

|         | INCF    | secs, F      | ; Increment seconds                           |

|         | MOVF    | secs, w      |                                               |

|         | SUBLW   | .60          |                                               |

|         | BTFSS   | STATUS, Z    | ; 60 seconds elapsed?                         |

|         | RETURN  |              | ; No, done                                    |

|         | CLRF    | seconds      | ; Clear seconds                               |

|         | INCF    | mins, f      | ; Increment minutes                           |

|         | MOVF    | mins, w      |                                               |

|         | SUBLW   | .60          |                                               |

|         | BTFSS   | STATUS, Z    | ; 60 seconds elapsed?                         |

|         | RETURN  |              | ; No, done                                    |

|         | CLRF    | mins         | ; Clear minutes                               |

|         | INCF    | hours, f     | ; Increment hours                             |

|         | MOVF    | hours, w     |                                               |

|         | SUBLW   | .24          |                                               |

|         | BTFSS   | STATUS, Z    | ; 24 hours elapsed?                           |

|         | RETURN  |              | ; No, done                                    |

|         | CLRF    | hours        | ; Clear hours                                 |

|         | RETURN  |              | ; Done                                        |

#### EXAMPLE 7-3: IMPLEMENTING A REAL-TIME CLOCK USING A TIMER1 INTERRUPT SERVICE

### TABLE 7-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Address                 | Name   | Bit 7   | Bit 6               | Bit 5        | Bit 4         | Bit 3          | Bit 2       | Bit 1     | Bit 0  | Value on<br>POR, BOR |      | all c | e on<br>other<br>sets |

|-------------------------|--------|---------|---------------------|--------------|---------------|----------------|-------------|-----------|--------|----------------------|------|-------|-----------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON | GIE     | PEIE                | TMR0IE       | INTOIE        | RBIE           | TMR0IF      | INTOIF    | RBIF   | 0000                 | 000x | 0000  | 000u                  |

| 0Ch                     | PIR1   | —       | ADIF <sup>(1)</sup> | RCIF         | TXIF          | SSPIF          | CCP1IF      | TMR2IF    | TMR1IF | -000                 | 0000 | -000  | 0000                  |

| 8Ch                     | PIE1   | —       | ADIE <sup>(1)</sup> | RCIE         | TXIE          | SSPIE          | CCP1IE      | TMR2IE    | TMR1IE | -000                 | 0000 | -000  | 0000                  |

| 0Eh                     | TMR1L  | Holding | g Registe           | r for the Le | ast Significa | ant Byte of th | ne 16-bit T | MR1 Regis | ster   | xxxx                 | xxxx | uuuu  | uuuu                  |

| 0Fh                     | TMR1H  | Holding | g Registe           | r for the Mo | st Significa  | nt Byte of th  | e 16-bit TN | /R1 Regis | ter    | xxxx                 | xxxx | uuuu  | uuuu                  |

| 10h                     | T1CON  |         | T1RUN               | T1CKPS1      | T1CKPS0       | T1OSCEN        | T1SYNC      | TMR1CS    | TMR10N | -000                 | 0000 | -uuu  | uuuu                  |

Legend:x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.Note1:This bit is only implemented on the PIC16F88. The bit will read '0' on the PIC16F87.

The maximum PWM resolution (bits) for a given PWM frequency is given by the following formula.

#### **EQUATION 9-3:**

Resolution =

$$\frac{\log(\frac{\text{FOSC}}{\text{FPWM}})}{\log(2)}$$

Note: If the PWM duty cycle value is longer than the PWM period, the CCP1 pin will not be cleared.

#### 9.3.3 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- Make the CCP1 pin an output by clearing the TRISB<x> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

#### TABLE 9-3:EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 20 MHz

| PWM Frequency              | 1.22 kHz | 4.88 kHz | 4.88 kHz 19.53 kHz |      | 156.3 kHz | 208.3 kHz |

|----------------------------|----------|----------|--------------------|------|-----------|-----------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1                  | 1    | 1         | 1         |

| PR2 Value                  | 0xFF     | 0xFF     | 0xFF               | 0x3F | 0x1F      | 0x17      |

| Maximum Resolution (bits)  | 10       | 10       | 10                 | 8    | 7         | 6.6       |

#### TABLE 9-4: REGISTERS ASSOCIATED WITH PWM AND TIMER2

bits

| Address              | Name    | Bit 7   | Bit 6               | Bit 5         | Bit 4      | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value<br>POR, |      | all o | e on<br>ther<br>sets |

|----------------------|---------|---------|---------------------|---------------|------------|---------|--------|---------|---------|---------------|------|-------|----------------------|

| 0Bh,8Bh<br>10Bh,18Bh | INTCON  | GIE     | PEIE                | TMR0IE        | INTOIE     | RBIE    | TMR0IF | INTOIF  | RBIF    | 0000          | 000x | 0000  | 000u                 |

| 0Ch                  | PIR1    | _       | ADIF <sup>(1)</sup> | RCIF          | TXIF       | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | -000          | 0000 | -000  | 0000                 |

| 8Ch                  | PIE1    | _       | ADIE <sup>(1)</sup> | RCIE          | TXIE       | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | -000          | 0000 | -000  | 0000                 |

| 86h                  | TRISB   | PORT    | B Data Direc        | ction Registe | er         |         |        |         |         | 1111          | 1111 | 1111  | 1111                 |

| 11h                  | TMR2    | Timer2  | Module Reg          | gister        |            |         |        |         |         | 0000          | 0000 | 0000  | 0000                 |

| 92h                  | PR2     | Timer2  | Period Regi         | ster          |            |         |        |         |         | 1111          | 1111 | 1111  | 1111                 |

| 12h                  | T2CON   |         | TOUTPS3             | TOUTPS2       | TOUTPS1    | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000          | 0000 | -000  | 0000                 |

| 15h                  | CCPR1L  | Captur  | e/Compare/I         | PWM Regist    | er 1 (LSB) |         |        |         |         | xxxx          | xxxx | uuuu  | uuuu                 |

| 16h                  | CCPR1H  | Capture | e/Compare/F         | PWM Registe   | er 1 (MSB) |         |        |         |         | xxxx          | xxxx | uuuu  | uuuu                 |

| 17h                  | CCP1CON | _       | _                   | CCP1X         | CCP1Y      | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0  | 00            | 0000 | 00    | 0000                 |

$\label{eq:logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical$

**Note 1:** This bit is only implemented on the PIC16F88. The bit will read '0' on the PIC16F87.

<sup>5.</sup> Configure the CCP1 module for PWM operation.

Note: The TRISB bit (0 or 3) is dependant upon the setting of configuration bit 12 (CCPMX).

| TABLE       | E 11-3: | BAUD       | RATES I                     | FOR AS  | OR ASYNCHRONOUS MODE (BRGH = 0) |                             |         |            |                             |  |  |

|-------------|---------|------------|-----------------------------|---------|---------------------------------|-----------------------------|---------|------------|-----------------------------|--|--|

| BAUD        | F       | osc = 20 M | lHz                         | F       | osc = 16 M                      | IHz                         | F       | osc = 10 N | /Hz                         |  |  |

| RATE<br>(K) | KBAUD   | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD   | %<br>ERROR                      | SPBRG<br>value<br>(decimal) | KBAUD   | %<br>ERROR | SPBRG<br>value<br>(decimal) |  |  |

| 0.3         |         | —          | —                           | —       | —                               | —                           | —       |            | —                           |  |  |

| 1.2         | 1.221   | +1.75      | 255                         | 1.202   | +0.17                           | 207                         | 1.202   | +0.17      | 129                         |  |  |

| 2.4         | 2.404   | +0.17      | 129                         | 2.404   | +0.17                           | 103                         | 2.404   | +0.17      | 64                          |  |  |

| 9.6         | 9.766   | +1.73      | 31                          | 9.615   | +0.16                           | 25                          | 9.766   | +1.73      | 15                          |  |  |

| 19.2        | 19.531  | + 1.72     | 15                          | 19.231  | +0.16                           | 12                          | 19.531  | +1.72      | 7                           |  |  |

| 28.8        | 31.250  | +8.51      | 9                           | 27.778  | -3.55                           | 8                           | 31.250  | +8.51      | 4                           |  |  |

| 33.6        | 34.722  | +3.34      | 8                           | 35.714  | +6.29                           | 6                           | 31.250  | -6.99      | 4                           |  |  |

| 57.6        | 62.500  | +8.51      | 4                           | 62.500  | +8.51                           | 3                           | 52.083  | -9.58      | 2                           |  |  |

| HIGH        | 1.221   | _          | 255                         | 0.977   | _                               | 255                         | 0.610   | —          | 255                         |  |  |

| LOW         | 312.500 | _          | 0                           | 250.000 | _                               | 0                           | 156.250 | _          | 0                           |  |  |

| DAUD                | l      | Fosc = 4 M | Hz                          | Fosc = 3.6864 MHz |            |                             |  |  |

|---------------------|--------|------------|-----------------------------|-------------------|------------|-----------------------------|--|--|

| BAUD<br>RATE<br>(K) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD             | %<br>ERROR | SPBRG<br>value<br>(decimal) |  |  |

| 0.3                 | 0.300  | 0          | 207                         | 0.3               | 0          | 191                         |  |  |

| 1.2                 | 1.202  | +0.17      | 51                          | 1.2               | 0          | 47                          |  |  |

| 2.4                 | 2.404  | +0.17      | 25                          | 2.4               | 0          | 23                          |  |  |

| 9.6                 | 8.929  | +6.99      | 6                           | 9.6               | 0          | 5                           |  |  |

| 19.2                | 20.833 | +8.51      | 2                           | 19.2              | 0          | 2                           |  |  |

| 28.8                | 31.250 | +8.51      | 1                           | 28.8              | 0          | 1                           |  |  |

| 33.6                | —      | _          | _                           | _                 | _          | _                           |  |  |

| 57.6                | 62.500 | +8.51      | 0                           | 57.6              | 0          | 0                           |  |  |

| HIGH                | 0.244  | _          | 255                         | 0.225             | _          | 255                         |  |  |

| LOW                 | 62.500 | _          | 0                           | 57.6              | _          | 0                           |  |  |

#### TABLE 11-4: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 1)

| BAUD        | Fosc = 20 MHz |            |                             | F        | osc = 16 M | Hz                          | Fosc = 10 MHz |            |                             |  |

|-------------|---------------|------------|-----------------------------|----------|------------|-----------------------------|---------------|------------|-----------------------------|--|

| RATE<br>(K) | KBAUD         | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD    | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD         | %<br>ERROR | SPBRG<br>value<br>(decimal) |  |

| 0.3         | —             | _          | _                           | —        | _          | _                           |               | _          | _                           |  |

| 1.2         | —             | _          | _                           | _        | _          | _                           | —             | _          | _                           |  |

| 2.4         | —             | —          | _                           | —        | _          | _                           | 2.441         | +1.71      | 255                         |  |

| 9.6         | 9.615         | +0.16      | 129                         | 9.615    | +0.16      | 103                         | 9.615         | +0.16      | 64                          |  |

| 19.2        | 19.231        | +0.16      | 64                          | 19.231   | +0.16      | 51                          | 19.531        | +1.72      | 31                          |  |

| 28.8        | 29.070        | +0.94      | 42                          | 29.412   | +2.13      | 33                          | 28.409        | -1.36      | 21                          |  |

| 33.6        | 33.784        | +0.55      | 36                          | 33.333   | -0.79      | 29                          | 32.895        | -2.10      | 18                          |  |

| 57.6        | 59.524        | +3.34      | 20                          | 58.824   | +2.13      | 16                          | 56.818        | -1.36      | 10                          |  |

| HIGH        | 4.883         | _          | 255                         | 3.906    | _          | 255                         | 2.441         | _          | 255                         |  |

| LOW         | 1250.000      | _          | 0                           | 1000.000 | _          | 0                           | 625.000       | _          | 0                           |  |

| BAUD        | F       | osc = 4 MH | łz                          | Fosc = 3.6864 MHz |            |                             |  |  |

|-------------|---------|------------|-----------------------------|-------------------|------------|-----------------------------|--|--|

| RATE<br>(K) | KBAUD   | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD             | %<br>ERROR | SPBRG<br>value<br>(decimal) |  |  |

| 0.3         |         | _          | _                           |                   | _          | _                           |  |  |

| 1.2         | 1.202   | +0.17      | 207                         | 1.2               | 0          | 191                         |  |  |

| 2.4         | 2.404   | +0.17      | 103                         | 2.4               | 0          | 95                          |  |  |

| 9.6         | 9.615   | +0.16      | 25                          | 9.6               | 0          | 23                          |  |  |

| 19.2        | 19.231  | +0.16      | 12                          | 19.2              | 0          | 11                          |  |  |

| 28.8        | 27.798  | -3.55      | 8                           | 28.8              | 0          | 7                           |  |  |

| 33.6        | 35.714  | +6.29      | 6                           | 32.9              | -2.04      | 6                           |  |  |

| 57.6        | 62.500  | +8.51      | 3                           | 57.6              | 0          | 3                           |  |  |

| HIGH        | 0.977   | _          | 255                         | 0.9               | _          | 255                         |  |  |

| LOW         | 250.000 | _          | 0                           | 230.4             | _          | 0                           |  |  |

When setting up an asynchronous transmission, follow these steps:

- Initialize the SPBRG register for the appropriate baud rate. If a high-speed baud rate is desired, set bit BRGH (Section 11.1 "AUSART Baud Rate Generator (BRG)").

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set transmit bit TX9.

- 5. Enable the transmission by setting bit TXEN which will also set bit TXIF.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Load data to the TXREG register (starts transmission).

- 8. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

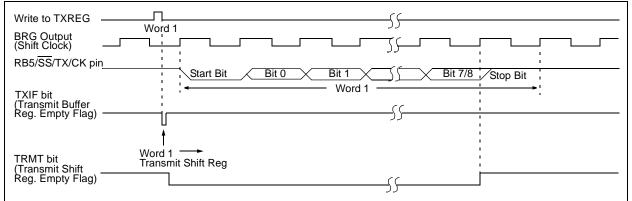

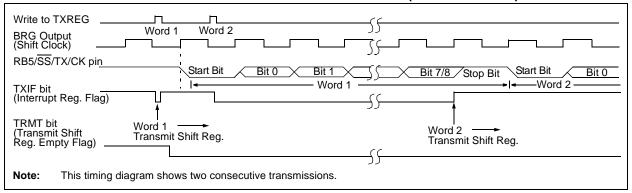

#### FIGURE 11-2: ASYNCHRONOUS MASTER TRANSMISSION

#### FIGURE 11-3: ASYNCHRONOUS MASTER TRANSMISSION (BACK TO BACK)

#### TABLE 11-7: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Address                | Name                                                                             | Bit 7  | Bit 6               | Bit 5     | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|------------------------|----------------------------------------------------------------------------------|--------|---------------------|-----------|--------|-------|--------|--------|--------|-----------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON                                                                           | GIE    | PEIE                | TMR0IE    | INT0IE | RBIE  | TMR0IF | INTOIF | RBIF   | 0000 000x             | 0000 000u                       |

| 0Ch                    | PIR1                                                                             | _      | ADIF <sup>(1)</sup> | RCIF      | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | -000 0000             | -000 0000                       |

| 18h                    | RCSTA                                                                            | SPEN   | RX9                 | SREN      | CREN   | ADDEN | FERR   | OERR   | RX9D   | 0000 000x             | 0000 000x                       |

| 19h                    | TXREG                                                                            | AUSART | Fransmit I          | Data Regi | ster   |       |        |        |        | 0000 0000             | 0000 0000                       |

| 8Ch                    | PIE1                                                                             | _      | ADIE <sup>(1)</sup> | RCIE      | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE | -000 0000             | -000 0000                       |

| 98h                    | TXSTA                                                                            | CSRC   | TX9                 | TXEN      | SYNC   |       | BRGH   | TRMT   | TX9D   | 0000 -010             | 0000 -010                       |

| 99h                    | SPBRG Baud Rate Generator Register                                               |        |                     |           |        |       |        |        |        | 0000 0000             | 0000 0000                       |

| Lonondi                | - unknown - unimplemented leasting read on (c). Chaded calls are not used for an |        |                     |           |        |       |        |        |        |                       |                                 |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous transmission.

Note 1: This bit is only implemented on the PIC16F88. The bit will read '0' on the PIC16F87.

### 11.3 AUSART Synchronous Master Mode

In Synchronous Master mode, the data is transmitted in a half-duplex manner (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit SYNC (TXSTA<4>). In addition, enable bit SPEN (RCSTA<7>) is set in order to configure the RB5/SS/TX/CK and RB2/SDO/RX/DT I/O pins to CK (clock) and DT (data) lines, respectively. The Master mode indicates that the processor transmits the master clock on the CK line. The Master mode is entered by setting bit CSRC (TXSTA<7>).

#### 11.3.1 AUSART SYNCHRONOUS MASTER TRANSMISSION

The AUSART transmitter block diagram is shown in Figure 11-6. The heart of the transmitter is the Transmit (Serial) Shift Register (TSR). The Shift register obtains its data from the Read/Write Transmit Buffer register, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TCYCLE), the TXREG is empty and interrupt bit TXIF (PIR1<4>) is set. The interrupt can be enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set, regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit, TRMT (TXSTA<1>), shows the status of the TSR register. TRMT is a read-only bit which is set when the TSR is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory, so it is not available to the user.

Transmission is enabled by setting enable bit TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data. The first data bit will be shifted out on the next available rising edge of the clock on the CK line. Data out is stable around the falling edge of the synchronous clock (Figure 11-9). The transmission can also be started by first loading the TXREG register and then setting bit TXEN (Figure 11-10). This is advantageous when slow baud rates are selected, since the BRG is kept in Reset when bits TXEN, CREN and SREN are clear. Setting enable bit TXEN will start the BRG, creating a shift clock immediately. Normally, when transmission is first started, the TSR register is empty, so a transfer to the TXREG register will result in an immediate transfer to TSR, resulting in an empty TXREG. Back-to-back transfers are possible.

Clearing enable bit TXEN during a transmission will cause the transmission to be aborted and will reset the transmitter. The DT and CK pins will revert to highimpedance. If either bit CREN or bit SREN is set during a transmission, the transmission is aborted and the DT pin reverts to a high-impedance state (for a reception). The CK pin will remain an output if bit CSRC is set (internal clock). The transmitter logic, however, is not reset, although it is disconnected from the pins. In order to reset the transmitter, the user has to clear bit TXEN. If bit SREN is set (to interrupt an on-going transmission and receive a single word), then after the single word is received, bit SREN will be cleared and the serial port will revert back to transmitting, since bit TXEN is still set. The DT line will immediately switch from High-Impedance Receive mode to transmit and start driving. To avoid this, bit TXEN should be cleared.

In order to select 9-bit transmission, the TX9 (TXSTA<6>) bit should be set and the ninth bit should be written to bit TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG can result in an immediate transfer of the data to the TSR register (if the TSR is empty). If the TSR was empty and the TXREG was written before writing the "new" TX9D, the "present" value of bit TX9D is loaded.

Steps to follow when setting up a synchronous master transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 11.1 "AUSART Baud Rate Generator (BRG)").

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. If interrupts are desired, set enable bit TXIE.

- 4. If 9-bit transmission is desired, set bit TX9.

- 5. Enable the transmission by setting bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

- 8. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

## 13.0 COMPARATOR MODULE

The comparator module contains two analog comparators. The inputs to the comparators are multiplexed with I/O port pins RA0 through RA3, while the outputs are multiplexed to pins RA3 and RA4. The on-chip Voltage Reference (Section 14.0 "Comparator Voltage Reference Module") can also be an input to the comparators.

The CMCON register (Register 13-1) controls the comparator input and output multiplexors. A block diagram of the various comparator configurations is shown in Figure 13-1.

| -       | R-0                                                                           | R-0                                      | R/W-0      | R/W-0      | R/W-0      | 、<br>R/W-1 | R/W-1         | ,<br>R/W-1 |  |  |  |

|---------|-------------------------------------------------------------------------------|------------------------------------------|------------|------------|------------|------------|---------------|------------|--|--|--|

|         | C2OUT                                                                         | C10UT                                    | C2INV      | C1INV      | CIS        | CM2        | CM1           | CM0        |  |  |  |

|         | bit 7                                                                         |                                          |            |            | ·          |            |               | bit 0      |  |  |  |

| bit 7   | <b>C2OUT:</b> Comparator 2 Output bit<br>When C2INV = 0:                      |                                          |            |            |            |            |               |            |  |  |  |

|         | 1 = C2 VIN + 3 $0 = C2 VIN + 4$                                               | < C2 VIN-                                |            |            |            |            |               |            |  |  |  |

|         | <u>When C2INV</u><br>1 = C2 VIN+<br>0 = C2 VIN+ :                             | < C2 VIN-                                |            |            |            |            |               |            |  |  |  |

| bit 6   | C1OUT: Com                                                                    | nparator 1 C                             | Output bit |            |            |            |               |            |  |  |  |

|         | <u>When C1INV</u><br>1 = C1 VIN+ :<br>0 = C1 VIN+ :                           | > C1 VIN-                                |            |            |            |            |               |            |  |  |  |

|         | <u>When C1INV</u><br>1 = C1 VIN+<br>0 = C1 VIN+                               | <u>′ = 1:</u><br>< C1 Vin-               |            |            |            |            |               |            |  |  |  |

| bit 5   |                                                                               | C2INV: Comparator 2 Output Inversion bit |            |            |            |            |               |            |  |  |  |

|         | 1 = C2 outpu<br>0 = C2 outpu                                                  | t inverted                               | -          |            |            |            |               |            |  |  |  |

| bit 4   | C1INV: Comparator 1 Output Inversion bit                                      |                                          |            |            |            |            |               |            |  |  |  |

|         | 1 = C1 outpu<br>0 = C1 outpu                                                  |                                          | ed         |            |            |            |               |            |  |  |  |

| bit 3   | CIS: Compar<br><u>When CM2:C</u><br>1 = C1 VIN- c<br>0 = C1 VIN- c            | CMO = 001:                               | RA3        |            |            |            |               |            |  |  |  |

|         | When CM2:CM0 = 010:<br>1 = C1 VIN- connects to RA3<br>C2 VIN- connects to RA2 |                                          |            |            |            |            |               |            |  |  |  |

|         | 0 = C1 VIN- c<br>C2 VIN- c                                                    | connects to<br>connects to l             | -          |            |            |            |               |            |  |  |  |

| bit 2-0 | CM<2:0>: Co                                                                   |                                          |            |            |            |            |               |            |  |  |  |

|         | Legend:                                                                       |                                          |            |            |            |            |               |            |  |  |  |

|         | R = Readabl                                                                   | e bit                                    | W = Wr     | itable bit | U = Unimpl | emented b  | it, read as ' | 0'         |  |  |  |

|         |                                                                               |                                          |            |            |            |            |               |            |  |  |  |

'1' = Bit is set

'0' = Bit is cleared

-n = Value at POR

x = Bit is unknown

## 13.2 Comparator Operation

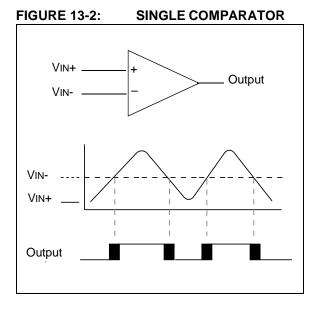

A single comparator is shown in Figure 13-2, along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input VIN-, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input VIN-, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 13-2 represent the uncertainty due to input offsets and response time.

### 13.3 Comparator Reference

An external or internal reference signal may be used depending on the comparator operating mode. The analog signal present at VIN- is compared to the signal at VIN+ and the digital output of the comparator is adjusted accordingly (Figure 13-2).

#### 13.3.1 EXTERNAL REFERENCE SIGNAL

When external voltage references are used, the comparator module can be configured to have the comparators operate from the same, or different reference sources. However, threshold detector applications may require the same reference. The reference signal must be between Vss and VDD and can be applied to either pin of the comparator(s).

#### 13.3.2 INTERNAL REFERENCE SIGNAL

The comparator module also allows the selection of an internally generated voltage reference for the comparators. Section 14.0 "Comparator Voltage Reference Module" contains a detailed description of the Comparator Voltage Reference module that provides this signal. The internal reference signal is used when comparators are in mode CM<2:0> = 010 (Figure 13-1). In this mode, the internal voltage reference is applied to the VIN+ pin of both comparators.

## 13.4 Comparator Response Time

Response time is the minimum time, after selecting a new reference voltage or input source, before the comparator output has a valid level. If the internal reference is changed, the maximum delay of the internal voltage reference must be considered when using the comparator outputs. Otherwise, the maximum delay of the comparators should be used (Section 18.0 "Electrical Characteristics").

## 13.5 Comparator Outputs

The comparator outputs are read through the CMCON register. These bits are read-only. The comparator outputs may also be directly output to the RA3 and RA4 I/O pins. When enabled, multiplexors in the output path of the RA3 and RA4 pins will switch and the output of each pin will be the unsynchronized output of the comparator. The uncertainty of each of the comparators is related to the input offset voltage and the response time given in the specifications. Figure 13-3 shows the comparator output block diagram.

The TRISA bits will still function as an output enable/ disable for the RA3 and RA4 pins while in this mode.

The polarity of the comparator outputs can be changed using the C2INV and C1INV bits (CMCON<5:4>).

- Note 1: When reading the Port register, all pins configured as analog inputs will read as '0'. Pins configured as digital inputs will convert an analog input, according to the Schmitt Trigger input specification.

- 2: Analog levels, on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

| <b>Operating Conditions:</b> 3.0V < VDD < 5.5V, -40°C < TA < +85°C, unless otherwise stated |        |                                            |     |      |            |          |                             |  |  |  |

|---------------------------------------------------------------------------------------------|--------|--------------------------------------------|-----|------|------------|----------|-----------------------------|--|--|--|

| Param<br>No.                                                                                | Sym    | Characteristics                            | Min | Тур  | Мах        | Units    | Comments                    |  |  |  |

| D300                                                                                        | VIOFF  | Input Offset Voltage                       |     | ±5.0 | ±10        | mV       |                             |  |  |  |

| D301                                                                                        | VICM   | Input Common Mode Voltage*                 | 0   |      | Vdd - 1.5  | V        |                             |  |  |  |

| D302                                                                                        | CMRR   | Common Mode Rejection Ratio*               | 55  | —    | —          | dB       |                             |  |  |  |

| 300<br>300A                                                                                 | TRESP  | Response Time <sup>(1)*</sup>              | _   | 150  | 400<br>600 | ns<br>ns | PIC16F87/88<br>PIC16LF87/88 |  |  |  |

| 301                                                                                         | TMC20V | Comparator Mode Change to<br>Output Valid* | _   | —    | 10         | μS       |                             |  |  |  |

#### TABLE 18-1: COMPARATOR SPECIFICATIONS

\* These parameters are characterized but not tested.

**Note 1:** Response time measured with one comparator input at (VDD – 1.5)/2 while the other input transitions from Vss to VDD.

#### TABLE 18-2: VOLTAGE REFERENCE SPECIFICATIONS

| Operating   | <b>Operating Conditions:</b> 3.0V < VDD < 5.5V, -40°C < TA < +85°C, unless otherwise stated |                               |        |     |        |       |                       |  |  |  |  |

|-------------|---------------------------------------------------------------------------------------------|-------------------------------|--------|-----|--------|-------|-----------------------|--|--|--|--|

| Spec<br>No. | Sym                                                                                         | Characteristics               | Min    | Тур | Max    | Units | Comments              |  |  |  |  |

| D310        | VRES                                                                                        | Resolution                    | Vdd/24 |     | VDD/32 | LSb   |                       |  |  |  |  |

| D311        | VRAA                                                                                        | Absolute Accuracy             | —      | -   | 1/2    | LSb   | Low Range (CVRR = 1)  |  |  |  |  |

|             |                                                                                             |                               |        | —   | 1/2    | LSb   | High Range (CVRR = 0) |  |  |  |  |

| D312        | VRur                                                                                        | Unit Resistor Value (R)*      | —      | 2k  | —      | Ω     |                       |  |  |  |  |

| 310         | TSET                                                                                        | Settling Time <sup>(1)*</sup> | —      | —   | 10     | μS    |                       |  |  |  |  |

\* These parameters are characterized but not tested.

**Note 1:** Settling time measured while CVRR = 1 and CVR<3:0> transitions from '0000' to '1111'.

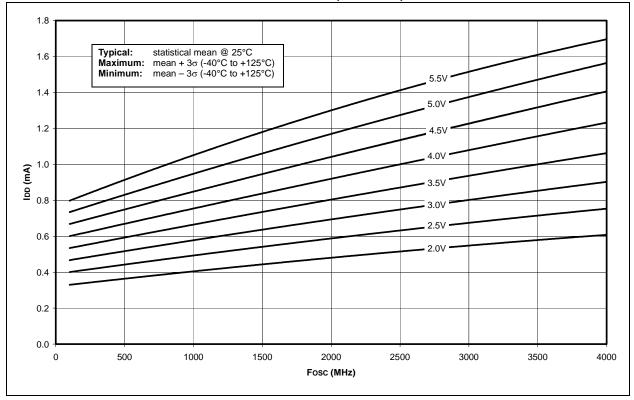

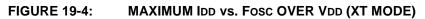

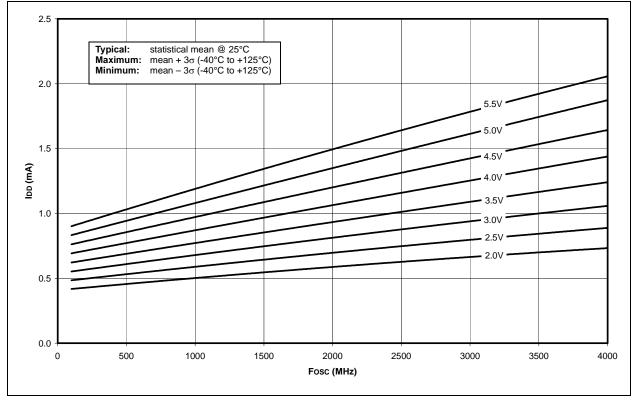

FIGURE 19-5: TYPICAL IDD vs. Fosc OVER VDD (LP MODE)

FIGURE 19-17: IPD A/D, -40°C TO +125°C, SLEEP MODE, A/D ENABLED (NOT CONVERTING)

© 2002-2013 Microchip Technology Inc.

# THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com, click on Customer Change Notification and follow the registration instructions.

## **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://support.microchip.com