Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 16                                                                      |

| Program Memory Size        | 7KB (4K x 14)                                                           |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 256 x 8                                                                 |

| RAM Size                   | 368 x 8                                                                 |

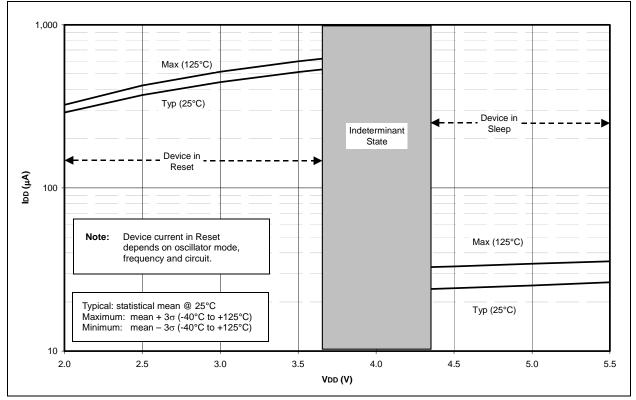

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                               |

| Data Converters            | -                                                                       |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

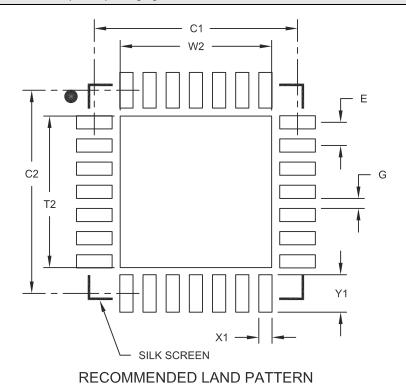

| Mounting Type              | Surface Mount                                                           |

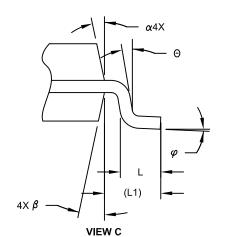

| Package / Case             | 28-VQFN Exposed Pad                                                     |

| Supplier Device Package    | 28-QFN (6x6)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f87-i-ml |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 2-1. The Special Function Registers can be classified into two sets: core (CPU) and peripheral. Those registers associated with the core functions are described in detail in this section. Those related to the operation of the peripheral features are described in detail in the peripheral feature section.

| Address              | Name                  | Bit 7       | Bit 6               | Bit 5         | Bit 4           | Bit 3                          | Bit 2           | Bit 1        | Bit 0    | Value on:<br>POR, BOR  | Details<br>on<br>page |

|----------------------|-----------------------|-------------|---------------------|---------------|-----------------|--------------------------------|-----------------|--------------|----------|------------------------|-----------------------|

| Bank 0               | •                     | •           |                     | •             | •               | •                              | •               | •            |          | •                      |                       |

| 00h <sup>(2)</sup>   | INDF                  | Addressing  | g this locatio      | n uses conte  | ents of FSR to  | address data                   | memory (not     | a physical r | egister) | 0000 0000              | 26, 135               |

| 01h                  | TMR0                  | Timer0 Mc   | dule Registe        | ər            |                 |                                |                 |              |          | XXXX XXXX              | 69                    |

| 02h <sup>(2)</sup>   | PCL                   | Program C   | Counter (PC)        | Least Signif  | icant Byte      |                                |                 |              |          | 0000 0000              |                       |

| 03h <sup>(2)</sup>   | STATUS                | IRP         | RP1                 | RP0           | TO              | PD                             | Z               | DC           | С        | 0001 1xxx              | 17                    |

| 04h <sup>(2)</sup>   | FSR                   | Indirect Da | ata Memory          | Address Poir  | nter            |                                |                 |              |          | xxxx xxxx              | 135                   |

| 05h                  | PORTA                 |             |                     |               |                 | hen read (PIC<br>hen read (PIC |                 |              |          | xxxx 0000<br>xxx0 0000 | 52                    |

| 06h                  | PORTB                 |             |                     |               |                 | hen read (PIC<br>hen read (PIC |                 |              |          | xxxx xxxx<br>00xx xxxx | 58                    |

| 07h                  | —                     | Unimplem    | ented               |               |                 |                                |                 |              |          | —                      | _                     |

| 08h                  | _                     | Unimplem    | ented               |               |                 |                                |                 |              |          | _                      | _                     |

| 09h                  | _                     | Unimplem    | ented               |               |                 |                                |                 |              |          | _                      | _                     |

| 0Ah <sup>(1,2)</sup> | PCLATH                | _           | _                   | _             | Write Buffer    | for the Upper                  | 5 bits of the F | Program Cou  | unter    | 0 0000                 | 135                   |

| 0Bh <sup>(2)</sup>   | INTCON                | GIE         | PEIE                | TMR0IE        | INTOIE          | RBIE                           | TMR0IF          | INTOIF       | RBIF     | 0000 000x              | 19, 69,<br>77         |

| 0Ch                  | PIR1                  | _           | ADIF <sup>(4)</sup> | RCIF          | TXIF            | SSPIF                          | CCP1IF          | TMR2IF       | TMR1IF   | -000 0000              | 21, 77                |

| 0Dh                  | PIR2                  | OSFIF       | CMIF                | —             | EEIF            | —                              | _               | _            | _        | 00-0                   | 23, 34                |

| 0Eh                  | TMR1L                 | Holding Re  | egister for th      | e Least Sign  | ificant Byte of | the 16-bit TM                  | IR1 Register    | •            | •        | xxxx xxxx              | 77, 83                |

| 0Fh                  | TMR1H                 | Holding Re  | egister for th      | e Most Signi  | ficant Byte of  | the 16-bit TM                  | R1 Register     |              |          | xxxx xxxx              | 77, 83                |

| 10h                  | T1CON                 | _           | T1RUN               | T1CKPS1       | T1CKPS0         | T1OSCEN                        | T1SYNC          | TMR1CS       | TMR10N   | -000 0000              | 72, 83                |

| 11h                  | TMR2                  | Timer2 Mc   | dule Registe        | er            |                 |                                |                 | •            | •        | 0000 0000              | 80, 85                |

| 12h                  | T2CON                 | _           | TOUTPS3             | TOUTPS2       | TOUTPS1         | TOUTPS0                        | TMR2ON          | T2CKPS1      | T2CKPS0  | -000 0000              | 80, 85                |

| 13h                  | SSPBUF                | Synchrono   | ous Serial Po       | ort Receive B | uffer/Transmi   | t Register                     |                 |              |          | xxxx xxxx              | 90, 95                |

| 14h                  | SSPCON                | WCOL        | SSPOV               | SSPEN         | CKP             | SSPM3                          | SSPM2           | SSPM1        | SSPM0    | 0000 0000              | 89, 95                |

| 15h                  | CCPR1L                | Capture/C   | ompare/PWI          | M Register 1  | (LSB)           |                                |                 |              |          | xxxx xxxx              | 83, 85                |

| 16h                  | CCPR1H                | Capture/C   | ompare/PWI          | M Register 1  | (MSB)           |                                |                 |              |          | XXXX XXXX              | 83, 85                |

| 17h                  | CCP1CON               | _           | _                   | CCP1X         | CCP1Y           | CCP1M3                         | CCP1M2          | CCP1M1       | CCP1M0   | 00 0000                | 81, 83                |

| 18h                  | RCSTA                 | SPEN        | RX9                 | SREN          | CREN            | ADDEN                          | FERR            | OERR         | RX9D     | 0000 000x              | 98, 99                |

| 19h                  | TXREG                 | AUSART 1    | Fransmit Dat        | a Register    |                 |                                |                 |              |          | 0000 0000              | 103                   |

| 1Ah                  | RCREG                 | AUSART F    | Receive Data        | a Register    |                 |                                |                 |              |          | 0000 0000              | 105                   |

| 1Bh                  | _                     | Unimplem    | ented               |               |                 |                                |                 |              |          | _                      |                       |

| 1Ch                  | _                     | Unimplem    | ented               |               |                 |                                |                 |              |          | _                      |                       |

| 1Dh                  | —                     | Unimplem    | ented               |               |                 |                                |                 |              |          | —                      | _                     |

| 1Eh                  | ADRESH <sup>(4)</sup> | A/D Resul   | t Register Hi       | gh Byte       |                 |                                |                 |              |          | xxxx xxxx              | 120                   |

| 1Fh                  | ADCON0 <sup>(4)</sup> | ADCS1       | ADCS0               | CHS2          | CHS1            | CHS0                           | GO/DONE         | _            | ADON     | 0000 00-0              | 114, 120              |

TABLE 2-1:

SPECIAL FUNCTION REGISTER SUMMARY

**Legend:** x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for PC<12:8>, whose contents are transferred to the upper byte of the program counter.

2: These registers can be addressed from any bank.

3: RA5 is an input only; the state of the TRISA5 bit has no effect and will always read '1'.

4: PIC16F88 device only.

### 4.5.1 INTRC MODES

Using the internal oscillator as the clock source can eliminate the need for up to two external oscillator pins, after which it can be used for digital I/O. Two distinct configurations are available:

- In INTIO1 mode, the OSC2 pin outputs Fosc/4, while OSC1 functions as RA7 for digital input and output.

- In INTIO2 mode, OSC1 functions as RA7 and OSC2 functions as RA6, both for digital input and output.

#### 4.5.2 OSCTUNE REGISTER

The internal oscillator's output has been calibrated at the factory but can be adjusted in the application. This is done by writing to the OSCTUNE register (Register 4-1). The tuning sensitivity is constant throughout the tuning range. The OSCTUNE register has a tuning range of  $\pm 12.5\%$ .

When the OSCTUNE register is modified, the INTOSC and INTRC frequencies will begin shifting to the new frequency. The INTRC clock will reach the new frequency within 8 clock cycles (approximately 8 \* 32  $\mu$ s = 256  $\mu$ s); the INTOSC clock will stabilize within 1 ms. Code execution continues during this shift. There is no indication that the shift has occurred. Operation of features that depend on the 31.25 kHz INTRC clock source frequency, such as the WDT, Fail-Safe Clock Monitor and peripherals, will also be affected by the change in frequency.

| REGISTER 4-1: | OSCTUNE: OSCILLATOR TUNING REGISTER (ADDRESS 90h) |

|---------------|---------------------------------------------------|

|---------------|---------------------------------------------------|

| 4-1. | USCIUNE   | . USUILL     | ATOR TON        |             | SIER (AD     | DRE33 90      | n)           |       |

|------|-----------|--------------|-----------------|-------------|--------------|---------------|--------------|-------|

|      | U-0       | U-0          | R/W-0           | R/W-0       | R/W-0        | R/W-0         | R/W-0        | R/W-0 |

|      | —         | —            | TUN5            | TUN4        | TUN3         | TUN2          | TUN1         | TUN0  |

|      | bit 7     |              |                 |             |              |               |              | bit 0 |

| 6    | Unimplem  | ented: Rea   | <b>d as</b> '0' |             |              |               |              |       |

| -0   | TUN<5:0>: | Frequency    | Tuning bits     |             |              |               |              |       |

|      | 011111 =  | Maximum fr   | equency         |             |              |               |              |       |

|      | 011110 =  |              |                 |             |              |               |              |       |

|      | •         |              |                 |             |              |               |              |       |

|      | •         |              |                 |             |              |               |              |       |

|      | •         |              |                 |             |              |               |              |       |

|      | 000001 =  | - · · ·      | 0               |             |              |               |              |       |

|      |           | Senter frequ | ency. Oscill    | ator module | is running a | t the calibra | ted frequend | :у.   |

|      | 111111 =  |              |                 |             |              |               |              |       |

|      | •         |              |                 |             |              |               |              |       |

|      | •         |              |                 |             |              |               |              |       |

|      | 100000 =  | Minimum fre  | auencv          |             |              |               |              |       |

|      |           |              |                 |             |              |               |              |       |

|      |           |              |                 |             |              |               |              |       |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented I  | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# PIC16F87/88

- Clock before switch: One of INTOSC/INTOSC postscaler (IRCF<2:0> ≠ 000)

- 1. IRCF bits are modified to a different INTOSC/ INTOSC postscaler frequency.

- 2. The clock switching circuitry waits for a falling edge of the current clock, at which point CLKO is held low.

- 3. The clock switching circuitry then waits for eight falling edges of requested clock, after which it switches CLKO to this new clock source.

- 4. The IOFS bit is set.

- 5. Oscillator switchover is complete.

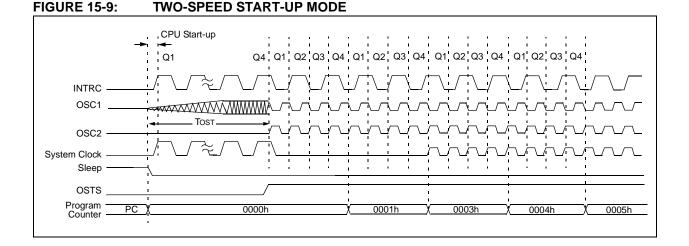

#### 4.6.6 OSCILLATOR DELAY UPON POWER-UP, WAKE-UP AND CLOCK SWITCHING

Table 4-3 shows the different delays invoked for various clock switching sequences. It also shows the delays invoked for POR and wake-up.

| Clock Sv             | witch                           | Frequency               | Occillator Dolov                                  | Comments                                                                                                                       |  |  |  |

|----------------------|---------------------------------|-------------------------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| From                 | То                              | Frequency               | Oscillator Delay                                  | Comments                                                                                                                       |  |  |  |

|                      | INTRC<br>T1OSC                  | 31.25 kHz<br>32.768 kHz | CPU Start-up <sup>(1)</sup>                       |                                                                                                                                |  |  |  |

| Sleep/POR            | INTOSC/<br>INTOSC<br>Postscaler | 125 kHz-8 MHz           | 4 ms (approx.) and<br>CPU Start-up <sup>(1)</sup> | Following a wake-up from Sleep mode or<br>POR, CPU start-up is invoked to allow the<br>CPU to become ready for code execution. |  |  |  |

| INTRC/Sleep          | EC, RC                          | DC – 20 MHz             |                                                   |                                                                                                                                |  |  |  |

| INTRC<br>(31.25 kHz) | EC, RC                          | DC – 20 MHz             |                                                   |                                                                                                                                |  |  |  |

| Sleep                | LP, XT, HS                      | 32.768 kHz-20 MHz       | 1024 Clock Cycles<br>(OST)                        | Following a change from INTRC, an OST of 1024 cycles must occur.                                                               |  |  |  |

| INTRC<br>(31.25 kHz) | INTOSC/<br>INTOSC<br>Postscaler | 125 kHz-8 MHz           | 4 ms (approx.)                                    | Refer to Section 4.6.4 "Modifying the IRCF Bits" for further details.                                                          |  |  |  |

## TABLE 4-3: OSCILLATOR DELAY EXAMPLES

**Note 1:** The 5-10  $\mu$ s start-up delay is based on a 1 MHz system clock.

### 6.3 Using Timer0 with an External Clock

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI, with the internal phase clocks, is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for T0CKI to be high for at least 2 Tosc (and a small RC delay of 20 ns) and low for at least 2 Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

#### 6.4 Prescaler

There is only one prescaler available, which is mutually exclusively shared between the Timer0 module and the Watchdog Timer. A prescaler assignment for the Timer0 module means that the prescaler cannot be used by the Watchdog Timer and vice versa. This prescaler is not readable or writable (see Figure 6-1). Note: Although the prescaler can be assigned to either the WDT or Timer0, but not both, a new divide counter is implemented in the WDT circuit to give multiple WDT time-out selections. This allows TMR0 and WDT to each have their own scaler. Refer to Section 15.12 "Watchdog Timer (WDT)" for further details.

The PSA and PS2:PS0 bits (OPTION\_REG<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

| Note: | Writing to TMR0, when the prescaler is  |

|-------|-----------------------------------------|

|       | assigned to Timer0, will clear the      |

|       | prescaler count but will not change the |

|       | prescaler assignment.                   |

## **REGISTER 6-1:** OPTION\_REG: OPTION CONTROL REGISTER (ADDRESS 81h, 181h)

|         | R/W-1       | R/W-1                          | R/W-1                  | R/W-1         | R/W-1          | R/W-1     | R/W-1         | R/W-1       |  |  |  |  |

|---------|-------------|--------------------------------|------------------------|---------------|----------------|-----------|---------------|-------------|--|--|--|--|

|         | RBPU        | INTEDG                         | TOCS                   | T0SE          | PSA            | PS2       | PS1           | PS0         |  |  |  |  |

|         | bit 7       | ·                              | ·                      |               |                |           |               | bit 0       |  |  |  |  |

| bit 7   | RBPU: PC    | RTB Pull-up                    | Enable bit             |               |                |           |               |             |  |  |  |  |

| bit 6   | INTEDG:     | nterrupt Edge                  | errupt Edge Select bit |               |                |           |               |             |  |  |  |  |

| bit 5   | TOCS: TM    | : TMR0 Clock Source Select bit |                        |               |                |           |               |             |  |  |  |  |

|         | 1 = Transit | ion on T0CKI                   | n on TOCKI pin         |               |                |           |               |             |  |  |  |  |

|         | 0 = Interna | I instruction a                | ycle clock (C          | LKO)          |                |           |               |             |  |  |  |  |

| bit 4   | TOSE: TMI   | R0 Source Ed                   | ge Select bit          | :             |                |           |               |             |  |  |  |  |

|         | 1 = Increm  | ent on high-to                 | o-low transitio        | on on T0CKI   | pin            |           |               |             |  |  |  |  |

|         |             | ent on low-to                  |                        |               | •              |           |               |             |  |  |  |  |

| bit 3   |             | caler Assignn                  | -                      |               | •              |           |               |             |  |  |  |  |

|         | 1 = Presca  | ller is assigne                | d to the WD            | г             |                |           |               |             |  |  |  |  |

|         |             | ler is assigne                 |                        |               |                |           |               |             |  |  |  |  |

| bit 2-0 | PS<2:0>:    | Prescaler Rat                  | e Select bits          |               |                |           |               |             |  |  |  |  |

|         | Bit Value   | TMR0 Rate                      | WDT Rate               |               |                |           |               |             |  |  |  |  |

|         | 000         | 1:2                            | 1:1                    |               |                |           |               |             |  |  |  |  |

|         | 001         | 1:4                            | 1:2                    |               |                |           |               |             |  |  |  |  |

|         | 010         | 1:8                            | 1:4                    |               |                |           |               |             |  |  |  |  |

|         | 011<br>100  | 1:16<br>1:32                   | 1:8<br>1:16            |               |                |           |               |             |  |  |  |  |

|         | 100         | 1:64                           | 1:32                   |               |                |           |               |             |  |  |  |  |

|         | 110         | 1:128                          | 1:64                   |               |                |           |               |             |  |  |  |  |

|         | 111         | 1 : 256                        | 1 : 128                |               |                |           |               |             |  |  |  |  |

|         | Legend:     |                                |                        |               |                |           |               |             |  |  |  |  |

|         | R = Reada   | ble bit                        | W = Wri                | table bit     | U = Unimpl     | emented b | it. read as ' | 0'          |  |  |  |  |

|         | -n = Value  |                                | '1' = Bit              |               | '0' = Bit is c |           | x = Bit is u  |             |  |  |  |  |

|         |             |                                | i – Dil                | 5 501         |                |           |               | INTOWN      |  |  |  |  |

|         | Note:       | To avoid an ι                  | unintended d           | evice Reset,  | the instructi  | on sequen | ce shown ir   | n the "PIC® |  |  |  |  |

|         |             | Mid-Range M                    |                        |               |                | •         |               |             |  |  |  |  |

|         |             | changing the                   | prescaler a            | ssignment fr  | om Timer0 t    | o the WD1 | . This sequ   | ence must   |  |  |  |  |

|         |             | be followed e                  | even if the W          | DT is disable | ed.            |           |               |             |  |  |  |  |

The maximum PWM resolution (bits) for a given PWM frequency is given by the following formula.

## **EQUATION 9-3:**

Resolution =

$$\frac{\log(\frac{\text{FOSC}}{\text{FPWM}})}{\log(2)}$$

Note: If the PWM duty cycle value is longer than the PWM period, the CCP1 pin will not be cleared.

#### 9.3.3 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- Make the CCP1 pin an output by clearing the TRISB<x> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

#### TABLE 9-3:EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 20 MHz

| PWM Frequency              | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|----------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                  | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8         | 7         | 6.6       |

#### TABLE 9-4: REGISTERS ASSOCIATED WITH PWM AND TIMER2

bits

| Address              | Name    | Bit 7   | Bit 6                                | Bit 5         | Bit 4      | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value<br>POR, |      | all o | e on<br>ther<br>sets |

|----------------------|---------|---------|--------------------------------------|---------------|------------|---------|--------|---------|---------|---------------|------|-------|----------------------|

| 0Bh,8Bh<br>10Bh,18Bh | INTCON  | GIE     | PEIE                                 | TMR0IE        | INTOIE     | RBIE    | TMR0IF | INTOIF  | RBIF    | 0000          | 000x | 0000  | 000u                 |

| 0Ch                  | PIR1    | _       | ADIF <sup>(1)</sup>                  | RCIF          | TXIF       | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | -000          | 0000 | -000  | 0000                 |

| 8Ch                  | PIE1    | _       | ADIE <sup>(1)</sup>                  | RCIE          | TXIE       | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | -000          | 0000 | -000  | 0000                 |

| 86h                  | TRISB   | PORT    | B Data Direc                         | ction Registe | er         |         |        |         |         | 1111          | 1111 | 1111  | 1111                 |

| 11h                  | TMR2    | Timer2  | Module Reg                           | gister        |            |         |        |         |         | 0000          | 0000 | 0000  | 0000                 |

| 92h                  | PR2     | Timer2  | Period Regi                          | ster          |            |         |        |         |         | 1111          | 1111 | 1111  | 1111                 |

| 12h                  | T2CON   |         | TOUTPS3                              | TOUTPS2       | TOUTPS1    | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000          | 0000 | -000  | 0000                 |

| 15h                  | CCPR1L  | Captur  | e/Compare/I                          | PWM Regist    | er 1 (LSB) |         |        |         |         | xxxx          | xxxx | uuuu  | uuuu                 |

| 16h                  | CCPR1H  | Capture | Capture/Compare/PWM Register 1 (MSB) |               |            |         |        |         |         | xxxx          | xxxx | uuuu  | uuuu                 |

| 17h                  | CCP1CON | _       | _                                    | CCP1X         | CCP1Y      | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0  | 00            | 0000 | 00    | 0000                 |

$\label{eq:logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical$

**Note 1:** This bit is only implemented on the PIC16F88. The bit will read '0' on the PIC16F87.

<sup>5.</sup> Configure the CCP1 module for PWM operation.

Note: The TRISB bit (0 or 3) is dependant upon the setting of configuration bit 12 (CCPMX).

# PIC16F87/88

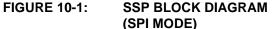

To enable the serial port, SSP Enable bit, SSPEN (SSPCON<5>), must be set. To reset or reconfigure SPI mode, clear bit SSPEN, reinitialize the SSPCON register and then set bit SSPEN. This configures the SDI, SDO, SCK and SS pins as serial port pins. For the pins to behave as the serial port function, they must have their data direction bits (in the TRISB register) appropriately programmed. That is:

- SDI must have TRISB<1> set

- SDO must have TRISB<2> cleared

- SCK (Master mode) must have TRISB<4> cleared

- SCK (Slave mode) must have TRISB<4> set

- SS must have TRISB<5> set

- Note 1: When the SPI is in Slave mode with SS pin control enabled (SSPCON<3:0> = 0100), the SPI module will reset if the SS pin is set to VDD.

- **2:** If the SPI is used in Slave mode with CKE = 1, then the  $\overline{SS}$  pin control must be enabled.

| TABLE 10-1: | <b>REGISTERS ASSOCIATED WITH SPI OPERATION</b> |

|-------------|------------------------------------------------|

|-------------|------------------------------------------------|

| Address              | Name    | Bit 7   | Bit 6               | Bit 5       | Bit 4      | Bit 3     | Bit 2       | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|----------------------|---------|---------|---------------------|-------------|------------|-----------|-------------|--------|--------|----------------------|---------------------------------|

| 0Bh,8Bh<br>10Bh,18Bh | INTCON  | GIE     | PEIE                | TMR0IE      | INT0IE     | RBIE      | TMR0IF      | INTOIF | RBIF   | 0000 000x            | 0000 000u                       |

| 0Ch                  | PIR1    | _       | ADIF <sup>(1)</sup> | RCIF        | TXIF       | SSPIF     | CCP1IF      | TMR2IF | TMR1IF | -000 0000            | -000 0000                       |

| 8Ch                  | PIE1    | _       | ADIE <sup>(1)</sup> | RCIE        | TXIE       | SSPIE     | CCP1IE      | TMR2IE | TMR1IE | -000 0000            | -000 0000                       |

| 86h                  | TRISB   | PORTB   | Data Dire           | ction Regis | ster       |           |             |        |        | 1111 1111            | 1111 1111                       |

| 13h                  | SSPBUF  | Synchro | nous Seria          | al Port Red | ceive Buff | er/Transn | nit Registe | r      |        | xxxx xxxx            | uuuu uuuu                       |

| 14h                  | SSPCON  | WCOL    | SSPOV               | SSPEN       | CKP        | SSPM3     | SSPM2       | SSPM1  | SSPM0  | 0000 0000            | 0000 0000                       |

| 94h                  | SSPSTAT | SMP     | CKE                 | D/A         | Р          | S         | R/W         | UA     | BF     | 0000 0000            | 0000 0000                       |

**Legend:** x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the SSP in SPI mode.**Note 1:**This bit is only implemented on the PIC16F88. The bit will read '0' on the PIC16F87.

## 10.3.1 SLAVE MODE

In Slave mode, the SCL and SDA pins must be configured as inputs (TRISB<4,1> set). The SSP module will override the input state with the output data when required (slave-transmitter).

When an address is matched, or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge ( $\overline{ACK}$ ) pulse and then load the SSPBUF register with the received value currently in the SSPSR register.

Either or both of the following conditions will cause the SSP module not to give this ACK pulse:

- a) The Buffer Full bit, BF (SSPSTAT<0>), was set before the transfer was received.

- b) The Overflow bit, SSPOV (SSPCON<6>), was set before the transfer was received.

In this case, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF (PIR1<3>) is set. Table 10-2 shows what happens when a data transfer byte is received, given the status of bits BF and SSPOV. The shaded cells show the condition where user software did not properly clear the overflow condition. Flag bit, BF, is cleared by reading the SSPBUF register while bit, SSPOV, is cleared through software.

The SCL clock input must have a minimum high and low for proper operation. The high and low times of the  $I^2C$  specification, as well as the requirement of the SSP module, are shown in timing parameter #100 and parameter #101.

## 10.3.1.1 Addressing

Once the SSP module has been enabled, it waits for a Start condition to occur. Following the Start condition, the eight bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match and the BF and SSPOV bits are clear, the following events occur:

- a) The SSPSR register value is loaded into the SSPBUF register.

- b) The Buffer Full bit, BF, is set.

- c) An  $\overline{ACK}$  pulse is generated.

- d) SSP Interrupt Flag bit, SSPIF (PIR1<3>), is set (interrupt is generated if enabled) – on the falling edge of the ninth SCL pulse.

In 10-bit Address mode, two address bytes need to be received by the slave device. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit R/W (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address, the first byte would equal '1111 0 A9 A8 0', where A9 and A8 are the two MSbs of the address.

The sequence of events for 10-bit Address mode is as follows, with steps 7-9 for slave transmitter:

- 1. Receive first (high) byte of address (bits SSPIF, BF and UA (SSPSTAT<1>) are set).

- Update the SSPADD register with second (low) byte of address (clears bit UA and releases the SCL line).

- 3. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 4. Receive second (low) byte of address (bits SSPIF, BF and UA are set).

- 5. Update the SSPADD register with the first (high) byte of address; if match releases SCL line, this will clear bit UA.

- 6. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 7. Receive Repeated Start condition.

- 8. Receive first (high) byte of address (bits SSPIF and BF are set).

- 9. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

## 10.3.1.2 Reception

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address byte overflow condition exists, then a no Acknowledge (ACK) pulse is given. An overflow condition is indicated if either bit, BF (SSPSTAT<0>), is set or bit, SSPOV (SSPCON<6>), is set.

An SSP interrupt is generated for each data transfer byte. Flag bit, SSPIF (PIR1<3>), must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

## 10.3.1.3 Transmission

When the  $R/\overline{W}$  bit of the incoming address byte is set and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The ACK pulse will be sent on the ninth bit and pin RB4/SCK/SCL is held low. The transmit data must be loaded into the SSPBUF register which also loads the SSPSR register. Then, pin RB4/SCK/SCL should be enabled by setting bit CKP (SSPCON<4>). The master device must monitor the SCL pin prior to asserting another clock pulse. The slave devices may be holding off the master device by stretching the clock. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 10-7).

## 11.2 AUSART Asynchronous Mode

In this mode, the AUSART uses standard Non-Returnto-Zero (NRZ) format (one Start bit, eight or nine data bits and one Stop bit). The most common data format is 8 bits. An on-chip, dedicated, 8-bit Baud Rate Generator can be used to derive standard baud rate frequencies from the oscillator. The AUSART transmits and receives the LSb first. The transmitter and receiver are functionally independent, but use the same data format and baud rate. The Baud Rate Generator produces a clock, either x16 or x64 of the bit shift rate, depending on bit BRGH (TXSTA<2>). Parity is not supported by the hardware, but can be implemented in software (and stored as the ninth data bit). Asynchronous mode is stopped during Sleep.

Asynchronous mode is selected by clearing bit SYNC (TXSTA<4>).

The AUSART Asynchronous module consists of the following important elements:

- Baud Rate Generator

- · Sampling Circuit

- Asynchronous Transmitter

- Asynchronous Receiver

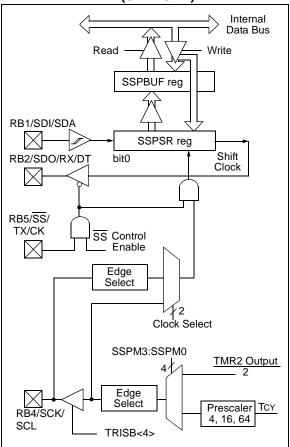

#### 11.2.1 AUSART ASYNCHRONOUS TRANSMITTER

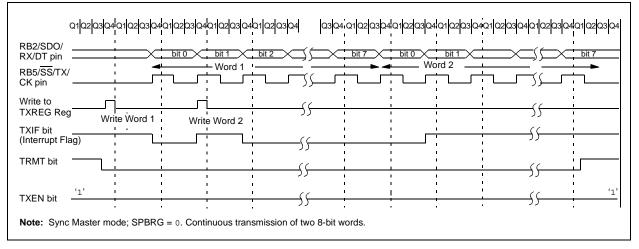

The AUSART transmitter block diagram is shown in Figure 11-1. The heart of the transmitter is the Transmit (Serial) Shift Register (TSR). The Shift register obtains its data from the Read/Write Transmit Buffer register, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the Stop bit has been transmitted from the previous load. As soon as the Stop bit is transmitted, the TSR is loaded with new data from the TXREG register (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TcY), the TXREG register is empty and flag bit, TXIF (PIR1<4>), is set. This interrupt can be enabled/disabled by setting/clearing enable bit, TXIE (PIE1<4>). Flag bit TXIF will be set, regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit, TRMT (TXSTA<1>), shows the status of the TSR register. Status bit TRMT is a read-only bit which is set when the TSR register is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty.

| Note 1: | The TSR register is not mapped in data memory, so it is not available to the user.  |

|---------|-------------------------------------------------------------------------------------|

| 2:      | Flag bit TXIF is set when enable bit TXEN is set. TXIF is cleared by loading TXREG. |

Transmission is enabled by setting enable bit TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data and the Baud Rate Generator (BRG) has produced a shift clock (Figure 11-2). The transmission can also be started by first loading the TXREG register and then setting enable bit TXEN. Normally, when transmission is first started, the TSR register is empty. At that point, transfer to the TXREG register will result in an immediate transfer to TSR, resulting in an empty TXREG. A back-to-back transfer is thus possible (Figure 11-3). Clearing enable bit TXEN during a transmission will cause the transmission to be aborted and will reset the transmitter. As a result, the RB5/SS/TX/CK pin will revert to high-impedance.

In order to select 9-bit transmission, transmit bit, TX9 (TXSTA<6>), should be set and the ninth bit should be written to TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG register can result in an immediate transfer of the data to the TSR register (if the TSR is empty). In such a case, an incorrect ninth data bit may be loaded in the TSR register.

## FIGURE 11-1: AUSART TRANSMIT BLOCK DIAGRAM

| Address                | Name   | Bit 7   | Bit 6                         | Bit 5      | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|------------------------|--------|---------|-------------------------------|------------|--------|-------|--------|--------|--------|-----------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE     | PEIE                          | TMR0IE     | INT0IE | RBIE  | TMR0IF | INTOIF | RBIF   | 0000 000x             | 0000 000u                       |

| 0Ch                    | PIR1   | —       | ADIF <sup>(1)</sup>           | RCIF       | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | -000 0000             | -000 0000                       |

| 18h                    | RCSTA  | SPEN    | RX9                           | SREN       | CREN   | ADDEN | FERR   | OERR   | RX9D   | 0000 000x             | 0000 000x                       |

| 19h                    | TXREG  | AUSART  | AUSART Transmit Data Register |            |        |       |        |        |        | 0000 0000             | 0000 0000                       |

| 8Ch                    | PIE1   | —       | ADIE <sup>(1)</sup>           | RCIE       | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE | -000 0000             | -000 0000                       |

| 98h                    | TXSTA  | CSRC    | TX9                           | TXEN       | SYNC   | _     | BRGH   | TRMT   | TX9D   | 0000 -010             | 0000 -010                       |

| 99h                    | SPBRG  | Baud Ra | te Genera                     | tor Regist | er     |       |        |        |        | 0000 0000             | 0000 0000                       |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission.

Note 1: This bit is only implemented on the PIC16F88. The bit will read '0' on the PIC16F87.

#### FIGURE 11-9: SYNCHRONOUS TRANSMISSION

#### FIGURE 11-10: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

| RB2/SDO/RX/DT pin     | bit 0 bit 1 bit 2 bit 6 bit 7 |

|-----------------------|-------------------------------|

| RB5/SS/TX/CK pin      |                               |

| Write to<br>TXREG Reg |                               |

| TXIF bit              | <u></u>                       |

| TRMT bit              |                               |

| TXEN bit              | \ \ .                         |

#### 11.3.2 AUSART SYNCHRONOUS MASTER RECEPTION

Once Synchronous mode is selected, reception is enabled by setting either enable bit SREN (RCSTA<5>), or enable bit CREN (RCSTA<4>). Data is sampled on the RB2/SDO/RX/DT pin on the falling edge of the clock. If enable bit SREN is set, then only a single word is received. If enable bit CREN is set, the reception is continuous until CREN is cleared. If both bits are set, CREN takes precedence.

After clocking the last bit, the received data in the Receive Shift Register (RSR) is transferred to the RCREG register (if it is empty). When the transfer is complete, interrupt flag bit, RCIF (PIR1<5>), is set. The actual interrupt can be enabled/disabled by setting/ clearing enable bit RCIE (PIE1<5>).

Flag bit RCIF is a read-only bit which is reset by the hardware. In this case, it is reset when the RCREG register has been read and is empty. The RCREG is a double-buffered register (i.e., it is a two-deep FIFO). It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting into the RSR register. On the clocking of the last bit of the third byte, if the RCREG register is still full, then Overrun Error bit, OERR (RCSTA<1>), is set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Bit OERR has to be cleared in software (by clearing bit CREN). If bit OERR is set, transfers from the RSR to the RCREG are inhibited, so it is essential to clear bit OERR if it is set.

receive data. Reading the RCREG register will load bit RX9D with a new value, therefore, it is essential for the user to read the RCSTA register, before reading RCREG, in order not to lose the old RX9D information.

When setting up a synchronous master reception:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 11.1 "AUSART Baud Rate Generator (BRG)").

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Ensure bits CREN and SREN are clear.

- 4. If interrupts are desired, then set enable bit RCIE.

- 5. If 9-bit reception is desired, then set bit RX9.

- 6. If a single reception is required, set bit SREN. For continuous reception, set bit CREN.

- 7. Interrupt flag bit, RCIF, will be set when reception is complete and an interrupt will be generated if enable bit, RCIE, was set.

- 8. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 9. Read the 8-bit received data by reading the RCREG register.

- 10. If any error occurred, clear the error by clearing bit CREN.

- 11. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

| ABLE II-II. REGISTERS ASSOCIATED WITH STRUCKOROUS MASTER RECEPTION |                                                           |                                                           |                                                                                                                         |                                                                                                                                                               |                                                                                                                                                                                              |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                                                               | Bit 7                                                     | Bit 6                                                     | Bit 5                                                                                                                   | Bit 4                                                                                                                                                         | Bit 3                                                                                                                                                                                        | Bit 2                                                                                                                                                                                                             | Bit 1                                                                                                                                                                                                                                                | Bit 0                                                                                                                                                                                                                                                                               | Value on:<br>POR, BOR                                                                                                                                                                                                                                                                                            | Value on<br>all other<br>Resets                                                                                                                                                                                                                                                                                                                                                              |

| INTCON                                                             | GIE                                                       | PEIE                                                      | TMR0IE                                                                                                                  | INT0IE                                                                                                                                                        | RBIE                                                                                                                                                                                         | TMR0IF                                                                                                                                                                                                            | INTOIF                                                                                                                                                                                                                                               | RBIF                                                                                                                                                                                                                                                                                | 0000 000x                                                                                                                                                                                                                                                                                                        | 0000 000u                                                                                                                                                                                                                                                                                                                                                                                    |

| PIR1                                                               |                                                           | ADIF <sup>(1)</sup>                                       | RCIF                                                                                                                    | TXIF                                                                                                                                                          | SSPIF                                                                                                                                                                                        | CCP1IF                                                                                                                                                                                                            | TMR2IF                                                                                                                                                                                                                                               | TMR1IF                                                                                                                                                                                                                                                                              | -000 0000                                                                                                                                                                                                                                                                                                        | -000 0000                                                                                                                                                                                                                                                                                                                                                                                    |

| RCSTA                                                              | SPEN                                                      | RX9                                                       | SREN                                                                                                                    | CREN                                                                                                                                                          | ADDEN                                                                                                                                                                                        | FERR                                                                                                                                                                                                              | OERR                                                                                                                                                                                                                                                 | RX9D                                                                                                                                                                                                                                                                                | 0000 000x                                                                                                                                                                                                                                                                                                        | 0000 000x                                                                                                                                                                                                                                                                                                                                                                                    |

| RCREG                                                              | AUSART                                                    | AUSART Receive Data Register 0000 0000 0000 0000          |                                                                                                                         |                                                                                                                                                               |                                                                                                                                                                                              |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                      | 0000 0000                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                              |

| PIE1                                                               | _                                                         | ADIE <sup>(1)</sup>                                       | RCIE                                                                                                                    | TXIE                                                                                                                                                          | SSPIE                                                                                                                                                                                        | CCP1IE                                                                                                                                                                                                            | TMR2IE                                                                                                                                                                                                                                               | TMR1IE                                                                                                                                                                                                                                                                              | -000 0000                                                                                                                                                                                                                                                                                                        | -000 0000                                                                                                                                                                                                                                                                                                                                                                                    |

| TXSTA                                                              | CSRC                                                      | TX9                                                       | TXEN                                                                                                                    | SYNC                                                                                                                                                          | _                                                                                                                                                                                            | BRGH                                                                                                                                                                                                              | TRMT                                                                                                                                                                                                                                                 | TX9D                                                                                                                                                                                                                                                                                | 0000 -010                                                                                                                                                                                                                                                                                                        | 0000 -010                                                                                                                                                                                                                                                                                                                                                                                    |

| SPBRG                                                              | Baud Ra                                                   | Baud Rate Generator Register 0000 0000 0000 0000          |                                                                                                                         |                                                                                                                                                               |                                                                                                                                                                                              |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                    | Name<br>INTCON<br>PIR1<br>RCSTA<br>RCREG<br>PIE1<br>TXSTA | NameBit 7INTCONGIEPIR1—RCSTASPENRCREGAUSARTPIE1—TXSTACSRC | NameBit 7Bit 6INTCONGIEPEIEPIR1—ADIF <sup>(1)</sup> RCSTASPENRX9RCREGAUSAT ReceivePIE1—ADIE <sup>(1)</sup> TXSTACSRCTX9 | NameBit 7Bit 6Bit 5INTCONGIEPEIETMR0IEPIR1—ADIF <sup>(1)</sup> RCIFRCSTASPENRX9SRENRCREGAUSART Receive Data RegiPIE1—ADIE <sup>(1)</sup> RCIETXSTACSRCTX9TXEN | NameBit 7Bit 6Bit 5Bit 4INTCONGIEPEIETMROIEINTOIEPIR1—ADIF <sup>(1)</sup> RCIFTXIFRCSTASPENRX9SRENCRENRCREGAUSART Receive Data RegisterPIE1—ADIE <sup>(1)</sup> RCIETXIETXSTACSRCTX9TXENSYNC | NameBit 7Bit 6Bit 5Bit 4Bit 3INTCONGIEPEIETMR0IEINT0IERBIEPIR1—ADIF <sup>(1)</sup> RCIFTXIFSSPIFRCSTASPENRX9SRENCRENADDENRCREGAUSATEcceveData RegisterFIE1—ADIE <sup>(1)</sup> RCIETXIESSPIETXSTACSRCTX9TXENSYNC— | NameBit 7Bit 6Bit 5Bit 4Bit 3Bit 2INTCONGIEPEIETMROIEINTOIERBIETMROIFPIR1—ADIF <sup>(1)</sup> RCIFTXIFSSPIFCCP1IFRCSTASPENRX9SRENCRENADDENFERRRCREGAUSART Receive Data RegisterPIE1—ADIE <sup>(1)</sup> RCIETXIESSPIECCP1IETXSTACSRCTX9TXENSYNC—BRGH | NameBit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1INTCONGIEPEIETMR0IEINT0IERBIETMR0IFINT0IFPIR1—ADIF <sup>(1)</sup> RCIFTXIFSSPIFCCP1IFTMR2IFRCSTASPENRX9SRENCRENADDENFERROERRRCREGAUSART Receive Data RegisterPIE1—ADIE <sup>(1)</sup> RCIETXIESSPIECCP1IETMR2IETXSTACSRCTX9TXENSYNC—BRGHTRMT | NameBit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0INTCONGIEPEIETMROIEINTOIERBIETMROIFINTOIFRBIFPIR1—ADIF <sup>(1)</sup> RCIFTXIFSSPIFCCP1IFTMR2IFTMR1IFRCSTASPENRX9SRENCRENADDENFERROERRRX9DRCREGAUSART Receive Data RegisterFIE1—ADIE <sup>(1)</sup> RCIETXIESSPIECCP1IETMR2IETMR1IETXSTACSRCTX9TXENSYNC—BRGHTRMTTX9D | NameBit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0Value on:<br>POR, BORINTCONGIEPEIETMROIEINTOIERBIETMROIFINTOIFRBIF0000000xPIR1—ADIF <sup>(1)</sup> RCIFTXIFSSPIFCCP1IFTMR2IFTMR1IF-000000xRCSTASPENRX9SRENCRENADDENFEROERRRX9D0000000xRCREGAUSATRCIETXIESSPIECCP1IETMR2IETMR1IE-0000000PIE1—ADIE <sup>(1)</sup> RCIETXIESSPIECCP1IETMR2IETMR1IE-0000000TXSTACSRCTX9TXENSYNC—BRGHTRMTTX9D0000-010 |

## TABLE 11-11: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous master reception.

**Note 1:** This bit is only implemented on the PIC16F88. The bit will read '0' on the PIC16F87.

# 12.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

The Analog-to-Digital (A/D) converter module has seven inputs for 18/20 pin devices (PIC16F88 devices only).

The conversion of an analog input signal results in a corresponding 10-bit digital number. The A/D module has a high and low-voltage reference input that is software selectable to some combination of VDD, VSS, VREF- (RA2) or VREF+ (RA3).

The A/D converter has a unique feature of being able to operate while the device is in Sleep mode. To operate in Sleep, the A/D conversion clock must be derived from the A/D's internal RC oscillator. The A/D module has five registers:

- A/D Result High Register (ADRESH)

- A/D Result Low Register (ADRESL)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

- Analog Select Register (ANSEL)

The ADCON0 register, shown in Register 12-2, controls the operation of the A/D module. The ANSEL register, shown in Register 12-1 and the ADCON1 register, shown in Register 12-3, configure the functions of the port pins. The port pins can be configured as analog inputs (RA3/RA2 can also be voltage references) or as digital I/O.

Additional information on using the A/D module can be found in the "*PIC*<sup>®</sup> *Mid-Range MCU Family Reference Manual*" (DS33023).

#### REGISTER 12-1: ANSEL: ANALOG SELECT REGISTER (ADDRESS9Bh) PIC16F88 DEVICES ONLY

|   | U-0   | R/W-1 |

|---|-------|-------|-------|-------|-------|-------|-------|-------|

|   | _     | ANS6  | ANS5  | ANS4  | ANS3  | ANS2  | ANS1  | ANS0  |

| - | bit 7 |       |       |       |       |       |       | bit 0 |

#### bit 7 Unimplemented: Read as '0'

bit 6-0 **ANS<6:0>:** Analog Input Select bits

Bits select input function on corresponding AN<6:0> pins.

1 = Analog I/O<sup>(1,2)</sup>

0 = Digital I/O

- **Note 1:** Setting a pin to an analog input disables the digital input buffer. The corresponding TRIS bit should be set to input mode when using pins as analog inputs. Only AN2 is an analog I/O, all other ANx pins are analog inputs.

- **2:** See the block diagrams for the analog I/O pins to see how ANSEL interacts with the CHS bits of the ADCON0 register.

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# 15.0 SPECIAL FEATURES OF THE CPU

These devices have a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power-saving operating modes and offer code protection:

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- Two-Speed Start-up

- Fail-Safe Clock Monitor

- Sleep

- Code Protection

- ID Locations

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only. It is designed to keep the part in Reset while the power supply stabilizes and is enabled or disabled using a configuration bit. With these two timers on-chip, most applications need no external Reset circuitry. Sleep mode is designed to offer a very low-current Power-down mode. The user can wake-up from Sleep through external Reset, Watchdog Timer wake-up or through an interrupt.

Additional information on special features is available in the "*PIC*<sup>®</sup> *Mid-Range MCU Family Reference Manual*" (DS33023).

# 15.1 Configuration Bits