Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Active                                                                 |

| Core Processor             | PIC                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 20MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                  |

| Number of I/O              | 16                                                                     |

| Program Memory Size        | 7KB (4K x 14)                                                          |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 256 x 8                                                                |

| RAM Size                   | 368 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                              |

| Data Converters            | -                                                                      |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Through Hole                                                           |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                |

| Supplier Device Package    | 18-PDIP                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f87-i-p |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name                    | PDIP/<br>SOIC<br>Pin# | SSOP<br>Pin# | QFN<br>Pin# | l/O/P<br>Type | Buffer<br>Type    | Description                                                                                                        |

|-----------------------------|-----------------------|--------------|-------------|---------------|-------------------|--------------------------------------------------------------------------------------------------------------------|

|                             |                       |              |             |               |                   | PORTB is a bidirectional I/O port. PORTB can be<br>software programmed for internal weak pull-up on all<br>inputs. |

| RB0/INT/CCP1 <sup>(5)</sup> | 6                     | 7            | 7           |               |                   |                                                                                                                    |

| RB0                         |                       |              |             | I/O           | TTL               | Bidirectional I/O pin.                                                                                             |

| INT                         |                       |              |             | I             | ST <sup>(1)</sup> | External interrupt pin.                                                                                            |

| CCP1                        |                       |              |             | I/O           | ST                | Capture input, Compare output, PWM output.                                                                         |

| RB1/SDI/SDA                 | 7                     | 8            | 8           |               |                   |                                                                                                                    |

| RB1<br>SDI                  |                       |              |             | I/O<br>I      | TTL<br>ST         | Bidirectional I/O pin.<br>SPI data in.                                                                             |

| SDA                         |                       |              |             | 1/0           | ST                | $I^2 C^{TM}$ data.                                                                                                 |

| RB2/SDO/RX/DT               | 8                     | 9            | 9           | 1/0           | 01                |                                                                                                                    |

| RB2                         | 0                     | 9            | 9           | I/O           | TTL               | Bidirectional I/O pin.                                                                                             |

| SDO                         |                       |              |             | 0             | ST                | SPI data out.                                                                                                      |

| RX                          |                       |              |             | I             |                   | AUSART asynchronous receive.                                                                                       |

| DT                          |                       |              |             | I/O           |                   | AUSART synchronous detect.                                                                                         |

| RB3/PGM/CCP1 <sup>(5)</sup> | 9                     | 10           | 10          |               |                   |                                                                                                                    |

| RB3                         |                       |              |             | I/O           | TTL               | Bidirectional I/O pin.                                                                                             |

| PGM                         |                       |              |             | I/O           | ST                | Low-Voltage ICSP™ Programming enable pin.                                                                          |

| CCP1                        |                       |              |             | I             | ST                | Capture input, Compare output, PWM output.                                                                         |

| RB4/SCK/SCL                 | 10                    | 11           | 12          |               |                   |                                                                                                                    |

| RB4<br>SCK                  |                       |              |             | 1/0<br>1/0    | TTL<br>ST         | Bidirectional I/O pin. Interrupt-on-change pin.<br>Synchronous serial clock input/output for SPI.                  |

| SCL                         |                       |              |             | 1/0           | ST                | Synchronous serial clock input/output for SP1.                                                                     |

| RB5/SS/TX/CK                | 11                    | 12           | 13          | •             | 01                | Cynonionous senarolook inpartor r C.                                                                               |

| RB5                         | 1 11                  | 12           | 15          | I/O           | TTL               | Bidirectional I/O pin. Interrupt-on-change pin.                                                                    |

| SS                          |                       |              |             | 1/0           | TTL               | Slave select for SPI in Slave mode.                                                                                |

| TX                          |                       |              |             | 0             |                   | AUSART asynchronous transmit.                                                                                      |

| СК                          |                       |              |             | I/O           |                   | AUSART synchronous clock.                                                                                          |

| RB6/AN5/PGC/T1OSO/          | 12                    | 13           | 15          |               |                   |                                                                                                                    |

| T1CKI                       |                       |              |             |               |                   |                                                                                                                    |

|                             |                       |              |             | I/O           | TTL               | Bidirectional I/O pin. Interrupt-on-change pin.                                                                    |

| AN5 <sup>(4)</sup><br>PGC   |                       |              |             | I<br>I/O      | ST <sup>(2)</sup> | Analog input channel 5.<br>In-Circuit Debugger and programming clock pin.                                          |

| T10S0                       |                       |              |             | 0             | ST                | Timer1 oscillator output.                                                                                          |

| T1CKI                       |                       |              |             | I             | ST                | Timer1 external clock input.                                                                                       |

| RB7/AN6/PGD/T1OSI           | 13                    | 14           | 16          |               |                   |                                                                                                                    |

| RB7                         |                       | 17           | 10          | I/O           | TTL               | Bidirectional I/O pin. Interrupt-on-change pin.                                                                    |

| AN6 <sup>(4)</sup>          |                       |              |             | I             |                   | Analog input channel 6.                                                                                            |

| PGD                         |                       |              |             | I             | ST <sup>(2)</sup> | In-Circuit Debugger and ICSP programming data pi                                                                   |

| T1OSI                       |                       |              |             | I             | ST                | Timer1 oscillator input.                                                                                           |

| Vss                         | 5                     | 5, 6         | 3, 5        | Р             | -                 | Ground reference for logic and I/O pins.                                                                           |

| VDD                         | 14                    | 15, 16       | 17, 19      | Р             | -                 | Positive supply for logic and I/O pins.                                                                            |

| TABLE 1-2: | PIC16F87/88 PINOUT DESCRIPTION ( | (CONTINUED) |

|------------|----------------------------------|-------------|

|            |                                  |             |

- = Not used TTL = TTL Input ST = Schmitt Trigger Input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

4: PIC16F88 devices only.

5: The CCP1 pin is determined by the CCPMX bit in Configuration Word 1 register.

### 2.2.2.1 STATUS Register

The STATUS register, shown in Register 2-1, contains the arithmetic status of the ALU, the Reset status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as '000u uluu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register because these instructions do not affect the Z, C or DC bits from the STATUS register. For other instructions not affecting any Status bits, see Section 16.0 "Instruction Set Summary".

Note: The C and DC bits operate as a borrow and digit borrow bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

## REGISTER 2-1: STATUS: ARITHMETIC STATUS REGISTER (ADDRESS 03h, 83h, 103h, 183h)

|         | R/W-0                                                                                                                                                                   | R/W-0                                                     | R/W-0         | R-1            | R-1           | R/W-x        | R/W-x          | R/W-x     |  |  |  |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|---------------|----------------|---------------|--------------|----------------|-----------|--|--|--|

|         | IRP                                                                                                                                                                     | RP1                                                       | RP0           | TO             | PD            | Z            | DC             | С         |  |  |  |

|         | bit 7                                                                                                                                                                   |                                                           |               |                |               |              |                | bit 0     |  |  |  |

| bit 7   | 1 = Bank                                                                                                                                                                | ster Bank Sel<br>2, 3 (100h-1F<br>0, 1 (00h-FFt           | Fh)           | for indirect a | ddressing)    |              |                |           |  |  |  |

| bit 6-5 | 11 = Bank                                                                                                                                                               | Register Ban<br>3 (180h-1FF                               | h)            | (used for dir  | ect address   | sing)        |                |           |  |  |  |

|         | 01 = Bank<br>00 = Bank                                                                                                                                                  | 2 (100h-17F<br>1 (80h-FFh)<br>0 (00h-7Fh)<br>is 128 bytes |               |                |               |              |                |           |  |  |  |

| bit 4   | TO: Time-                                                                                                                                                               | out bit                                                   |               |                |               |              |                |           |  |  |  |

|         |                                                                                                                                                                         | power-up, CL                                              |               | tion or SLEE   | P instruction | n            |                |           |  |  |  |

| bit 3   | PD: Powe                                                                                                                                                                | r-Down bit                                                |               |                |               |              |                |           |  |  |  |

|         |                                                                                                                                                                         | power-up or b<br>ecution of the                           |               |                |               |              |                |           |  |  |  |

| bit 2   | Z: Zero bit                                                                                                                                                             | t                                                         |               |                |               |              |                |           |  |  |  |

|         |                                                                                                                                                                         | esult of an ari<br>esult of an ari                        |               |                |               |              |                |           |  |  |  |

| bit 1   | DC: Digit                                                                                                                                                               | carry/borrow b                                            | oit (Addwf, A | DDLW, SUBLI    | N and SUBW    | F instructio | ns) <b>(1)</b> |           |  |  |  |

|         |                                                                                                                                                                         | ry-out from the<br>arry-out from t                        |               |                |               | red          |                |           |  |  |  |

| bit 0   | C: Carry/borrow bit (ADDWF, ADDLW, SUBLW and SUBWF instructions) <sup>(1,2)</sup>                                                                                       |                                                           |               |                |               |              |                |           |  |  |  |

|         | <ul> <li>1 = A carry-out from the Most Significant bit of the result occurred</li> <li>0 = No carry-out from the Most Significant bit of the result occurred</li> </ul> |                                                           |               |                |               |              |                |           |  |  |  |

|         | <b>Note 1:</b> For borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand.                                    |                                                           |               |                |               |              |                |           |  |  |  |

|         | 2:                                                                                                                                                                      | For rotate (R:<br>bit of the sou                          |               | ructions, this | bit is loade  | d with eithe | r the high or  | low-order |  |  |  |

|         | Logondy                                                                                                                                                                 |                                                           |               |                |               |              |                |           |  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### 2.2.2.3 INTCON Register

The INTCON register is a readable and writable register that contains various enable and flag bits for the TMR0 register overflow, RB Port change and External RB0/INT pin interrupts. Note: Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

## REGISTER 2-3: INTCON: INTERRUPT CONTROL REGISTER (ADDRESS 0Bh, 8Bh, 10Bh, 18Bh)

| R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0 | R/W-0  | R/W-0  | R/W-x |

|-------|-------|--------|--------|-------|--------|--------|-------|

| GIE   | PEIE  | TMR0IE | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF  |

| bit 7 |       |        |        |       |        |        | bit 0 |

| bit 7  | GIE: Global Interrupt Enable bit                                                                                |

|--------|-----------------------------------------------------------------------------------------------------------------|

|        | 1 = Enables all unmasked interrupts                                                                             |

|        | 0 = Disables all interrupts                                                                                     |

| bit 6  | PEIE: Peripheral Interrupt Enable bit                                                                           |

|        | 1 = Enables all unmasked peripheral interrupts                                                                  |

|        | <ul> <li>0 = Disables all peripheral interrupts</li> </ul>                                                      |

| bit 5  | TMR0IE: TMR0 Overflow Interrupt Enable bit                                                                      |

|        | 1 = Enables the TMR0 interrupt                                                                                  |

|        | 0 = Disables the TMR0 interrupt                                                                                 |

| bit 4  | INTOIE: RB0/INT External Interrupt Enable bit                                                                   |

|        | 1 = Enables the RB0/INT external interrupt                                                                      |

| 1.14.0 | 0 = Disables the RB0/INT external interrupt                                                                     |

| bit 3  | <b>RBIE:</b> RB Port Change Interrupt Enable bit                                                                |

|        | <ul> <li>1 = Enables the RB port change interrupt</li> <li>0 = Disables the RB port change interrupt</li> </ul> |

| bit 2  | TMR0IF: TMR0 Overflow Interrupt Flag bit                                                                        |

| 511 2  | 1 = TMR0 register has overflowed (must be cleared in software)                                                  |

|        | 0 = TMR0 register did not overflow                                                                              |

| bit 1  | INTOIF: RB0/INT External Interrupt Flag bit                                                                     |

|        | 1 = The RB0/INT external interrupt occurred (must be cleared in software)                                       |

|        | 0 = The RB0/INT external interrupt did not occur                                                                |

| bit 0  | RBIF: RB Port Change Interrupt Flag bit                                                                         |

|        | A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch                    |

|        | condition and allow flag bit RBIF to be cleared.                                                                |

|        | 1 = At least one of the RB7:RB4 pins changed state (must be cleared in software)                                |

|        | 0 = None of the RB7:RB4 pins have changed state                                                                 |

|        |                                                                                                                 |

|        | Legend:                                                                                                         |

|        | D. Deadable bit W. Writeble bit II. Unimplemented bit read as (0)                                               |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|                   |                  |                      |                    |

### 4.6.3 CLOCK TRANSITION AND WDT

When clock switching is performed, the Watchdog Timer is disabled because the Watchdog ripple counter is used as the Oscillator Start-up Timer.

Once the clock transition is complete (i.e., new oscillator selection switch has occurred), the Watchdog counter is re-enabled with the counter reset. This allows the user to synchronize the Watchdog Timer to the start of execution at the new clock frequency.

| Note: | The OST is only used when switching to |

|-------|----------------------------------------|

|       | XT, HS and LP Oscillator modes.        |

## REGISTER 4-2: OSCCON: OSCILLATOR CONTROL REGISTER (ADDRESS 8Fh)

| U-0   | R/W-0 | R/W-0 | R/W-0 | R-0                 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|---------------------|-------|-------|-------|

| -     | IRCF2 | IRCF1 | IRCF0 | OSTS <sup>(1)</sup> | IOFS  | SCS1  | SCS0  |

| bit 7 |       |       |       |                     |       |       | bit 0 |

- bit 7 Unimplemented: Read as '0'

- bit 6-4 IRCF<2:0>: Internal RC Oscillator Frequency Select bits

- 000 = 31.25 kHz

- 001 = 125 kHz

- 010 = 250 kHz

- 011 = 500 kHz

- 100 = 1 MHz

- 101 = 2 MHz

- 110 = 4 MHz

- 111 = 8 MHz

### bit 3 **OSTS:** Oscillator Start-up Time-out Status bit<sup>(1)</sup>

- 1 = Device is running from the primary system clock

- 0 = Device is running from T1OSC or INTRC as a secondary system clock

- Note 1: Bit resets to '0' with Two-Speed Start-up mode and LP, XT or HS selected as the oscillator mode.

- bit 2 **IOFS:** INTOSC Frequency Stable bit

- 1 = Frequency is stable

- 0 = Frequency is not stable

- bit 1-0 SCS<1:0>: Oscillator Mode Select bits

- 00 = Oscillator mode defined by FOSC<2:0>

- 01 = T1OSC is used for system clock

- 10 = Internal RC is used for system clock

- 11 = Reserved

| Legend:           |                  |                      |                     |  |  |

|-------------------|------------------|----------------------|---------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | ed bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown  |  |  |

NOTES:

© 2002-2013 Microchip Technology Inc.

|         | R/W-0                                                                                                                                     | R/W-0                        | R/W-0         | R/W-0         | R/W-0       | R/W-0         | U-0           | R/W-0 |  |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|---------------|---------------|-------------|---------------|---------------|-------|--|

|         | ADCS1                                                                                                                                     | ADCS0                        | CHS2          | CHS1          | CHS0        | GO/DONE       | _             | ADON  |  |

|         | bit 7                                                                                                                                     |                              |               |               |             |               |               | bit 0 |  |

| bit 7-6 | ADCS<1:0                                                                                                                                  | )>: A/D Conv                 | version Cloc  | k Select bits |             |               |               |       |  |

|         | If ADCS2 :                                                                                                                                |                              |               |               |             |               |               |       |  |

|         | 00 = Fosc<br>01 = Fosc                                                                                                                    |                              |               |               |             |               |               |       |  |

|         | 10 = FOSC<br>10 = FOSC                                                                                                                    |                              |               |               |             |               |               |       |  |

|         |                                                                                                                                           | clock derive                 | d from the ir | nternal A/D n | nodule RC o | oscillator)   |               |       |  |

|         | If ADCS2 :                                                                                                                                | = 1:                         |               |               |             |               |               |       |  |

|         | 00 = Fosc                                                                                                                                 |                              |               |               |             |               |               |       |  |

|         | 01 = FOSC                                                                                                                                 |                              |               |               |             |               |               |       |  |

|         | 10 = FOSC/64<br>11 = FRC (clock derived from the internal A/D module RC oscillator)                                                       |                              |               |               |             |               |               |       |  |

| bit 5-3 | CHS<2:0>: Analog Channel Select bits                                                                                                      |                              |               |               |             |               |               |       |  |

|         |                                                                                                                                           | annel 0 (RA0                 |               |               |             |               |               |       |  |

|         |                                                                                                                                           | annel 1 (RA1                 | ,             |               |             |               |               |       |  |

|         |                                                                                                                                           | annel 2 (RA2<br>annel 3 (RA3 | ,             |               |             |               |               |       |  |

|         | 011 = Channel 3 (RA3/AN3)<br>100 = Channel 4 (RA4/AN4)                                                                                    |                              |               |               |             |               |               |       |  |

|         | 101 = Channel 5 (RB6/AN5)                                                                                                                 |                              |               |               |             |               |               |       |  |

|         | 110 = Channel 6 (RB7/AN6)                                                                                                                 |                              |               |               |             |               |               |       |  |

| bit 2   | GO/DONE: A/D Conversion Status bit                                                                                                        |                              |               |               |             |               |               |       |  |

|         | If ADON = 1:<br>1 = A/D conversion in progress (setting this bit starts the A/D conversion)                                               |                              |               |               |             |               |               |       |  |

|         | 0 = A/D conversion not in progress (this bit is automatically cleared by hardware when the A/D                                            |                              |               |               |             |               |               |       |  |

|         | conversion is complete)                                                                                                                   |                              |               |               |             |               |               |       |  |

| bit 1   | Unimplemented: Read as '0'                                                                                                                |                              |               |               |             |               |               |       |  |

| bit 0   | ADON: A/D On bit                                                                                                                          |                              |               |               |             |               |               |       |  |

|         | <ul> <li>1 = A/D converter module is operating</li> <li>0 = A/D converter module is shut off and consumes no operating current</li> </ul> |                              |               |               |             |               |               |       |  |

|         | Legend:                                                                                                                                   |                              |               |               |             |               |               |       |  |

|         | R = Reada                                                                                                                                 | able bit                     | W = W         | /ritable bit  | U = Unir    | mplemented bi | t, read as '  | 0'    |  |

|         | -n = Value                                                                                                                                |                              | (1) _ D       | it is set     | (O' D:+     | is cleared    | k = Bit is ur |       |  |

| R/P-1      |                                                                             |               | R/P-1      | WORD 1 REGISTER (ADDRESS 2007h)<br>R/P-1 R/P-1 R/P-1 R/P-1 R/P-1 R/P-1                                   |

|------------|-----------------------------------------------------------------------------|---------------|------------|----------------------------------------------------------------------------------------------------------|

|            |                                                                             | VRT0 CPD      | 1          | BOREN MCLRE FOSC2 PWRTEN WDTEN FOSC1 FOSC0                                                               |

| bit 13     |                                                                             |               | LVI        | bit 0                                                                                                    |

|            |                                                                             |               |            | 5.1 0                                                                                                    |

| bit 13     | CP: Flash Program Mem                                                       | ory Code Pro  | tection bi | its                                                                                                      |

|            | 1 = Code protection off                                                     |               |            |                                                                                                          |

|            | 0 = 0000h to 0FFFh code                                                     | •             | ll protect | ed)                                                                                                      |

| bit 12     | CCPMX: CCP1 Pin Select                                                      |               |            |                                                                                                          |

|            | 1 = CCP1 function on RE<br>0 = CCP1 function on RE                          |               |            |                                                                                                          |

| bit 11     | DEBUG: In-Circuit Debug                                                     | ger Mode bit  |            |                                                                                                          |

|            |                                                                             | -             |            | 7 are general purpose I/O pins                                                                           |

|            | 0 = In-Circuit Debugger e                                                   | nabled, RB6   | and RB7    | 7 are dedicated to the debugger                                                                          |

| bit 10-9   | 5                                                                           | m Memory W    | /rite Enat | ble bits                                                                                                 |

|            | 11 = Write protection off                                                   | e-protected   | 0100h to   | 0FFFh may be modified by EECON control                                                                   |

|            |                                                                             | •             |            | 0FFFh may be modified by EECON control                                                                   |

|            | 00 = 0000h to 0FFFh write                                                   | e-protected   |            |                                                                                                          |

| bit 8      | CPD: Data EE Memory C                                                       | ode Protectio | on bit     |                                                                                                          |

|            | <ul> <li>1 = Code protection off</li> <li>0 = Data EE memory cod</li> </ul> | o protoctod   |            |                                                                                                          |

| bit 7      | LVP: Low-Voltage Progra                                                     |               | la hit     |                                                                                                          |

|            |                                                                             | -             |            | age Programming enabled                                                                                  |

|            | 0 = RB3 is digital I/O, HV                                                  |               |            |                                                                                                          |

| bit 6      | BOREN: Brown-out Rese                                                       | et Enable bit |            |                                                                                                          |

|            | 1 = BOR enabled                                                             |               |            |                                                                                                          |

| hit E      | 0 = BOR disabled<br>MCLRE: RA5/MCLR/VPF                                     | Din Function  |            | -iu                                                                                                      |

| bit 5      | 1 = RA5/MCLR/VPP pin f                                                      |               |            | Sit.                                                                                                     |

|            |                                                                             |               |            | ACLR internally tied to VDD                                                                              |

| bit 3      | PWRTEN: Power-up Tim                                                        | er Enable bit |            |                                                                                                          |

|            | 1 = PWRT disabled                                                           |               |            |                                                                                                          |

|            | 0 = PWRT enabled                                                            |               |            |                                                                                                          |

| bit 2      | WDTEN: Watchdog Time<br>1 = WDT enabled                                     | r Enable bit  |            |                                                                                                          |

|            | 0 = WDT disabled                                                            |               |            |                                                                                                          |

| bit 4, 1-0 | ) FOSC<2:0>: Oscillator S                                                   | election bits |            |                                                                                                          |

|            | 111 = EXTRC oscillator;                                                     |               |            |                                                                                                          |

|            | 110 = EXTRC oscillator;                                                     |               |            |                                                                                                          |

|            |                                                                             |               |            | /OSC2/CLKO pin and port I/O function on RA7/OSC1/CLKI pir<br>oth RA6/OSC2/CLKO pin and RA7/OSC1/CLKI pin |

|            | 011 = ECIO; port I/O fun                                                    |               |            |                                                                                                          |

|            | 010 = HS oscillator                                                         |               |            |                                                                                                          |

|            | 001 = XT oscillator<br>000 = LP oscillator                                  |               |            |                                                                                                          |

|            |                                                                             |               |            |                                                                                                          |

|            | Legend:                                                                     |               |            |                                                                                                          |

|            | R = Readable bit                                                            |               | Writable   |                                                                                                          |

|            | -n = Value at POR                                                           | '1' =         | Bit is set | t '0' = Bit is cleared $x = Bit$ is unknown                                                              |

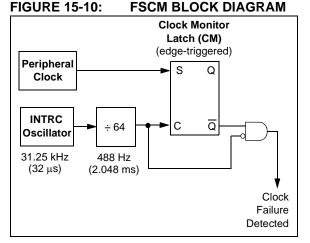

### 15.12.4 FAIL-SAFE OPTION

The Fail-Safe Clock Monitor (FSCM) is designed to allow the device to continue to operate even in the event of an oscillator failure.

The FSCM function is enabled by setting the FCMEN bit in Configuration Word 2.

In the event of an oscillator failure, the FSCM will generate an oscillator fail interrupt and will switch the system clock over to the internal oscillator. The system will continue to come from the internal oscillator until the fail-safe condition is exited. The fail-safe condition is exited with either a Reset, the execution of a SLEEP instruction or a write to the OSCCON register.

The frequency of the internal oscillator will depend upon the value contained in the IRCF bits. Another clock source can be selected via the IRCF and the SCS bits of the OSCCON register. The FSCM sample clock is generated by dividing the INTRC clock by 64. This will allow enough time between FSCM sample clocks for a system clock edge to occur.

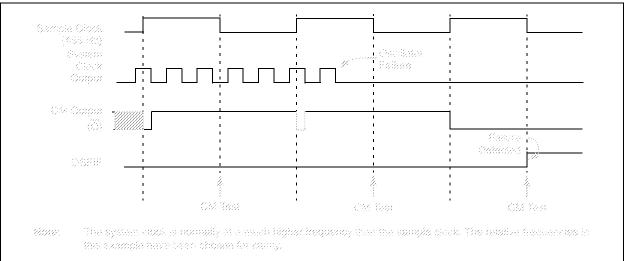

On the rising edge of the postscaled clock, the monitoring latch (CM = 0) will be cleared. On a falling edge of the primary or secondary system clock, the monitoring latch will be set (CM = 1). In the event that a falling edge of the postscaled clock occurs and the monitoring latch is not set, a clock failure has been detected.

While in Fail-Safe mode, a Reset will exit the fail-safe condition. If the primary clock source is configured for a crystal, the OST timer will wait for the 1024 clock cycles for the OST time-out and the device will continue running from the internal oscillator until the OST is complete. A SLEEP instruction, or a write to the SCS bits (where SCS bits do not = 00), can be performed to put the device into a low-power mode.

| Note: | Two-Speed Start-up mode is automatically |      |     |           |        |    |  |

|-------|------------------------------------------|------|-----|-----------|--------|----|--|

|       | enabled                                  | when | the | fail-safe | option | is |  |

|       | enabled.                                 |      |     |           |        |    |  |

If Reset occurs while in Fail-Safe mode and the primary clock source is EC or RC, then the device will immediately switch back to EC or RC mode.

### 15.12.4.1 Fail-Safe in Low-Power Mode

A write to the OSCCON register, or SLEEP instruction, will end the fail-safe condition. The system clock will default to the source selected by the SCS bits, which is either T1OSC, INTRC or none (Sleep mode). However, the FSCM will continue to monitor the system clock. If the secondary clock fails, the device will immediately switch to the internal oscillator clock. If OSFIE is set, an interrupt will be generated.

## FIGURE 15-11: FSCM TIMING DIAGRAM

## 16.0 INSTRUCTION SET SUMMARY

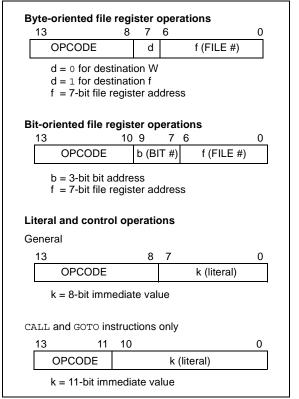

The PIC16 instruction set is highly orthogonal and is comprised of three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

Each PIC16 instruction is a 14-bit word divided into an **opcode**, which specifies the instruction type and one or more **operands**, which further specify the operation of the instruction. The formats for each of the categories are presented in Figure 16-1, while the various opcode fields are summarized in Table 16-1.

Table 16-2 lists the instructions recognized by the MPASM<sup>TM</sup> assembler. A complete description of each instruction is also available in the "*PIC*<sup>®</sup> *Mid-Range MCU Family Reference Manual*" (DS33023).

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator, which selects the bit affected by the operation, while 'f' represents the address of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven-bit constant or literal value

One instruction cycle consists of four oscillator periods. For an oscillator frequency of 4 MHz, this gives a normal instruction execution time of 1  $\mu$ s. All instructions are executed within a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of an instruction. When this occurs, the execution takes two instruction cycles, with the second cycle executed as a NOP.

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

## 16.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (RMW) operation. The register is read, the data is modified and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register. For example, a "CLRF PORTB" instruction will read PORTB, clear all the data bits, then write the result back to PORTB. This example would have the unintended result that the condition that sets the RBIF flag would be cleared.

## TABLE 16-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                       |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                              |

| W     | Working register (accumulator)                                                                                                                                                    |

| b     | Bit address within an 8-bit file register                                                                                                                                         |

| k     | Literal field, constant data or label                                                                                                                                             |

| x     | Don't care location (= $0$ or 1).<br>The assembler will generate code with x = $0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; $d = 0$ : store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1.                                                                  |

| PC    | Program Counter                                                                                                                                                                   |

| ТО    | Time-out bit                                                                                                                                                                      |

| PD    | Power-Down bit                                                                                                                                                                    |

## FIGURE 16-1: GENERAL FORMAT FOR INSTRUCTIONS

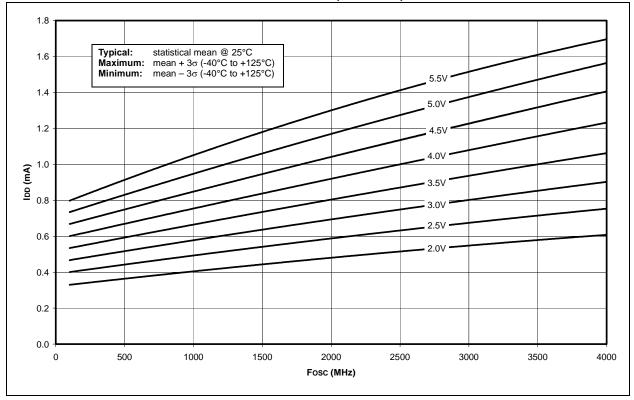

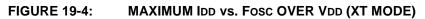

## 18.2 DC Characteristics: Power-Down and Supply Current PIC16F87/88 (Industrial, Extended) PIC16LF87/88 (Industrial) (Continued)

| PIC16LF8<br>(Indus | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |     |     |       |                  |            |                                       |  |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|------------------|------------|---------------------------------------|--|--|

| PIC16F87<br>(Indus | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                               |     |     |       |                  |            |                                       |  |  |

| Param<br>No.       | Device                                                                                                                             | Тур | Max | Units | Units Conditions |            |                                       |  |  |

|                    | Supply Current (IDD) <sup>(2,3)</sup>                                                                                              |     |     |       |                  |            |                                       |  |  |

|                    | PIC16LF87/88                                                                                                                       | 310 | 420 | μΑ    | -40°C            |            |                                       |  |  |

|                    |                                                                                                                                    | 300 | 410 | μΑ    | +25°C            | VDD = 2.0V |                                       |  |  |

|                    |                                                                                                                                    | 300 | 410 | μΑ    | +85°C            |            |                                       |  |  |

|                    | PIC16LF87/88                                                                                                                       | 550 | 650 | μΑ    | -40°C            |            |                                       |  |  |

|                    |                                                                                                                                    | 530 | 620 | μΑ    | +25°C            | VDD = 3.0V | Fosc = 4 MHz<br>( <b>RC_RUN</b> mode, |  |  |

|                    |                                                                                                                                    | 530 | 620 | μΑ    | +85°C            |            | Internal RC Oscillator)               |  |  |

|                    | All devices                                                                                                                        | 1.2 | 1.5 | mA    | -40°C            | Vdd = 5.0V | ,                                     |  |  |

|                    |                                                                                                                                    | 1.1 | 1.4 | mA    | +25°C            |            |                                       |  |  |

|                    |                                                                                                                                    | 1.1 | 1.4 | mA    | +85°C            |            |                                       |  |  |

|                    | Extended devices                                                                                                                   | 1.3 | 1.6 | mA    | +125°C           |            |                                       |  |  |

Legend: Shading of rows is to assist in readability of the table.

**Note 1:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or VSS and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;

MCLR = VDD; WDT enabled/disabled as specified.

**3:** For RC oscillator configurations, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

| Param<br>No. | Symbol                | Characteristic                                                         | Min                                           | Тур†         | Max      | Units     | Conditions |  |

|--------------|-----------------------|------------------------------------------------------------------------|-----------------------------------------------|--------------|----------|-----------|------------|--|

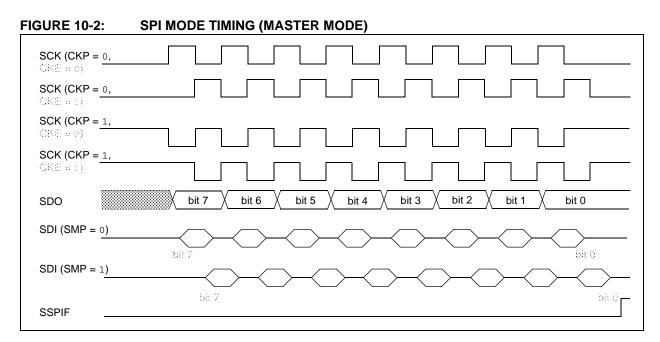

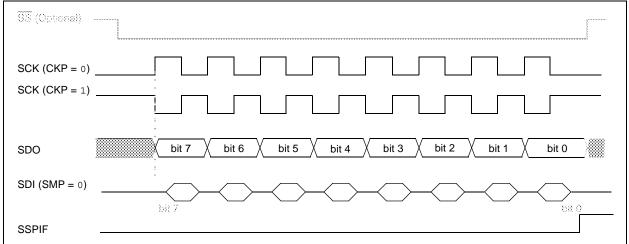

| 70*          | TssL2scH,<br>TssL2scL | $\overline{SS} \downarrow$ to SCK $\downarrow$ or SCK $\uparrow$ Input | Тсү                                           | -            | -        | ns        |            |  |

| 71*          | TscH                  | SCK Input High Time (Slave mode)                                       |                                               | TCY + 20     | -        | _         | ns         |  |

| 72*          | TscL                  | SCK Input Low Time (Slave mode)                                        |                                               | TCY + 20     | _        | —         | ns         |  |

| 73*          | TdiV2scH,<br>TdiV2scL | Setup Time of SDI Data Input to SC                                     | 100                                           | —            | —        | ns        |            |  |

| 74*          | TscH2diL,<br>TscL2diL | Hold Time of SDI Data Input to SCK Edge                                |                                               | 100          | —        | —         | ns         |  |

| 75*          | TdoR                  | SDO Data Output Rise Time                                              | PIC16 <b>F</b> 87/88<br>PIC16 <b>LF</b> 87/88 |              | 10<br>25 | 25<br>50  | ns<br>ns   |  |

| 76*          | TdoF                  | SDO Data Output Fall Time                                              |                                               | 10           | 25       | ns        |            |  |

| 77*          | TssH2doZ              | SS ↑ to SDO Output High-Impedan                                        | се                                            | 10           | _        | 50        | ns         |  |

| 78*          | TscR                  | SCK Output Rise Time PIC16F87/88<br>(Master mode) PIC16LF87/88         |                                               |              | 10<br>25 | 25<br>50  | ns<br>ns   |  |

| 79*          | TscF                  | SCK Output Fall Time (Master mod                                       | e)                                            | _            | 10       | 25        | ns         |  |

| 80*          | TscH2doV,<br>TscL2doV | SDO Data Output Valid after SCK<br>Edge                                | PIC16 <b>F</b> 87/88<br>PIC16 <b>LF</b> 87/88 |              | _        | 50<br>145 | ns<br>ns   |  |

| 81*          | TdoV2scH,<br>TdoV2scL | SDO Data Output Setup to SCK Edge                                      |                                               | Тсү          | —        | -         | ns         |  |

| 82*          | TssL2doV              | SDO Data Output Valid after $\overline{SS} \downarrow E$               | _                                             | - 1          | 50       | ns        |            |  |

| 83*          | TscH2ssH,<br>TscL2ssH | SS ↑ after SCK Edge                                                    |                                               | 1.5 Tcy + 40 | -        | -         | ns         |  |

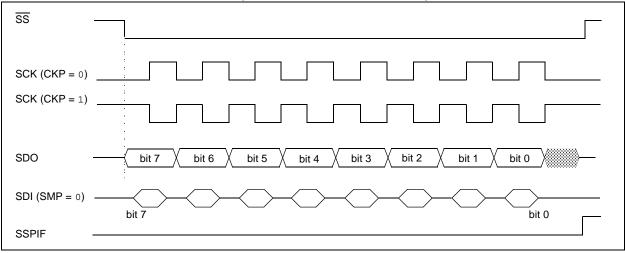

### TABLE 18-8: SPI MODE REQUIREMENTS

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

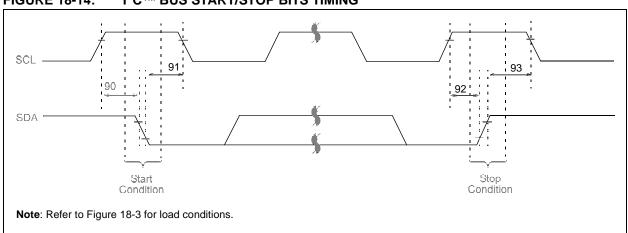

## FIGURE 18-14: I<sup>2</sup>C<sup>™</sup> BUS START/STOP BITS TIMING

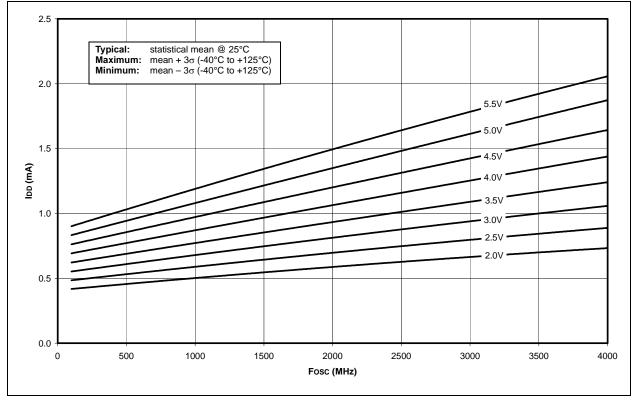

FIGURE 19-21: TYPICAL, MINIMUM AND MAXIMUM Vol vs. Iol (VDD = 3V, -40°C TO +125°C)

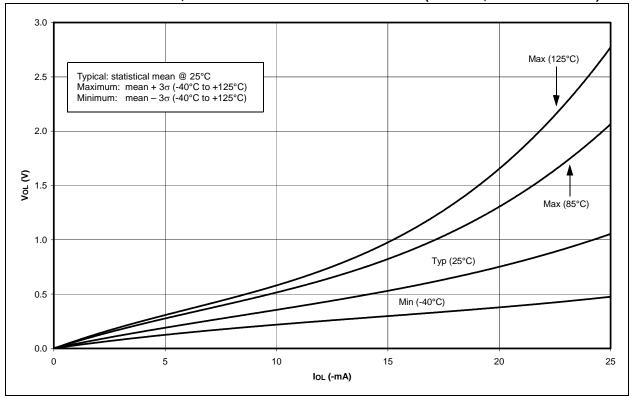

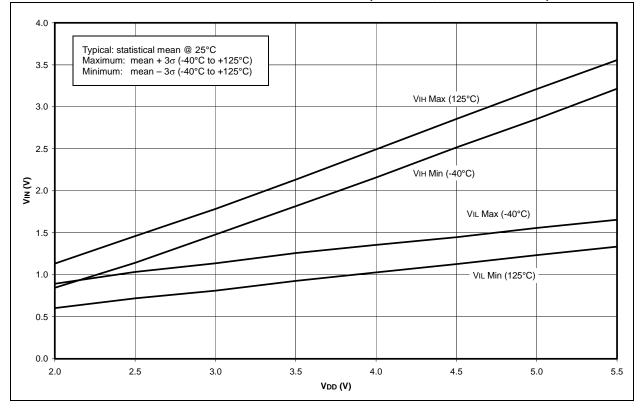

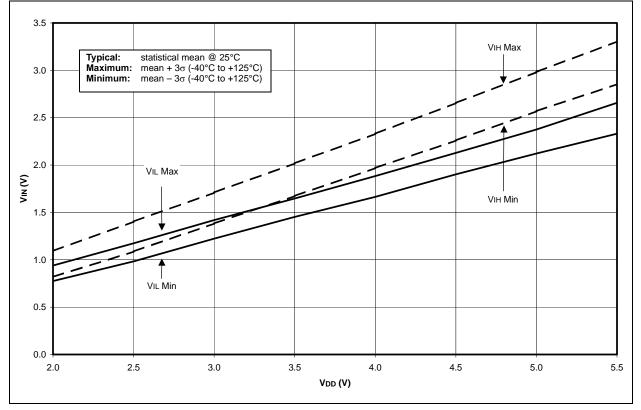

### FIGURE 19-23: MINIMUM AND MAXIMUM VIN vs. VDD (ST INPUT, -40°C TO +125°C)

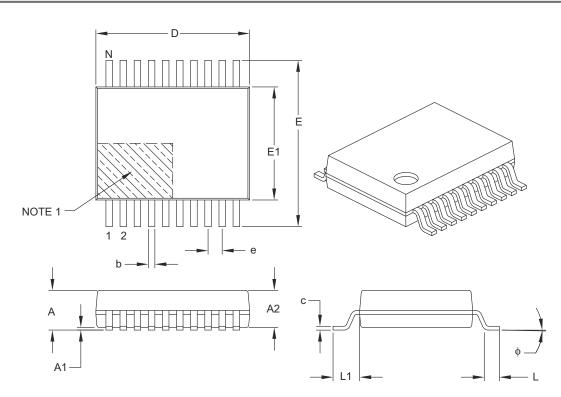

## 20-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units    |          |         | MILLIMETERS |  |  |  |

|--------------------------|----------|----------|---------|-------------|--|--|--|

| Dimension                | n Limits | MIN      | MIN NOM |             |  |  |  |

| Number of Pins           | Ν        | 20       |         |             |  |  |  |

| Pitch                    | е        | 0.65 BSC |         |             |  |  |  |

| Overall Height           | Α        | -        | -       | 2.00        |  |  |  |

| Molded Package Thickness | A2       | 1.65     | 1.75    | 1.85        |  |  |  |

| Standoff                 | A1       | 0.05     | -       | -           |  |  |  |

| Overall Width            | Е        | 7.40     | 7.80    | 8.20        |  |  |  |

| Molded Package Width     | E1       | 5.00     | 5.30    | 5.60        |  |  |  |

| Overall Length           | D        | 6.90     | 7.20    | 7.50        |  |  |  |

| Foot Length              | L        | 0.55     | 0.75    | 0.95        |  |  |  |

| Footprint L1             |          | 1.25 REF |         |             |  |  |  |

| Lead Thickness           | с        | 0.09     | -       | 0.25        |  |  |  |

| Foot Angle               | φ        | 0°       | 4°      | 8°          |  |  |  |

| Lead Width               | b        | 0.22     | -       | 0.38        |  |  |  |

### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-072B

## APPENDIX A: REVISION HISTORY

## **Revision A (November 2003)**

Original data sheet for PIC16F87/88 devices.

## **Revision B (August 2003)**

The specifications in **Section 18.0** "**Electrical Characteristics**" have been updated to include the addition of maximum specifications to the DC Characteristics tables, text clarification has been made to **Section 4.6.2** "**Clock Switching**" and there have been minor updates to the data sheet text.

## **Revision C (January 2005)**

This revision includes the DC and AC Characteristics Graphs and Tables. The Electrical Specifications in **Section 18.0 "Electrical Characteristics"** have been updated and there have been minor corrections to the data sheet text.

## **Revision D (October 2011)**

This revision updated the package marking and package outline drawings in **Section 20.0** "**Packaging Information**".

## APPENDIX B: DEVICE DIFFERENCES

The differences between the devices in this data sheet are listed in Table B-1.

| TABLE B-1: | DIFFERENCES BETWEEN       |  |  |  |

|------------|---------------------------|--|--|--|

|            | THE PIC16F87 AND PIC16F88 |  |  |  |

| Features                       | PIC16F87 | PIC16F88          |

|--------------------------------|----------|-------------------|

| Analog-to-Digital<br>Converter | N/A      | 10-bit, 7-channel |

NOTES:

NOTES: