Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 16                                                                      |

| Program Memory Size        | 7KB (4K x 14)                                                           |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 256 x 8                                                                 |

| RAM Size                   | 368 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                               |

| Data Converters            | -                                                                       |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                          |

| Supplier Device Package    | 18-SOIC                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f87-i-so |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.2.2.6 PIE2 Register

The PIE2 register contains the individual enable bit for the EEPROM write operation interrupt.

| REGISTER 2-6: | PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2 (ADDRESS 8Dh) |                            |               |               |              |           |              |        |  |  |  |

|---------------|------------------------------------------------------------|----------------------------|---------------|---------------|--------------|-----------|--------------|--------|--|--|--|

|               | R/W-0                                                      | R/W-0                      | U-0           | R/W-0         | U-0          | U-0       | U-0          | U-0    |  |  |  |

|               | OSFIE                                                      | CMIE                       | —             | EEIE          | —            | —         |              | _      |  |  |  |

|               | bit 7                                                      |                            |               |               |              |           |              | bit 0  |  |  |  |

| bit 7         | OSFIE: Os                                                  | cillator Fail In           | terrupt Enab  | le bit        |              |           |              |        |  |  |  |

|               | 1 = Enable<br>0 = Disable                                  |                            |               |               |              |           |              |        |  |  |  |

| bit 6         | CMIE: Corr                                                 | parator Inter              | rupt Enable I | oit           |              |           |              |        |  |  |  |

|               | 1 = Enable                                                 |                            |               |               |              |           |              |        |  |  |  |

|               | 0 = Disable                                                |                            |               |               |              |           |              |        |  |  |  |

| bit 5         | Unimplem                                                   | ented: Read                | <b>as</b> '0' |               |              |           |              |        |  |  |  |

| bit 4         | EEIE: EEP                                                  | ROM Write C                | peration Inte | errupt Enable | bit          |           |              |        |  |  |  |

|               | 1 = Enable<br>0 = Disable                                  |                            |               |               |              |           |              |        |  |  |  |

| bit 3-0       | Unimplem                                                   | Unimplemented: Read as '0' |               |               |              |           |              |        |  |  |  |

|               |                                                            |                            |               |               |              |           |              |        |  |  |  |

|               | Legend:                                                    |                            |               |               |              |           |              |        |  |  |  |

|               | R = Reada                                                  | ble bit                    | W = W         | ritable bit   | U = Unimp    | olemented | bit, read as | '0'    |  |  |  |

|               | -n = Value                                                 | at POR                     | '1' = Bi      | t is set      | '0' = Bit is | cleared   | x = Bit is u | nknown |  |  |  |

### 3.0 DATA EEPROM AND FLASH PROGRAM MEMORY

The data EEPROM and Flash program memory are readable and writable during normal operation (over the full VDD range). This memory is not directly mapped in the register file space. Instead, it is indirectly addressed through the Special Function Registers. There are six SFRs used to read and write this memory:

- EECON1

- EECON2

- EEDATA

- EEDATH

- EEADR

- EEADRH

This section focuses on reading and writing data EEPROM and Flash program memory during normal operation. Refer to the appropriate device programming specification document for serial programming information.

When interfacing the data memory block, EEDATA holds the 8-bit data for read/write and EEADR holds the address of the EEPROM location being accessed. The PIC16F87/88 devices have 256 bytes of data EEPROM with an address range from 00h to 0FFh. When writing to unimplemented locations, the charge pump will be turned off.

When interfacing the program memory block, the EED-ATA and EEDATH registers form a two-byte word that holds the 14-bit data for read/write and the EEADR and EEADRH registers form a two-byte word that holds the 13-bit address of the EEPROM location being accessed. The PIC16F87/88 devices have 4K words of program Flash with an address range from 0000h to 0FFFh. Addresses above the range of the respective device will wraparound to the beginning of program memory.

The EEPROM data memory allows single byte read and write. The Flash program memory allows singleword reads and four-word block writes. Program memory writes must first start with a 32-word block erase, then write in 4-word blocks. A byte write in data EEPROM memory automatically erases the location and writes the new data (erase before write).

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump, rated to operate over the voltage range of the device for byte or word operations.

When the device is code-protected, the CPU may continue to read and write the data EEPROM memory. Depending on the settings of the write-protect bits, the device may or may not be able to write certain blocks of the program memory; however, reads of the program memory are allowed. When code-protected, the device programmer can no longer access data or program memory; this does NOT inhibit internal reads or writes.

### 3.1 EEADR and EEADRH

The EEADRH:EEADR register pair can address up to a maximum of 256 bytes of data EEPROM, or up to a maximum of 8K words of program EEPROM. When selecting a data address value, only the LSB of the address is written to the EEADR register. When selecting a program address value, the MSB of the address is written to the EEADRH register and the LSB is written to the EEADR register.

If the device contains less memory than the full address reach of the address register pair, the Most Significant bits of the registers are not implemented. For example, if the device has 128 bytes of data EEPROM, the Most Significant bit of EEADR is not implemented on access to data EEPROM.

#### 3.2 EECON1 and EECON2 Registers

EECON1 is the control register for memory accesses.

Control bit EEPGD determines if the access will be a program or data memory access. When clear, as it is when reset, any subsequent operations will operate on the data memory. When set, any subsequent operations will operate on the program memory.

Control bits, RD and WR, initiate read and write, respectively. These bits cannot be cleared, only set in software. They are cleared in hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write or erase operation. On power-up, the WREN bit is clear. The WRERR bit is set when a write (or erase) operation is interrupted by a MCLR, or a WDT Time-out Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and rewrite the location. The data and address will be unchanged in the EEDATA and EEADR registers.

Interrupt flag bit, EEIF in the PIR2 register, is set when the write is complete. It must be cleared in software.

EECON2 is not a physical register. Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the EEPROM write sequence.

#### 4.7 **Power-Managed Modes**

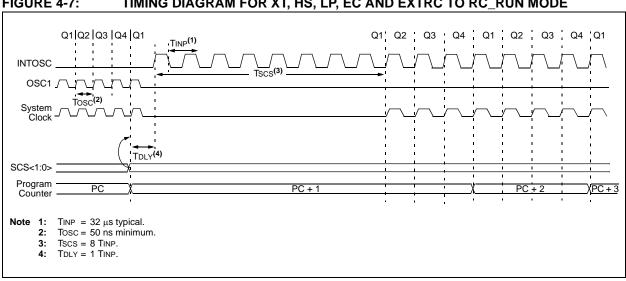

#### 4.7.1 RC RUN MODE

When SCS bits are configured to run from the INTRC, a clock transition is generated if the system clock is not already using the INTRC. The event will clear the OSTS bit, switch the system clock from the primary system clock (if SCS < 1:0 > = 0.0) determined by the value contained in the configuration bits, or from the T1OSC (if SCS<1:0> = 01) to the INTRC clock option and shut down the primary system clock to conserve power. Clock switching will not occur if the primary system clock is already configured as INTRC.

If the system clock does not come from the INTRC (31.25 kHz) when the SCS bits are changed and the IRCF bits in the OSCCON register are configured for a frequency other than INTRC, the frequency may not be stable immediately. The IOFS bit (OSCCON<2>) will be set when the INTOSC or postscaler frequency is stable, after 4 ms (approx.).

After a clock switch has been executed, the OSTS bit is cleared, indicating a low-power mode and the device does not run from the primary system clock. The internal Q clocks are held in the Q1 state until eight falling edge clocks are counted on the INTRC oscillator. After the eight clock periods have transpired, the clock input to the Q clocks is released and operation resumes (see Figure 4-7).

#### FIGURE 4-7: TIMING DIAGRAM FOR XT, HS, LP, EC AND EXTRC TO RC\_RUN MODE

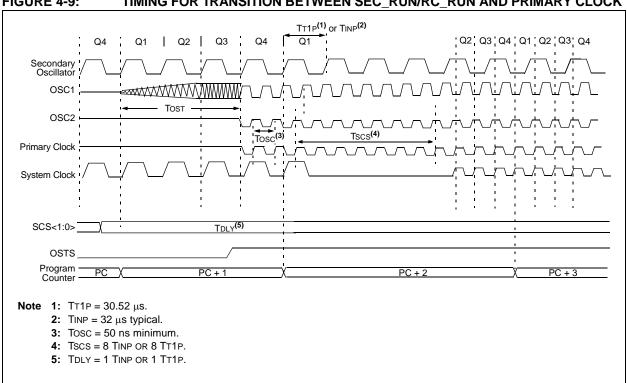

#### FIGURE 4-9: TIMING FOR TRANSITION BETWEEN SEC\_RUN/RC\_RUN AND PRIMARY CLOCK

### 5.0 I/O PORTS

Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Additional information on I/O ports may be found in the "*PIC*<sup>®</sup> *Mid-Range MCU Family Reference Manual*" (DS33023).

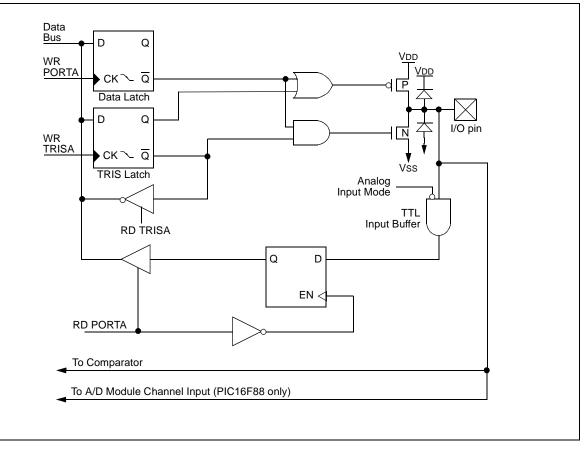

#### 5.1 PORTA and the TRISA Register

PORTA is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin).

| Note: | On    | а     | Power-on      | Reset,     | the | pins   |

|-------|-------|-------|---------------|------------|-----|--------|

|       | POR   | RTA<  | :4:0> are c   | configured | as  | analog |

|       | input | ts ar | nd read as 'o | 0'.        |     |        |

Reading the PORTA register, reads the status of the pins, whereas writing to it, will write to the port latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the port data latch.

Pin RA4 is multiplexed with the Timer0 module clock input. On PIC16F88 devices, it is also multiplexed with an analog input to become the RA4/AN4/T0CKI/C2OUT pin. The RA4/AN4/T0CKI/C2OUT pin is a Schmitt Trigger input and full CMOS output driver.

Pin RA5 is multiplexed with the Master Clear module input. The RA5/MCLR/VPP pin is a Schmitt Trigger input.

Pin RA6 is multiplexed with the oscillator module input and external oscillator output. Pin RA7 is multiplexed with the oscillator module input and external oscillator input. Pin RA6/OSC2/CLKO and pin RA7/OSC1/CLKI are Schmitt Trigger inputs and full CMOS output drivers.

Pins RA<1:0> are multiplexed with analog inputs. Pins RA<3:2> are multiplexed with analog inputs and comparator outputs. On PIC16F88 devices, pins RA<3:2> are also multiplexed with the VREF inputs. Pins RA<3:0> have TTL inputs and full CMOS output drivers.

| EXAMPLE 5-1: | INITIALIZING PORTA |

|--------------|--------------------|

|              |                    |

|                |                                            | ;<br>;<br>;                                              | select bank of PORTA<br>Initialize PORTA by<br>clearing output<br>data latches                  |

|----------------|--------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| MOVLW          | 0x00                                       | ;<br>;<br>;                                              | Select Bank of ANSEL<br>Configure all pins<br>as digital inputs                                 |

| MOVLW<br>MOVWF | 0xFF<br>TRISA                              | ;<br>;<br>;                                              | Value used to<br>initialize data<br>direction<br>Set RA<7:0> as inputs                          |

|                | CLRF<br>BANKSEL<br>MOVLW<br>MOVWF<br>MOVLW | BANKSEL ANSEL<br>MOVLW 0x00<br>MOVWF ANSEL<br>MOVLW 0xFF | CLRF PORTA ;<br>;<br>BANKSEL ANSEL ;<br>MOVLW 0x00 ;<br>MOVWF ANSEL ;<br>MOVLW 0xFF ;<br>;<br>; |

| Name                                | Bit#  | Buffer                 | Function                                                                                                                                           |

|-------------------------------------|-------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| RA0/AN0                             | bit 0 | TTL                    | Input/output or analog input.                                                                                                                      |

| RA1/AN1                             | bit 1 | TTL                    | Input/output or analog input.                                                                                                                      |

| RA2/AN2/CVREF/VREF- <sup>(2)</sup>  | bit 2 | TTL                    | Input/output, analog input, VREF- or comparator VREF output.                                                                                       |

| RA3/AN3/VREF+ <sup>(2)</sup> /C1OUT | bit 3 | TTL                    | Input/output, analog input, VREF+ or comparator output.                                                                                            |

| RA4/AN4 <sup>(2)</sup> /T0CKI/C2OUT | bit 4 | ST                     | Input/output, analog input, TMR0 external input or comparator output.                                                                              |

| RA5/MCLR/VPP                        | bit 5 | ST                     | Input, Master Clear (Reset) or programming voltage input.                                                                                          |

| RA6/OSC2/CLKO                       | bit 6 | ST                     | Input/output, connects to crystal or resonator, oscillator<br>output or 1/4 the frequency of OSC1 and denotes the<br>instruction cycle in RC mode. |

| RA7/OSC1/CLKI                       | bit 7 | ST/CMOS <sup>(1)</sup> | Input/output, connects to crystal or resonator or oscillator input.                                                                                |

#### TABLE 5-1: PORTA FUNCTIONS

**Legend:** TTL = TTL input, ST = Schmitt Trigger input

**Note 1:** This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

2: PIC16F88 only.

| TABLE 5-2: SU | JMMARY OF REGISTERS ASSOCIATED WITH PORTA |

|---------------|-------------------------------------------|

|---------------|-------------------------------------------|

| Address | Name                 | Bit 7  | Bit 6  | Bit 5                 | Bit 4 | Bit 3     | Bit 2     | Bit 1   | Bit 0     | Value on<br>POR, BOR                                 | Value on<br>all other<br>Resets              |

|---------|----------------------|--------|--------|-----------------------|-------|-----------|-----------|---------|-----------|------------------------------------------------------|----------------------------------------------|

| 05h     | PORTA                | RA7    | RA6    | RA5                   | RA4   | RA3       | RA2       | RA1     | RA0       | xxxx 0000 <sup>(1)</sup><br>xxx0 0000 <sup>(2)</sup> | uuuu 0000 <b>(1)</b><br>uuu0 0000 <b>(2)</b> |

| 85h     | TRISA                | TRISA7 | TRISA6 | TRISA5 <sup>(3)</sup> | PORTA | Data Dire | ection Re | egister | 1111 1111 | 1111 1111                                            |                                              |

| 9Fh     | ADCON1               | ADFM   | ADCS2  | VCFG1                 | VCFG0 | _         | _         | _       | _         | 0000                                                 | 0000                                         |

| 9Bh     | ANSEL <sup>(4)</sup> | —      | ANS6   | ANS5                  | ANS4  | ANS3      | ANS2      | ANS1    | ANS0      | -111 1111                                            | -111 1111                                    |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

**Note 1:** This value applies only to the PIC16F87.

2: This value applies only to the PIC16F88.

3: Pin 5 is an input only; the state of the TRISA5 bit has no effect and will always read '1'.

4: PIC16F88 device only.

#### FIGURE 5-1: BLOCK DIAGRAM OF RA0/AN0:RA1/AN1 PINS

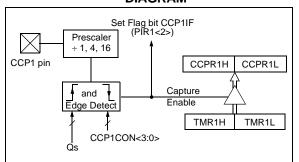

#### 9.1 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on the CCP1 pin. An event is defined as:

- Every falling edge

- Every rising edge

- Every 4th rising edge

- Every 16th rising edge

An event is selected by control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit, CCP1IF (PIR1<2>), is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value is overwritten by the new captured value.

#### 9.1.1 CCP PIN CONFIGURATION

In Capture mode, the CCP1 pin should be configured as an input by setting the TRISB<x> bit.

- **Note 1:** If the CCP1 pin is configured as an output, a write to the port can cause a capture condition.

- 2: The TRISB bit (0 or 3) is dependent upon the setting of configuration bit 12 (CCPMX).

### FIGURE 9-1:

#### CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 9.1.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

#### 9.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit CCP1IE (PIE1<2>) clear to avoid false interrupts and should clear the flag bit, CCP1IF, following any such change in operating mode.

#### 9.1.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. This means that any Reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore, the first capture may be from a non-zero prescaler. Example 9-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

#### EXAMPLE 9-1: CHANGING BETWEEN CAPTURE PRESCALERS

| ;Turn CCP module off                   |

|----------------------------------------|

| <code>I_PS</code> ;Load the W reg with |

| ;the new prescaler                     |

| ;move value and CCP ON                 |

| ;Load CCP1CON with this                |

| ;value                                 |

|                                        |

© 2002-2013 Microchip Technology Inc.

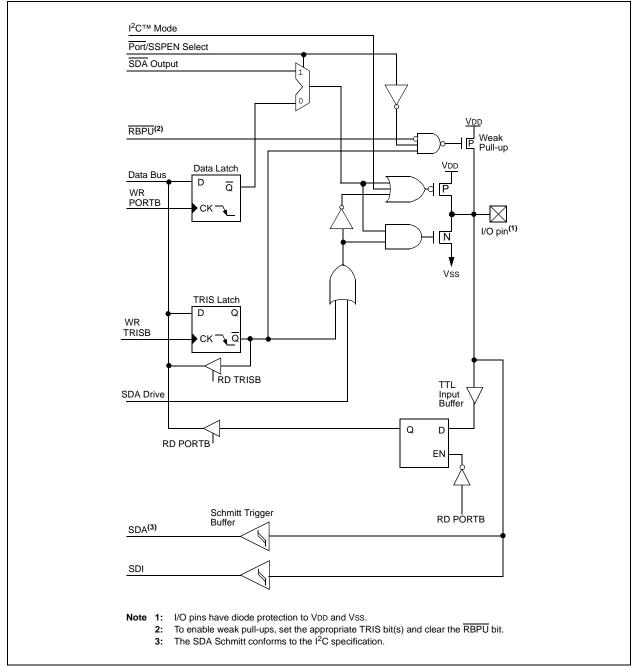

#### 10.3 SSP I<sup>2</sup>C Mode Operation

The SSP module in I<sup>2</sup>C mode fully implements all slave functions, except general call support and provides interrupts on Start and Stop bits in hardware to facilitate firmware implementations of the master functions. The SSP module implements the standard mode specifications, as well as 7-bit and 10-bit addressing.

Two pins are used for data transfer. These are the RB4/ SCK/SCL pin, which is the clock (SCL) and the RB1/ SDI/SDA pin, which is the data (SDA). The user must configure these pins as inputs or outputs through the TRISB<4,1> bits. To ensure proper communication of the I<sup>2</sup>C Slave mode, the TRIS bits (TRISx [SDA, SCL]) corresponding to the I<sup>2</sup>C pins must be set to '1'. If any TRIS bits (TRISx<7:0>) of the port containing the I<sup>2</sup>C pins (PORTx [SDA, SCL]) are changed in software during I<sup>2</sup>C communication using a Read-Modify-Write instruction (BSF, BCF), then the I<sup>2</sup>C mode may stop functioning properly and I<sup>2</sup>C communication may suspend. Do not change any of the TRISx bits (TRIS bits of the port containing the I<sup>2</sup>C pins) using the instruction BSF or BCF during I<sup>2</sup>C communication. If it is absolutely necessary to change the TRISx bits during communication, the following method can be used:

#### EXAMPLE 10-1:

| MOVF  | TRISC, W    | ; Example for an 18-pin part such as the PIC16F818/819              |

|-------|-------------|---------------------------------------------------------------------|

| IORLW | 0x18        | ; Ensures <4:3> bits are `11'                                       |

| ANDLW | B'11111001' | ; Sets <2:1> as output, but will not alter other bits               |

|       |             | ; User can use their own logic here, such as IORLW, XORLW and ANDLW |

| MOVWF | TRISC       |                                                                     |

The SSP module functions are enabled by setting SSP Enable bit, SSPEN (SSPCON<5>).

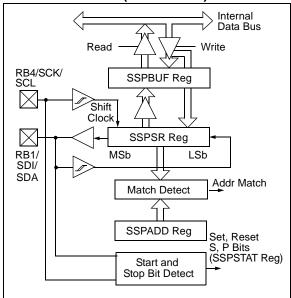

FIGURE 10-5: SSP BLOCK DIAGRAM (I<sup>2</sup>C<sup>™</sup> MODE)

The SSP module has five registers for I<sup>2</sup>C operation:

- SSP Control register (SSPCON)

- SSP Status register (SSPSTAT)

- Serial Receive/Transmit Buffer register (SSPBUF)

- SSP Shift register (SSPSR) Not directly accessible

- SSP Address register (SSPADD)

The SSPCON register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address) with Start and Stop bit interrupts enabled to support Firmware Controlled Master mode

- I<sup>2</sup>C Slave mode (10-bit address) with Start and Stop bit interrupts enabled to support Firmware Controlled Master mode

- I<sup>2</sup>C Firmware Controlled Master mode operation with Start and Stop bit interrupts enabled; slave is Idle

Selection of any  $I^2C$  mode, with the SSPEN bit set, forces the SCL and SDA pins to be open-drain, provided these pins are programmed to inputs by setting the appropriate TRISB bits. Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the  $I^2C$  module.

Additional information on SSP I<sup>2</sup>C operation may be found in the "*PIC*<sup>®</sup> *Mid-Range MCU Family Reference Manual*" (DS33023).

#### 12.6 A/D Operation During Sleep

The A/D module can operate during Sleep mode. This requires that the A/D clock source be set to RC (ADCS1:ADCS0 = 11). When the RC clock source is selected, the A/D module waits one instruction cycle before starting the conversion. This allows the SLEEP instruction to be executed which eliminates all digital switching noise from the conversion. When the conversion is completed, the GO/DONE bit will be cleared and the result loaded into the ADRES registers. If the A/D interrupt is enabled, the device will wake-up from Sleep. If the A/D interrupt is not enabled, the ADON bit will remain set.

When the A/D clock source is another clock option (not RC), a SLEEP instruction will cause the present conversion to be aborted and the A/D module to be turned off, though the ADON bit will remain set.

Turning off the A/D places the A/D module in its lowest current consumption state.

Note: For the A/D module to operate in Sleep, the A/D clock source must be set to RC (ADCS1:ADCS0 = 11). To perform an A/D conversion in Sleep, ensure the SLEEP instruction immediately follows the instruction that sets the GO/DONE bit.

#### 12.7 Effects of a Reset

A device Reset forces all registers to their Reset state. The A/D module is disabled and any conversion in progress is aborted. All A/D input pins are configured as analog inputs.

The value that is in the ADRESH:ADRESL registers is not modified for a Power-on Reset. The ADRESH:ADRESL registers will contain unknown data after a Power-on Reset.

#### 12.8 Use of the CCP Trigger

An A/D conversion can be started by the "special event trigger" of the CCP module. This requires that the CCP1M3:CCP1M0 bits (CCP1CON<3:0>) be programmed as '1011' and that the A/D module is enabled (ADON bit is set). When the trigger occurs, the GO/ DONE bit will be set, starting the A/D conversion and the Timer1 counter will be reset to zero. Timer1 is reset to automatically repeat the A/D acquisition period with software minimal overhead (moving the ADRESH: ADRESL to the desired location). The appropriate analog input channel must be selected and the minimum acquisition done before the "special event trigger" sets the GO/DONE bit (starts a conversion).

If the A/D module is not enabled (ADON is cleared), then the "special event trigger" will be ignored by the A/D module, but will still reset the Timer1 counter.

| Address                   | Name                              | Bit 7   | Bit 6               | Bit 5                 | Bit 4   | Bit 3     | Bit 2        | Bit 1     | Bit 0     | Value on<br>POR, BOR   | Value on<br>all other<br>Resets |

|---------------------------|-----------------------------------|---------|---------------------|-----------------------|---------|-----------|--------------|-----------|-----------|------------------------|---------------------------------|

| 0Bh, 8Bh<br>10Bh,<br>18Bh | INTCON                            | GIE     | PEIE                | TMR0IE                | INT0IE  | RBIE      | TMR0IF       | INTOIF    | RBIF      | 0000 000x              | 0000 000u                       |

| 0Ch                       | PIR1                              |         | ADIF <sup>(1)</sup> | RCIF                  | TXIF    | SSPIF     | CCP1IF       | TMR2IF    | TMR1IF    | -000 0000              | -000 0000                       |

| 8Ch                       | PIE1                              |         | ADIE <sup>(1)</sup> | RCIE                  | TXIE    | SSPIE     | CCP1IE       | TMR2IE    | TMR1IE    | -000 0000              | -000 0000                       |

| 1Eh                       | ADRESH <sup>(2)</sup>             | A/D Res | ult Regist          | er High Byt           | е       |           |              |           |           | XXXX XXXX              | uuuu uuuu                       |

| 9Eh                       | ADRESL <sup>(2)</sup>             | A/D Res | ult Regist          | er Low Byte           | e       |           |              |           |           | xxxx xxxx              | uuuu uuuu                       |

| 1Fh                       | ADCON0 <sup>(2)</sup>             | ADCS1   | ADCS0               | CHS2                  | CHS1    | CHS0      | GO/DONE      | _         | ADON      | 0000 00-0              | 0000 00-0                       |

| 9Fh                       | ADCON1 <sup>(2)</sup>             | ADFM    | ADCS2               | VCFG1                 | VCFG0   | _         | —            | _         | —         | 0000                   | 0000                            |

| 9Bh                       | ANSEL <sup>(2</sup>               | _       | ANS6                | ANS5                  | ANS4    | ANS3      | ANS2         | ANS1      | ANS0      | -111 1111              | -111 1111                       |

| 05h                       | PORTA<br>(PIC16F87)<br>(PIC16F88) | RA7     | RA6                 | RA5                   | RA4     | RA3       | RA2          | RA1       | RA0       | xxxx 0000<br>xxx0 0000 | uuuu 0000<br>uuu0 0000          |

| 05h, 106h                 | PORTB<br>(PIC16F87)<br>(PIC16F88) | RB7     | RB6                 | RB5                   | RB4     | RB3       | RB2          | RB1       | RB0       | xxxx xxxx<br>00xx xxxx | uuuu uuuu<br>00uu uuuu          |

| 85h                       | TRISA                             | TRISA7  | TRISA6              | TRISA5 <sup>(3)</sup> | PORTA I | Data Dire | ction Regist | 1111 1111 | 1111 1111 |                        |                                 |

| 86h, 186h                 | TRISB                             | TRISB7  | TRISB6              | TRISB5                | TRISB4  | TRISB3    | TRISB2       | TRISB1    | TRISB0    | 1111 1111              | 1111 1111                       |

TABLE 12-2:

REGISTERS/BITS ASSOCIATED WITH A/D

**Legend:** x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used for A/D conversion.

Note 1: This bit is only implemented on the PIC16F88. The bit will read '0' on the PIC16F87.

2: PIC16F88 only.

3: Pin 5 is an input only; the state of the TRISA5 bit has no effect and will always read '1'.

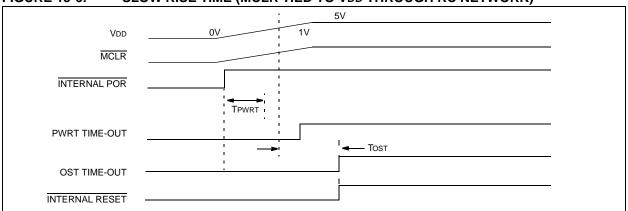

#### FIGURE 15-6: SLOW RISE TIME (MCLR TIED TO VDD THROUGH RC NETWORK)

#### 15.10 Interrupts

The PIC16F87/88 has up to 12 sources of interrupt. The Interrupt Control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

| Note: | Individual                             | interro    | upt | flag | bits | are | set   |  |  |  |

|-------|----------------------------------------|------------|-----|------|------|-----|-------|--|--|--|

|       | regardless                             | of the sta |     | sta  | tus  | of  | their |  |  |  |

|       | corresponding mask bit or the GIE bit. |            |     |      |      |     |       |  |  |  |

A global interrupt enable bit, GIE (INTCON<7>), enables (if set) all unmasked interrupts, or disables (if cleared) all interrupts. When bit GIE is enabled and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt bits are set regardless of the status of the GIE bit. The GIE bit is cleared on Reset.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine, as well as sets the GIE bit which re-enables interrupts.

The RB0/INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flags are contained in the Special Function Register, PIR1. The corresponding interrupt enable bits are contained in Special Function Register, PIE1 and the peripheral interrupt enable bit is contained in Special Function Register, INTCON.

When an interrupt is serviced, the GIE bit is cleared to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends on when the interrupt event occurs, relative to the current Q cycle. The latency is the same for one or two cycle instructions. Individual interrupt flag bits are set regardless of the status of their corresponding mask bit, PEIE bit or the GIE bit.

#### 15.10.1 INT INTERRUPT

External interrupt on the RB0/INT pin is edge-triggered, either rising if bit INTEDG (OPTION\_REG<6>) is set, or falling if the INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, flag bit, INT0IF (INTCON<1>), is set. This interrupt can be disabled by clearing enable bit INT0IE (INTCON<4>). Flag bit INT0IF must be cleared in software in the Interrupt Service Routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from Sleep, if bit INT0IE was set prior to going into Sleep. The status of global interrupt enable bit GIE decides whether or not the processor branches to the interrupt vector, following wake-up. See **Section 15.13 "Power-Down Mode (Sleep)**" for details on Sleep mode.

#### 15.10.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit TMR0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit TMR0IE (INTCON<5>), see Section 6.0 "Timer0 Module".

#### 15.10.3 PORTB INTCON CHANGE

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit RBIE (INTCON<4>), see Section 3.2 "EECON1 and EECON2 Registers".

#### 15.11 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (i.e., W, STATUS registers).

Since the upper 16 bytes of each bank are common in the PIC16F87/88 devices, temporary holding registers W\_TEMP, STATUS\_TEMP and PCLATH\_TEMP should be placed in here. These 16 locations don't require banking and therefore, make it easier for context save and restore. The same code shown in Example 15-1 can be used.

| ſ | MOVWF  | W_TEMP         | ;Copy W to TEMP register                                |

|---|--------|----------------|---------------------------------------------------------|

|   | SWAPF  | STATUS, W      | ;Swap status to be saved into W                         |

|   | CLRF   | STATUS         | ;bank 0, regardless of current bank, Clears IRP,RP1,RP0 |

|   | MOVWF  | STATUS_TEMP    | ;Save status to bank zero STATUS_TEMP register          |

|   | MOVF   | PCLATH, W      | ;Only required if using page 1                          |

|   | MOVWF  | PCLATH_TEMP    | ;Save PCLATH into W                                     |

|   | CLRF   | PCLATH         | ;Page zero, regardless of current page                  |

|   | :      |                |                                                         |

|   | :(ISR) |                | ;(Insert user code here)                                |

|   | :      |                |                                                         |

|   | MOVF   | PCLATH_TEMP, W | ;Restore PCLATH                                         |

|   | MOVWF  | PCLATH         | ;Move W into PCLATH                                     |

|   | SWAPF  | STATUS_TEMP, W | ;Swap STATUS_TEMP register into W                       |

|   |        |                | ;(sets bank to original state)                          |

|   | MOVWF  | STATUS         | ;Move W into STATUS register                            |

|   | SWAPF  | W_TEMP, F      | ;Swap W_TEMP                                            |

|   | SWAPF  | W_TEMP, W      | ;Swap W_TEMP into W                                     |

|   |        |                |                                                         |

#### 15.13.1 WAKE-UP FROM SLEEP

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on MCLR pin.

- 2. Watchdog Timer wake-up (if WDT was enabled).

- 3. Interrupt from INT pin, RB port change or a peripheral interrupt.

External MCLR Reset will cause a device Reset. All other events are considered a continuation of program execution and cause a "wake-up". The TO and PD bits in the STATUS register can be used to determine the cause of the device Reset. The PD bit, which is <u>set</u> on power-up, is cleared when Sleep is invoked. The TO bit is cleared if a WDT time-out occurred and caused wake-up.

The following peripheral interrupts can wake the device from Sleep:

- 1. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 2. CCP Capture mode interrupt.

- 3. Special event trigger (Timer1 in Asynchronous mode using an external clock).

- 4. SSP (Start/Stop) bit detect interrupt.

- 5. SSP transmit or receive in Slave mode (SPI/I<sup>2</sup>C).

- 6. A/D conversion (when A/D clock source is RC).

- 7. EEPROM write operation completion.

- 8. Comparator output changes state.

- 9. AUSART RX or TX (Synchronous Slave mode).

Other peripherals cannot generate interrupts, since during Sleep, no on-chip clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding

interrupt enable bit must be set (enabled). Wake-up occurs regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

#### 15.13.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs before the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT prescaler and postscaler (if enabled) will not be cleared, the TO bit will not be set and the PD bit will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake-up from Sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT prescaler and postscaler (if enabled) will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

| OSC1                                 | Q1   Q2   Q3   Q4                            | Q1 Q2 Q3 Q4                                            | Q1                                             | -                    | Q1 Q2 Q3 Q4                   | Q1 Q2 Q3 Q4;     | Q1 Q2 Q3 Q4; |

|--------------------------------------|----------------------------------------------|--------------------------------------------------------|------------------------------------------------|----------------------|-------------------------------|------------------|--------------|

| CLKO <sup>(4)</sup>                  | \                                            | /                                                      | Tost <sup>(2)</sup>                            | ·/                   | \/                            | \'               |              |

| INT pin                              |                                              |                                                        |                                                | 1                    | ı ı<br>ı ı                    | 1                |              |

| INT0IF Flag<br>(INTCON<1>            | >)                                           |                                                        |                                                | 1<br><br>1<br>1      | Interrupt Latency<br>(Note 2) | ו<br>            |              |

| GIE bit <sup>(3)</sup><br>(INTCON<7> | >)                                           |                                                        | Processor in<br>Sleep                          | <br> <br> <br>       | · · · · ·                     | ו<br>ו<br>ו<br>ו |              |

| INSTRUCTIO                           | ON FLOW                                      |                                                        |                                                | 1                    |                               | 1                |              |

| PC                                   | с <u>Х РС</u>                                | ( PC + 1                                               | X PC + 2                                       | X PC + 2             | X PC + 2                      | X 0004h          | (0005h       |

| Instruction<br>Fetched               | {Inst(PC) = Sleep                            | Inst(PC + 1)                                           | 1<br>1<br>1                                    | Inst(PC + 2)         | · · ·                         | Inst(0004h)      | Inst(0005h)  |

| Instruction<br>Executed              | { Inst(PC - 1)                               | Sleep                                                  | 1<br>1<br>1                                    | Inst(PC + 1)         | Dummy Cycle                   | Dummy Cycle      | Inst(0004h)  |

| 2:<br>3:                             | GIE = 1 assumed. In<br>If GIE = 0, execution | drawing not to scanthis case, after will continue in-l | ale). This delay will no wake-up, the processo | or jumps to the inte | errupt routine.               |                  |              |

#### FIGURE 15-12: WAKE-UP FROM SLEEP THROUGH INTERRUPT<sup>(1)</sup>

| IORLW            | Inclusive OR Literal with W                                                                                               | MOVLW            | Move Literal to W                                                                                 |

|------------------|---------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                                  | Syntax:          | [ <i>label</i> ] MOVLW k                                                                          |

| Operands:        | $0 \le k \le 255$                                                                                                         | Operands:        | $0 \le k \le 255$                                                                                 |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                              | Operation:       | $k \rightarrow (W)$                                                                               |

| Status Affected: | Z                                                                                                                         | Status Affected: | None                                                                                              |

| Description:     | The contents of the W register are<br>OR'ed with the eight-bit literal 'k'.<br>The result is placed in the W<br>register. | Description:     | The eight-bit literal 'k' is loaded<br>into W register. The don't cares<br>will assemble as '0's. |

| IORWF            | Inclusive OR W with f                                                                                                                                                 |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] IORWF f,d                                                                                                                                                     |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                           |  |  |  |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                              |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                     |  |  |  |  |  |

| Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' = 0, the result is<br>placed in the W register. If 'd' = 1,<br>the result is placed back in<br>register 'f'. |  |  |  |  |  |

| MOVWF            | Move W to f                                |  |  |  |  |  |

|------------------|--------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVWF f                   |  |  |  |  |  |

| Operands:        | $0 \leq f \leq 127$                        |  |  |  |  |  |

| Operation:       | $(W) \rightarrow (f)$                      |  |  |  |  |  |

| Status Affected: | None                                       |  |  |  |  |  |

| Description:     | Move data from W register to register 'f'. |  |  |  |  |  |

| MOVF             | Move f                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] MOVF f,d                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>d $\in$ [0,1]                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| Operation:       | (f) $\rightarrow$ (destination)                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>moved to a destination dependant<br>upon the status of 'd'. If 'd' = 0,<br>the destination is W register. If<br>'d' = 1, the destination is file<br>register 'f' itself. 'd' = 1 is useful to<br>test a file register, since status<br>flag Z is affected. |  |  |  |  |  |  |

| NOP              | No Operation  |  |  |  |  |  |

|------------------|---------------|--|--|--|--|--|

| Syntax:          | [label] NOP   |  |  |  |  |  |

| Operands:        | None          |  |  |  |  |  |

| Operation:       | No operation  |  |  |  |  |  |

| Status Affected: | None          |  |  |  |  |  |

| Description:     | No operation. |  |  |  |  |  |

#### 18.2 DC Characteristics: Power-Down and Supply Current PIC16F87/88 (Industrial, Extended) PIC16LF87/88 (Industrial) (Continued)

| PIC16LF<br>(Indu | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |     |       |            |        |            |                                           |

|------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|-------|------------|--------|------------|-------------------------------------------|

| PIC16F8<br>(Indu |                                                                                                                                    |     |       |            |        |            |                                           |

| Param<br>No.     | Тур                                                                                                                                | Max | Units | Conditions |        |            |                                           |

|                  | Supply Current (IDD) <sup>(2,3)</sup>                                                                                              |     |       |            |        |            |                                           |

|                  | PIC16LF87/88                                                                                                                       | 8   | 20    | μA         | -40°C  |            |                                           |

|                  |                                                                                                                                    | 7   | 15    | μA         | +25°C  | VDD = 2.0V |                                           |

|                  |                                                                                                                                    | 7   | 15    | μΑ         | +85°C  |            |                                           |

|                  | PIC16LF87/88                                                                                                                       | 16  | 30    | μΑ         | -40°C  |            |                                           |

|                  |                                                                                                                                    | 14  | 25    | μΑ         | +25°C  | VDD = 3.0V | Fosc = 31.25 kHz<br>( <b>RC RUN</b> mode, |

|                  |                                                                                                                                    | 14  | 25    | μA         | +85°C  |            | Internal RC Oscillator)                   |

|                  | All devices                                                                                                                        | 32  | 40    | μΑ         | -40°C  |            |                                           |

|                  |                                                                                                                                    | 29  | 35    | μΑ         | +25°C  |            |                                           |

|                  |                                                                                                                                    | 29  | 35    | μA         | +85°C  | VDD = 0.0V |                                           |

|                  | Extended devices                                                                                                                   | 35  | 45    | μΑ         | +125°C |            |                                           |

|                  | PIC16LF87/88                                                                                                                       | 132 | 160   | μΑ         | -40°C  | _          |                                           |

|                  |                                                                                                                                    | 126 | 155   | μΑ         | +25°C  | VDD = 2.0V |                                           |

|                  |                                                                                                                                    | 126 | 155   | μA         | +85°C  |            |                                           |

|                  | PIC16LF87/88                                                                                                                       | 260 | 310   | μΑ         | -40°C  |            |                                           |

|                  |                                                                                                                                    | 230 | 300   | μΑ         | +25°C  | VDD = 3.0V | Fosc = 1 MHz<br>( <b>RC RUN</b> mode,     |

|                  |                                                                                                                                    | 230 | 300   | μΑ         | +85°C  |            | Internal RC Oscillator)                   |

|                  | All devices                                                                                                                        | 560 | 690   | μΑ         | -40°C  | VDD = 5.0V |                                           |

|                  |                                                                                                                                    | 500 | 650   | μΑ         | +25°C  |            |                                           |

|                  |                                                                                                                                    | 500 | 650   | μΑ         | +85°C  |            |                                           |

|                  | Extended devices                                                                                                                   | 570 | 710   | μA         | +125°C |            |                                           |

Legend: Shading of rows is to assist in readability of the table.

**Note 1:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or VSs and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;

- MCLR = VDD; WDT enabled/disabled as specified.

- 3: For RC oscillator configurations, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

#### 18.4 DC Characteristics: PIC16F87/88 (Industrial, Extended) PIC16LF87/88 (Industrial)

| DC CH/       | ARACT | ERISTICS                           | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extendedOperating voltage VDD range as described in DC Specification,Section 18.1 "DC Characteristics: Supply Voltage". |      |          |       |                                                                          |  |

|--------------|-------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|-------|--------------------------------------------------------------------------|--|

| Param<br>No. | Sym   | Characteristic                     | Min                                                                                                                                                                                                                                                                                                    | Тур† | Max      | Units | Conditions                                                               |  |

|              | VIL   | Input Low Voltage                  |                                                                                                                                                                                                                                                                                                        |      |          |       |                                                                          |  |

|              |       | I/O ports:                         |                                                                                                                                                                                                                                                                                                        |      |          |       |                                                                          |  |

| D030         |       | with TTL buffer                    | Vss                                                                                                                                                                                                                                                                                                    | _    | 0.15 Vdd | V     | For entire VDD range                                                     |  |

| D030A        |       |                                    | Vss                                                                                                                                                                                                                                                                                                    | _    | 0.8V     | V     | $4.5V \le VDD \le 5.5V$                                                  |  |

| D031         |       | with Schmitt Trigger buffer        | Vss                                                                                                                                                                                                                                                                                                    | _    | 0.2 Vdd  | V     |                                                                          |  |

| D032         |       | MCLR, OSC1 (in RC mode)            | Vss                                                                                                                                                                                                                                                                                                    | _    | 0.2 Vdd  | V     | (Note 1)                                                                 |  |

| D033         |       | OSC1 (in XT and LP mode)           | Vss                                                                                                                                                                                                                                                                                                    | _    | 0.3V     | V     |                                                                          |  |

|              |       | OSC1 (in HS mode)                  | Vss                                                                                                                                                                                                                                                                                                    | _    | 0.3 Vdd  | V     |                                                                          |  |

|              |       | Ports RB1 and RB4:                 |                                                                                                                                                                                                                                                                                                        |      |          |       |                                                                          |  |

| D034         |       | with Schmitt Trigger buffer        | Vss                                                                                                                                                                                                                                                                                                    | _    | 0.3 Vdd  | V     | For entire VDD range                                                     |  |

|              | Vін   | Input High Voltage                 |                                                                                                                                                                                                                                                                                                        |      |          |       |                                                                          |  |

|              |       | I/O ports:                         |                                                                                                                                                                                                                                                                                                        |      |          |       |                                                                          |  |

| D040         |       | with TTL buffer                    | 2.0                                                                                                                                                                                                                                                                                                    | —    | Vdd      | V     | $4.5V \leq V\text{DD} \leq 5.5V$                                         |  |

| D040A        |       |                                    | 0.25 VDD + 0.8V                                                                                                                                                                                                                                                                                        | —    | Vdd      | V     | For entire VDD range                                                     |  |

| D041         |       | with Schmitt Trigger buffer        | 0.8 Vdd                                                                                                                                                                                                                                                                                                | —    | Vdd      | V     | For entire VDD range                                                     |  |

| D042         |       | MCLR                               | 0.8 Vdd                                                                                                                                                                                                                                                                                                | _    | Vdd      | V     |                                                                          |  |

| D042A        |       | OSC1 (in XT and LP mode)           | 1.6V                                                                                                                                                                                                                                                                                                   | —    | Vdd      | V     |                                                                          |  |

|              |       | OSC1 (in HS mode)                  | 0.7 Vdd                                                                                                                                                                                                                                                                                                | —    | Vdd      | V     |                                                                          |  |

| D043         |       | OSC1 (in RC mode)                  | 0.9 Vdd                                                                                                                                                                                                                                                                                                | —    | Vdd      | V     | (Note 1)                                                                 |  |

|              |       | Ports RB1 and RB4:                 |                                                                                                                                                                                                                                                                                                        |      |          |       |                                                                          |  |

| D044         |       | with Schmitt Trigger buffer        | 0.7 Vdd                                                                                                                                                                                                                                                                                                |      | Vdd      | V     | For entire VDD range                                                     |  |

| D070         | Ipurb | PORTB Weak Pull-up Current         | 50                                                                                                                                                                                                                                                                                                     | 250  | 400      | μA    | VDD = 5V, VPIN = VSS                                                     |  |

|              | lı∟   | Input Leakage Current (Notes 2, 3) |                                                                                                                                                                                                                                                                                                        |      |          |       |                                                                          |  |

| D060         |       | I/O ports                          | —                                                                                                                                                                                                                                                                                                      | _    | ±1       | μA    | $Vss \le VPIN \le VDD, pin at high-impedance$                            |  |

| D061         |       | MCLR                               | —                                                                                                                                                                                                                                                                                                      | _    | ±5       | μA    | $Vss \leq VPIN \leq VDD$                                                 |  |

| D063         |       | OSC1                               | —                                                                                                                                                                                                                                                                                                      | _    | ±5       | μΑ    | Vss $\leq$ VPIN $\leq$ VDD, XT, HS<br>and LP oscillator<br>configuration |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1/CLKI pin is a Schmitt Trigger input. It is not recommended that the PIC16F87/88 be driven with external clock in RC mode.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- **3:** Negative current is defined as current sourced by the pin.

| Param<br>No. | Symbol | Characte                      | Min          | Тур†     | Max      | Units | Conditions |                                                                                                                                                                                                                              |

|--------------|--------|-------------------------------|--------------|----------|----------|-------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

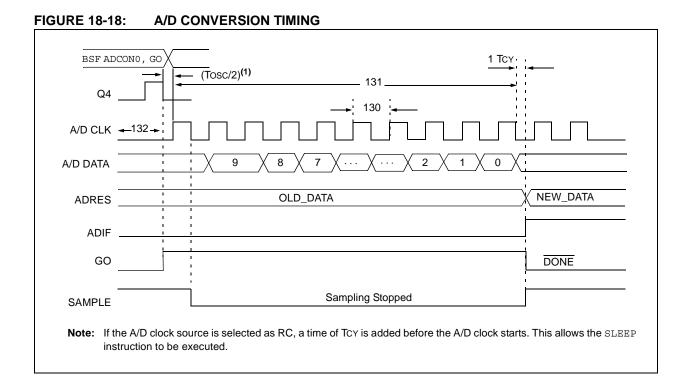

| 130          | Tad    | A/D Clock Period              | PIC16F87/88  | 1.6      | _        | _     | μS         | Tosc based, VREF $\geq$ 3.0V                                                                                                                                                                                                 |

|              |        |                               | PIC16LF87/88 | 3.0      | _        | _     | μS         | Tosc based, VREF $\ge 2.0V$                                                                                                                                                                                                  |

|              |        |                               | PIC16F87/88  | 2.0      | 4.0      | 6.0   | μS         | A/D RC mode                                                                                                                                                                                                                  |

|              |        |                               | PIC16LF87/88 | 3.0      | 6.0      | 9.0   | μS         | A/D RC mode                                                                                                                                                                                                                  |

| 131          | TCNV   | Conversion Time (not (Note 1) |              | —        | 12       | TAD   |            |                                                                                                                                                                                                                              |

| 132          | TACQ   | Acquisition Time              |              | (Note 2) | 40       | _     | μS         |                                                                                                                                                                                                                              |

|              |        |                               |              | 10*      | _        | _     | μs         | The minimum time is the<br>amplifier settling time. This may<br>be used if the "new" input<br>voltage has not changed by<br>more than 1 LSb (i.e., 5.0 mV @<br>5.12V) from the last sampled<br>voltage (as stated on CHOLD). |

| 134          | TGO    | Q4 to A/D Clock Start         |              |          | Tosc/2 § |       | _          | If the A/D clock source is<br>selected as RC, a time of TCY is<br>added before the A/D clock<br>starts. This allows the SLEEP<br>instruction to be executed.                                                                 |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification ensured by design.

Note 1: ADRES registers may be read on the following TCY cycle.

2: See Section 12.1 "A/D Acquisition Requirements" for minimum conditions.

NOTES:

### Worldwide Sales and Service

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC