# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 16                                                                      |

| Program Memory Size        | 7KB (4K x 14)                                                           |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 256 x 8                                                                 |

| RAM Size                   | 368 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                               |

| Data Converters            | -                                                                       |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                          |

| Supplier Device Package    | 20-SSOP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f87-i-ss |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name                    | PDIP/<br>SOIC<br>Pin# | SSOP<br>Pin# | QFN<br>Pin# | I/O/P<br>Type | Buffer<br>Type    | Description                                                                                                        |

|-----------------------------|-----------------------|--------------|-------------|---------------|-------------------|--------------------------------------------------------------------------------------------------------------------|

|                             |                       |              |             |               |                   | PORTB is a bidirectional I/O port. PORTB can be<br>software programmed for internal weak pull-up on all<br>inputs. |

| RB0/INT/CCP1 <sup>(5)</sup> | 6                     | 7            | 7           |               |                   |                                                                                                                    |

| RB0                         |                       |              |             | I/O           | TTL               | Bidirectional I/O pin.                                                                                             |

| INT                         |                       |              |             | I             | ST <sup>(1)</sup> | External interrupt pin.                                                                                            |

| CCP1                        |                       |              |             | I/O           | ST                | Capture input, Compare output, PWM output.                                                                         |

| RB1/SDI/SDA                 | 7                     | 8            | 8           |               |                   |                                                                                                                    |

| RB1<br>SDI                  |                       |              |             | I/O<br>I      | TTL<br>ST         | Bidirectional I/O pin.<br>SPI data in.                                                                             |

| SDA                         |                       |              |             | 1/O           | ST                | $I^2 C^{TM}$ data.                                                                                                 |

| RB2/SDO/RX/DT               | 8                     | 9            | 9           | 1/0           | 01                |                                                                                                                    |

| RB2                         | 0                     | 9            | 9           | I/O           | TTL               | Bidirectional I/O pin.                                                                                             |

| SDO                         |                       |              |             | 0             | ST                | SPI data out.                                                                                                      |

| RX                          |                       |              |             | I             |                   | AUSART asynchronous receive.                                                                                       |

| DT                          |                       |              |             | I/O           |                   | AUSART synchronous detect.                                                                                         |

| RB3/PGM/CCP1 <sup>(5)</sup> | 9                     | 10           | 10          |               |                   |                                                                                                                    |

| RB3                         |                       |              |             | I/O           | TTL               | Bidirectional I/O pin.                                                                                             |

| PGM                         |                       |              |             | I/O           | ST                | Low-Voltage ICSP™ Programming enable pin.                                                                          |

| CCP1                        |                       |              |             | I             | ST                | Capture input, Compare output, PWM output.                                                                         |

| RB4/SCK/SCL                 | 10                    | 11           | 12          |               |                   |                                                                                                                    |

| RB4<br>SCK                  |                       |              |             | 1/0<br>1/0    | TTL<br>ST         | Bidirectional I/O pin. Interrupt-on-change pin.<br>Synchronous serial clock input/output for SPI.                  |

| SCL                         |                       |              |             | 1/0           | ST                | Synchronous serial clock input/output for SP1.                                                                     |

| RB5/SS/TX/CK                | 11                    | 12           | 13          | •             | 01                | Cynonionous senarolook inpartor r C.                                                                               |

| RB5                         | 1 11                  | 12           | 15          | I/O           | TTL               | Bidirectional I/O pin. Interrupt-on-change pin.                                                                    |

| SS                          |                       |              |             | 1/0           | TTL               | Slave select for SPI in Slave mode.                                                                                |

| TX                          |                       |              |             | 0             |                   | AUSART asynchronous transmit.                                                                                      |

| СК                          |                       |              |             | I/O           |                   | AUSART synchronous clock.                                                                                          |

| RB6/AN5/PGC/T1OSO/          | 12                    | 13           | 15          |               |                   |                                                                                                                    |

| T1CKI                       |                       |              |             |               |                   |                                                                                                                    |

|                             |                       |              |             | I/O           | TTL               | Bidirectional I/O pin. Interrupt-on-change pin.                                                                    |

| AN5 <sup>(4)</sup><br>PGC   |                       |              |             | I<br>I/O      | ST <sup>(2)</sup> | Analog input channel 5.<br>In-Circuit Debugger and programming clock pin.                                          |

| T10S0                       |                       |              |             | 0             | ST                | Timer1 oscillator output.                                                                                          |

| T1CKI                       |                       |              |             | I             | ST                | Timer1 external clock input.                                                                                       |

| RB7/AN6/PGD/T1OSI           | 13                    | 14           | 16          |               |                   |                                                                                                                    |

| RB7                         |                       | 17           | 10          | I/O           | TTL               | Bidirectional I/O pin. Interrupt-on-change pin.                                                                    |

| AN6 <sup>(4)</sup>          |                       |              |             | I             |                   | Analog input channel 6.                                                                                            |

| PGD                         |                       |              |             | I             | ST <sup>(2)</sup> | In-Circuit Debugger and ICSP programming data pi                                                                   |

| T1OSI                       |                       |              |             | Ι             | ST                | Timer1 oscillator input.                                                                                           |

| Vss                         | 5                     | 5, 6         | 3, 5        | Р             | -                 | Ground reference for logic and I/O pins.                                                                           |

| VDD                         | 14                    | 15, 16       | 17, 19      | Р             | -                 | Positive supply for logic and I/O pins.                                                                            |

| TABLE 1-2: | PIC16F87/88 PINOUT DESCRIPTION ( | (CONTINUED) |

|------------|----------------------------------|-------------|

|            |                                  |             |

- = Not used TTL = TTL Input ST = Schmitt Trigger Input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

4: PIC16F88 devices only.

5: The CCP1 pin is determined by the CCPMX bit in Configuration Word 1 register.

#### 2.2.2.1 STATUS Register

The STATUS register, shown in Register 2-1, contains the arithmetic status of the ALU, the Reset status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as '000u uluu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register because these instructions do not affect the Z, C or DC bits from the STATUS register. For other instructions not affecting any Status bits, see Section 16.0 "Instruction Set Summary".

Note: The C and DC bits operate as a borrow and digit borrow bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

### REGISTER 2-1: STATUS: ARITHMETIC STATUS REGISTER (ADDRESS 03h, 83h, 103h, 183h)

|         | R/W-0                   | R/W-0                                                     | R/W-0         | R-1            | R-1           | R/W-x                     | R/W-x          | R/W-x     |  |  |  |  |

|---------|-------------------------|-----------------------------------------------------------|---------------|----------------|---------------|---------------------------|----------------|-----------|--|--|--|--|

|         | IRP                     | RP1                                                       | RP0           | TO             | PD            | Z                         | DC             | С         |  |  |  |  |

|         | bit 7                   |                                                           |               |                |               |                           |                | bit 0     |  |  |  |  |

| bit 7   | 1 = Bank                | ster Bank Sel<br>2, 3 (100h-1F<br>0, 1 (00h-FFt           | Fh)           | for indirect a | ddressing)    |                           |                |           |  |  |  |  |

| bit 6-5 | 11 = Bank 3 (180h-1FFh) |                                                           |               |                |               |                           |                |           |  |  |  |  |

|         | 01 = Bank<br>00 = Bank  | 2 (100h-17F<br>1 (80h-FFh)<br>0 (00h-7Fh)<br>is 128 bytes |               |                |               |                           |                |           |  |  |  |  |

| bit 4   | TO: Time-               | out bit                                                   |               |                |               |                           |                |           |  |  |  |  |

|         |                         | power-up, CL                                              |               | tion or SLEE   | P instruction | n                         |                |           |  |  |  |  |

| bit 3   | PD: Powe                | r-Down bit                                                |               |                |               |                           |                |           |  |  |  |  |

|         |                         | power-up or b<br>ecution of the                           |               |                |               |                           |                |           |  |  |  |  |

| bit 2   | Z: Zero bit             | t                                                         |               |                |               |                           |                |           |  |  |  |  |

|         |                         | esult of an ari<br>esult of an ari                        |               |                |               |                           |                |           |  |  |  |  |

| bit 1   | DC: Digit               | carry/borrow b                                            | oit (Addwf, A | DDLW, SUBLI    | and SUBW      | F instructio              | ns) <b>(1)</b> |           |  |  |  |  |

|         |                         | ry-out from the<br>arry-out from t                        |               |                |               | red                       |                |           |  |  |  |  |

| bit 0   | C: Carry/b              | orrow bit (AD                                             | DWF, ADDLW,   | SUBLW and      | SUBWF instr   | uctions) <sup>(1,2)</sup> | )              |           |  |  |  |  |

|         |                         | ry-out from the                                           | 0             |                |               |                           |                |           |  |  |  |  |

|         | Note 1:                 | For borrow, t complement                                  |               |                | subtractior   | n is execute              | d by adding    | the two's |  |  |  |  |

|         | 2:                      | For rotate (R:<br>bit of the sou                          |               | ructions, this | bit is loade  | d with eithe              | r the high or  | low-order |  |  |  |  |

|         | Logondy                 |                                                           |               |                |               |                           |                |           |  |  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### 2.2.2.3 INTCON Register

The INTCON register is a readable and writable register that contains various enable and flag bits for the TMR0 register overflow, RB Port change and External RB0/INT pin interrupts. Note: Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

### REGISTER 2-3: INTCON: INTERRUPT CONTROL REGISTER (ADDRESS 0Bh, 8Bh, 10Bh, 18Bh)

| R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0 | R/W-0  | R/W-0  | R/W-x |

|-------|-------|--------|--------|-------|--------|--------|-------|

| GIE   | PEIE  | TMR0IE | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF  |

| bit 7 |       |        |        |       |        |        | bit 0 |

| bit 7  | GIE: Global Interrupt Enable bit                                                                                |

|--------|-----------------------------------------------------------------------------------------------------------------|

|        | 1 = Enables all unmasked interrupts                                                                             |

|        | 0 = Disables all interrupts                                                                                     |

| bit 6  | PEIE: Peripheral Interrupt Enable bit                                                                           |

|        | 1 = Enables all unmasked peripheral interrupts                                                                  |

|        | <ul> <li>0 = Disables all peripheral interrupts</li> </ul>                                                      |

| bit 5  | TMR0IE: TMR0 Overflow Interrupt Enable bit                                                                      |

|        | 1 = Enables the TMR0 interrupt                                                                                  |

|        | 0 = Disables the TMR0 interrupt                                                                                 |

| bit 4  | INTOIE: RB0/INT External Interrupt Enable bit                                                                   |

|        | 1 = Enables the RB0/INT external interrupt                                                                      |

| 1.14.0 | 0 = Disables the RB0/INT external interrupt                                                                     |

| bit 3  | <b>RBIE:</b> RB Port Change Interrupt Enable bit                                                                |

|        | <ul> <li>1 = Enables the RB port change interrupt</li> <li>0 = Disables the RB port change interrupt</li> </ul> |

| bit 2  | TMR0IF: TMR0 Overflow Interrupt Flag bit                                                                        |

| 511 2  | 1 = TMR0 register has overflowed (must be cleared in software)                                                  |

|        | 0 = TMR0 register did not overflow                                                                              |

| bit 1  | INTOIF: RB0/INT External Interrupt Flag bit                                                                     |

|        | 1 = The RB0/INT external interrupt occurred (must be cleared in software)                                       |

|        | 0 = The RB0/INT external interrupt did not occur                                                                |

| bit 0  | RBIF: RB Port Change Interrupt Flag bit                                                                         |

|        | A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch                    |

|        | condition and allow flag bit RBIF to be cleared.                                                                |

|        | 1 = At least one of the RB7:RB4 pins changed state (must be cleared in software)                                |

|        | 0 = None of the RB7:RB4 pins have changed state                                                                 |

|        |                                                                                                                 |

|        | Legend:                                                                                                         |

|        | D. Deadable bit W. Writeble bit II. Unimplemented bit read as (0)                                               |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|                   |                  |                      |                    |

#### 4.7.3 SEC\_RUN/RC\_RUN TO PRIMARY CLOCK SOURCE

When switching from a SEC\_RUN or RC\_RUN mode back to the primary system clock, following a change of SCS<1:0> to '00', the sequence of events that takes place will depend upon the value of the FOSC bits in the Configuration register. If the primary clock source is configured as a crystal (HS, XT or LP), then the transition will take place after 1024 clock cycles. This is necessary because the crystal oscillator has been powered down until the time of the transition. In order to provide the system with a reliable clock when the changeover has occurred, the clock will not be released to the changeover circuit until the 1024 count has expired.

During the oscillator start-up time, the system clock comes from the current system clock. Instruction execution and/or peripheral operation continues using the currently selected oscillator as the CPU clock source, until the necessary clock count has expired, to ensure that the primary system clock is stable.

To know when the OST has expired, the OSTS bit should be monitored. OSTS = 1 indicates that the Oscillator Start-up Timer has timed out and the system clock comes from the primary clock source.

Following the oscillator start-up time, the internal Q clocks are held in the Q1 state until eight falling edge clocks are counted from the primary system clock. The clock input to the Q clocks is then released and operation resumes with the primary system clock determined by the FOSC bits (see Figure 4-10).

When in SEC\_RUN mode, the act of clearing the T1OSCEN bit in the T1CON register will cause SCS<0> to be cleared, which causes the SCS<1:0> bits to revert to '00' or '10' depending on what SCS<1> is. Although the T1OSCEN bit was cleared, T1OSC will be enabled and instruction execution will continue until the OST time-out for the main system clock is complete. At that time, the system clock will switch from the T1OSC to the primary clock or the INTRC. Following this, the T1 oscillator will be shut down.

Note: If the primary system clock is either RC or EC, an internal delay timer (5-10 μs) will suspend operation after exiting Secondary Clock mode to allow the CPU to become ready for code execution.

## 4.7.3.1 Returning to Primary Clock Source Sequence

Changing back to the primary oscillator from SEC\_RUN or RC\_RUN can be accomplished by either changing SCS<1:0> to '00', or clearing the T1OSCEN bit in the T1CON register (if T1OSC was the secondary clock).

The sequence of events that follows is the same for both modes:

- If the primary system clock is configured as EC, RC or INTRC, then the OST time-out is skipped. Skip to step 3.

- 2. If the primary system clock is configured as an external oscillator (HS, XT, LP), then the OST will be active, waiting for 1024 clocks of the primary system clock.

- 3. On the following Q1, the device holds the system clock in Q1.

- 4. The device stays in Q1 while eight falling edges of the primary system clock are counted.

- 5. Once the eight counts transpire, the device begins to run from the primary oscillator.

- If the secondary clock was INTRC and the primary is not INTRC, the INTRC will be shut down to save current providing that the INTRC is not being used for any other function, such as WDT or Fail-Safe Clock monitoring.

- If the secondary clock was T1OSC, the T1OSC will continue to run if T1OSCEN is still set; otherwise, the T1 oscillator will be shut down.

| RTCinit | BANKSEL | TMR1H        |                                               |

|---------|---------|--------------|-----------------------------------------------|

|         | MOVLW   | 0x80         | ; Preload TMR1 register pair                  |

|         | MOVWF   | TMR1H        | ; for 1 second overflow                       |

|         | CLRF    | TMR1L        |                                               |

|         | MOVLW   | b'00001111'  | ; Configure for external clock,               |

|         | MOVWF   | T1CON        | ; Asynchronous operation, external oscillator |

|         | CLRF    | secs         | ; Initialize timekeeping registers            |

|         | CLRF    | mins         |                                               |

|         | MOVLW   | .12          |                                               |

|         | MOVWF   | hours        |                                               |

|         | BANKSEL | PIE1         |                                               |

|         | BSF     | PIE1, TMR1IE | ; Enable Timer1 interrupt                     |

|         | RETURN  |              |                                               |

| RTCisr  | BANKSEL | TMR1H        |                                               |

|         | BSF     | TMR1H, 7     | ; Preload for 1 sec overflow                  |

|         | BCF     | PIR1, TMR1IF | ; Clear interrupt flag                        |

|         | INCF    | secs, F      | ; Increment seconds                           |

|         | MOVF    | secs, w      |                                               |

|         | SUBLW   | .60          |                                               |

|         | BTFSS   | STATUS, Z    | ; 60 seconds elapsed?                         |

|         | RETURN  |              | ; No, done                                    |

|         | CLRF    | seconds      | ; Clear seconds                               |

|         | INCF    | mins, f      | ; Increment minutes                           |

|         | MOVF    | mins, w      |                                               |

|         | SUBLW   | .60          |                                               |

|         | BTFSS   | STATUS, Z    | ; 60 seconds elapsed?                         |

|         | RETURN  |              | ; No, done                                    |

|         | CLRF    | mins         | ; Clear minutes                               |

|         | INCF    | hours, f     | ; Increment hours                             |

|         | MOVF    | hours, w     |                                               |

|         | SUBLW   | .24          |                                               |

|         | BTFSS   | STATUS, Z    | ; 24 hours elapsed?                           |

|         | RETURN  |              | ; No, done                                    |

|         | CLRF    | hours        | ; Clear hours                                 |

|         | RETURN  |              | ; Done                                        |

### EXAMPLE 7-3: IMPLEMENTING A REAL-TIME CLOCK USING A TIMER1 INTERRUPT SERVICE

### TABLE 7-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Address                 | Name   | Bit 7   | Bit 6                                                                      | Bit 5        | Bit 4         | Bit 3          | Bit 2       | Bit 1     | Bit 0  | Valu<br>POR, | e on<br>BOR | all c | e on<br>other<br>sets |

|-------------------------|--------|---------|----------------------------------------------------------------------------|--------------|---------------|----------------|-------------|-----------|--------|--------------|-------------|-------|-----------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON | GIE     | PEIE                                                                       | TMR0IE       | INTOIE        | RBIE           | TMR0IF      | INTOIF    | RBIF   | 0000         | 000x        | 0000  | 000u                  |

| 0Ch                     | PIR1   | —       | ADIF <sup>(1)</sup>                                                        | RCIF         | TXIF          | SSPIF          | CCP1IF      | TMR2IF    | TMR1IF | -000         | 0000        | -000  | 0000                  |

| 8Ch                     | PIE1   | —       | ADIE <sup>(1)</sup>                                                        | RCIE         | TXIE          | SSPIE          | CCP1IE      | TMR2IE    | TMR1IE | -000         | 0000        | -000  | 0000                  |

| 0Eh                     | TMR1L  | Holding | g Registe                                                                  | r for the Le | ast Significa | ant Byte of th | ne 16-bit T | MR1 Regis | ster   | xxxx         | xxxx        | uuuu  | uuuu                  |

| 0Fh                     | TMR1H  | Holding | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register |              |               |                |             |           |        | xxxx         | xxxx        | uuuu  | uuuu                  |

| 10h                     | T1CON  |         | T1RUN                                                                      | T1CKPS1      | T1CKPS0       | T1OSCEN        | T1SYNC      | TMR1CS    | TMR10N | -000         | 0000        | -uuu  | uuuu                  |

Legend:x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.Note1:This bit is only implemented on the PIC16F88. The bit will read '0' on the PIC16F87.

NOTES:

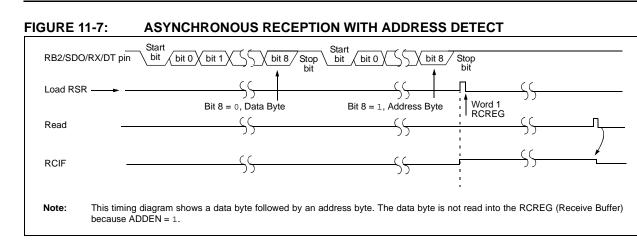

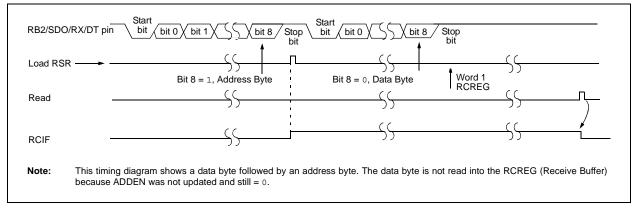

#### FIGURE 11-8: ASYNCHRONOUS RECEPTION WITH ADDRESS BYTE FIRST

#### TABLE 11-9: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Address                | Name   | Bit 7   | Bit 6                        | Bit 5     | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|------------------------|--------|---------|------------------------------|-----------|--------|-------|--------|--------|--------|-----------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE     | PEIE                         | TMR0IE    | INT0IE | RBIE  | TMR0IF | INTOIF | RBIF   | 0000 000x             | 0000 000u                       |

| 0Ch                    | PIR1   | —       | ADIF <sup>(1)</sup>          | RCIF      | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | -000 0000             | -000 0000                       |

| 18h                    | RCSTA  | SPEN    | RX9                          | SREN      | CREN   | ADDEN | FERR   | OERR   | RX9D   | x000 000x             | 0000 000x                       |

| 1Ah                    | RCREG  | AUSART  | Receive                      | Data Regi | ster   |       |        |        |        | 0000 0000             | 0000 0000                       |

| 8Ch                    | PIE1   | —       | ADIE <sup>(1)</sup>          | RCIE      | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE | -000 0000             | -000 0000                       |

| 98h                    | TXSTA  | CSRC    | TX9                          | TXEN      | SYNC   | —     | BRGH   | TRMT   | TX9D   | 0000 -010             | 0000 -010                       |

| 99h                    | SPBRG  | Baud Ra | Baud Rate Generator Register |           |        |       |        |        |        |                       | 0000 0000                       |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception.

**Note 1:** This bit is only implemented on the PIC16F88. The bit will read '0' on the PIC16F87.

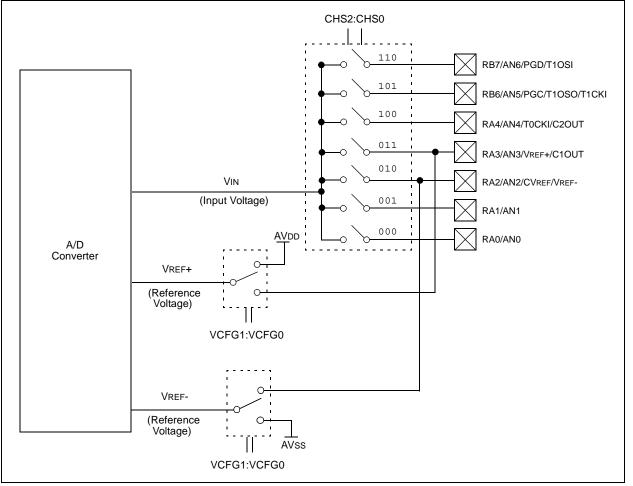

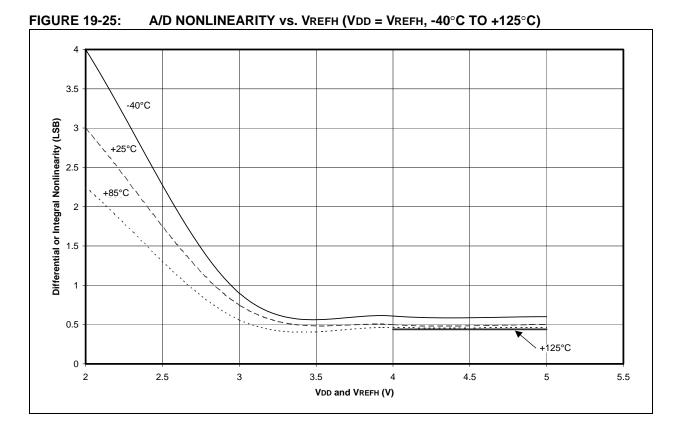

## 12.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

The Analog-to-Digital (A/D) converter module has seven inputs for 18/20 pin devices (PIC16F88 devices only).

The conversion of an analog input signal results in a corresponding 10-bit digital number. The A/D module has a high and low-voltage reference input that is software selectable to some combination of VDD, VSS, VREF- (RA2) or VREF+ (RA3).

The A/D converter has a unique feature of being able to operate while the device is in Sleep mode. To operate in Sleep, the A/D conversion clock must be derived from the A/D's internal RC oscillator. The A/D module has five registers:

- A/D Result High Register (ADRESH)

- A/D Result Low Register (ADRESL)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

- Analog Select Register (ANSEL)

The ADCON0 register, shown in Register 12-2, controls the operation of the A/D module. The ANSEL register, shown in Register 12-1 and the ADCON1 register, shown in Register 12-3, configure the functions of the port pins. The port pins can be configured as analog inputs (RA3/RA2 can also be voltage references) or as digital I/O.

Additional information on using the A/D module can be found in the "*PIC*<sup>®</sup> *Mid-Range MCU Family Reference Manual*" (DS33023).

#### REGISTER 12-1: ANSEL: ANALOG SELECT REGISTER (ADDRESS9Bh) PIC16F88 DEVICES ONLY

|   | U-0   | R/W-1 |

|---|-------|-------|-------|-------|-------|-------|-------|-------|

|   | _     | ANS6  | ANS5  | ANS4  | ANS3  | ANS2  | ANS1  | ANS0  |

| - | bit 7 |       |       |       |       |       |       | bit 0 |

#### bit 7 Unimplemented: Read as '0'

bit 6-0 **ANS<6:0>:** Analog Input Select bits

Bits select input function on corresponding AN<6:0> pins.

1 = Analog I/O<sup>(1,2)</sup>

0 = Digital I/O

- **Note 1:** Setting a pin to an analog input disables the digital input buffer. The corresponding TRIS bit should be set to input mode when using pins as analog inputs. Only AN2 is an analog I/O, all other ANx pins are analog inputs.

- **2:** See the block diagrams for the analog I/O pins to see how ANSEL interacts with the CHS bits of the ADCON0 register.

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

The ADRESH:ADRESL registers contain the result of the A/D conversion. When the A/D conversion is complete, the result is loaded into the A/D Result register pair, the GO/DONE bit (ADCON0<2>) is cleared and A/D Interrupt Flag bit, ADIF, is set. The block diagram of the A/D module is shown in Figure 12-1.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as inputs.

To determine sample time, see **Section 12.1** "**A/D Acquisition Requirements**". After this sample time has elapsed, the A/D conversion can be started.

These steps should be followed for doing an A/D conversion:

- 1. Configure the A/D module:

- Configure analog/digital I/O (ANSEL)

- Configure voltage reference (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D conversion clock (ADCON0)

- Turn on A/D module (ADCON0)

- 2. Configure A/D interrupt (if desired):

- Clear ADIF bit

- Set ADIE bit

- SET PEIE bit

- Set GIE bit

- 3. Wait the required acquisition time.

- 4. Start conversion:

- Set GO/DONE bit (ADCON0)

- 5. Wait for A/D conversion to complete, by either:

- Polling for the GO/DONE bit to be cleared (with interrupts disabled); OR

- Waiting for the A/D interrupt

- Read A/D Result register pair (ADRESH:ADRESL), clear bit ADIF if required.

- 7. For next conversion, go to step 1 or step 2 as required. The A/D conversion time per bit is defined as TAD. A minimum wait of 2 TAD is required before the next acquisition starts.

## FIGURE 12-1: A/D BLOCK DIAGRAM

## 15.0 SPECIAL FEATURES OF THE CPU

These devices have a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power-saving operating modes and offer code protection:

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- Two-Speed Start-up

- Fail-Safe Clock Monitor

- Sleep

- Code Protection

- ID Locations

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

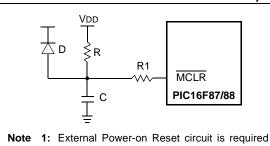

There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only. It is designed to keep the part in Reset while the power supply stabilizes and is enabled or disabled using a configuration bit. With these two timers on-chip, most applications need no external Reset circuitry. Sleep mode is designed to offer a very low-current Power-down mode. The user can wake-up from Sleep through external Reset, Watchdog Timer wake-up or through an interrupt.

Additional information on special features is available in the "*PIC*<sup>®</sup> *Mid-Range MCU Family Reference Manual*" (DS33023).

## 15.1 Configuration Bits

The configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations. These bits are mapped in program memory locations 2007h and 2008h.

The user will note that address 2007h is beyond the user program memory space which can be accessed only during programming.

## 15.3 MCLR

PIC16F87/88 devices have a noise filter in the MCLR Reset path. The filter will detect and ignore small pulses.

It should be noted that a WDT Reset does not drive MCLR pin low.

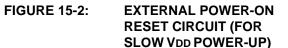

The behavior of the ESD protection on the MCLR pin has been altered from previous devices of this family. Voltages applied to the pin that exceed its specification can result in both MCLR and excessive current beyond the device specification during the ESD event. The circuit, as shown in Figure 15-2, is suggested.

| Note: | For this reason, Microchip recommends |

|-------|---------------------------------------|

|       | that the MCLR pin no longer be tied   |

|       | directly to VDD.                      |

The RA5/MCLR/VPP pin can be configured for MCLR (default), or as an I/O pin (RA5). This is configured through the MCLRE bit in Configuration Word 1.

only if the VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- 2:  $R < 40 \text{ k}\Omega$  is recommended to make sure that the voltage drop across R does not violate the device's electrical specification.

- 3:  $R1 = 1 \ k\Omega \ to \ 10 \ k\Omega \ will limit any current flow$  $ing into MCLR from external capacitor C (0.1 <math>\mu$ F), in the event of RA5/MCLR/VPP pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

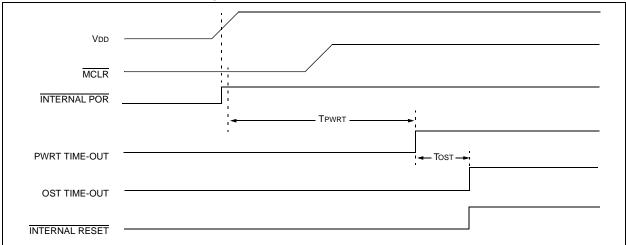

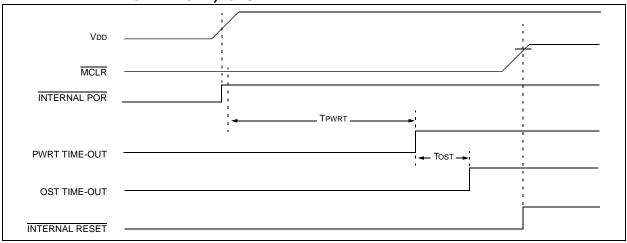

## 15.4 Power-on Reset (POR)

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.2V-1.7V). To take advantage of the POR, tie the MCLR pin to VDD, as described in Section 15.3 "MCLR". A maximum rise time for VDD is specified. See Section 18.0 "Electrical Characteristics" for details.

When the device starts normal operation (exits the Reset condition), device operating parameters (voltage, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met. For more information, see Application Note, *AN607 "Power-up Trouble Shooting"* (DS00607).

## 15.5 Power-up Timer (PWRT)

The Power-up Timer (PWRT) of the PIC16F87/88 is a counter that uses the INTRC oscillator as the clock input. This yields a count of 72 ms. While the PWRT is counting, the device is held in Reset.

The power-up time delay depends on the INTRC and will vary from chip-to-chip due to temperature and process variation. See DC parameter #33 for details.

The PWRT is enabled by clearing configuration bit PWRTEN.

## 15.6 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over (if enabled). This helps to ensure that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from Sleep.

## 15.7 Brown-out Reset (BOR)

The configuration bit, BOREN, can enable or disable the Brown-out Reset circuit. If VDD falls below VBOR (parameter D005, about 4V) for longer than TBOR (parameter #35, about 100  $\mu$ s), the brown-out situation will reset the device. If VDD falls below VBOR for less than TBOR, a Reset may not occur.

Once the brown-out occurs, the device will remain in Brown-out Reset until VDD rises above VBOR. The Power-up Timer (if enabled) will keep the device in Reset for TPWRT (parameter #33, about 72 ms). If VDD should fall below VBOR during TPWRT, the Brown-out Reset process will restart when VDD rises above VBOR with the Power-up Timer Reset. Unlike previous PIC16 devices, the PWRT is no longer automatically enabled when the Brown-out Reset circuit is enabled. The PWRTEN and BOREN configuration bits are independent of each other.

#### FIGURE 15-5: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD THROUGH RC NETWORK): CASE 2

| COMF             | Complement f                                                                                                                                 |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] COMF f,d                                                                                                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                   |

| Operation:       | (f) $\rightarrow$ (destination)                                                                                                              |

| Status Affected: | Z                                                                                                                                            |

| Description:     | The contents of register 'f' are complemented. If 'd' = 0, the result is stored in W. If 'd' = 1, the result is stored back in register 'f'. |

| GOTO             | Unconditional Branch                                                                                                                                                                             |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                          |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                               |

| Operation:       | $k \rightarrow PC<10:0>$ ,<br>PCLATH<4:3> $\rightarrow PC<12:11>$                                                                                                                                |

| Status Affected: | None                                                                                                                                                                                             |

| Description:     | GOTO is an unconditional branch.<br>The eleven-bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded<br>from PCLATH<4:3>. GOTO is a<br>two-cycle instruction. |

| DECF             | Decrement f                                                                                                                                 | INCF             | Increment f                                                                                                                                                          |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] DECF f,d                                                                                                                          | Syntax:          | [label] INCF f,d                                                                                                                                                     |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                          | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                      |

| Operation:       | (f) – 1 $\rightarrow$ (destination)                                                                                                         | Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                  |

| Status Affected: | Z                                                                                                                                           | Status Affected: | Z                                                                                                                                                                    |

| Description:     | Decrement register 'f'. If 'd' = 0,<br>the result is stored in the W<br>register. If 'd' = 1, the result is<br>stored back in register 'f'. | Description:     | The contents of register 'f' are<br>incremented. If 'd' = 0, the result<br>is placed in the W register. If<br>'d' = 1, the result is placed back in<br>register 'f'. |

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                           | INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                               | Syntax:          | [ <i>label</i> ] INCFSZ f,d                                                                                                                                                                                                                                                                                                 |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                                                                                                                                                                                                       | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                             |

| Operation:       | (f) $-1 \rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                                        | Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                             | Status Affected: | None                                                                                                                                                                                                                                                                                                                        |

| Description:     | The contents of register 'f' are<br>decremented. If 'd' = 0, the result<br>is placed in the W register. If<br>'d' = 1, the result is placed back in<br>register 'f'.<br>If the result is '1', the next<br>instruction is executed. If the<br>result is '0', then a NOP is<br>executed instead, making it a<br>2 TCY instruction. | Description:     | The contents of register 'f' are<br>incremented. If 'd' = 0, the result is<br>placed in the W register. If 'd' = 1,<br>the result is placed back in<br>register 'f'.<br>If the result is '1', the next<br>instruction is executed. If the<br>result is '0', a NOP is executed<br>instead, making it a 2 TCY<br>instruction. |

## 17.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers and dsPIC<sup>®</sup> digital signal controllers are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Compilers/Assemblers/Linkers

- MPLAB C Compiler for Various Device Families

- HI-TECH C<sup>®</sup> for Various Device Families

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers

- MPLAB ICD 3

- PICkit<sup>™</sup> 3 Debug Express

- Device Programmers

- PICkit<sup>™</sup> 2 Programmer

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits, and Starter Kits

## 17.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16/32-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- In-Circuit Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- High-level source code debugging

- Mouse over variable inspection

- Drag and drop variables from source to watch windows

- Extensive on-line help

- Integration of select third party tools, such as IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either C or assembly)

- One-touch compile or assemble, and download to emulator and simulator tools (automatically updates all project information)

- Debug using:

- Source files (C or assembly)

- Mixed C and assembly

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

## 18.3 DC Characteristics: Internal RC Accuracy PIC16F87/88 (Industrial, Extended) PIC16LF87/88 (Industrial)

|                 | PIC16LF87/88<br>(Industrial)       Standard Operating Conditions (unless otherwise stated)         Operating temperature       -40°C ≤ TA ≤ +85°C for industrial |                                                                                               |    |         |     |                 |                |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|----|---------|-----|-----------------|----------------|

| PIC16F<br>(Indu | <b>587/88</b><br>ustrial, Extended)                                                                                                                              | IOperating temperature $-40^{\circ}\text{C} < T\text{A} < +85^{\circ}\text{C}$ for industrial |    |         |     |                 |                |

| Param<br>No.    | <sup>n</sup> Device Min Typ Max Units Conditions                                                                                                                 |                                                                                               |    | ditions |     |                 |                |

|                 | INTOSC Accuracy @ Freq = 8 MHz, 4 MHz, 2 MHz, 1 MHz, 500 kHz, 250 kHz, 125 kHz <sup>(1)</sup>                                                                    |                                                                                               |    |         |     |                 |                |

|                 | PIC16LF87/88                                                                                                                                                     | -2                                                                                            | ±1 | 2       | %   | +25°C           |                |

|                 |                                                                                                                                                                  | -5                                                                                            | —  | 5       | %   | -10°C to +85°C  | VDD = 2.7-3.3V |

|                 |                                                                                                                                                                  | -10                                                                                           | _  | 10      | %   | -40°C to +85°C  |                |

|                 | PIC16F87/88                                                                                                                                                      | -2                                                                                            | ±1 | 2       | %   | 25°C            |                |

|                 |                                                                                                                                                                  | -5                                                                                            | _  | 5       | %   | -10°C to +85°C  | VDD = 4.5-5.5V |

|                 |                                                                                                                                                                  | -10                                                                                           | _  | 10      | %   | -40°C to +85°C  |                |

|                 | Extended devices                                                                                                                                                 | -15                                                                                           | —  | 15      | %   | -40°C to +125°C | VDD = 4.5-5.5V |

|                 | INTRC Accuracy @ Freq = 31 kHz <sup>(2)</sup>                                                                                                                    |                                                                                               |    |         |     |                 |                |

|                 | PIC16LF87/88                                                                                                                                                     | 26.562                                                                                        | _  | 35.938  | kHz | -40°C to +85°C  | VDD = 2.7-3.3V |

|                 | PIC16F87/88                                                                                                                                                      | 26.562                                                                                        | _  | 35.938  | kHz | -40°C to +85°C  | VDD = 4.5-5.5V |

Legend: Shading of rows is to assist in readability of the table.

Note 1: Frequency calibrated at 25°C. OSCTUNE register can be used to compensate for temperature drift.

2: INTRC frequency after calibration.

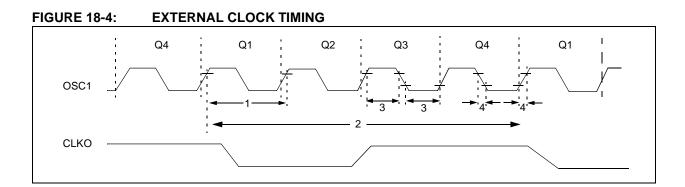

#### TABLE 18-3: EXTERNAL CLOCK TIMING REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                   | Min    | Тур† | Max       | Units      | Conditions                               |

|------------------|-------|----------------------------------|--------|------|-----------|------------|------------------------------------------|

|                  | Fosc  | External CLKI Frequency          | DC     | _    | 1         | MHz        | XT and RC Oscillator mode                |

|                  |       | (Note 1)                         | DC     | _    | 20        | MHz        | HS Oscillator mode                       |

|                  |       |                                  | DC     | —    | 32        | kHz        | LP Oscillator mode                       |

|                  |       | Oscillator Frequency             | DC     | _    | 4         | MHz        | RC Oscillator mode                       |

|                  |       | (Note 1)                         | 0.1    | —    | 4         | MHz        | XT Oscillator mode                       |

|                  |       |                                  | 4<br>5 | _    | 20<br>200 | MHz<br>kHz | HS Oscillator mode<br>LP Oscillator mode |

| 1                | Tosc  | External CLKI Period (Note 1)    | 1000   | _    | —         | ns         | XT and RC Oscillator modes               |

|                  |       |                                  | 50     | _    |           | ns         | HS Oscillator mode                       |

|                  |       |                                  | 5      | _    | _         | ms         | LP Oscillator mode                       |

|                  |       | Oscillator Period                | 250    | —    | —         | ns         | RC Oscillator mode                       |

|                  |       | (Note 1)                         | 250    | —    | 10,000    | ns         | XT Oscillator mode                       |

|                  |       |                                  | 50     | —    | 250       | ns         | HS Oscillator mode                       |

|                  |       |                                  | 5      | _    |           | ms         | LP Oscillator mode                       |

| 2                | Тсү   | Instruction Cycle Time (Note 1)  | 200    | Тсү  | DC        | ns         | TCY = 4/FOSC                             |

| 3                | TosL, | External Clock in (OSC1) High or | 500    | —    | —         | ns         | XT oscillator                            |

|                  | TosH  | Low Time                         | 2.5    | —    | —         | ms         | LP oscillator                            |

|                  |       |                                  | 15     |      | —         | ns         | HS oscillator                            |

| 4                | TosR, | External Clock in (OSC1) Rise or | —      |      | 25        | ns         | XT oscillator                            |

|                  | TosF  | Fall Time                        | —      | —    | 50        | ns         | LP oscillator                            |

|                  |       |                                  | —      |      | 15        | ns         | HS oscillator                            |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TcY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKI pin. When an external clock input is used, the "max." cycle time limit is "DC" (no clock) for all devices.

© 2002-2013 Microchip Technology Inc.

## Е

| 3, 29 |

|-------|

| 3, 29 |

| 3, 29 |

| 3, 29 |

| 3, 29 |

| 3, 29 |

| 163   |

| 6     |

| 52    |

| 38    |

|       |

|       |

|       |

### F

| Flash Program Memory<br>Associated Registers<br>EEADR Register<br>EEADRH Register | 36<br>29 |

|-----------------------------------------------------------------------------------|----------|

| EEADR Register                                                                    | 29       |

| 0                                                                                 |          |

| EEADRH Register                                                                   | . 29     |

|                                                                                   |          |

| EECON1 Register                                                                   | 29       |

| EECON2 Register                                                                   | . 29     |

| EEDATA Register                                                                   | 29       |

| EEDATH Register                                                                   |          |

| Erasing                                                                           | 32       |

| Reading                                                                           | 32       |

| Writing                                                                           | 34       |

| FSR Register 16, 17                                                               |          |

## G

| General Purpose Register File |  |

|-------------------------------|--|

|-------------------------------|--|

## I

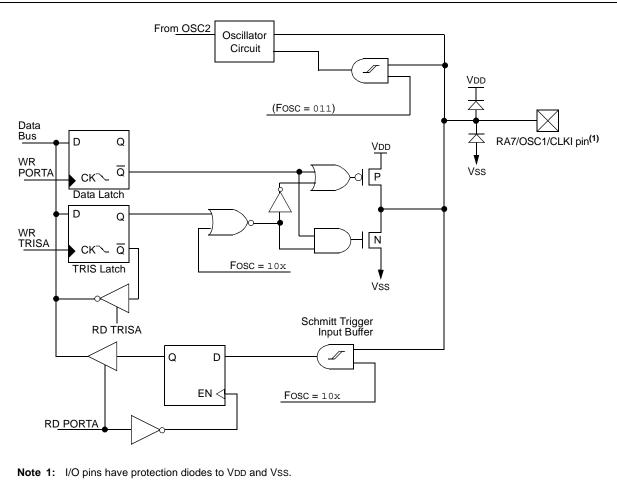

| I/O Po           | orts                                     |            |

|------------------|------------------------------------------|------------|

| F                | PORTA                                    | 53         |

| F                | PORTB                                    |            |

| 7                | TRISB Register                           |            |

| I <sup>2</sup> C | J. J |            |

| 1                | Addressing                               |            |

|                  | Associated Registers                     |            |

| 1                | Master Mode                              |            |

| ſ                | Mode                                     | 94         |

| ſ                | Mode Selection                           |            |

| 1                | Multi-Master Mode                        |            |

| F                | Reception                                |            |

| 5                | SCL and SDA Pins                         |            |

| 5                | Slave Mode                               |            |

| ٦                | Transmission                             |            |

| ID Lo            | cations                                  | . 131, 149 |

| In-Cir           | cuit Debugger                            | 149        |

| In-Cir           | cuit Serial Programming                  | 131        |

| In-Cir           | cuit Serial Programming (ICSP)           | 149        |

| INDF             | Register                                 | 16, 17, 28 |

| Indire           | ct Addressing                            |            |

| Instru           | ction Set                                | 151        |

| [                | Descriptions                             | 153        |

| (                | General Format                           | 151        |

| F                | Read-Modify-Write Operations             | 151        |

| 5                | Summary Table                            | 152        |

|                  | ADDLW                                    | 153        |

|                  | ADDWF                                    | 153        |

|                  | ANDLW                                    | 153        |

| 1                | ANDWF                                    | 153        |

| E                | BCF                                      | 153        |

| E                | BSF                                      | 153        |

|                  |                                          |            |

| BTFSC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 154                                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| BTFSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 154                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                            |

| CALL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                            |

| CLRF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 154                                                                                                        |

| CLRW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 154                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                            |

| CLRWDT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -                                                                                                          |