Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 16                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 368 × 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                           |

| Supplier Device Package    | 18-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f87t-e-so |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| 1.0   | Device Overview                                                              | 5     |

|-------|------------------------------------------------------------------------------|-------|

| 2.0   | Memory Organization                                                          |       |

| 3.0   | Data EEPROM and Flash Program Memory                                         | 27    |

| 4.0   | Oscillator Configurations                                                    | 35    |

| 5.0   | I/O Ports                                                                    |       |

| 6.0   | Timer0 Module                                                                | 67    |

| 7.0   | Timer1 Module                                                                | 71    |

| 8.0   | Timer2 Module                                                                | 79    |

| 9.0   | Capture/Compare/PWM (CCP) Module                                             | 81    |

| 10.0  | Synchronous Serial Port (SSP) Module                                         | 87    |

| 11.0  | Addressable Universal Synchronous Asynchronous Receiver Transmitter (AUSART) | 97    |

| 12.0  | Analog-to-Digital Converter (A/D) Module                                     | . 113 |

|       | Comparator Module                                                            |       |

|       | Comparator Voltage Reference Module                                          |       |

| 15.0  | Special Features of the CPU                                                  | . 129 |

| 16.0  | Instruction Set Summary                                                      | . 149 |

| 17.0  | Development Support                                                          | . 157 |

| 18.0  | Electrical Characteristics                                                   | . 161 |

| 19.0  | DC and AC Characteristics Graphs and Tables                                  | . 191 |

| 20.0  | Packaging Information                                                        | . 205 |

| Appe  | ndix A: Revision History                                                     | . 215 |

| Appe  | ndix B: Device Differences                                                   | . 215 |

| INDE  | X                                                                            | . 217 |

| The I | Aicrochip Web Site                                                           | . 225 |

| Custo | omer Change Notification Service                                             | . 225 |

| Custo | omer Support                                                                 | . 225 |

| Read  | er Response                                                                  | . 226 |

| PIC1  | 6F87/88 Product Identification System                                        | . 227 |

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

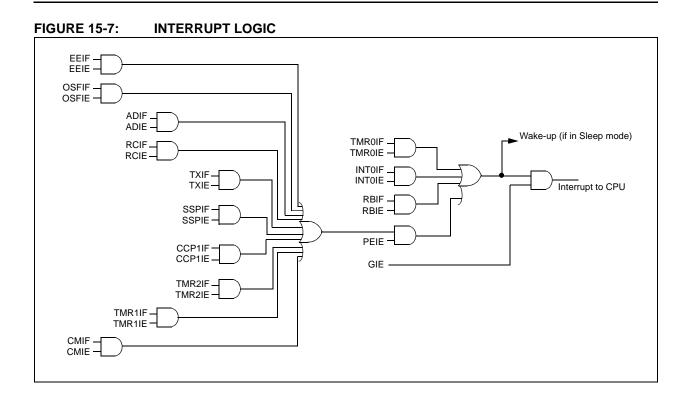

#### 2.2.2.3 INTCON Register

The INTCON register is a readable and writable register that contains various enable and flag bits for the TMR0 register overflow, RB Port change and External RB0/INT pin interrupts. Note: Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 2-3: INTCON: INTERRUPT CONTROL REGISTER (ADDRESS 0Bh, 8Bh, 10Bh, 18Bh)

| R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0 | R/W-0  | R/W-0  | R/W-x |

|-------|-------|--------|--------|-------|--------|--------|-------|

| GIE   | PEIE  | TMR0IE | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF  |

| bit 7 |       |        |        |       |        |        | bit 0 |

| bit 7  | GIE: Global Interrupt Enable bit                                                                                |

|--------|-----------------------------------------------------------------------------------------------------------------|

|        | 1 = Enables all unmasked interrupts                                                                             |

|        | 0 = Disables all interrupts                                                                                     |

| bit 6  | PEIE: Peripheral Interrupt Enable bit                                                                           |

|        | 1 = Enables all unmasked peripheral interrupts                                                                  |

|        | <ul><li>0 = Disables all peripheral interrupts</li></ul>                                                        |

| bit 5  | TMR0IE: TMR0 Overflow Interrupt Enable bit                                                                      |

|        | 1 = Enables the TMR0 interrupt                                                                                  |

|        | 0 = Disables the TMR0 interrupt                                                                                 |

| bit 4  | INTOIE: RB0/INT External Interrupt Enable bit                                                                   |

|        | 1 = Enables the RB0/INT external interrupt                                                                      |

| 1.14.0 | 0 = Disables the RB0/INT external interrupt                                                                     |

| bit 3  | <b>RBIE:</b> RB Port Change Interrupt Enable bit                                                                |

|        | <ul> <li>1 = Enables the RB port change interrupt</li> <li>0 = Disables the RB port change interrupt</li> </ul> |

| bit 2  | TMR0IF: TMR0 Overflow Interrupt Flag bit                                                                        |

| 511 2  | 1 = TMR0 register has overflowed (must be cleared in software)                                                  |

|        | 0 = TMR0 register did not overflow                                                                              |

| bit 1  | INTOIF: RB0/INT External Interrupt Flag bit                                                                     |

|        | 1 = The RB0/INT external interrupt occurred (must be cleared in software)                                       |

|        | 0 = The RB0/INT external interrupt did not occur                                                                |

| bit 0  | RBIF: RB Port Change Interrupt Flag bit                                                                         |

|        | A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch                    |

|        | condition and allow flag bit RBIF to be cleared.                                                                |

|        | 1 = At least one of the RB7:RB4 pins changed state (must be cleared in software)                                |

|        | 0 = None of the RB7:RB4 pins have changed state                                                                 |

|        |                                                                                                                 |

|        | Legend:                                                                                                         |

|        | D. Deadable bit W. Writeble bit II. Unimplemented bit read as (0)                                               |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|                   |                  |                      |                    |

#### 2.2.2.7 PIR2 Register

The PIR2 register contains the flag bit for the EEPROM write operation interrupt.

| Note: | Interrupt flag bits are set when an interrupt |  |  |

|-------|-----------------------------------------------|--|--|

|       | condition occurs, regardless of the state of  |  |  |

|       | its corresponding enable bit, or the global   |  |  |

|       | enable bit, GIE (INTCON<7>). User             |  |  |

|       | software should ensure the appropriate        |  |  |

|       | interrupt flag bits are clear prior to        |  |  |

|       | enabling an interrupt.                        |  |  |

### REGISTER 2-7: PIR2: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 2 (ADDRESS 0Dh)

| R/W-0 | R/W-0 | U-0 | R/W-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|-----|-------|-----|-----|-----|-------|

| OSFIF | CMIF  | —   | EEIF  | —   | —   | —   | —     |

| bit 7 |       |     |       |     |     |     | bit 0 |

| bit 7   | <b>OSFIF:</b> Oscillator Fail Interrupt Flag bit<br>1 = System oscillator failed, clock input has changed to INTRC (must be cleared in software)<br>0 = System clock operating |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | CMIF: Comparator Interrupt Flag bit                                                                                                                                            |

|         | <ul><li>1 = Comparator input has changed (must be cleared in software)</li><li>0 = Comparator input has not changed</li></ul>                                                  |

| bit 5   | Unimplemented: Read as '0'                                                                                                                                                     |

| bit 4   | EEIF: EEPROM Write Operation Interrupt Flag bit                                                                                                                                |

|         | <ul><li>1 = The write operation completed (must be cleared in software)</li><li>0 = The write operation is not complete or has not been started</li></ul>                      |

| bit 3-0 | Unimplemented: Read as '0'                                                                                                                                                     |

|         |                                                                                                                                                                                |

|         | Legend:                                                                                                                                                                        |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 2.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses the register pointed to by the File Select Register, FSR. Reading the INDF register itself, indirectly (FSR = 0) will read 00h. Writing to the INDF register indirectly results in a no operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 2-5. A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-2.

| EXAMPLE 2-2: | INDIRECT ADDRESSING |

|--------------|---------------------|

|--------------|---------------------|

|          | MOVLW | 0x20 |   | ;initialize pointer  |

|----------|-------|------|---|----------------------|

|          | MOVWF | FSR  |   | ;to RAM              |

| NEXT     | CLRF  | INDF |   | ;clear INDF register |

|          | INCF  | FSR, | F | ;inc pointer         |

|          | BTFSS | FSR, | 4 | ;all done?           |

|          | GOTO  | NEXT |   | ;no clear next       |

| CONTINUE |       |      |   |                      |

|          | :     |      |   | ;yes continue        |

#### Direct Addressing Indirect Addressing FSR Register RP1:RP0 6 From Opcode IRP 7 0 0 Bank Select Location Select Bank Select Location Select ▶ 00 01 10 11 00h 80h 100h 180h Data Memory<sup>(1)</sup> FFh 17Fh 7Fh 1FFh Bank 0 Bank 1 Bank 2 Bank 3 Note 1: For register file map detail, see Figure 2-2 or Figure 2-3.

#### FIGURE 2-5: DIRECT/INDIRECT ADDRESSING

An example of the complete four-word write sequence is shown in Example 3-5. The initial address is loaded into the EEADRH:EEADR register pair; the four words of data are loaded using indirect addressing, assuming that a row erase sequence has already been performed.

#### EXAMPLE 3-5: WRITING TO FLASH PROGRAM MEMORY

; This write routine assumes the following: ; 1. The 32 words in the erase block have already been erased. ; 2. A valid starting address (the least significant bits = '00') is loaded into EEADRH:EEADR ; 3. This example is starting at 0x100, this is an application dependent setting. ; 4. The 8 bytes (4 words) of data are loaded, starting at an address in RAM called ARRAY. ; 5. This is an example only, location of data to program is application dependent. ; 6. word block is located in data memory. BANKSEL EECON1 ;prepare for WRITE procedure EECON1, EEPGD BSF ; point to program memory EECON1, WREN BSF ;allow write cycles BCF EECON1, FREE ;perform write only BANKSEL word block MOVLW .4 MOVWF word block ;prepare for 4 words to be written BANKSEL EEADRH ;Start writing at 0x100 MOVLW  $0 \times 01$ MOVWF ;load HIGH address EEADRH MOVLW 0x00 MOVWF ;load LOW address EEADR BANKSEL ARRAY MOVLW ARRAY ; initialize FSR to start of data MOVWF FSR LOOP BANKSEL EEDATA MOVF INDF, W ; indirectly load EEDATA MOVWF EEDATA INCF FSR, F ; increment data pointer MOVF INDF, W ; indirectly load EEDATH MOVWF EEDATH INCF FSR, F ; increment data pointer BANKSEL EECON1 MOVLW 0x55 ;required sequence MOVWF EECON2 MOVIW 0xAA MOVWF EECON2 BSF EECON1, WR ;set WR bit to begin write NOP ; instructions here are ignored as processor NOP BANKSEL EEADR INCF EEADR, f ;load next word address word\_block BANKSEL word block, f DECFSZ ;have 4 words been written? GOTO loop ;NO, continue with writing BANKSEL EECON1 BCF EECON1, WREN ;YES, 4 words complete, disable writes BSF INTCON,GIE ;enable interrupts

| TABLE 5-3: | PORTB FUNCTIONS |

|------------|-----------------|

|            |                 |

| Name                                        | Bit#  | Buffer                | Function                                                                                                                                                                                                        |

|---------------------------------------------|-------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RB0/INT/CCP1 <sup>(7)</sup>                 | bit 0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input.<br>Capture input/Compare output/PWM output pin.<br>Internal software programmable weak pull-up.                                                                   |

| RB1/SDI/SDA                                 | bit 1 | TTL/ST <sup>(5)</sup> | Input/output pin, SPI data input pin or I <sup>2</sup> C™ data I/O pin.<br>Internal software programmable weak pull-up.                                                                                         |

| RB2/SDO/RX/DT                               | bit 2 | TTL/ST <sup>(4)</sup> | Input/output pin, SPI data output pin.<br>AUSART asynchronous receive or synchronous data.<br>Internal software programmable weak pull-up.                                                                      |

| RB3/PGM/CCP1 <sup>(3,7)</sup>               | bit 3 | TTL/ST <sup>(2)</sup> | Input/output pin, programming in LVP mode or Capture input/Compare output/PWM output pin. Internal software programmable weak pull-up.                                                                          |

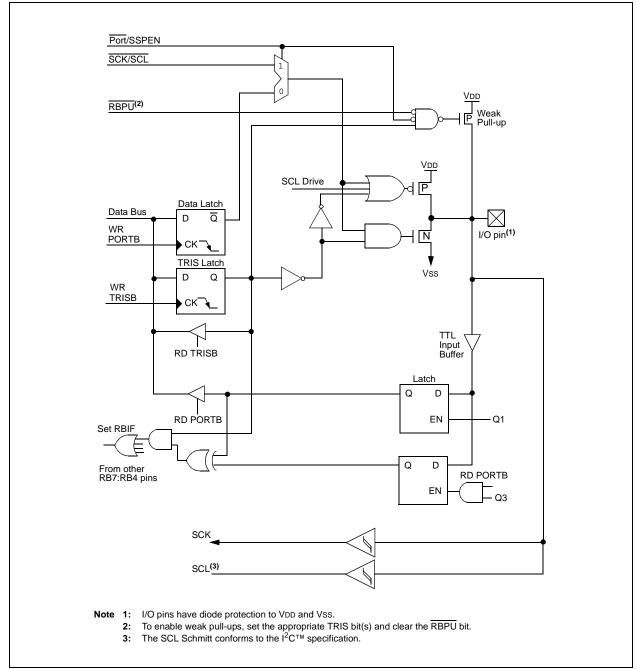

| RB4/SCK/SCL                                 | bit 4 | TTL/ST <sup>(5)</sup> | Input/output pin or SPI and I <sup>2</sup> C clock pin (with interrupt-on-change).<br>Internal software programmable weak pull-up.                                                                              |

| RB5/SS/TX/CK                                | bit 5 | TTL                   | Input/output pin or SPI slave select pin (with interrupt-on-change).<br>AUSART asynchronous transmit or synchronous clock.<br>Internal software programmable weak pull-up.                                      |

| RB6/AN5 <sup>(6)</sup> /PGC/<br>T1OSO/T1CKI | bit 6 | TTL/ST <sup>(2)</sup> | Input/output pin, analog input <sup>(6)</sup> , serial programming clock<br>(with interrupt-on-change), Timer1 oscillator output pin or Timer1 clock<br>input pin. Internal software programmable weak pull-up. |

| RB7/AN6 <sup>(6)</sup> /PGD/<br>T1OSI       | bit 7 | TTL/ST <sup>(2)</sup> | Input/output pin, analog input <sup>(6)</sup> , serial programming data (with interrupt-on-change) or Timer1 oscillator input pin.<br>Internal software programmable weak pull-up.                              |

**Legend:** TTL = TTL input, ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

- 3: Low-Voltage ICSP<sup>™</sup> Programming (LVP) is enabled by default, which disables the RB3 I/O function. LVP must be disabled to enable RB3 as an I/O pin and allow maximum compatibility to the other 18-pin mid-range devices.

- 4: This buffer is a Schmitt Trigger input when configured for CCP or SSP mode.

- **5**: This buffer is a Schmitt Trigger input when configured for SPI or  $I^2C$  mode.

- 6: PIC16F88 only.

- 7: The CCP1 pin is determined by the CCPMX bit in Configuration Word 1 register.

| Address   | Name                 | Bit 7 | Bit 6                         | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0     | Value on<br>POR, BOR                                 | Value on<br>all other<br>Resets              |

|-----------|----------------------|-------|-------------------------------|-------|-------|-------|-------|-------|-----------|------------------------------------------------------|----------------------------------------------|

| 06h, 106h | PORTB                | RB7   | RB6                           | RB5   | RB4   | RB3   | RB2   | RB1   | RB0       | xxxx xxxx <sup>(1)</sup><br>00xx xxxx <sup>(2)</sup> | uuuu uuuu <b>(1)</b><br>00uu uuuu <b>(2)</b> |

| 86h, 186h | TRISB                | PORTB | PORTB Data Direction Register |       |       |       |       |       | 1111 1111 | 1111 1111                                            |                                              |

| 81h, 181h | OPTION_REG           | RBPU  | INTEDG                        | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0       | 1111 1111                                            | 1111 1111                                    |

| 9Bh       | ANSEL <sup>(2)</sup> | _     | ANS6                          | ANS5  | ANS4  | ANS3  | ANS2  | ANS1  | ANS0      | -111 1111                                            | -111 1111                                    |

#### TABLE 5-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PORTB.

**Note 1:** This value applies only to the PIC16F87.

**2:** This value applies only to the PIC16F88.

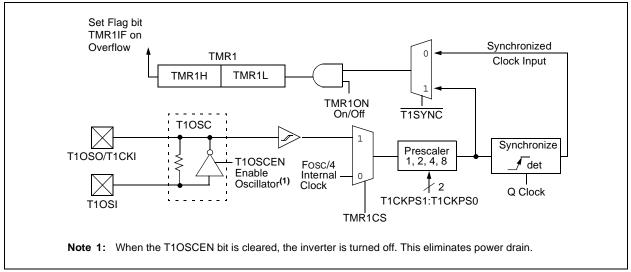

#### 7.2 Timer1 Operation in Timer Mode

Timer mode is selected by clearing the TMR1CS (T1CON<1>) bit. In this mode, the input clock to the timer is FOSC/4. The synchronize control bit, T1SYNC (T1CON<2>), has no effect since the internal clock is always in sync.

#### 7.3 Timer1 Counter Operation

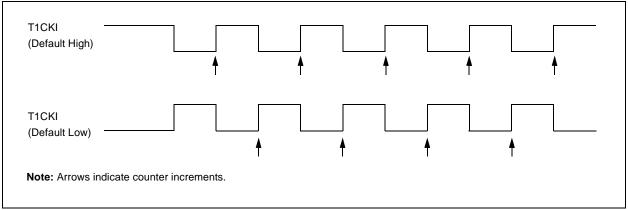

Timer1 may operate in Asynchronous or Synchronous mode, depending on the setting of the TMR1CS bit.

When Timer1 is being incremented via an external source, increments occur on a rising edge. After Timer1 is enabled in Counter mode, the module must first have a falling edge before the counter begins to increment.

#### 7.4 Timer1 Operation in Synchronized Counter Mode

Counter mode is selected by setting bit TMR1CS. In this mode, the timer increments on every rising edge of clock input on pin RB7/PGD/T1OSI when bit T1OSCEN is set, or on pin RB6/PGC/T1OSO/T1CKI when bit T1OSCEN is cleared.

If  $\overline{\text{T1SYNC}}$  is cleared, then the external clock input is synchronized with internal phase clocks. The synchronization is done after the prescaler stage. The prescaler stage is an asynchronous ripple counter.

In this configuration, during Sleep mode, Timer1 will not increment even if the external clock is present since the synchronization circuit is shut off. The prescaler, however, will continue to increment.

## 7.6 Timer1 Oscillator

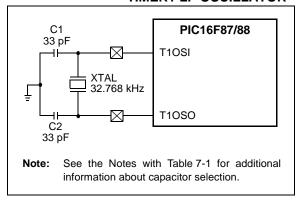

A crystal oscillator circuit is built between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low-power oscillator, rated up to 32.768 kHz. It will continue to run during all power-managed modes. It is primarily intended for a 32 kHz crystal. The circuit for a typical LP oscillator is shown in Figure 7-3. Table 7-1 shows the capacitor selection for the Timer1 oscillator.

The user must provide a software time delay to ensure proper oscillator start-up.

Note: The Timer1 oscillator shares the T1OSI and T1OSO pins with the PGD and PGC pins used for programming and debugging. When using the Timer1 oscillator, In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) may not function correctly (high voltage or low voltage), or the In-Circuit Debugger (ICD) may not communicate with the controller. As a result of using either ICSP or ICD, the Timer1 crystal may be damaged. If ICSP or ICD operations are required, the crystal should be disconnected from the circuit (disconnect either lead) or installed after programming. The oscillator loading capacitors may remain in-circuit during ICSP or ICD operation.

#### FIGURE 7-3: EXTERNAL COMPONENTS FOR THE TIMER1 LP OSCILLATOR

## TABLE 7-1:CAPACITOR SELECTION FOR<br/>THE TIMER1 OSCILLATOR

| Osc Type | Freq   | C1    | C2    |  |

|----------|--------|-------|-------|--|

| LP       | 32 kHz | 33 pF | 33 pF |  |

- **Note 1:** Microchip suggests this value as a starting point in validating the oscillator circuit.

- **2:** Higher capacitance increases the stability of the oscillator but also increases the start-up time.

- 3: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- 4: Capacitor values are for design guidance only.

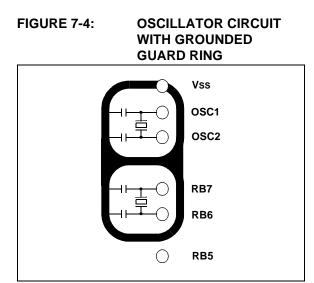

### 7.7 Timer1 Oscillator Layout Considerations

The Timer1 oscillator circuit draws very little power during operation. Due to the low-power nature of the oscillator, it may also be sensitive to rapidly changing signals in close proximity.

The oscillator circuit, shown in Figure 7-3, should be located as close as possible to the microcontroller. There should be no circuits passing within the oscillator circuit boundaries other than Vss or VDD.

If a high-speed circuit must be located near the oscillator, a grounded guard ring around the oscillator circuit, as shown in Figure 7-4, may be helpful when used on a single-sided PCB or in addition to a ground plane.

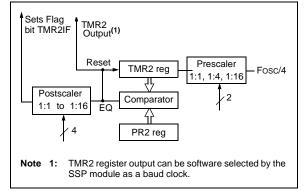

## 8.0 TIMER2 MODULE

Timer2 is an 8-bit timer with a prescaler and a postscaler. It can be used as the PWM time base for the PWM mode of the CCP1 module. The TMR2 register is readable and writable and is cleared on any device Reset.

The input clock (FOSC/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits T2CKPS1:T2CKPS0 (T2CON<1:0>).

The Timer2 module has an 8-bit period register, PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon Reset.

The match output of TMR2 goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling inclusive) to generate a TMR2 interrupt (latched in flag bit TMR2IF (PIR1<1>)).

Timer2 can be shut off by clearing control bit TMR2ON (T2CON<2>) to minimize power consumption.

Register 8-1 shows the Timer2 Control register.

Additional information on timer modules is available in the "*PIC*<sup>®</sup> *Mid-Range MCU Family Reference Manual*" (DS33023).

#### 8.1 Timer2 Prescaler and Postscaler

The prescaler and postscaler counters are cleared when any of the following occurs:

- A write to the TMR2 register

- A write to the T2CON register

- Any device Reset (Power-on Reset, MCLR, WDT Reset or Brown-out Reset)

TMR2 is not cleared when T2CON is written.

### 8.2 Output of TMR2

The output of TMR2 (before the postscaler) is fed to the Synchronous Serial Port module (SSP) which optionally uses it to generate a shift clock.

#### FIGURE 8-1: TIMER2 BLOCK DIAGRAM

## 15.0 SPECIAL FEATURES OF THE CPU

These devices have a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power-saving operating modes and offer code protection:

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- Two-Speed Start-up

- Fail-Safe Clock Monitor

- Sleep

- Code Protection

- ID Locations

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only. It is designed to keep the part in Reset while the power supply stabilizes and is enabled or disabled using a configuration bit. With these two timers on-chip, most applications need no external Reset circuitry. Sleep mode is designed to offer a very low-current Power-down mode. The user can wake-up from Sleep through external Reset, Watchdog Timer wake-up or through an interrupt.

Additional information on special features is available in the "*PIC*<sup>®</sup> *Mid-Range MCU Family Reference Manual*" (DS33023).

## 15.1 Configuration Bits

The configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations. These bits are mapped in program memory locations 2007h and 2008h.

The user will note that address 2007h is beyond the user program memory space which can be accessed only during programming.

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                 |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ]BTFSS f,b                                                                                                                                                                               |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b < 7 \end{array}$                                                                                                                                        |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                 |

| Status Affected: | None                                                                                                                                                                                                    |

| Description:     | If bit 'b' in register 'f' = 0, the next<br>instruction is executed.<br>If bit 'b' = 1, then the next<br>instruction is discarded and a NOP<br>is executed instead, making this a<br>2 TCY instruction. |

| CLRF             | Clear f                                                                |

|------------------|------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CLRF f                                                |

| Operands:        | $0 \leq f \leq 127$                                                    |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f), \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                      |

| Description:     | The contents of register 'f' are<br>cleared and the Z bit is set.      |

| BTFSC            | Bit Test, Skip if Clear                                                                                                                                                                                              |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                                  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                  |  |  |  |

| Operation:       | skip if (f <b>) = 0</b>                                                                                                                                                                                              |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                 |  |  |  |

| Description:     | If bit 'b' in register 'f' = 1, the next<br>instruction is executed.<br>If bit 'b', in register 'f', = 0, the next<br>instruction is discarded and a NOP<br>is executed instead, making this a<br>2 TCY instruction. |  |  |  |

| CLRW             | Clear W                                                                |  |  |  |

|------------------|------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] CLRW                                                           |  |  |  |

| Operands:        | None                                                                   |  |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (W), \\ 1 \rightarrow Z \end{array}$ |  |  |  |

| Status Affected: | Z                                                                      |  |  |  |

| Description:     | W register is cleared. Zero bit (Z) is set.                            |  |  |  |

| CALL             | Call Subroutine                                                                                                                                                                                             | CLRWDT           | Clear Watchdog Timer                                                                                                           |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                     | Syntax:          | [label] CLRWDT                                                                                                                 |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                                          | Operands:        | None                                                                                                                           |

| Operation:       | (PC) + 1 $\rightarrow$ TOS,<br>k $\rightarrow$ PC<10:0>,<br>(PCLATH<4:3>) $\rightarrow$ PC<12:11>                                                                                                           | Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \text{ prescaler,} \\ 1 \rightarrow \overline{TO}, \end{array}$    |

| Status Affected: | None                                                                                                                                                                                                        |                  | $1 \rightarrow PD$                                                                                                             |

| Description:     | Call subroutine. First, return                                                                                                                                                                              | Status Affected: | TO, PD                                                                                                                         |

|                  | address (PC + 1) is pushed onto<br>the stack. The eleven-bit<br>immediate address is loaded into<br>PC bits <10:0>. The upper bits of<br>the PC are loaded from PCLATH.<br>CALL is a two-cycle instruction. | Description:     | CLRWDT instruction resets the<br>Watchdog Timer. It also resets the<br>prescaler of the WDT. Status bits<br>TO and PD are set. |

| SUBLW            | Subtract W from Literal                                                                                                        | XORLW            | Exclusive OR Literal with W                                                                                                |

|------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] SUBLW k                                                                                                       | Syntax:          | [label] XORLW k                                                                                                            |

| Operands:        | $0 \le k \le 255$                                                                                                              | Operands:        | $0 \leq k \leq 255$                                                                                                        |

| Operation:       | $k - (W) \rightarrow (W)$                                                                                                      | Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                              |

| Status Affected: | C, DC, Z                                                                                                                       | Status Affected: | Z                                                                                                                          |

| Description:     | The W register is subtracted (two's complement method) from the eight-bit literal 'k'. The result is placed in the W register. | Description:     | The contents of the W register<br>are XOR'ed with the eight-bit<br>literal 'k'. The result is placed in<br>the W register. |

| SUBWF            | Subtract W from f                                                                                                                                                                       | XORWF            | Exclusive OR W with f                                                                                                                                                     |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SUBWF f,d                                                                                                                                                                       | Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                                                |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                             | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                         |

| Operation:       | (f) – (W) $\rightarrow$ (destination)                                                                                                                                                   | Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                 |

| Status Affected: | C, DC, Z                                                                                                                                                                                | Status Affected: | Z                                                                                                                                                                         |

| Description:     | Subtract (two's complement<br>method) W register from register 'f'.<br>If 'd' = 0, the result is stored in the<br>W register. If 'd' = 1, the result is<br>stored back in register 'f'. | Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' = 0, the result is stored in the W register. If 'd' = 1, the result is stored back in register 'f'. |

| SWAPF            | Swap Nibbles in f                                                                                                                                            |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] SWAPF f,d                                                                                                                                   |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                            |  |  |  |  |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                      |  |  |  |  |

| Status Affected: | None                                                                                                                                                         |  |  |  |  |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' = 0, the result is placed in W register. If 'd' = 1, the result is placed in register 'f'. |  |  |  |  |

DS30487D-page 156

#### 18.4 DC Characteristics: PIC16F87/88 (Industrial, Extended) PIC16LF87/88 (Industrial)

| DC CHARACTERISTICS |       | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for extended} \\ \mbox{Operating voltage VDD range as described in DC Specification,} \\ \mbox{Section 18.1 "DC Characteristics: Supply Voltage".} \end{array}$ |                 |      |          |       |                                                                |

|--------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|----------|-------|----------------------------------------------------------------|

| Param<br>No.       | Sym   | Characteristic                                                                                                                                                                                                                                                                                                                                                                                     | Min             | Тур† | Max      | Units | Conditions                                                     |

|                    | VIL   | Input Low Voltage                                                                                                                                                                                                                                                                                                                                                                                  |                 |      |          |       |                                                                |

|                    |       | I/O ports:                                                                                                                                                                                                                                                                                                                                                                                         |                 |      |          |       |                                                                |

| D030               |       | with TTL buffer                                                                                                                                                                                                                                                                                                                                                                                    | Vss             | _    | 0.15 Vdd | V     | For entire VDD range                                           |

| D030A              |       |                                                                                                                                                                                                                                                                                                                                                                                                    | Vss             | _    | 0.8V     | V     | $4.5V \le VDD \le 5.5V$                                        |

| D031               |       | with Schmitt Trigger buffer                                                                                                                                                                                                                                                                                                                                                                        | Vss             | _    | 0.2 Vdd  | V     |                                                                |

| D032               |       | MCLR, OSC1 (in RC mode)                                                                                                                                                                                                                                                                                                                                                                            | Vss             | _    | 0.2 Vdd  | V     | (Note 1)                                                       |

| D033               |       | OSC1 (in XT and LP mode)                                                                                                                                                                                                                                                                                                                                                                           | Vss             | _    | 0.3V     | V     |                                                                |

|                    |       | OSC1 (in HS mode)                                                                                                                                                                                                                                                                                                                                                                                  | Vss             | _    | 0.3 Vdd  | V     |                                                                |

|                    |       | Ports RB1 and RB4:                                                                                                                                                                                                                                                                                                                                                                                 |                 |      |          |       |                                                                |

| D034               |       | with Schmitt Trigger buffer                                                                                                                                                                                                                                                                                                                                                                        | Vss             | _    | 0.3 Vdd  | V     | For entire VDD range                                           |

|                    | Vін   | Input High Voltage                                                                                                                                                                                                                                                                                                                                                                                 |                 |      |          |       |                                                                |

|                    |       | I/O ports:                                                                                                                                                                                                                                                                                                                                                                                         |                 |      |          |       |                                                                |

| D040               |       | with TTL buffer                                                                                                                                                                                                                                                                                                                                                                                    | 2.0             | —    | Vdd      | V     | $4.5V \leq V\text{DD} \leq 5.5V$                               |

| D040A              |       |                                                                                                                                                                                                                                                                                                                                                                                                    | 0.25 VDD + 0.8V | —    | Vdd      | V     | For entire VDD range                                           |

| D041               |       | with Schmitt Trigger buffer                                                                                                                                                                                                                                                                                                                                                                        | 0.8 Vdd         | —    | Vdd      | V     | For entire VDD range                                           |

| D042               |       | MCLR                                                                                                                                                                                                                                                                                                                                                                                               | 0.8 Vdd         | _    | Vdd      | V     |                                                                |

| D042A              |       | OSC1 (in XT and LP mode)                                                                                                                                                                                                                                                                                                                                                                           | 1.6V            | —    | Vdd      | V     |                                                                |

|                    |       | OSC1 (in HS mode)                                                                                                                                                                                                                                                                                                                                                                                  | 0.7 Vdd         | —    | Vdd      | V     |                                                                |

| D043               |       | OSC1 (in RC mode)                                                                                                                                                                                                                                                                                                                                                                                  | 0.9 Vdd         | —    | Vdd      | V     | (Note 1)                                                       |

|                    |       | Ports RB1 and RB4:                                                                                                                                                                                                                                                                                                                                                                                 |                 |      |          |       |                                                                |

| D044               |       | with Schmitt Trigger buffer                                                                                                                                                                                                                                                                                                                                                                        | 0.7 Vdd         |      | Vdd      | V     | For entire VDD range                                           |

| D070               | Ipurb | PORTB Weak Pull-up Current                                                                                                                                                                                                                                                                                                                                                                         | 50              | 250  | 400      | μA    | VDD = 5V, VPIN = VSS                                           |

|                    | lı∟   | Input Leakage Current (Notes                                                                                                                                                                                                                                                                                                                                                                       | 2, 3)           |      |          |       |                                                                |

| D060               |       | I/O ports                                                                                                                                                                                                                                                                                                                                                                                          | —               | _    | ±1       | μA    | $Vss \le VPIN \le VDD, pin at high-impedance$                  |

| D061               |       | MCLR                                                                                                                                                                                                                                                                                                                                                                                               | —               | _    | ±5       | μA    | $Vss \leq VPIN \leq VDD$                                       |

| D063               |       | OSC1                                                                                                                                                                                                                                                                                                                                                                                               | —               | _    | ±5       | μΑ    | Vss ≤ VPIN ≤ VDD, XT, HS<br>and LP oscillator<br>configuration |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1/CLKI pin is a Schmitt Trigger input. It is not recommended that the PIC16F87/88 be driven with external clock in RC mode.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- **3:** Negative current is defined as current sourced by the pin.

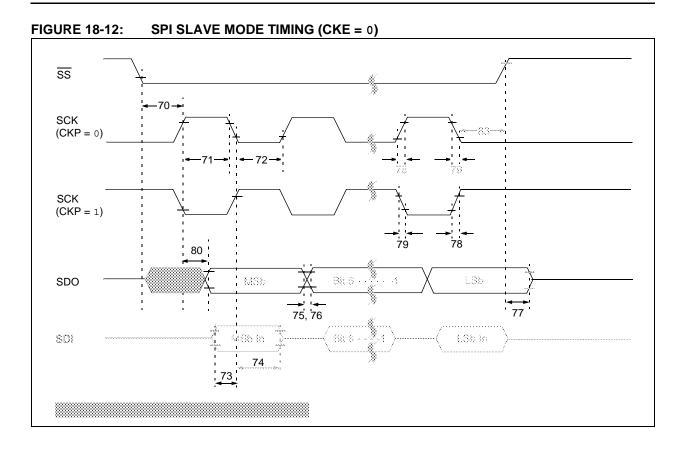

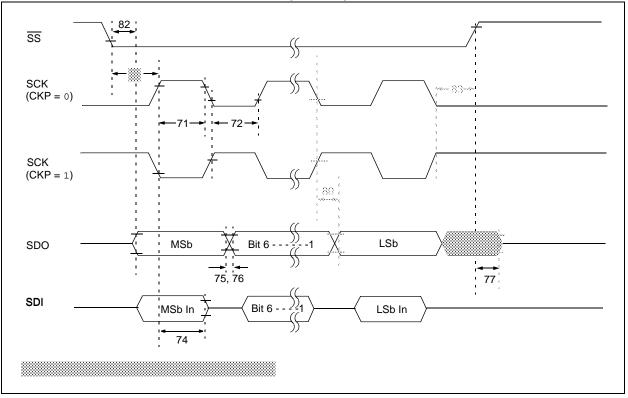

## FIGURE 18-13: SPI SLAVE MODE TIMING (CKE = 1)

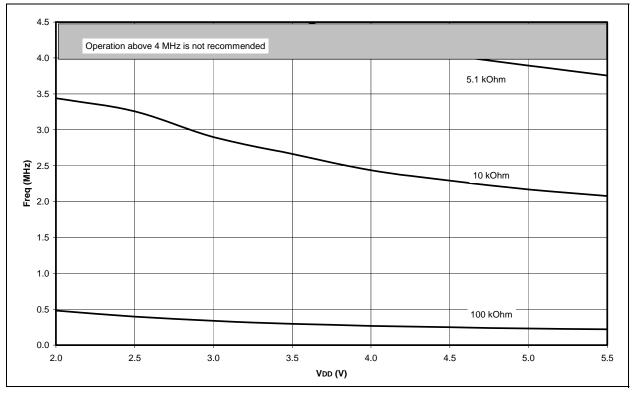

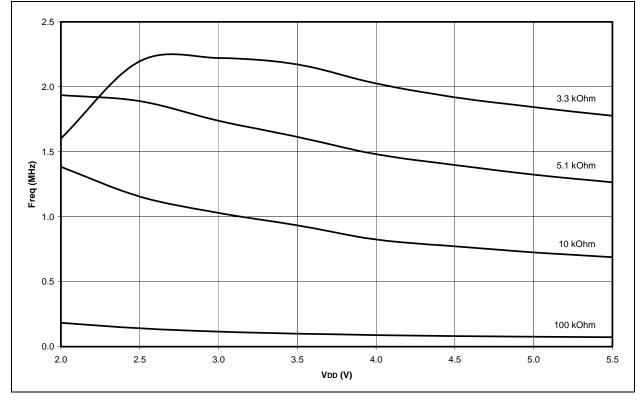

#### FIGURE 19-12: AVERAGE FOSC vs. VDD FOR VARIOUS VALUES OF R (RC MODE, C = 100 pF, +25°C)

DS30487D-page 196

## **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| To:                                                                                     | Technical Publications Manager                                                                                | Total Pages Sent                                  |

|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| RE:                                                                                     | Reader Response                                                                                               |                                                   |

| From                                                                                    | n: Name                                                                                                       |                                                   |

|                                                                                         | Company                                                                                                       |                                                   |

|                                                                                         | Address                                                                                                       |                                                   |

|                                                                                         | City / State / ZIP / Country                                                                                  |                                                   |

|                                                                                         | Telephone: ()                                                                                                 | FAX: ()                                           |

| Application (optional):                                                                 |                                                                                                               |                                                   |

| Would you like a reply?YN                                                               |                                                                                                               |                                                   |

| Devi                                                                                    | ce: PIC16F87/88                                                                                               | Literature Number: DS30487D                       |

| Questions:                                                                              |                                                                                                               |                                                   |

| 1. What are the best features of this document?                                         |                                                                                                               |                                                   |

| _                                                                                       |                                                                                                               |                                                   |

| _                                                                                       |                                                                                                               |                                                   |

| 2. ł                                                                                    | 2. How does this document meet your hardware and software development needs?                                  |                                                   |

| -                                                                                       |                                                                                                               |                                                   |

| -                                                                                       |                                                                                                               |                                                   |

| 3. [                                                                                    | 3. Do you find the organization of this document easy to follow? If not, why?                                 |                                                   |

| -                                                                                       |                                                                                                               |                                                   |

| -<br>-                                                                                  |                                                                                                               | thisk would askes a the structure and subject?    |

| 4. What additions to the document do you think would enhance the structure and subject? |                                                                                                               | ou think would enhance the structure and subject? |

| -                                                                                       |                                                                                                               |                                                   |

| 5. \                                                                                    | <ul><li>5. What deletions from the document could be made without affecting the overall usefulness?</li></ul> |                                                   |

| •                                                                                       |                                                                                                               |                                                   |

| -                                                                                       |                                                                                                               |                                                   |

| 6. I                                                                                    | s there any incorrect or misleading i                                                                         | nformation (what and where)?                      |

|                                                                                         |                                                                                                               |                                                   |

| -                                                                                       |                                                                                                               |                                                   |

| 7. H                                                                                    | How would you improve this docume                                                                             | nt?                                               |

| -                                                                                       |                                                                                                               |                                                   |

| _                                                                                       |                                                                                                               |                                                   |

## Worldwide Sales and Service

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Chongqing** Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-2819-3187 Fax: 86-571-2819-3189

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

**India - New Delhi** Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Osaka** Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7828 Fax: 886-7-330-9305

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828

**France - Paris** Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Fax: 45-4485-2829

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820