# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 16                                                                      |

| Program Memory Size        | 7KB (4K x 14)                                                           |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 256 x 8                                                                 |

| RAM Size                   | 368 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                               |

| Data Converters            | A/D 7x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 28-VQFN Exposed Pad                                                     |

| Supplier Device Package    | 28-QFN (6x6)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f88-e-ml |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

### 2.2.2.6 PIE2 Register

The PIE2 register contains the individual enable bit for the EEPROM write operation interrupt.

| REGISTER 2-6: | PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2 (ADDRESS 8Dh) |                             |               |               |              |           |              |        |

|---------------|------------------------------------------------------------|-----------------------------|---------------|---------------|--------------|-----------|--------------|--------|

|               | R/W-0                                                      | R/W-0                       | U-0           | R/W-0         | U-0          | U-0       | U-0          | U-0    |

|               | OSFIE                                                      | CMIE                        | —             | EEIE          | —            | —         |              | _      |

|               | bit 7                                                      |                             |               |               |              |           |              | bit 0  |

| bit 7         | OSFIE: Os                                                  | cillator Fail In            | terrupt Enab  | le bit        |              |           |              |        |

|               |                                                            | 1 = Enabled<br>0 = Disabled |               |               |              |           |              |        |

| bit 6         | CMIE: Corr                                                 | parator Inter               | rupt Enable I | oit           |              |           |              |        |

|               | 1 = Enable                                                 |                             |               |               |              |           |              |        |

|               | 0 = Disable                                                |                             |               |               |              |           |              |        |

| bit 5         | Unimplem                                                   | ented: Read                 | <b>as</b> '0' |               |              |           |              |        |

| bit 4         | EEIE: EEP                                                  | ROM Write C                 | peration Inte | errupt Enable | bit          |           |              |        |

|               |                                                            | 1 = Enabled<br>0 = Disabled |               |               |              |           |              |        |

| bit 3-0       | Unimplemented: Read as '0'                                 |                             |               |               |              |           |              |        |

|               |                                                            |                             |               |               |              |           |              |        |

|               | Legend:                                                    |                             |               |               |              |           |              |        |

|               | R = Reada                                                  | ble bit                     | W = W         | ritable bit   | U = Unimp    | olemented | bit, read as | '0'    |

|               | -n = Value                                                 | at POR                      | '1' = Bi      | t is set      | '0' = Bit is | cleared   | x = Bit is u | nknown |

### 2.2.2.8 PCON Register

| Note: | Interrupt flag bits get set when an interrupt<br>condition occurs, regardless of the state of<br>its corresponding enable bit, or the global<br>enable bit, GIE (INTCON<7>). User<br>software should ensure the appropriate |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | interrupt flag bits are clear prior to enabling an interrupt.                                                                                                                                                               |

The Power Control (PCON) register contains a flag bit to allow differentiation between a Power-on Reset (POR), a Brown-out Reset, an external MCLR Reset and WDT Reset.

Note: BOR is unknown on Power-on Reset. It must then be set by the user and checked on subsequent Resets to see if BOR is clear, indicating a brown-out has occurred. The BOR status bit is a 'don't care' and is not necessarily predictable if the brownout circuit is disabled (by clearing the BOREN bit in the Configuration Word register).

### REGISTER 2-8: PCON: POWER CONTROL REGISTER (ADDRESS 8Eh)

|         |            |              |               |                |              | ,           |              |         |

|---------|------------|--------------|---------------|----------------|--------------|-------------|--------------|---------|

|         | U-0        | U-0          | U-0           | U-0            | U-0          | U-0         | R/W-0        | R/W-x   |

|         | _          | _            | _             | _              | _            | _           | POR          | BOR     |

|         | bit 7      |              |               |                |              |             |              | bit 0   |

| bit 7-2 | Unimplem   | nented: Rea  | d as '0'      |                |              |             |              |         |

|         | '          |              |               |                |              |             |              |         |

| bit 1   | POR: Pow   | er-on Reset  | Status bit    |                |              |             |              |         |

|         | 1 = No Por | wer-on Rese  | et occurred   |                |              |             |              |         |

|         | 0 = A Pow  | er-on Reset  | occurred (m   | ust be set in  | software aft | er a Power- | on Reset o   | ccurs)  |

| L:1.0   |            |              | ``            |                | contrat o an |             |              |         |

| bit 0   | BOK: Brov  | wn-out Rese  | t Status bit  |                |              |             |              |         |

|         | 1 = No Bro | own-out Res  | et occurred   |                |              |             |              |         |

|         | 0 = A Brow | vn-out Reset | t occurred (m | nust be set in | software af  | ter a Brown | -out Reset   | occurs) |

|         |            |              | , ,           |                |              |             |              | ,       |

|         | Legend:    |              |               |                |              |             |              |         |

|         | -          |              |               |                |              |             |              |         |

|         | R = Reada  | able bit     | W = W         | /ritable bit   | U = Unim     | plemented   | bit, read as | ʻ0'     |

|         | -n = Value | at POR       | '1' = B       | it is set      | '0' = Bit is | s cleared   | x = Bit is ι | unknown |

-n = Value at POR

'1' = Bit is set

| REGISTER 3-1: | EECON1:                                                                                                                                                                                                          | EEPROM                                 | ACCESS          | CONTROL    | REGISTE     | R 1 (ADDR      | ESS 18Ch    | )           |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-----------------|------------|-------------|----------------|-------------|-------------|

|               | R/W-x                                                                                                                                                                                                            | U-0                                    | U-0             | R/W-x      | R/W-x       | R/W-0          | R/S-0       | R/S-0       |

|               | EEPGD                                                                                                                                                                                                            | _                                      | _               | FREE       | WRERR       | WREN           | WR          | RD          |

|               | bit 7                                                                                                                                                                                                            |                                        |                 |            |             |                |             | bit 0       |

|               |                                                                                                                                                                                                                  |                                        |                 |            |             |                |             |             |

| bit 7         |                                                                                                                                                                                                                  | rogram/Data                            |                 | Select bit |             |                |             |             |

|               |                                                                                                                                                                                                                  | ses program<br>ses data mer            | •               |            |             |                |             |             |

| bit 6-5       | Unimplem                                                                                                                                                                                                         | ented: Rea                             | <b>d as</b> '0' |            |             |                |             |             |

| bit 4         | FREE: EE                                                                                                                                                                                                         | PROM Force                             | ed Row Eras     | se bit     |             |                |             |             |

|               |                                                                                                                                                                                                                  | he program<br>n write only             | memory row      | addressed  | by EEADRH   | I:EEADR on     | the next WF | R command   |

| bit 3         | WRERR: E                                                                                                                                                                                                         | EPROM Er                               | ror Flag bit    |            |             |                |             |             |

|               | operat                                                                                                                                                                                                           | e operation i<br>ion)<br>rite operatio | •               | -          | d (any MCLI | R or any WE    | DT Reset du | ring normal |

| bit 2         | WREN: EE                                                                                                                                                                                                         | PROM Writ                              | e Enable bit    |            |             |                |             |             |

|               |                                                                                                                                                                                                                  | write cycles<br>write to the           |                 |            |             |                |             |             |

| bit 1         | WR: Write                                                                                                                                                                                                        | Control bit                            |                 |            |             |                |             |             |

|               | <ul> <li>1 = Initiates a write cycle. The bit is cleared by hardware once write is complete. The WR bit can only be set (not cleared) in software.</li> <li>0 = Write cycle to the EEPROM is complete</li> </ul> |                                        |                 |            |             |                |             |             |

| bit 0         | RD: Read                                                                                                                                                                                                         | Control bit                            |                 |            |             |                |             |             |

|               | <ul> <li>1 = Initiates an EEPROM read, RD is cleared in hardware. The RD bit can only be set (not cleared) in software.</li> <li>0 = Does not initiate an EEPROM read</li> </ul>                                 |                                        |                 |            |             |                | be set (not |             |

|               | 5 - 20001                                                                                                                                                                                                        |                                        |                 | 1000       |             |                |             |             |

|               | Legend:                                                                                                                                                                                                          |                                        |                 |            |             |                |             |             |

|               | R = Reada                                                                                                                                                                                                        | ble bit M                              | / = Writable I  | oit U = Un | implemented | l bit, read as | '0' S = Set | only        |

|               |                                                                                                                                                                                                                  |                                        |                 |            |             | , 1000 00      |             | Siny        |

'0' = Bit is cleared

x = Bit is unknown

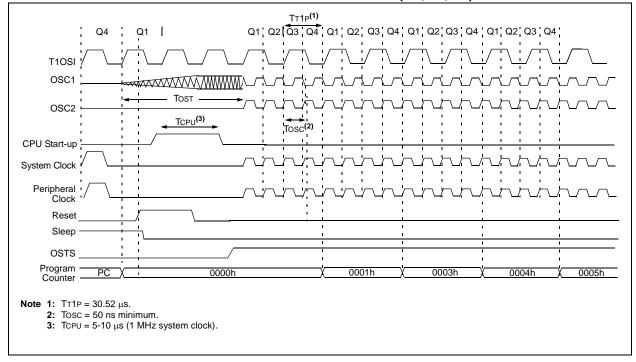

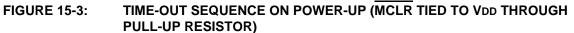

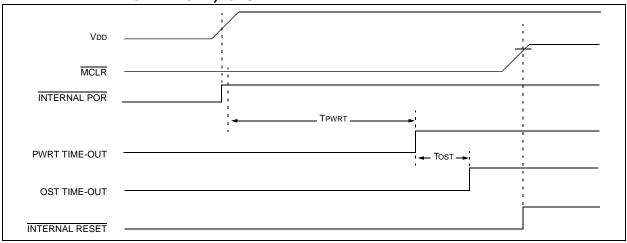

### 4.7.3.2 Returning to Primary Oscillator with a Reset

A Reset will clear SCS<1:0> back to '00'. The sequence for starting the primary oscillator following a Reset is the same for all forms of Reset, including POR. There is no transition sequence from the alternate system clock to the primary system clock on a Reset condition. Instead, the device will reset the state of the OSCCON register and default to the primary system clock. The sequence of events that takes place after this will depend upon the value of the FOSC bits in the Configuration register. If the external oscillator is configured as a crystal (HS, XT or LP), the CPU will be held in the Q1 state until 1024 clock cycles have transpired on the primary clock. This is necessary because the crystal oscillator has been powered down until the time of the transition.

During the oscillator start-up time, instruction execution and/or peripheral operation is suspended.

| Note: | If Two-Speed Clock Start-up mode is       |  |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|--|

|       | enabled, the INTRC will act as the system |  |  |  |  |  |  |  |  |

|       | clock until the OST timer has timed out.  |  |  |  |  |  |  |  |  |

If the primary system clock is either RC, EC or INTRC, the CPU will begin operating on the first Q1 cycle following the wake-up event. This means that there is no oscillator start-up time required because the primary clock is already stable; however, there is a delay between the wake-up event and the following Q2. An internal delay timer of 5-10  $\mu$ s will suspend operation after the Reset to allow the CPU to become ready for code execution. The CPU and peripheral clock will be held in the first Q1.

The sequence of events is as follows:

- 1. A device Reset is asserted from one of many sources (WDT, BOR, MCLR, etc.).

- 2. The device resets and the CPU start-up timer is enabled if in Sleep mode. The device is held in Reset until the CPU start-up time-out is complete.

- 3. If the primary system clock is configured as an external oscillator (HS, XT, LP), then the OST will be active waiting for 1024 clocks of the primary system clock. While waiting for the OST, the device will be held in Reset. The OST and CPU start-up timers run in parallel.

- After both the CPU start-up and OST timers have timed out, the device will wait for one additional clock cycle and instruction execution will begin.

FIGURE 4-10: PRIMARY SYSTEM CLOCK AFTER RESET (HS, XT, LP)

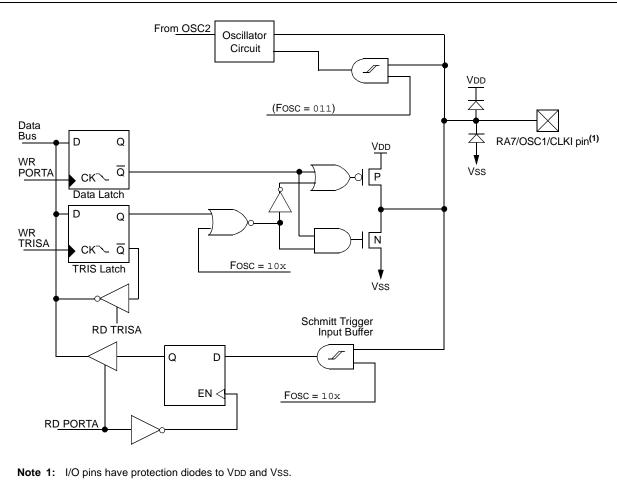

### 5.2 PORTB and the TRISB Register

PORTB is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (OPTION\_REG<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Four of PORTB's pins, RB7:RB4, have an interrupt-onchange feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupton-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RB Port Change Interrupt with Flag bit RBIF (INTCON<0>).

This interrupt can wake the device from Sleep. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

RB0/INT is an external interrupt input pin and is configured using the INTEDG bit (OPTION\_REG<6>).

PORTB is multiplexed with several peripheral functions (see Table 5-3). PORTB pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTB pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modifywrite instructions (BSF, BCF, XORWF) with TRISB as the destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

| TABLE 5-3: | PORTB FUNCTIONS |

|------------|-----------------|

|            |                 |

| Name                                        | Bit#  | Buffer                | Function                                                                                                                                                                                                        |

|---------------------------------------------|-------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RB0/INT/CCP1 <sup>(7)</sup>                 | bit 0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input.<br>Capture input/Compare output/PWM output pin.<br>Internal software programmable weak pull-up.                                                                   |

| RB1/SDI/SDA                                 | bit 1 | TTL/ST <sup>(5)</sup> | Input/output pin, SPI data input pin or I <sup>2</sup> C™ data I/O pin.<br>Internal software programmable weak pull-up.                                                                                         |

| RB2/SDO/RX/DT                               | bit 2 | TTL/ST <sup>(4)</sup> | Input/output pin, SPI data output pin.<br>AUSART asynchronous receive or synchronous data.<br>Internal software programmable weak pull-up.                                                                      |

| RB3/PGM/CCP1 <sup>(3,7)</sup>               | bit 3 | TTL/ST <sup>(2)</sup> | Input/output pin, programming in LVP mode or Capture input/Compare output/PWM output pin. Internal software programmable weak pull-up.                                                                          |

| RB4/SCK/SCL                                 | bit 4 | TTL/ST <sup>(5)</sup> | Input/output pin or SPI and I <sup>2</sup> C clock pin (with interrupt-on-change).<br>Internal software programmable weak pull-up.                                                                              |

| RB5/SS/TX/CK                                | bit 5 | TTL                   | Input/output pin or SPI slave select pin (with interrupt-on-change).<br>AUSART asynchronous transmit or synchronous clock.<br>Internal software programmable weak pull-up.                                      |

| RB6/AN5 <sup>(6)</sup> /PGC/<br>T1OSO/T1CKI | bit 6 | TTL/ST <sup>(2)</sup> | Input/output pin, analog input <sup>(6)</sup> , serial programming clock<br>(with interrupt-on-change), Timer1 oscillator output pin or Timer1 clock<br>input pin. Internal software programmable weak pull-up. |

| RB7/AN6 <sup>(6)</sup> /PGD/<br>T1OSI       | bit 7 | TTL/ST <sup>(2)</sup> | Input/output pin, analog input <sup>(6)</sup> , serial programming data (with interrupt-on-change) or Timer1 oscillator input pin.<br>Internal software programmable weak pull-up.                              |

**Legend:** TTL = TTL input, ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

- 3: Low-Voltage ICSP<sup>™</sup> Programming (LVP) is enabled by default, which disables the RB3 I/O function. LVP must be disabled to enable RB3 as an I/O pin and allow maximum compatibility to the other 18-pin mid-range devices.

- 4: This buffer is a Schmitt Trigger input when configured for CCP or SSP mode.

- **5**: This buffer is a Schmitt Trigger input when configured for SPI or  $I^2C$  mode.

- 6: PIC16F88 only.

- 7: The CCP1 pin is determined by the CCPMX bit in Configuration Word 1 register.

| Address   | Name                 | Bit 7 | Bit 6                         | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR                                 | Value on<br>all other<br>Resets              |

|-----------|----------------------|-------|-------------------------------|-------|-------|-------|-------|-------|-------|------------------------------------------------------|----------------------------------------------|

| 06h, 106h | PORTB                | RB7   | RB6                           | RB5   | RB4   | RB3   | RB2   | RB1   | RB0   | xxxx xxxx <sup>(1)</sup><br>00xx xxxx <sup>(2)</sup> | uuuu uuuu <b>(1)</b><br>00uu uuuu <b>(2)</b> |

| 86h, 186h | TRISB                | PORTB | PORTB Data Direction Register |       |       |       |       |       |       | 1111 1111                                            | 1111 1111                                    |

| 81h, 181h | OPTION_REG           | RBPU  | INTEDG                        | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                                            | 1111 1111                                    |

| 9Bh       | ANSEL <sup>(2)</sup> | _     | ANS6                          | ANS5  | ANS4  | ANS3  | ANS2  | ANS1  | ANS0  | -111 1111                                            | -111 1111                                    |

### TABLE 5-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PORTB.

**Note 1:** This value applies only to the PIC16F87.

**2:** This value applies only to the PIC16F88.

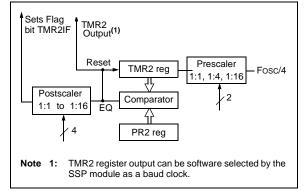

### 8.0 TIMER2 MODULE

Timer2 is an 8-bit timer with a prescaler and a postscaler. It can be used as the PWM time base for the PWM mode of the CCP1 module. The TMR2 register is readable and writable and is cleared on any device Reset.

The input clock (FOSC/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits T2CKPS1:T2CKPS0 (T2CON<1:0>).

The Timer2 module has an 8-bit period register, PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon Reset.

The match output of TMR2 goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling inclusive) to generate a TMR2 interrupt (latched in flag bit TMR2IF (PIR1<1>)).

Timer2 can be shut off by clearing control bit TMR2ON (T2CON<2>) to minimize power consumption.

Register 8-1 shows the Timer2 Control register.

Additional information on timer modules is available in the "*PIC*<sup>®</sup> *Mid-Range MCU Family Reference Manual*" (DS33023).

### 8.1 Timer2 Prescaler and Postscaler

The prescaler and postscaler counters are cleared when any of the following occurs:

- A write to the TMR2 register

- A write to the T2CON register

- Any device Reset (Power-on Reset, MCLR, WDT Reset or Brown-out Reset)

TMR2 is not cleared when T2CON is written.

### 8.2 Output of TMR2

The output of TMR2 (before the postscaler) is fed to the Synchronous Serial Port module (SSP) which optionally uses it to generate a shift clock.

### FIGURE 8-1: TIMER2 BLOCK DIAGRAM

| Address                | Name   | Bit 7   | Bit 6                       | Bit 5    | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|------------------------|--------|---------|-----------------------------|----------|--------|-------|--------|--------|--------|-----------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE     | PEIE                        | TMR0IE   | INT0IE | RBIE  | TMR0IF | INTOIF | RBIF   | 0000 000x             | 0000 000u                       |

| 0Ch                    | PIR1   | —       | ADIF <sup>(1)</sup>         | RCIF     | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | -000 0000             | -000 0000                       |

| 18h                    | RCSTA  | SPEN    | RX9                         | SREN     | CREN   | ADDEN | FERR   | OERR   | RX9D   | 0000 000x             | 0000 000x                       |

| 19h                    | TXREG  | AUSART  | <sup>-</sup> Transmit       | Data Reg | ister  |       |        |        |        | 0000 0000             | 0000 0000                       |

| 8Ch                    | PIE1   | —       | ADIE <sup>(1)</sup>         | RCIE     | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE | -000 0000             | -000 0000                       |

| 98h                    | TXSTA  | CSRC    | TX9                         | TXEN     | SYNC   | _     | BRGH   | TRMT   | TX9D   | 0000 -010             | 0000 -010                       |

| 99h                    | SPBRG  | Baud Ra | aud Rate Generator Register |          |        |       |        |        |        | 0000 0000             | 0000 0000                       |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission.

Note 1: This bit is only implemented on the PIC16F88. The bit will read '0' on the PIC16F87.

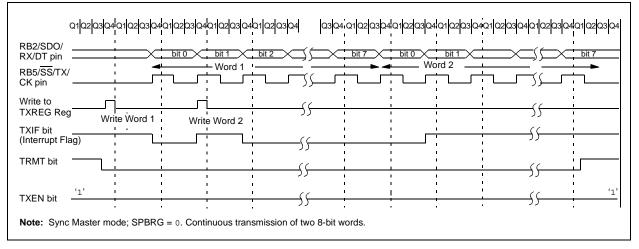

### FIGURE 11-9: SYNCHRONOUS TRANSMISSION

### FIGURE 11-10: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

| RB2/SDO/RX/DT pin     | bit 0 bit 1 bit 2 bit 6 bit 7 |

|-----------------------|-------------------------------|

| RB5/SS/TX/CK pin      |                               |

| Write to<br>TXREG Reg |                               |

| TXIF bit              | <u></u>                       |

| TRMT bit              |                               |

| TXEN bit              | \ \ .                         |

### 11.4.2 AUSART SYNCHRONOUS SLAVE RECEPTION

The operation of the Synchronous Master and Slave modes is identical, except in the case of the Sleep mode. Bit SREN is a "don't care" in Slave mode.

If receive is enabled by setting bit CREN prior to the SLEEP instruction, then a word may be received during Sleep. On completely receiving the word, the RSR register will transfer the data to the RCREG register and if enable bit RCIE bit is set, the interrupt generated will wake the chip from Sleep. If the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

When setting up a synchronous slave reception, follow these steps:

- Enable the synchronous master serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. If interrupts are desired, set enable bit RCIE.

- 3. If 9-bit reception is desired, set bit RX9.

- 4. To enable reception, set enable bit CREN.

- 5. Flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 7. Read the 8-bit received data by reading the RCREG register.

- 8. If any error occurred, clear the error by clearing bit CREN.

- 9. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

### TABLE 11-13: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

| Address                | Name   | Bit 7                        | Bit 6               | Bit 5       | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value<br>POR, |      | all o | e on<br>other<br>sets |

|------------------------|--------|------------------------------|---------------------|-------------|--------|-------|--------|--------|--------|---------------|------|-------|-----------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                          | PEIE                | TMR0IE      | INTOIE | RBIE  | TMR0IF | INTOIF | RBIF   | 0000          | 000x | 0000  | 000u                  |

| 0Ch                    | PIR1   | _                            | ADIF <sup>(1)</sup> | RCIF        | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | -000          | 0000 | -000  | 0000                  |

| 18h                    | RCSTA  | SPEN                         | RX9                 | SREN        | CREN   | ADDEN | FERR   | OERR   | RX9D   | 0000          | 000x | 0000  | 000x                  |

| 1Ah                    | RCREG  | AUSART Receive Data Register |                     |             |        |       |        |        | 0000   | 0000          | 0000 | 0000  |                       |

| 8Ch                    | PIE1   | _                            | ADIE <sup>(1)</sup> | RCIE        | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE | -000          | 0000 | -000  | 0000                  |

| 98h                    | TXSTA  | CSRC                         | TX9                 | TXEN        | SYNC   | _     | BRGH   | TRMT   | TX9D   | 0000          | -010 | 0000  | -010                  |

| 99h                    | SPBRG  | Baud Rat                     | te Genera           | tor Registe | ər     |       |        |        |        | 0000          | 0000 | 0000  | 0000                  |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous slave reception.

**Note 1:** This bit is only implemented on the PIC16F88. The bit will read '0' on the PIC16F87.

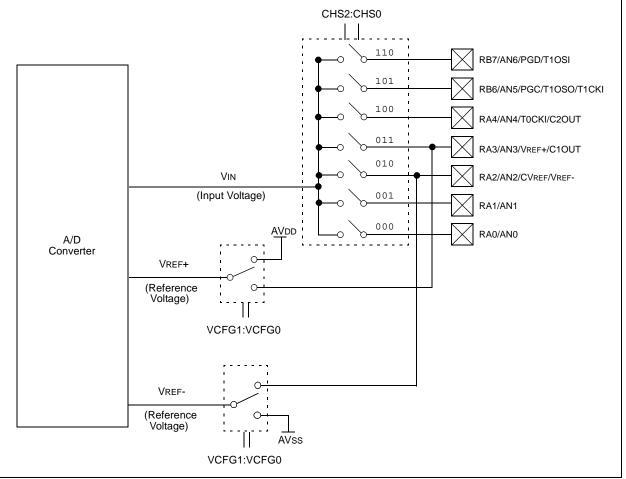

The ADRESH: ADRESL registers contain the result of the A/D conversion. When the A/D conversion is complete, the result is loaded into the A/D Result register pair, the GO/DONE bit (ADCON0<2>) is cleared and A/D Interrupt Flag bit, ADIF, is set. The block diagram of the A/D module is shown in Figure 12-1.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as inputs.

To determine sample time, see Section 12.1 "A/D Acquisition Requirements". After this sample time has elapsed, the A/D conversion can be started.

These steps should be followed for doing an A/D conversion:

- 1. Configure the A/D module:

- Configure analog/digital I/O (ANSEL)

- Configure voltage reference (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D conversion clock (ADCON0)

- Turn on A/D module (ADCON0)

- 2. Configure A/D interrupt (if desired):

- Clear ADIF bit

- Set ADIE bit

- SET PEIE bit

- Set GIE bit

- 3. Wait the required acquisition time.

- 4. Start conversion:

- Set GO/DONE bit (ADCON0)

- 5. Wait for A/D conversion to complete, by either:

- Polling for the GO/DONE bit to be cleared (with interrupts disabled); OR

- Waiting for the A/D interrupt

- 6. Read A/D Result register pair (ADRESH: ADRESL), clear bit ADIF if required.

- For next conversion, go to step 1 or step 2 as 7. required. The A/D conversion time per bit is defined as TAD. A minimum wait of 2 TAD is required before the next acquisition starts.

#### **FIGURE 12-1:** A/D BLOCK DIAGRAM

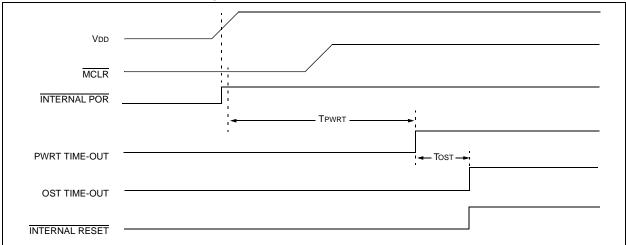

### FIGURE 15-5: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD THROUGH RC NETWORK): CASE 2

### 17.7 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

### 17.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs PIC<sup>®</sup> Flash MCUs and dsPIC<sup>®</sup> Flash DSCs with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with incircuit debugger systems (RJ11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

### 17.9 MPLAB ICD 3 In-Circuit Debugger System

MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost effective high-speed hardware debugger/programmer for Microchip Flash Digital Signal Controller (DSC) and microcontroller (MCU) devices. It debugs and programs PIC<sup>®</sup> Flash microcontrollers and dsPIC<sup>®</sup> DSCs with the powerful, yet easyto-use graphical user interface of MPLAB Integrated Development Environment (IDE).

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

### 17.10 PICkit 3 In-Circuit Debugger/ Programmer and PICkit 3 Debug Express

The MPLAB PICkit 3 allows debugging and programming of PIC<sup>®</sup> and dsPIC<sup>®</sup> Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB Integrated Development Environment (IDE). The MPLAB PICkit 3 is connected to the design engineer's PC using a full speed USB interface and can be connected to the target via an Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup>.

The PICkit 3 Debug Express include the PICkit 3, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

### 18.1 DC Characteristics: Supply Voltage PIC16F87/88 (Industrial, Extended) PIC16LF87/88 (Industrial)

| PIC16LF87/88<br>(Industrial) |        |                                                                     |      | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial                                                      |      |       |                                                        |  |  |  |  |  |

|------------------------------|--------|---------------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------------------------------------------------------|--|--|--|--|--|

| PIC16F87/88                  |        |                                                                     |      | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |      |       |                                                        |  |  |  |  |  |

| Param<br>No.                 | Symbol | Symbol Characteristic                                               |      | Тур                                                                                                                                                                                     | Max  | Units | Conditions                                             |  |  |  |  |  |

|                              | Vdd    | Supply Voltage                                                      |      |                                                                                                                                                                                         |      |       |                                                        |  |  |  |  |  |

| D001                         |        | PIC16LF87/88                                                        | 2.0  | _                                                                                                                                                                                       | 5.5  | V     | HS, XT, RC and LP Oscillator mode                      |  |  |  |  |  |

| D001                         |        | PIC16F87/88                                                         | 4.0  |                                                                                                                                                                                         | 5.5  | V     |                                                        |  |  |  |  |  |

| D002                         | Vdr    | RAM Data Retention<br>Voltage <sup>(1)</sup>                        | 1.5  | —                                                                                                                                                                                       | —    | V     |                                                        |  |  |  |  |  |

| D003                         | VPOR   | VDD Start Voltage<br>to ensure internal<br>Power-on Reset signal    | _    | _                                                                                                                                                                                       | 0.7  | V     | See Section 15.4 "Power-on Reset (POR)"<br>for details |  |  |  |  |  |

| D004                         | SVDD   | <b>VDD Rise Rate</b><br>to ensure internal<br>Power-on Reset signal | 0.05 | _                                                                                                                                                                                       | —    | V/ms  | See Section 15.4 "Power-on Reset (POR)"<br>for details |  |  |  |  |  |

|                              | VBOR   | Brown-out Reset Voltage                                             |      | •                                                                                                                                                                                       |      | •     |                                                        |  |  |  |  |  |

| D005                         |        | PIC16LF87/88                                                        |      |                                                                                                                                                                                         | 4.35 | V     |                                                        |  |  |  |  |  |

| D005                         |        | PIC16F87/88                                                         | 3.65 |                                                                                                                                                                                         | 4.35 | V     | Fmax = 14 MHz <sup>(2)</sup>                           |  |  |  |  |  |

**Legend:** Shading of rows is to assist in readability of the table.

Note 1: This is the limit to which VDD can be lowered in Sleep mode, or during a device Reset, without losing RAM data.

2: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

| <b>Operating Conditions:</b> 3.0V < VDD < 5.5V, -40°C < TA < +85°C, unless otherwise stated |        |                                            |     |      |            |          |                             |  |  |

|---------------------------------------------------------------------------------------------|--------|--------------------------------------------|-----|------|------------|----------|-----------------------------|--|--|

| Param<br>No.                                                                                | Sym    | Characteristics                            | Min | Тур  | Мах        | Units    | Comments                    |  |  |

| D300                                                                                        | VIOFF  | Input Offset Voltage                       |     | ±5.0 | ±10        | mV       |                             |  |  |

| D301                                                                                        | VICM   | Input Common Mode Voltage*                 | 0   |      | Vdd - 1.5  | V        |                             |  |  |

| D302                                                                                        | CMRR   | Common Mode Rejection Ratio*               | 55  | —    | —          | dB       |                             |  |  |

| 300<br>300A                                                                                 | TRESP  | Response Time <sup>(1)*</sup>              | _   | 150  | 400<br>600 | ns<br>ns | PIC16F87/88<br>PIC16LF87/88 |  |  |

| 301                                                                                         | TMC20V | Comparator Mode Change to<br>Output Valid* | _   | —    | 10         | μS       |                             |  |  |

### TABLE 18-1: COMPARATOR SPECIFICATIONS

\* These parameters are characterized but not tested.

**Note 1:** Response time measured with one comparator input at (VDD – 1.5)/2 while the other input transitions from Vss to VDD.

### TABLE 18-2: VOLTAGE REFERENCE SPECIFICATIONS

| <b>Operating Conditions:</b> 3.0V < VDD < 5.5V, -40°C < TA < +85°C, unless otherwise stated |      |                               |        |     |        |       |                       |  |  |  |

|---------------------------------------------------------------------------------------------|------|-------------------------------|--------|-----|--------|-------|-----------------------|--|--|--|

| Spec<br>No.                                                                                 | Sym  | Characteristics               | Min    | Тур | Max    | Units | Comments              |  |  |  |

| D310                                                                                        | VRES | Resolution                    | Vdd/24 |     | VDD/32 | LSb   |                       |  |  |  |

| D311                                                                                        | VRAA | Absolute Accuracy             | —      | -   | 1/2    | LSb   | Low Range (CVRR = 1)  |  |  |  |

|                                                                                             |      |                               |        | —   | 1/2    | LSb   | High Range (CVRR = 0) |  |  |  |

| D312                                                                                        | VRur | Unit Resistor Value (R)*      | —      | 2k  | —      | Ω     |                       |  |  |  |

| 310                                                                                         | TSET | Settling Time <sup>(1)*</sup> | —      | —   | 10     | μS    |                       |  |  |  |

\* These parameters are characterized but not tested.

**Note 1:** Settling time measured while CVRR = 1 and CVR<3:0> transitions from '0000' to '1111'.

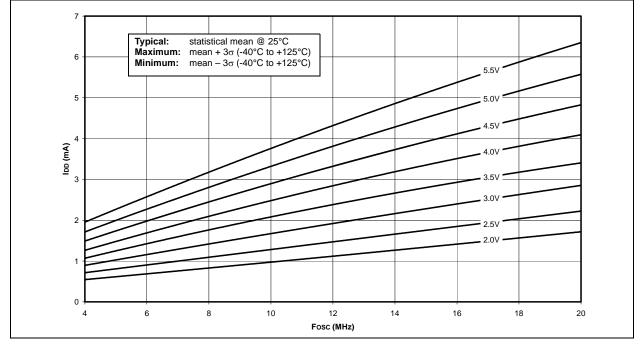

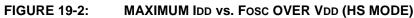

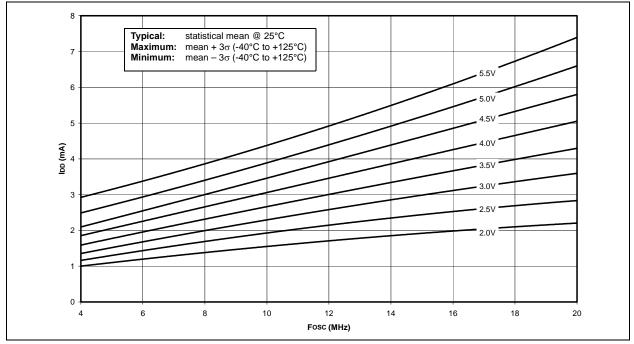

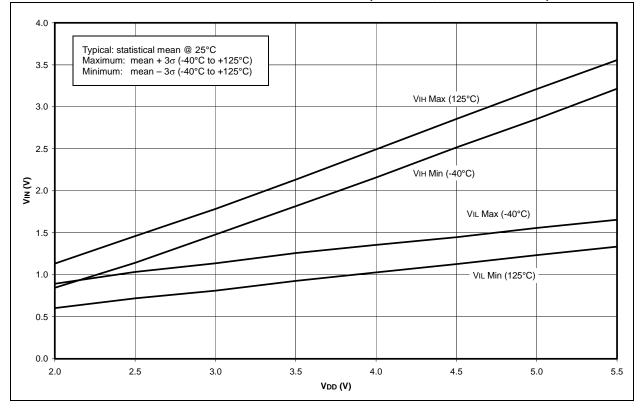

### 19.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over the whole temperature range.

#### FIGURE 19-23: MINIMUM AND MAXIMUM VIN vs. VDD (ST INPUT, -40°C TO +125°C)

NOTES:

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

### QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MTP, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

Analog-for-the-Digital Age, Application Maestro, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, SQI, Serial Quad I/O, Total Endurance, TSHARC, UniWinDriver, WiperLock, ZENA and Z-Scale are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

GestIC and ULPP are registered trademarks of Microchip Technology Germany II GmbH & Co. & KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2002-2013, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 9781620769416

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEEL0Q® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.