Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 16                                                                      |

| Program Memory Size        | 7KB (4K x 14)                                                           |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 256 x 8                                                                 |

| RAM Size                   | 368 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                               |

| Data Converters            | A/D 7x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                          |

| Supplier Device Package    | 18-SOIC                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f88-e-so |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

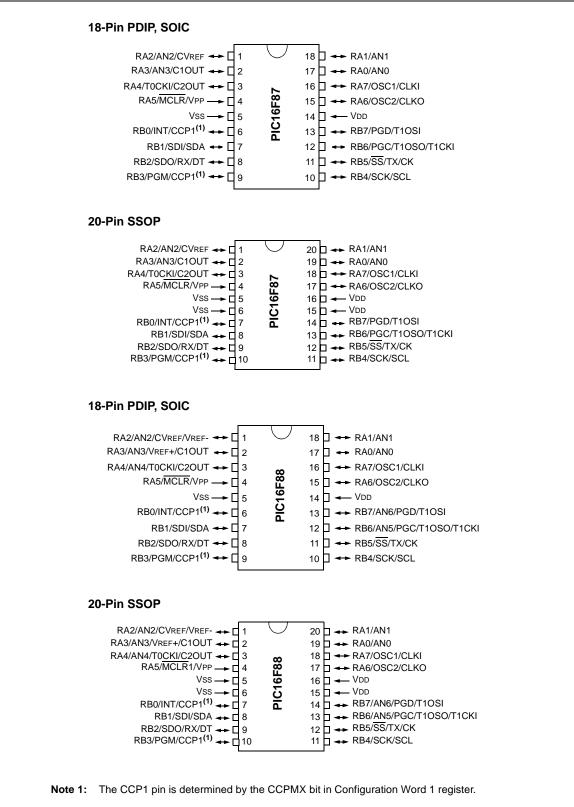

### Pin Diagrams

## 2.0 MEMORY ORGANIZATION

There are two memory blocks in the PIC16F87/88 devices. These are the program memory and the data memory. Each block has its own bus, so access to each block can occur during the same oscillator cycle.

The data memory can be further broken down into the general purpose RAM and the Special Function Registers (SFRs). The operation of the SFRs that control the "core" are described here. The SFRs used to control the peripheral modules are described in the section discussing each individual peripheral module.

The data memory area also contains the data EEPROM memory. This memory is not directly mapped into the data memory but is indirectly mapped. That is, an indirect address pointer specifies the address of the data EEPROM memory to read/write. The PIC16F87/88 device's 256 bytes of data EEPROM memory have the address range of 00h-FFh. More details on the EEPROM memory can be found in Section 3.0 "Data EEPROM and Flash Program Memory".

Additional information on device memory may be found in the "*PIC*<sup>®</sup> *Mid-Range MCU Family Reference Manual*" (DS33023).

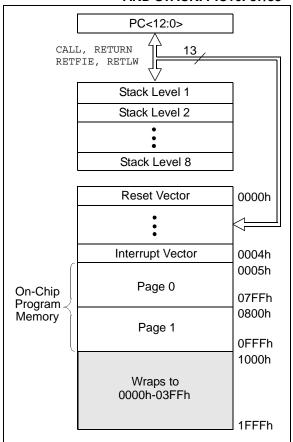

## 2.1 Program Memory Organization

The PIC16F87/88 devices have a 13-bit program counter capable of addressing an 8K x 14 program memory space. For the PIC16F87/88, the first 4K x 14 (0000h-0FFFh) is physically implemented (see Figure 2-1). Accessing a location above the physically implemented address will cause a wraparound. For example, the same instruction will be accessed at locations 020h, 420h, 820h, C20h, 1020h, 1420h, 1820h and 1C20h.

The Reset vector is at 0000h and the interrupt vector is at 0004h.

### FIGURE 2-1:

#### PROGRAM MEMORY MAP AND STACK: PIC16F87/88

## 2.2 Data Memory Organization

The data memory is partitioned into multiple banks that contain the General Purpose Registers and the Special Function Registers. Bits RP1 (STATUS<6>) and RP0 (STATUS<5>) are the bank select bits.

| RP1:RP0 | Bank |

|---------|------|

| 00      | 0    |

| 01      | 1    |

| 10      | 2    |

| 11      | 3    |

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM. All implemented banks contain SFRs. Some "high use" SFRs from one bank may be mirrored in another bank for code reduction and quicker access (e.g., the STATUS register is in Banks 0-3).

Note: EEPROM data memory description can be found in Section 3.0 "Data EEPROM and Flash Program Memory" of this data sheet.

| Address               | Name       | Bit 7       | Bit 6          | Bit 5         | Bit 4         | Bit 3          | Bit 2           | Bit 1         | Bit 0    | Value on:<br>POR, BOR  | Details<br>on<br>page |

|-----------------------|------------|-------------|----------------|---------------|---------------|----------------|-----------------|---------------|----------|------------------------|-----------------------|

| Bank 2                |            |             |                |               |               |                |                 |               |          |                        |                       |

| 100h <sup>(2)</sup>   | INDF       | Addressing  | egister)       | 0000 0000     | 26, 135       |                |                 |               |          |                        |                       |

| 101h                  | TMR0       | Timer0 Mc   | dule Registe   | er            |               |                |                 |               |          | xxxx xxxx              | 69                    |

| 102h <sup>(2)</sup>   | PCL        | Program C   | Counter's (PC  | C) Least Sign | ificant Byte  |                |                 |               |          | 0000 0000              | 135                   |

| 103h <sup>(2)</sup>   | STATUS     | IRP         | RP1            | RP0           | TO            | PD             | Z               | DC            | С        | 0001 1xxx              | 17                    |

| 104h <sup>(2)</sup>   | FSR        | Indirect Da | ata Memory /   | Address Poin  | iter          |                |                 |               |          | xxxx xxxx              | 135                   |

| 105h                  | WDTCON     | _           | _              | _             | WDTPS3        | WDTPS2         | WDTPS1          | WDTPS0        | SWDTEN   | 0 1000                 | 142                   |

| 106h                  | PORTB      |             |                |               |               | hen read (PIC  |                 |               |          | xxxx xxxx<br>00xx xxxx | 58                    |

| 107h                  | _          | Unimplem    | ented          |               |               |                |                 |               |          | —                      | —                     |

| 108h                  | _          | Unimplem    | ented          |               |               |                |                 |               |          | _                      |                       |

| 109h                  | —          | Unimplem    | ented          |               |               |                |                 |               |          | —                      | _                     |

| 10Ah <b>(1,2)</b>     | PCLATH     | _           | -              | -             | Write Buffer  | for the Upper  | 5 bits of the F | Program Cou   | unter    | 0 0000                 | 135                   |

| 10Bh <sup>(2)</sup>   | INTCON     | GIE         | PEIE           | TMR0IE        | INT0IE        | RBIE           | TMR0IF          | INTOIF        | RBIF     | 0000 000x              | 19, 69,<br>77         |

| 10Ch                  | EEDATA     | EEPROM/     | Flash Data F   | Register Low  | Byte          |                |                 |               |          | xxxx xxxx              | 34                    |

| 10Dh                  | EEADR      | EEPROM/     | Flash Addre    | ss Register L | ow Byte       |                |                 |               |          | xxxx xxxx              | 34                    |

| 10Eh                  | EEDATH     | —           | _              | EEPROM/F      | lash Data Re  | gister High By | te              |               |          | xx xxxx                | 34                    |

| 10Fh                  | EEADRH     | —           | —              | —             | —             | EEPROM/Fla     | ash Address F   | Register High | n Byte   | xxxx                   | 34                    |

| Bank 3                |            |             |                |               |               |                |                 |               |          |                        |                       |

| 180h <sup>(2)</sup>   | INDF       | Addressing  | g this locatio | n uses conte  | nts of FSR to | address data   | memory (not     | a physical r  | egister) | 0000 0000              | 135                   |

| 181h                  | OPTION_REG | RBPU        | INTEDG         | TOCS          | TOSE          | PSA            | PS2             | PS1           | PS0      | 1111 1111              | 18, 69                |

| 182h <sup>(2)</sup>   | PCL        | Program C   | Counter (PC)   | Least Signif  | ficant Byte   | •              |                 | •             |          | 0000 0000              | 135                   |

| 183h <sup>(2)</sup>   | STATUS     | IRP         | RP1            | RP0           | TO            | PD             | Z               | DC            | С        | 0001 1xxx              | 17                    |

| 184h <sup>(2)</sup>   | FSR        | Indirect Da | ata Memory A   | Address Poin  | ter           | •              |                 | •             |          | xxxx xxxx              | 135                   |

| 185h                  | _          | Unimplem    | ented          |               |               |                |                 |               |          | _                      | _                     |

| 186h                  | TRISB      | PORTB Da    | ata Direction  | Register      |               |                |                 |               |          | 1111 1111              | 58, 83                |

| 187h                  | —          | Unimplem    | ented          |               |               |                |                 |               |          | —                      | _                     |

| 188h                  | —          | Unimplem    | ented          |               |               |                |                 |               |          | —                      | _                     |

| 189h                  | —          | Unimplem    | ented          |               |               |                |                 |               |          | —                      | _                     |

| 18Ah <sup>(1,2)</sup> | PCLATH     | _           | _              | —             | Write Buffer  | for the Upper  | 5 bits of the F | Program Cou   | unter    | 0 0000                 | 135                   |

| 18Bh <sup>(2)</sup>   | INTCON     | GIE         | PEIE           | TMR0IE        | INTOIE        | RBIE           | TMR0IF          | INTOIF        | RBIF     | 0000 000x              | 19, 69,<br>77         |

| 18Ch                  | EECON1     | EEPGD       | _              | —             | FREE          | WRERR          | WREN            | WR            | RD       | xx x000                | 28, 34                |

| 18Dh                  | EECON2     | EEPROM      | Control Regi   | ster 2 (not a | physical regi | ster)          |                 |               |          |                        | 34                    |

| 18Eh                  | —          | Reserved,   | maintain cle   | ar            |               |                |                 |               |          | 0000 0000              | _                     |

| 18Fh                  | —          | Reserved,   | maintain cle   | ar            |               |                |                 |               |          | 0000 0000              | _                     |

## TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

**Note 1:** The upper byte of the program counter is not directly accessible. PCLATH is a holding register for PC<12:8>, whose contents are transferred to the upper byte of the program counter.

2: These registers can be addressed from any bank.

3: RA5 is an input only; the state of the TRISA5 bit has no effect and will always read '1'.

4: PIC16F88 device only.

### 2.2.2.1 STATUS Register

The STATUS register, shown in Register 2-1, contains the arithmetic status of the ALU, the Reset status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as '000u uluu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register because these instructions do not affect the Z, C or DC bits from the STATUS register. For other instructions not affecting any Status bits, see Section 16.0 "Instruction Set Summary".

Note: The C and DC bits operate as a borrow and digit borrow bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

### REGISTER 2-1: STATUS: ARITHMETIC STATUS REGISTER (ADDRESS 03h, 83h, 103h, 183h)

|         | R/W-0                                                                                                   | R/W-0                                                     | R/W-0 | R-1            | R-1           | R/W-x        | R/W-x         | R/W-x     |  |  |  |  |  |

|---------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-------|----------------|---------------|--------------|---------------|-----------|--|--|--|--|--|

|         | IRP                                                                                                     | RP1                                                       | RP0   | TO             | PD            | Z            | DC            | С         |  |  |  |  |  |

|         | bit 7                                                                                                   |                                                           |       |                |               |              |               | bit 0     |  |  |  |  |  |

| bit 7   | 1 = Bank                                                                                                | ster Bank Sel<br>2, 3 (100h-1F<br>0, 1 (00h-FFt           | Fh)   | for indirect a | ddressing)    |              |               |           |  |  |  |  |  |

| bit 6-5 | <b>RP&lt;1:0&gt;:</b> Register Bank Select bits (used for direct addressing)<br>11 = Bank 3 (180h-1FFh) |                                                           |       |                |               |              |               |           |  |  |  |  |  |

|         | 01 = Bank<br>00 = Bank                                                                                  | 2 (100h-17F<br>1 (80h-FFh)<br>0 (00h-7Fh)<br>is 128 bytes |       |                |               |              |               |           |  |  |  |  |  |

| bit 4   | TO: Time-                                                                                               | out bit                                                   |       |                |               |              |               |           |  |  |  |  |  |

|         |                                                                                                         | power-up, CL                                              |       | tion or SLEE   | P instruction | n            |               |           |  |  |  |  |  |

| bit 3   | PD: Power-Down bit                                                                                      |                                                           |       |                |               |              |               |           |  |  |  |  |  |

|         |                                                                                                         | power-up or b<br>ecution of the                           |       |                |               |              |               |           |  |  |  |  |  |

| bit 2   | Z: Zero bit                                                                                             | t                                                         |       |                |               |              |               |           |  |  |  |  |  |

|         |                                                                                                         | esult of an ari<br>esult of an ari                        |       |                |               |              |               |           |  |  |  |  |  |

| bit 1   | DC: Digit carry/borrow bit (ADDWF, ADDLW, SUBLW and SUBWF instructions) <sup>(1)</sup>                  |                                                           |       |                |               |              |               |           |  |  |  |  |  |

|         |                                                                                                         | ry-out from the<br>arry-out from t                        |       |                |               | red          |               |           |  |  |  |  |  |

| bit 0   | C: Carry/borrow bit (ADDWF, ADDLW, SUBLW and SUBWF instructions) <sup>(1,2)</sup>                       |                                                           |       |                |               |              |               |           |  |  |  |  |  |

|         |                                                                                                         | ry-out from the                                           | 0     |                |               |              |               |           |  |  |  |  |  |

|         | Note 1:                                                                                                 | For borrow, t complement                                  |       |                | subtractior   | n is execute | d by adding   | the two's |  |  |  |  |  |

|         | 2:                                                                                                      | For rotate (R:<br>bit of the sou                          |       | ructions, this | bit is loade  | d with eithe | r the high or | low-order |  |  |  |  |  |

|         | Logondy                                                                                                 |                                                           |       |                |               |              |               |           |  |  |  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

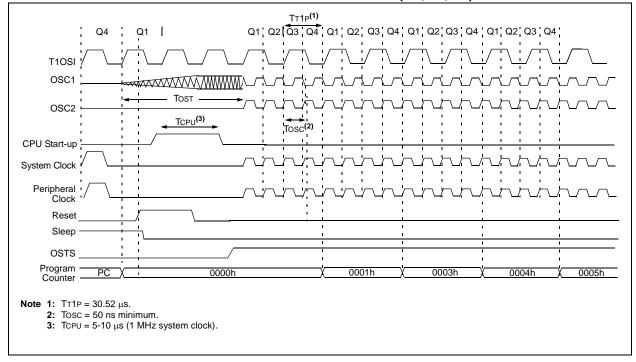

### 4.7.3 SEC\_RUN/RC\_RUN TO PRIMARY CLOCK SOURCE

When switching from a SEC\_RUN or RC\_RUN mode back to the primary system clock, following a change of SCS<1:0> to '00', the sequence of events that takes place will depend upon the value of the FOSC bits in the Configuration register. If the primary clock source is configured as a crystal (HS, XT or LP), then the transition will take place after 1024 clock cycles. This is necessary because the crystal oscillator has been powered down until the time of the transition. In order to provide the system with a reliable clock when the changeover has occurred, the clock will not be released to the changeover circuit until the 1024 count has expired.

During the oscillator start-up time, the system clock comes from the current system clock. Instruction execution and/or peripheral operation continues using the currently selected oscillator as the CPU clock source, until the necessary clock count has expired, to ensure that the primary system clock is stable.

To know when the OST has expired, the OSTS bit should be monitored. OSTS = 1 indicates that the Oscillator Start-up Timer has timed out and the system clock comes from the primary clock source.

Following the oscillator start-up time, the internal Q clocks are held in the Q1 state until eight falling edge clocks are counted from the primary system clock. The clock input to the Q clocks is then released and operation resumes with the primary system clock determined by the FOSC bits (see Figure 4-10).

When in SEC\_RUN mode, the act of clearing the T1OSCEN bit in the T1CON register will cause SCS<0> to be cleared, which causes the SCS<1:0> bits to revert to '00' or '10' depending on what SCS<1> is. Although the T1OSCEN bit was cleared, T1OSC will be enabled and instruction execution will continue until the OST time-out for the main system clock is complete. At that time, the system clock will switch from the T1OSC to the primary clock or the INTRC. Following this, the T1 oscillator will be shut down.

Note: If the primary system clock is either RC or EC, an internal delay timer (5-10 μs) will suspend operation after exiting Secondary Clock mode to allow the CPU to become ready for code execution.

## 4.7.3.1 Returning to Primary Clock Source Sequence

Changing back to the primary oscillator from SEC\_RUN or RC\_RUN can be accomplished by either changing SCS<1:0> to '00', or clearing the T1OSCEN bit in the T1CON register (if T1OSC was the secondary clock).

The sequence of events that follows is the same for both modes:

- If the primary system clock is configured as EC, RC or INTRC, then the OST time-out is skipped. Skip to step 3.

- 2. If the primary system clock is configured as an external oscillator (HS, XT, LP), then the OST will be active, waiting for 1024 clocks of the primary system clock.

- 3. On the following Q1, the device holds the system clock in Q1.

- 4. The device stays in Q1 while eight falling edges of the primary system clock are counted.

- 5. Once the eight counts transpire, the device begins to run from the primary oscillator.

- If the secondary clock was INTRC and the primary is not INTRC, the INTRC will be shut down to save current providing that the INTRC is not being used for any other function, such as WDT or Fail-Safe Clock monitoring.

- If the secondary clock was T1OSC, the T1OSC will continue to run if T1OSCEN is still set; otherwise, the T1 oscillator will be shut down.

## 4.7.3.2 Returning to Primary Oscillator with a Reset

A Reset will clear SCS<1:0> back to '00'. The sequence for starting the primary oscillator following a Reset is the same for all forms of Reset, including POR. There is no transition sequence from the alternate system clock to the primary system clock on a Reset condition. Instead, the device will reset the state of the OSCCON register and default to the primary system clock. The sequence of events that takes place after this will depend upon the value of the FOSC bits in the Configuration register. If the external oscillator is configured as a crystal (HS, XT or LP), the CPU will be held in the Q1 state until 1024 clock cycles have transpired on the primary clock. This is necessary because the crystal oscillator has been powered down until the time of the transition.

During the oscillator start-up time, instruction execution and/or peripheral operation is suspended.

| Note: | If Two-Speed Clock Start-up mode is       |

|-------|-------------------------------------------|

|       | enabled, the INTRC will act as the system |

|       | clock until the OST timer has timed out.  |

If the primary system clock is either RC, EC or INTRC, the CPU will begin operating on the first Q1 cycle following the wake-up event. This means that there is no oscillator start-up time required because the primary clock is already stable; however, there is a delay between the wake-up event and the following Q2. An internal delay timer of 5-10  $\mu$ s will suspend operation after the Reset to allow the CPU to become ready for code execution. The CPU and peripheral clock will be held in the first Q1.

The sequence of events is as follows:

- 1. A device Reset is asserted from one of many sources (WDT, BOR, MCLR, etc.).

- 2. The device resets and the CPU start-up timer is enabled if in Sleep mode. The device is held in Reset until the CPU start-up time-out is complete.

- 3. If the primary system clock is configured as an external oscillator (HS, XT, LP), then the OST will be active waiting for 1024 clocks of the primary system clock. While waiting for the OST, the device will be held in Reset. The OST and CPU start-up timers run in parallel.

- After both the CPU start-up and OST timers have timed out, the device will wait for one additional clock cycle and instruction execution will begin.

FIGURE 4-10: PRIMARY SYSTEM CLOCK AFTER RESET (HS, XT, LP)

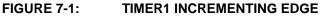

### 7.2 Timer1 Operation in Timer Mode

Timer mode is selected by clearing the TMR1CS (T1CON<1>) bit. In this mode, the input clock to the timer is FOSC/4. The synchronize control bit, T1SYNC (T1CON<2>), has no effect since the internal clock is always in sync.

### 7.3 Timer1 Counter Operation

Timer1 may operate in Asynchronous or Synchronous mode, depending on the setting of the TMR1CS bit.

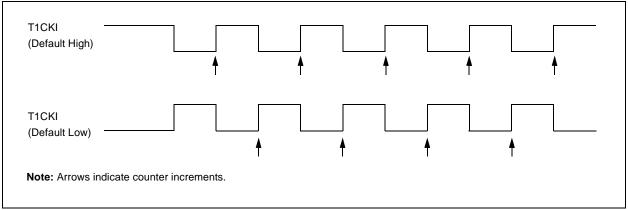

When Timer1 is being incremented via an external source, increments occur on a rising edge. After Timer1 is enabled in Counter mode, the module must first have a falling edge before the counter begins to increment.

### 7.4 Timer1 Operation in Synchronized Counter Mode

Counter mode is selected by setting bit TMR1CS. In this mode, the timer increments on every rising edge of clock input on pin RB7/PGD/T1OSI when bit T1OSCEN is set, or on pin RB6/PGC/T1OSO/T1CKI when bit T1OSCEN is cleared.

If  $\overline{\text{T1SYNC}}$  is cleared, then the external clock input is synchronized with internal phase clocks. The synchronization is done after the prescaler stage. The prescaler stage is an asynchronous ripple counter.

In this configuration, during Sleep mode, Timer1 will not increment even if the external clock is present since the synchronization circuit is shut off. The prescaler, however, will continue to increment.

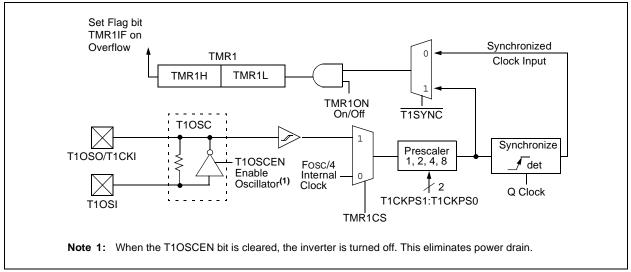

## 9.2 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the CCP1 pin is:

- Driven high

- Driven low

- · Remains unchanged

The action on the pin is based on the value of control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time, interrupt flag bit, CCP1IF, is set.

### FIGURE 9-2: COMPARE MODE OPERATION BLOCK DIAGRAM

### 9.2.1 CCP PIN CONFIGURATION

The user must configure the CCP1 pin as an output by clearing the TRISB<x> bit.

- Note 1: Clearing the CCP1CON register will force the CCP1 compare output latch to the default low level. This is not the data latch.

- 2: The TRISB bit (0 or 3) is dependent upon the setting of configuration bit 12 (CCPMX).

### 9.2.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

### 9.2.3 SOFTWARE INTERRUPT MODE

When generate software interrupt is chosen, the CCP1 pin is not affected. Only a CCP interrupt is generated (if enabled).

### 9.2.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated that may be used to initiate an action.

The special event trigger output of CCP1 resets the TMR1 register pair and starts an A/D conversion (if the A/D module is enabled). This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

Note: The special event trigger from the CCP1 module will not set interrupt flag bit TMR1IF (PIR1<0>).

### TABLE 9-2: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE AND TIMER1

| Address              | Name    | Bit 7  | Bit 6               | Bit 5         | Bit 4         | Bit 3       | Bit 2        | Bit 1    | Bit 0  |      | e on<br>BOR | all c | ie on<br>other<br>sets |

|----------------------|---------|--------|---------------------|---------------|---------------|-------------|--------------|----------|--------|------|-------------|-------|------------------------|

| 0Bh,8Bh<br>10BH,18Bh | INTCON  | GIE    | PEIE                | TMR0IE        | INTOIE        | RBIE        | TMR0IF       | INTOIF   | RBIF   | 0000 | 000x        | 0000  | 000u                   |

| 0Ch                  | PIR1    | _      | ADIF <sup>(1)</sup> | RCIF          | TXIF          | SSPIF       | CCP1IF       | TMR2IF   | TMR1IF | -000 | 0000        | -000  | 0000                   |

| 8Ch                  | PIE1    | _      | ADIE <sup>(1)</sup> | RCIE          | TXIE          | SSPIE       | CCP1IE       | TMR2IE   | TMR1IE | -000 | 0000        | -000  | 0000                   |

| 86h                  | TRISB   | PORT   | B Data Di           | irection Re   | gister        |             |              |          |        | 1111 | 1111        | 1111  | 1111                   |

| 0Eh                  | TMR1L   | Holdin | g Registe           | er for the Le | east Signific | ant Byte of | the 16-bit   | TMR1 Reg | gister | xxxx | xxxx        | uuuu  | uuuu                   |

| 0Fh                  | TMR1H   | Holdin | g Registe           | r for the M   | ost Signific  | ant Byte of | the 16-bit 7 | FMR1 Reg | ister  | xxxx | xxxx        | uuuu  | uuuu                   |

| 10h                  | T1CON   | —      | T1RUN               | T1CKPS1       | T1CKPS0       | T1OSCEN     | T1SYNC       | TMR1CS   | TMR1ON | -000 | 0000        | -uuu  | uuuu                   |

| 15h                  | CCPR1L  | Captu  | re/Compa            | re/PWM R      | egister 1 (L  | .SB)        |              |          |        | xxxx | xxxx        | uuuu  | uuuu                   |

| 16h                  | CCPR1H  | Captu  | re/Compa            | re/PWM R      | egister 1 (N  | ISB)        |              |          |        | xxxx | xxxx        | uuuu  | uuuu                   |

| 17h                  | CCP1CON |        | —                   | CCP1X         | CCP1Y         | CCP1M3      | CCP1M2       | CCP1M1   | CCP1M0 | 00   | 0000        | 00    | 0000                   |

**Note 1:** This bit is only implemented on the PIC16F88. The bit will read '0' on the PIC16F87.

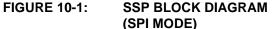

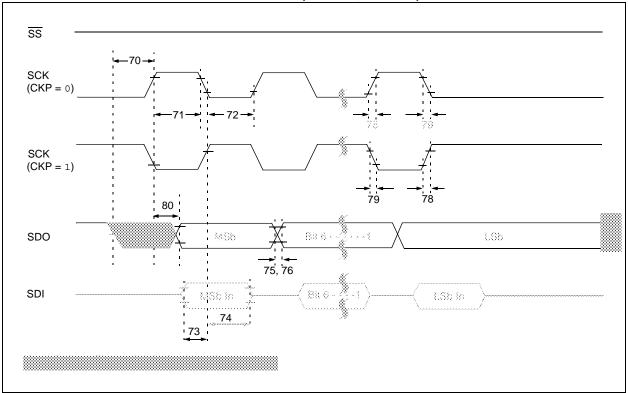

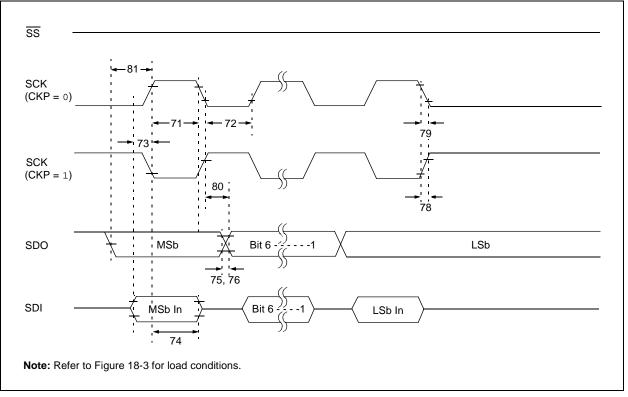

To enable the serial port, SSP Enable bit, SSPEN (SSPCON<5>), must be set. To reset or reconfigure SPI mode, clear bit SSPEN, reinitialize the SSPCON register and then set bit SSPEN. This configures the SDI, SDO, SCK and SS pins as serial port pins. For the pins to behave as the serial port function, they must have their data direction bits (in the TRISB register) appropriately programmed. That is:

- SDI must have TRISB<1> set

- SDO must have TRISB<2> cleared

- SCK (Master mode) must have TRISB<4> cleared

- SCK (Slave mode) must have TRISB<4> set

- SS must have TRISB<5> set

- Note 1: When the SPI is in Slave mode with SS pin control enabled (SSPCON<3:0> = 0100), the SPI module will reset if the SS pin is set to VDD.

- **2:** If the SPI is used in Slave mode with CKE = 1, then the  $\overline{SS}$  pin control must be enabled.

| TABLE 10-1: | <b>REGISTERS ASSOCIATED WITH SPI OPERATION</b> |

|-------------|------------------------------------------------|

|-------------|------------------------------------------------|

| Address              | Name    | Bit 7   | Bit 6               | Bit 5       | Bit 4      | Bit 3     | Bit 2       | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|----------------------|---------|---------|---------------------|-------------|------------|-----------|-------------|--------|--------|----------------------|---------------------------------|

| 0Bh,8Bh<br>10Bh,18Bh | INTCON  | GIE     | PEIE                | TMR0IE      | INT0IE     | RBIE      | TMR0IF      | INTOIF | RBIF   | 0000 000x            | 0000 000u                       |

| 0Ch                  | PIR1    | _       | ADIF <sup>(1)</sup> | RCIF        | TXIF       | SSPIF     | CCP1IF      | TMR2IF | TMR1IF | -000 0000            | -000 0000                       |

| 8Ch                  | PIE1    | _       | ADIE <sup>(1)</sup> | RCIE        | TXIE       | SSPIE     | CCP1IE      | TMR2IE | TMR1IE | -000 0000            | -000 0000                       |

| 86h                  | TRISB   | PORTB   | Data Dire           | ction Regis | ster       |           |             |        |        | 1111 1111            | 1111 1111                       |

| 13h                  | SSPBUF  | Synchro | nous Seria          | al Port Red | ceive Buff | er/Transn | nit Registe | r      |        | xxxx xxxx            | uuuu uuuu                       |

| 14h                  | SSPCON  | WCOL    | SSPOV               | SSPEN       | CKP        | SSPM3     | SSPM2       | SSPM1  | SSPM0  | 0000 0000            | 0000 0000                       |

| 94h                  | SSPSTAT | SMP     | CKE                 | D/A         | Р          | S         | R/W         | UA     | BF     | 0000 0000            | 0000 0000                       |

**Legend:** x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the SSP in SPI mode.**Note 1:**This bit is only implemented on the PIC16F88. The bit will read '0' on the PIC16F87.

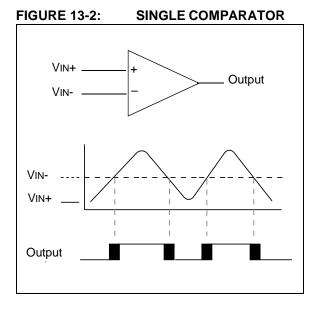

## 13.0 COMPARATOR MODULE

The comparator module contains two analog comparators. The inputs to the comparators are multiplexed with I/O port pins RA0 through RA3, while the outputs are multiplexed to pins RA3 and RA4. The on-chip Voltage Reference (Section 14.0 "Comparator Voltage Reference Module") can also be an input to the comparators.

The CMCON register (Register 13-1) controls the comparator input and output multiplexors. A block diagram of the various comparator configurations is shown in Figure 13-1.

| REGISTER 13-1: | CMCON: COMPARATOR MODULE CONTROL REGISTER (ADDRESS 9Ch) |

|----------------|---------------------------------------------------------|

|----------------|---------------------------------------------------------|

|         | R-0                                                                                                                          | R-0                                                                      | R/W-0        | R/W-0      | R/W-0      | R/W-1     | R/W-1         | R/W-1 |  |  |  |  |  |  |

|---------|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------|------------|------------|-----------|---------------|-------|--|--|--|--|--|--|

|         | C2OUT                                                                                                                        | C10UT                                                                    | C2INV        | C1INV      | CIS        | CM2       | CM1           | CM0   |  |  |  |  |  |  |

|         | bit 7                                                                                                                        |                                                                          |              |            | •          |           |               | bit 0 |  |  |  |  |  |  |

| bit 7   | C2OUT: Con                                                                                                                   | -                                                                        | Output bit   |            |            |           |               |       |  |  |  |  |  |  |

|         | $\frac{\text{When C2INV} = 0:}{1 = C2 \text{ VIN+ } > C2 \text{ VIN-}}$<br>0 = C2 VIN+ < C2 VIN-                             |                                                                          |              |            |            |           |               |       |  |  |  |  |  |  |

|         | <u>When C2INV</u><br>1 = C2 VIN+                                                                                             | < C2 VIN-                                                                |              |            |            |           |               |       |  |  |  |  |  |  |

|         | 0 = C2 VIN+                                                                                                                  |                                                                          |              |            |            |           |               |       |  |  |  |  |  |  |

| bit 6   |                                                                                                                              | C1OUT: Comparator 1 Output bit                                           |              |            |            |           |               |       |  |  |  |  |  |  |

|         | 1 = C1 VIN+                                                                                                                  | <u>When C1INV = 0:</u><br>1 = C1 VIN+ > C1 VIN-<br>0 = C1 VIN+ < C1 VIN- |              |            |            |           |               |       |  |  |  |  |  |  |

|         | When C1INV<br>1 = C1 VIN+<br>0 = C1 VIN+                                                                                     | <u>/ = 1:</u><br>< C1 Vin-                                               |              |            |            |           |               |       |  |  |  |  |  |  |

| bit 5   | C2INV: Comparator 2 Output Inversion bit                                                                                     |                                                                          |              |            |            |           |               |       |  |  |  |  |  |  |

|         | 1 = C2 outpu<br>0 = C2 outpu                                                                                                 | it inverted                                                              | -            |            |            |           |               |       |  |  |  |  |  |  |

| bit 4   | C1INV: Com                                                                                                                   | parator 1 O                                                              | utput Invers | ion bit    |            |           |               |       |  |  |  |  |  |  |

|         | 1 = C1 outpu<br>0 = C1 outpu                                                                                                 |                                                                          | ed           |            |            |           |               |       |  |  |  |  |  |  |

| bit 3   | CIS: Comparator Input Switch bit<br><u>When CM2:CM0 = 001:</u><br>1 = C1 VIN- connects to RA3<br>0 = C1 VIN- connects to RA0 |                                                                          |              |            |            |           |               |       |  |  |  |  |  |  |

|         | When CM2:CM0 = 010:<br>1 = C1 VIN- connects to RA3<br>C2 VIN- connects to RA2<br>0 = C1 VIN- connects to RA0                 |                                                                          |              |            |            |           |               |       |  |  |  |  |  |  |

| hit 2.0 |                                                                                                                              | connects to                                                              |              |            |            |           |               |       |  |  |  |  |  |  |

| bit 2-0 | CM<2:0>: Comparator Mode bits                                                                                                |                                                                          |              |            |            |           |               |       |  |  |  |  |  |  |

|         | Legend:                                                                                                                      |                                                                          |              |            |            |           |               |       |  |  |  |  |  |  |

|         | R = Readabl                                                                                                                  | e bit                                                                    | W = Wr       | itable bit | U = Unimpl | emented b | it, read as ' | 0'    |  |  |  |  |  |  |

|         |                                                                                                                              |                                                                          |              |            |            |           |               |       |  |  |  |  |  |  |

'1' = Bit is set

'0' = Bit is cleared

-n = Value at POR

x = Bit is unknown

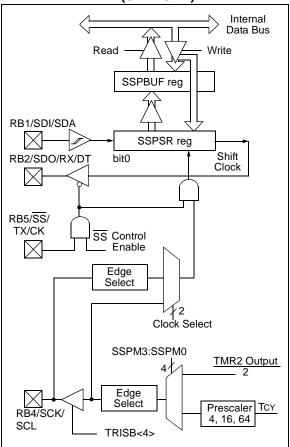

## 13.2 Comparator Operation

A single comparator is shown in Figure 13-2, along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input VIN-, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input VIN-, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 13-2 represent the uncertainty due to input offsets and response time.

### 13.3 Comparator Reference

An external or internal reference signal may be used depending on the comparator operating mode. The analog signal present at VIN- is compared to the signal at VIN+ and the digital output of the comparator is adjusted accordingly (Figure 13-2).

### 13.3.1 EXTERNAL REFERENCE SIGNAL

When external voltage references are used, the comparator module can be configured to have the comparators operate from the same, or different reference sources. However, threshold detector applications may require the same reference. The reference signal must be between Vss and VDD and can be applied to either pin of the comparator(s).

### 13.3.2 INTERNAL REFERENCE SIGNAL

The comparator module also allows the selection of an internally generated voltage reference for the comparators. Section 14.0 "Comparator Voltage Reference Module" contains a detailed description of the Comparator Voltage Reference module that provides this signal. The internal reference signal is used when comparators are in mode CM<2:0> = 010 (Figure 13-1). In this mode, the internal voltage reference is applied to the VIN+ pin of both comparators.

### 13.4 Comparator Response Time

Response time is the minimum time, after selecting a new reference voltage or input source, before the comparator output has a valid level. If the internal reference is changed, the maximum delay of the internal voltage reference must be considered when using the comparator outputs. Otherwise, the maximum delay of the comparators should be used (Section 18.0 "Electrical Characteristics").

### 13.5 Comparator Outputs

The comparator outputs are read through the CMCON register. These bits are read-only. The comparator outputs may also be directly output to the RA3 and RA4 I/O pins. When enabled, multiplexors in the output path of the RA3 and RA4 pins will switch and the output of each pin will be the unsynchronized output of the comparator. The uncertainty of each of the comparators is related to the input offset voltage and the response time given in the specifications. Figure 13-3 shows the comparator output block diagram.

The TRISA bits will still function as an output enable/ disable for the RA3 and RA4 pins while in this mode.

The polarity of the comparator outputs can be changed using the C2INV and C1INV bits (CMCON<5:4>).

- Note 1: When reading the Port register, all pins configured as analog inputs will read as '0'. Pins configured as digital inputs will convert an analog input, according to the Schmitt Trigger input specification.

- 2: Analog levels, on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR | Value on<br>all other<br>Resets |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------|---------------------------------|

| 9Dh     | CVRCON | CVREN | CVROE | CVRR  | _     | CVR3  | CVR2  | CVR1  | CVR0  | 000- 0000       | 000- 0000                       |

| 9Ch     | CMCON  | C2OUT | C10UT | C2INV | C1INV | CIS   | CM2   | CM1   | CM0   | 0000 0111       | 0000 0111                       |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used with the comparator voltage reference.

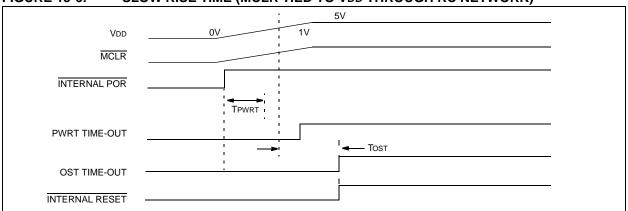

### FIGURE 15-6: SLOW RISE TIME (MCLR TIED TO VDD THROUGH RC NETWORK)

### 15.10 Interrupts

The PIC16F87/88 has up to 12 sources of interrupt. The Interrupt Control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

| Note: | Individual                             | interrupt |     | flag | bits | are | set   |  |

|-------|----------------------------------------|-----------|-----|------|------|-----|-------|--|

|       | regardless                             | of        | the | sta  | tus  | of  | their |  |

|       | corresponding mask bit or the GIE bit. |           |     |      |      |     |       |  |

A global interrupt enable bit, GIE (INTCON<7>), enables (if set) all unmasked interrupts, or disables (if cleared) all interrupts. When bit GIE is enabled and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt bits are set regardless of the status of the GIE bit. The GIE bit is cleared on Reset.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine, as well as sets the GIE bit which re-enables interrupts.

The RB0/INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flags are contained in the Special Function Register, PIR1. The corresponding interrupt enable bits are contained in Special Function Register, PIE1 and the peripheral interrupt enable bit is contained in Special Function Register, INTCON.

When an interrupt is serviced, the GIE bit is cleared to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends on when the interrupt event occurs, relative to the current Q cycle. The latency is the same for one or two cycle instructions. Individual interrupt flag bits are set regardless of the status of their corresponding mask bit, PEIE bit or the GIE bit.

| ADDLW            | Add Literal and W                                                                                                          |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                   |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                        |  |  |  |  |  |

| Operation:       | $(W) + k \to (W)$                                                                                                          |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                   |  |  |  |  |  |

| Description:     | The contents of the W register<br>are added to the eight-bit literal 'k'<br>and the result is placed in the W<br>register. |  |  |  |  |  |

| ANDWF            | AND W with f                                                                                                                                              |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] ANDWF f,d                                                                                                                                         |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                         |  |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                 |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                         |  |  |  |  |  |

| Description:     | AND the W register with register<br>'f'. If 'd' = 0, the result is stored in<br>the W register. If 'd' = 1, the result<br>is stored back in register 'f'. |  |  |  |  |  |

| ADDWF            | Add W and f                                                                                                                                                                  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                            |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                              |  |  |  |  |  |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                        |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                     |  |  |  |  |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' = 0, the result<br>is stored in the W register. If<br>'d' = 1, the result is stored back in<br>register 'f'. |  |  |  |  |  |

| BCF              | Bit Clear f                                                         |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ label ] BCF f,b                                                   |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |  |  |  |  |  |  |

| Operation:       | $0 \rightarrow (f < b >)$                                           |  |  |  |  |  |  |

| Status Affected: | None                                                                |  |  |  |  |  |  |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |  |  |  |  |  |  |

| ANDLW            | AND Literal with W                                                                                                     |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                               |  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                    |  |  |  |  |  |  |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                        |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                      |  |  |  |  |  |  |

| Description:     | The contents of W register are<br>AND'ed with the eight-bit literal<br>'k'. The result is placed in the W<br>register. |  |  |  |  |  |  |

| BSF              | Bit Set f                                                           |  |  |  |  |

|------------------|---------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ label ] BSF f,b                                                   |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |  |  |  |  |

| Operation:       | $1 \rightarrow (f < b >)$                                           |  |  |  |  |

| Status Affected: | None                                                                |  |  |  |  |

| Description:     | Bit 'b' in register 'f' is set.                                     |  |  |  |  |

## **18.0 ELECTRICAL CHARACTERISTICS**

## Absolute Maximum Ratings †

| Ambient temperature under bias                                                                                                                                               | 40°C to +125°C                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Ambient temperature under bias<br>Storage temperature                                                                                                                        | 65°C to +150°C                                     |

| Voltage on any pin with respect to Vss (except VDD and MCLR)                                                                                                                 |                                                    |

| Voltage on VDD with respect to Vss                                                                                                                                           | 0.3 to +7.5V                                       |

| Voltage on MCLR with respect to Vss (Note 2)                                                                                                                                 | 0.3 to +14V                                        |

| Total power dissipation (Note 1)                                                                                                                                             | 1W                                                 |

| Maximum current out of Vss pin                                                                                                                                               | 200 mA                                             |

| Maximum current into VDD pin                                                                                                                                                 | 200 mA                                             |

| Input clamp current, Iik (VI < 0 or VI > VDD)                                                                                                                                | ±20 mA                                             |

| Output clamp current, Ioк (Vo < 0 or Vo > VDD)                                                                                                                               | ±20 mA                                             |

| Maximum output current sunk by any I/O pin                                                                                                                                   | 25 mA                                              |

| Maximum output current sourced by any I/O pin                                                                                                                                | 25 mA                                              |

| Maximum current sunk by PORTA                                                                                                                                                | 100 mA                                             |

| Maximum current sourced by PORTA                                                                                                                                             | 100 mA                                             |

| Maximum current sunk by PORTB                                                                                                                                                | 100 mA                                             |

| Maximum current sourced by PORTB                                                                                                                                             | 100 mA                                             |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD $-\Sigma$ IOH} + $\Sigma$ {(VDD $-$ VOH)                                                        | $x \text{ IOH} + \sum (\text{VOL } x \text{ IOL})$ |

| <ol> <li>Voltage spikes at the MCLR pin may cause latch-up. A series resistor of greater than<br/>to pull MCLR to VDD, rather than tying the pin directly to VDD.</li> </ol> | 1 k $\Omega$ should be used                        |

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

## 18.2 DC Characteristics: Power-Down and Supply Current PIC16F87/88 (Industrial, Extended) PIC16LF87/88 (Industrial) (Continued)

| PIC16LF87/88<br>(Industrial)          |                                       | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |      |       |        |            |                                                |  |  |  |

|---------------------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------|------------|------------------------------------------------|--|--|--|

| PIC16F87/88<br>(Industrial, Extended) |                                       |                                                                                                                                    |      |       |        |            |                                                |  |  |  |

| Param Device                          |                                       | Тур                                                                                                                                | Max  | Units |        | Conditions |                                                |  |  |  |

|                                       | Supply Current (IDD) <sup>(2,3)</sup> |                                                                                                                                    |      |       |        |            |                                                |  |  |  |

|                                       | PIC16LF87/88                          | 72                                                                                                                                 | 95   | μΑ    | -40°C  |            |                                                |  |  |  |

|                                       |                                       | 76                                                                                                                                 | 90   | μΑ    | +25°C  | VDD = 2.0V |                                                |  |  |  |

|                                       |                                       | 76                                                                                                                                 | 90   | μΑ    | +85°C  |            |                                                |  |  |  |

|                                       | PIC16LF87/88                          | 138                                                                                                                                | 175  | μΑ    | -40°C  |            | Fosc = 1 MHz<br>(RC Oscillator) <sup>(3)</sup> |  |  |  |

|                                       |                                       | 136                                                                                                                                | 170  | μA    | +25°C  | VDD = 3.0V |                                                |  |  |  |

|                                       |                                       | 136                                                                                                                                | 170  | μΑ    | +85°C  |            |                                                |  |  |  |

|                                       | All devices                           | 310                                                                                                                                | 380  | μA    | -40°C  |            |                                                |  |  |  |

|                                       |                                       | 290                                                                                                                                | 360  | μΑ    | +25°C  |            |                                                |  |  |  |

|                                       |                                       | 280                                                                                                                                | 360  | μA    | +85°C  | VDD = 3.0V |                                                |  |  |  |

|                                       | Extended devices                      | 330                                                                                                                                | 500  | μA    | 125°C  |            |                                                |  |  |  |

|                                       | PIC16LF87/88                          | 270                                                                                                                                | 335  | μΑ    | -40°C  | _          |                                                |  |  |  |

|                                       |                                       | 280                                                                                                                                | 330  | μA    | +25°C  | VDD = 2.0V |                                                |  |  |  |

|                                       |                                       | 285                                                                                                                                | 330  | μA    | +85°C  |            |                                                |  |  |  |

|                                       | PIC16LF87/88                          | 460                                                                                                                                | 610  | μA    | -40°C  |            |                                                |  |  |  |

|                                       |                                       | 450                                                                                                                                | 600  | μΑ    | +25°C  | VDD = 3.0V | Fosc = 4 MHz                                   |  |  |  |

|                                       |                                       | 450                                                                                                                                | 600  | μΑ    | +85°C  |            | (RC Oscillator) <sup>(3)</sup>                 |  |  |  |

|                                       | All devices                           | 900                                                                                                                                | 1060 | μΑ    | -40°C  |            |                                                |  |  |  |

|                                       |                                       | 890                                                                                                                                | 1050 | μΑ    | +25°C  | VDD = 5.0V |                                                |  |  |  |

|                                       |                                       | 890                                                                                                                                | 1050 | μΑ    | +85°C  |            |                                                |  |  |  |

|                                       | Extended devices                      | .920                                                                                                                               | 1.5  | mA    | +125°C |            |                                                |  |  |  |

Legend: Shading of rows is to assist in readability of the table.

**Note 1:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or VSs and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

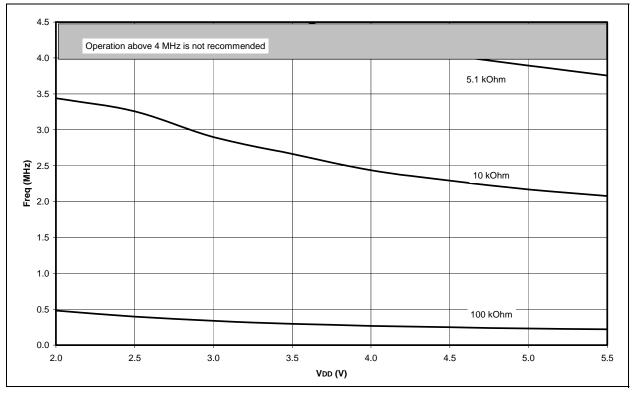

2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;

- MCLR = VDD; WDT enabled/disabled as specified.

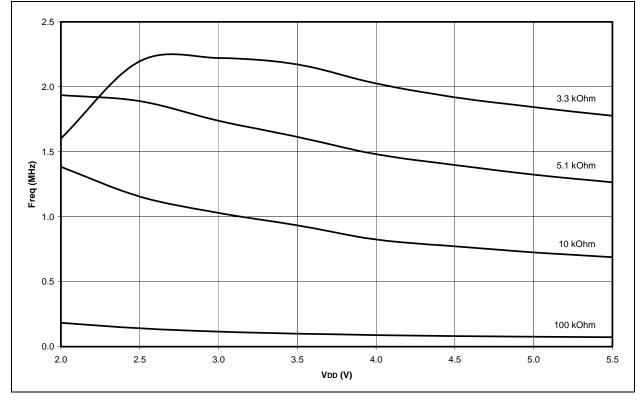

- 3: For RC oscillator configurations, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

## 18.2 DC Characteristics: Power-Down and Supply Current PIC16F87/88 (Industrial, Extended) PIC16LF87/88 (Industrial) (Continued)

| PIC16LF87/88<br>(Industrial)          |                                       | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |     |       |        |            |                                                                      |  |  |  |

|---------------------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|-------|--------|------------|----------------------------------------------------------------------|--|--|--|

| PIC16F87/88<br>(Industrial, Extended) |                                       |                                                                                                                                    |     |       |        |            |                                                                      |  |  |  |

| Param Device                          |                                       | Тур                                                                                                                                | Max | Units |        | Conditions |                                                                      |  |  |  |

|                                       | Supply Current (IDD) <sup>(2,3)</sup> |                                                                                                                                    |     |       |        |            |                                                                      |  |  |  |

|                                       | PIC16LF87/88                          | 8                                                                                                                                  | 20  | μA    | -40°C  |            |                                                                      |  |  |  |

|                                       |                                       | 7                                                                                                                                  | 15  | μA    | +25°C  | VDD = 2.0V | Fosc = 31.25 kHz<br>( <b>RC_RUN</b> mode,<br>Internal RC Oscillator) |  |  |  |

|                                       |                                       | 7                                                                                                                                  | 15  | μΑ    | +85°C  |            |                                                                      |  |  |  |

|                                       | PIC16LF87/88                          | 16                                                                                                                                 | 30  | μΑ    | -40°C  |            |                                                                      |  |  |  |

|                                       |                                       | 14                                                                                                                                 | 25  | μΑ    | +25°C  | VDD = 3.0V |                                                                      |  |  |  |

|                                       |                                       | 14                                                                                                                                 | 25  | μA    | +85°C  |            |                                                                      |  |  |  |

|                                       | All devices                           | 32                                                                                                                                 | 40  | μΑ    | -40°C  |            |                                                                      |  |  |  |

|                                       |                                       | 29                                                                                                                                 | 35  | μΑ    | +25°C  |            |                                                                      |  |  |  |

|                                       |                                       | 29                                                                                                                                 | 35  | μA    | +85°C  | VDD = 0.0V |                                                                      |  |  |  |

|                                       | Extended devices                      | 35                                                                                                                                 | 45  | μΑ    | +125°C |            |                                                                      |  |  |  |

|                                       | PIC16LF87/88                          | 132                                                                                                                                | 160 | μΑ    | -40°C  | _          |                                                                      |  |  |  |

|                                       |                                       | 126                                                                                                                                | 155 | μΑ    | +25°C  | VDD = 2.0V |                                                                      |  |  |  |

|                                       |                                       | 126                                                                                                                                | 155 | μA    | +85°C  |            |                                                                      |  |  |  |

|                                       | PIC16LF87/88                          | 260                                                                                                                                | 310 | μA    | -40°C  |            |                                                                      |  |  |  |

|                                       |                                       | 230                                                                                                                                | 300 | μΑ    | +25°C  | VDD = 3.0V | Fosc = 1 MHz<br>( <b>RC RUN</b> mode,                                |  |  |  |

|                                       |                                       | 230                                                                                                                                | 300 | μΑ    | +85°C  |            | Internal RC Oscillator)                                              |  |  |  |

|                                       | All devices                           | 560                                                                                                                                | 690 | μΑ    | -40°C  |            | ,                                                                    |  |  |  |

|                                       |                                       | 500                                                                                                                                | 650 | μΑ    | +25°C  | VDD = 5.0V |                                                                      |  |  |  |

|                                       |                                       | 500                                                                                                                                | 650 | μΑ    | +85°C  |            |                                                                      |  |  |  |