Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 16                                                                      |

| Program Memory Size        | 7KB (4K x 14)                                                           |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 256 x 8                                                                 |

| RAM Size                   | 368 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                               |

| Data Converters            | A/D 7x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                          |

| Supplier Device Package    | 20-SSOP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f88-e-ss |

#### 1.0 DEVICE OVERVIEW

This document contains device specific information for the operation of the PIC16F87/88 devices. Additional information may be found in the "PIC® Mid-Range MCU Family Reference Manual" (DS33023) which may be downloaded from the Microchip web site. This Reference Manual should be considered a complementary document to this data sheet and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules.

The PIC16F87/88 belongs to the Mid-Range family of the PIC® devices. Block diagrams of the devices are shown in Figure 1-1 and Figure 1-2. These devices contain features that are new to the PIC16 product line:

- Low-power modes: RC\_RUN allows the core and peripherals to be clocked from the INTRC, while SEC\_RUN allows the core and peripherals to be clocked from the low-power Timer1. Refer to Section 4.7 "Power-Managed Modes" for further details.

- Internal RC oscillator with eight selectable frequencies, including 31.25 kHz, 125 kHz, 250 kHz, 500 kHz, 1 MHz, 2 MHz, 4 MHz and 8 MHz. The INTRC can be configured as a primary or secondary clock source. Refer to Section 4.5 "Internal Oscillator Block" for further details.

- The Timer1 module current consumption has been greatly reduced from 20 μA (previous PIC16 devices) to 1.8 μA typical (32 kHz at 2V), which is ideal for real-time clock applications. Refer to Section 7.0 "Timer1 Module" for further details.

- Extended Watchdog Timer (WDT) that can have a programmable period from 1 ms to 268s. The WDT has its own 16-bit prescaler. Refer to Section 15.12 "Watchdog Timer (WDT)" for further details.

- Two-Speed Start-up: When the oscillator is configured for LP, XT or HS Oscillator mode, this feature will clock the device from the INTRC while the oscillator is warming up. This, in turn, will enable almost immediate code execution. Refer to Section 15.12.3 "Two-Speed Clock Start-up Mode" for further details.

- Fail-Safe Clock Monitor: This feature will allow the device to continue operation if the primary or secondary clock source fails by switching over to the INTRC.

- The A/D module has a new register for PIC16 devices named ANSEL. This register allows easier configuration of analog or digital I/O pins.

TABLE 1-1: AVAILABLE MEMORY IN PIC16F87/88 DEVICES

| Device      | Program | Data    | Data    |

|-------------|---------|---------|---------|

|             | Flash   | Memory  | EEPROM  |

| PIC16F87/88 | 4K x 14 | 368 x 8 | 256 x 8 |

There are 16 I/O pins that are user configurable on a pin-to-pin basis. Some pins are multiplexed with other device functions. These functions include:

- External Interrupt

- Change on PORTB Interrupt

- Timer0 Clock Input

- Low-Power Timer1 Clock/Oscillator

- · Capture/Compare/PWM

- 10-bit, 7-channel A/D Converter (PIC16F88 only)

- SPI/I<sup>2</sup>C™

- Two Analog Comparators

- AUSART

- MCLR (RA5) can be configured as an input

Table 1-2 details the pinout of the devices with descriptions and details for each pin.

bit 7

#### REGISTER 3-1: EECON1: EEPROM ACCESS CONTROL REGISTER 1 (ADDRESS 18Ch)

| R/W-x | U-0 | U-0 | R/W-x | R/W-x | R/W-0 | R/S-0 | R/S-0 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| EEPGD | _   | _   | FREE  | WRERR | WREN  | WR    | RD    |

| bit 7 |     |     |       |       |       |       | bit 0 |

EEPGD: Program/Data EEPROM Select bit

1 = Accesses program memory

0 = Accesses data memory

bit 6-5 **Unimplemented:** Read as '0'

bit 4 FREE: EEPROM Forced Row Erase bit

1 = Erase the program memory row addressed by EEADRH:EEADR on the next WR command

0 = Perform write only

bit 3 WRERR: EEPROM Error Flag bit

1 = A write operation is prematurely terminated (any  $\overline{MCLR}$  or any WDT Reset during normal

operation)

0 = The write operation completed

bit 2 WREN: EEPROM Write Enable bit

1 = Allows write cycles

0 = Inhibits write to the EEPROM

bit 1 WR: Write Control bit

1 =Initiates a write cycle. The bit is cleared by hardware once write is complete. The WR bit

can only be set (not cleared) in software.

0 = Write cycle to the EEPROM is complete

bit 0 RD: Read Control bit

${\tt 1}$  = Initiates an EEPROM read, RD is cleared in hardware. The RD bit can only be set (not

cleared) in software.

0 = Does not initiate an EEPROM read

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' S = Set only

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

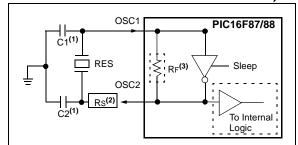

FIGURE 4-2: CERAMIC RESONATOR OPERATION (HS OR XT OSC CONFIGURATION)

Note 1: See Table 4-2 for typical values of C1 and C2.

- 2: A series resistor (Rs) may be required.

- 3: RF varies with the resonator chosen (typically between 2 M $\Omega$  to 10 M $\Omega$ ).

TABLE 4-2: CERAMIC RESONATORS (FOR DESIGN GUIDANCE ONLY)

| - /                            |                               |                         |                         |  |  |  |  |

|--------------------------------|-------------------------------|-------------------------|-------------------------|--|--|--|--|

| Typical Capacitor Values Used: |                               |                         |                         |  |  |  |  |

| Mode                           | Freq                          | OSC1                    | OSC2                    |  |  |  |  |

| XT                             | 455 kHz<br>2.0 MHz<br>4.0 MHz | 56 pF<br>47 pF<br>33 pF | 56 pF<br>47 pF<br>33 pF |  |  |  |  |

| HS                             | 8.0 MHz<br>16.0 MHz           | 27 pF<br>22 pF          | 27 pF<br>22 pF          |  |  |  |  |

#### Capacitor values are for design guidance only.

These capacitors were tested with the resonators listed below for basic start-up and operation. These values were not optimized.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes following this table for additional information.

Note:

When using resonators with frequencies above 3.5 MHz, the use of HS mode, rather than XT mode, is recommended. HS mode may be used at any VDD for which the controller is rated. If HS is selected, it is possible that the gain of the oscillator will overdrive the resonator. Therefore, a series resistor should be placed between the OSC2 pin and the resonator. As a good starting point, the recommended value of Rs is  $330\Omega$ .

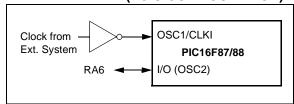

#### 4.3 External Clock Input

The ECIO Oscillator mode requires an external clock source to be connected to the OSC1 pin. There is no oscillator start-up time required after a Power-on Reset, or after an exit from Sleep mode.

In the ECIO Oscillator mode, the OSC2 pin becomes an additional general purpose I/O pin. The I/O pin becomes bit 6 of PORTA (RA6). Figure 4-3 shows the pin connections for the ECIO Oscillator mode.

FIGURE 4-3: EXTERNAL CLOCK INPUT OPERATION (ECIO CONFIGURATION)

#### 4.5.1 INTRC MODES

Using the internal oscillator as the clock source can eliminate the need for up to two external oscillator pins, after which it can be used for digital I/O. Two distinct configurations are available:

- In INTIO1 mode, the OSC2 pin outputs Fosc/4, while OSC1 functions as RA7 for digital input and output.

- In INTIO2 mode, OSC1 functions as RA7 and OSC2 functions as RA6, both for digital input and output.

#### 4.5.2 OSCTUNE REGISTER

The internal oscillator's output has been calibrated at the factory but can be adjusted in the application. This is done by writing to the OSCTUNE register (Register 4-1). The tuning sensitivity is constant throughout the tuning range. The OSCTUNE register has a tuning range of ±12.5%.

When the OSCTUNE register is modified, the INTOSC and INTRC frequencies will begin shifting to the new frequency. The INTRC clock will reach the new frequency within 8 clock cycles (approximately 8 \* 32  $\mu s = 256~\mu s$ ); the INTOSC clock will stabilize within 1 ms. Code execution continues during this shift. There is no indication that the shift has occurred. Operation of features that depend on the 31.25 kHz INTRC clock source frequency, such as the WDT, Fail-Safe Clock Monitor and peripherals, will also be affected by the change in frequency.

#### REGISTER 4-1: OSCTUNE: OSCILLATOR TUNING REGISTER (ADDRESS 90h)

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| _     | _   | TUN5  | TUN4  | TUN3  | TUN2  | TUN1  | TUN0  |

| hit 7 |     |       |       |       |       |       | hit 0 |

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 **TUN<5:0>:** Frequency Tuning bits

011111 = Maximum frequency

011110 =

•

•

000001 =

000000 = Center frequency. Oscillator module is running at the calibrated frequency.

111111 =

•

•

100000 = Minimum frequency

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

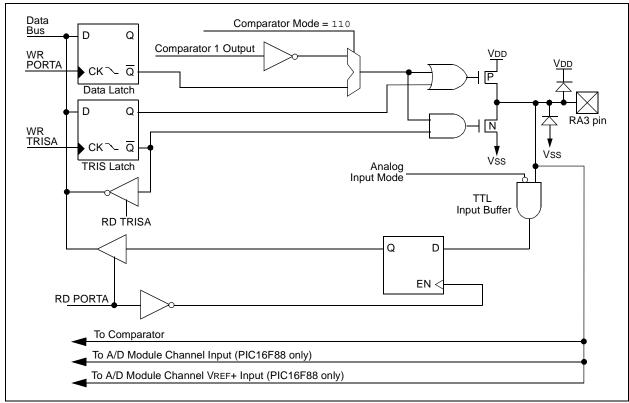

FIGURE 5-2: BLOCK DIAGRAM OF RA3/AN3/VREF+/C1OUT PIN

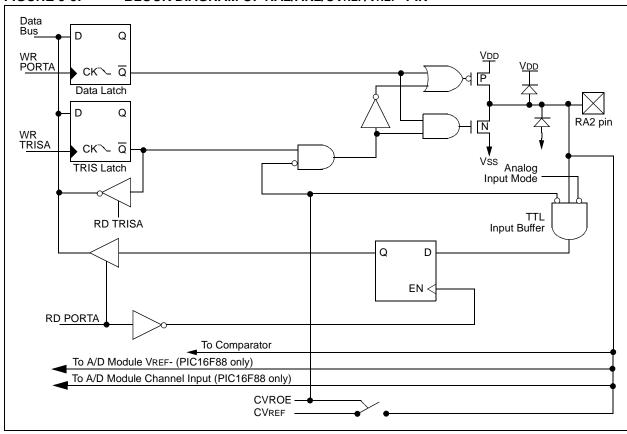

#### FIGURE 5-3: BLOCK DIAGRAM OF RA2/AN2/CVREF/VREF- PIN

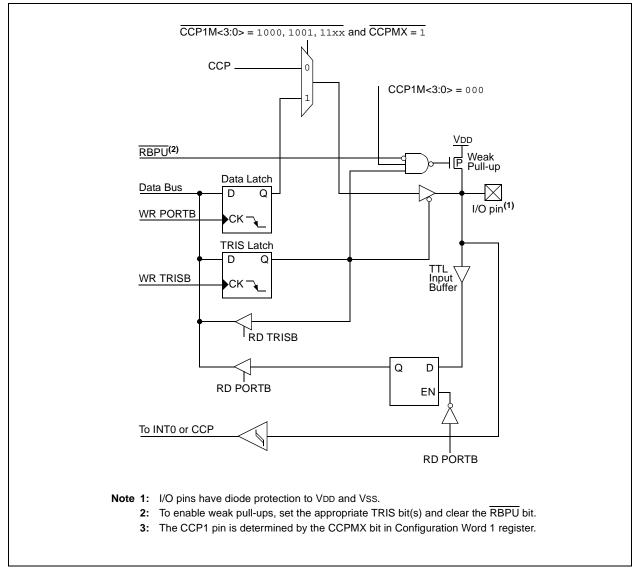

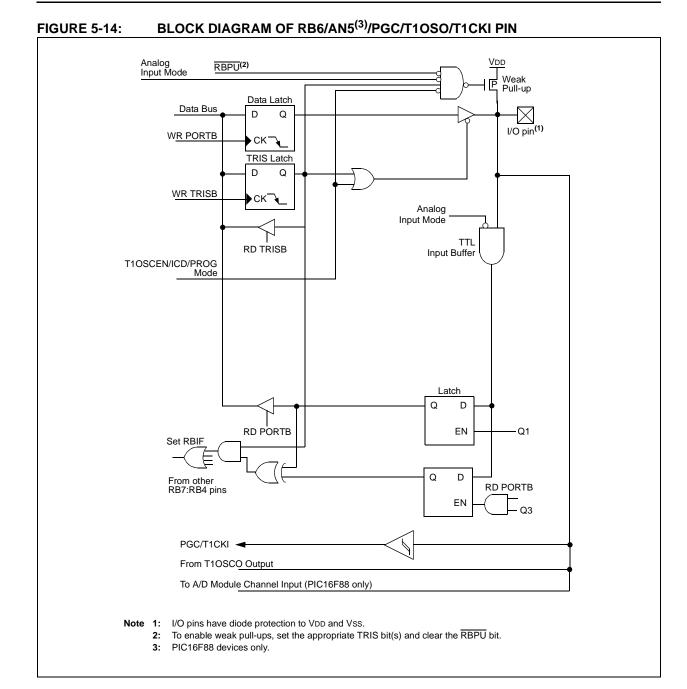

#### 5.2 PORTB and the TRISB Register

PORTB is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (OPTION\_REG<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Four of PORTB's pins, RB7:RB4, have an interrupt-onchange feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupton-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RB Port Change Interrupt with Flag bit RBIF (INTCON<0>).

This interrupt can wake the device from Sleep. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

RB0/INT is an external interrupt input pin and is configured using the INTEDG bit (OPTION\_REG<6>).

PORTB is multiplexed with several peripheral functions (see Table 5-3). PORTB pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTB pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modify-write instructions (BSF, BCF, XORWF) with TRISB as the destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

FIGURE 5-8: BLOCK DIAGRAM OF RB0/INT/CCP1<sup>(3)</sup> PIN

© 2002-2013 Microchip Technology Inc.

**NOTES:**

## 11.1 AUSART Baud Rate Generator (BRG)

The BRG supports both the Asynchronous and Synchronous modes of the AUSART. It is a dedicated 8-bit Baud Rate Generator. The SPBRG register controls the period of a free running 8-bit timer. In Asynchronous mode, bit BRGH (TXSTA<2>) also controls the baud rate. In Synchronous mode, bit BRGH is ignored. Table 11-1 shows the formula for computation of the baud rate for different AUSART modes which only apply in Master mode (internal clock).

Given the desired baud rate and Fosc, the nearest integer value for the SPBRG register can be calculated using the formula in Table 11-1. From this, the error in baud rate can be determined.

It may be advantageous to use the high baud rate (BRGH = 1) even for slower baud clocks. This is because the Fosc/(16(X + 1)) equation can reduce the baud rate error in some cases.

Writing a new value to the SPBRG register causes the BRG timer to be reset (or cleared). This ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

#### 11.1.1 AUSART AND INTRC OPERATION

The PIC16F87/88 has an 8 MHz INTRC that can be used as the system clock, thereby eliminating the need for external components to provide the clock source. When the INTRC provides the system clock, the AUSART module will also use the INTRC as its system clock. Table 11-1 shows some of the INTRC frequencies that can be used to generate the AUSART module's baud rate.

#### 11.1.2 LOW-POWER MODE OPERATION

The system clock is used to generate the desired baud rate; however, when a low-power mode is entered, the low-power clock source may be operating at a different frequency than in full power execution. In Sleep mode, no clocks are present. This may require the value in SPBRG to be adjusted.

#### 11.1.3 SAMPLING

The data on the RB2/SDO/RX/DT pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin.

TABLE 11-1: BAUD RATE FORMULA

| SYNC | BRGH = 0 (Low Speed)                        | BRGH = 1 (High Speed)        |

|------|---------------------------------------------|------------------------------|

| 0    | (Asynchronous) Baud Rate = Fosc/(64(X + 1)) | Baud Rate = Fosc/(16(X + 1)) |

| 1    | (Synchronous) Baud Rate = Fosc/(4(X + 1))   | N/A                          |

**Legend:** X = value in SPBRG (0 to 255)

TABLE 11-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Address | Name  | Bit 7    | Bit 6                        | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|-------|----------|------------------------------|-------|-------|-------|-------|-------|-------|-----------------------|---------------------------------|

| 98h     | TXSTA | CSRC     | TX9                          | TXEN  | SYNC  | _     | BRGH  | TRMT  | TX9D  | 0000 -010             | 0000 -010                       |

| 18h     | RCSTA | SPEN     | RX9                          | SREN  | CREN  | ADDEN | FERR  | OERR  | RX9D  | 0000 000x             | 0000 000x                       |

| 99h     | SPBRG | Baud Rat | Baud Rate Generator Register |       |       |       |       |       |       | 0000 0000             | 0000 0000                       |

**Legend:** x = unknown, -= unimplemented, read as '0'. Shaded cells are not used by the BRG.

VDD 16 Stages R R 8R -CVRR RA2/AN2/CVREF/VREF- pin(1) CVROE -CVR3 **CVREF** CVR2 Input to 16-to-1 Analog MUX CVR1 Comparator CVR0 Note 1: VREF is available on the PIC16F88 device only.

**FIGURE 14-1:** COMPARATOR VOLTAGE REFERENCE BLOCK DIAGRAM

**TABLE 14-1:** REGISTERS ASSOCIATED WITH COMPARATOR VOLTAGE REFERENCE

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR | Value on<br>all other<br>Resets |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------|---------------------------------|

| 9Dh     | CVRCON | CVREN | CVROE | CVRR  | _     | CVR3  | CVR2  | CVR1  | CVR0  | 000- 0000       | 000- 0000                       |

| 9Ch     | CMCON  | C2OUT | C1OUT | C2INV | C1INV | CIS   | CM2   | CM1   | CM0   | 0000 0111       | 0000 0111                       |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used with the comparator voltage reference.

TABLE 15-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

| Register   | Power-on Reset,<br>Brown-out Reset | MCLR Reset,<br>WDT Reset | Wake-up via WDT or<br>Interrupt |

|------------|------------------------------------|--------------------------|---------------------------------|

| TXREG      | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| RCREG      | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| ADRESH     | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| ADCON0     | 0000 00-0                          | 0000 00-0                | uuuu uu-u                       |

| OPTION_REG | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| TRISA      | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| TRISB      | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| PIE1       | -000 0000                          | -000 0000                | -uuu uuuu                       |

| PIE2       | 00-0                               | 00-0                     | uu-u                            |

| PCON       | 0q                                 | uu                       | uu                              |

| OSCCON     | -000 0000                          | -000 0000                | -uuu uuuu                       |

| OSCTUNE    | 00 0000                            | 00 0000                  | uu uuuu                         |

| PR2        | 1111 1111                          | 1111 1111                | 1111 1111                       |

| SSPADD     | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| SSPSTAT    | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| TXSTA      | 0000 -010                          | 0000 -010                | uuuu -u1u                       |

| SPBRG      | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| ANSEL      | -111 1111                          | -111 1111                | -111 1111                       |

| CMCON      | 0000 0111                          | 0000 0111                | uuuu u111                       |

| CVRCON     | 000- 0000                          | 000- 0000                | uuu- uuuu                       |

| WDTCON     | 0 1000                             | 0 1000                   | u uuuu                          |

| ADRESL     | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| ADCON1     | 0000                               | 0000                     | uuuu                            |

| EEDATA     | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| EEADR      | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| EEDATH     | xx xxxx                            | uu uuuu                  | uu uuuu                         |

| EEADRH     | xxx                                | uuu                      | uuu                             |

| EECON1     | xx x000                            | ux u000                  | uu uuuu                         |

| EECON2     |                                    |                          |                                 |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', <math>q = value depends on condition

Note 1: One or more bits in INTCON, PIR1 and PR2 will be affected (to cause wake-up).

<sup>2:</sup> When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

<sup>3:</sup> See Table 15-3 for Reset value for specific condition.

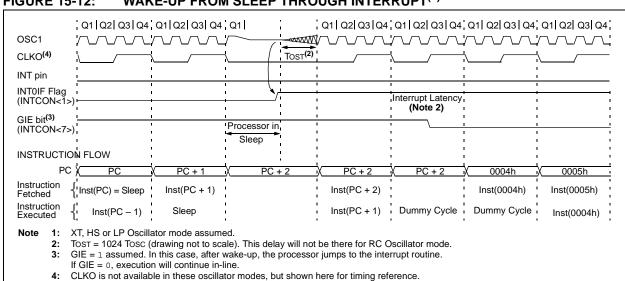

#### 15.13.1 WAKE-UP FROM SLEEP

The device can wake-up from Sleep through one of the following events:

- External Reset input on MCLR pin.

- 2. Watchdog Timer wake-up (if WDT was enabled).

- Interrupt from INT pin, RB port change or a peripheral interrupt.

External MCLR Reset will cause a device Reset. All other events are considered a continuation of program execution and cause a "wake-up". The TO and PD bits in the STATUS register can be used to determine the cause of the device Reset. The PD bit, which is set on power-up, is cleared when Sleep is invoked. The TO bit is cleared if a WDT time-out occurred and caused wake-up.

The following peripheral interrupts can wake the device from Sleep:

- TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 2. CCP Capture mode interrupt.

- 3. Special event trigger (Timer1 in Asynchronous mode using an external clock).

- 4. SSP (Start/Stop) bit detect interrupt.

- 5. SSP transmit or receive in Slave mode (SPI/I<sup>2</sup>C).

- 6. A/D conversion (when A/D clock source is RC).

- 7. EEPROM write operation completion.

- 8. Comparator output changes state.

- 9. AUSART RX or TX (Synchronous Slave mode).

Other peripherals cannot generate interrupts, since during Sleep, no on-chip clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding

interrupt enable bit must be set (enabled). Wake-up occurs regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

#### 15.13.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs before the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT prescaler and postscaler (if enabled) will not be cleared, the TO bit will not be set and the PD bit will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake-up from Sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT prescaler and postscaler (if enabled) will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overline{PD}$  bit. If the  $\overline{PD}$  bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

TABLE 16-2: PIC16F87/88 INSTRUCTION SET

| Mnemonic, |      | Description                  | Cycles  |        | 14-Bit | Opcode | )    | Status   | Notes |

|-----------|------|------------------------------|---------|--------|--------|--------|------|----------|-------|

| Operar    | nds  | Description                  |         | MSb    |        |        | LSb  | Affected | Notes |

|           |      | BYTE-ORIENTED FILE REGIS     | TER OPE | RATIO  | NS     |        |      |          |       |

| ADDWF     | f, d | Add W and f                  | 1       | 00     | 0111   | dfff   | ffff | C,DC,Z   | 1,2   |

| ANDWF     | f, d | AND W with f                 | 1       | 00     | 0101   | dfff   | ffff | Z        | 1,2   |

| CLRF      | f    | Clear f                      | 1       | 00     | 0001   | lfff   | ffff | Z        | 2     |

| CLRW      | -    | Clear W                      | 1       | 00     | 0001   | 0xxx   | xxxx | Z        |       |

| COMF      | f, d | Complement f                 | 1       | 00     | 1001   | dfff   | ffff | Z        | 1,2   |

| DECF      | f, d | Decrement f                  | 1       | 00     | 0011   | dfff   | ffff | Z        | 1,2   |

| DECFSZ    | f, d | Decrement f, Skip if 0       | 1(2)    | 00     | 1011   | dfff   | ffff |          | 1,2,3 |

| INCF      | f, d | Increment f                  | 1       | 00     | 1010   | dfff   | ffff | Z        | 1,2   |

| INCFSZ    | f, d | Increment f, Skip if 0       | 1(2)    | 00     | 1111   | dfff   | ffff |          | 1,2,3 |

| IORWF     | f, d | Inclusive OR W with f        | 1       | 00     | 0100   | dfff   | ffff | Z        | 1,2   |

| MOVF      | f, d | Move f                       | 1       | 00     | 1000   | dfff   | ffff | Z        | 1,2   |

| MOVWF     | f    | Move W to f                  | 1       | 00     | 0000   | lfff   | ffff |          |       |

| NOP       | -    | No Operation                 | 1       | 00     | 0000   | 0xx0   | 0000 |          |       |

| RLF       | f, d | Rotate Left f through Carry  | 1       | 00     | 1101   | dfff   | ffff | С        | 1,2   |

| RRF       | f, d | Rotate Right f through Carry | 1       | 00     | 1100   | dfff   | ffff | С        | 1,2   |

| SUBWF     | f, d | Subtract W from f            | 1       | 00     | 0010   | dfff   | ffff | C,DC,Z   | 1,2   |

| SWAPF     | f, d | Swap nibbles in f            | 1       | 00     | 1110   | dfff   | ffff |          | 1,2   |

| XORWF     | f, d | Exclusive OR W with f        | 1       | 00     | 0110   | dfff   | ffff | Z        | 1,2   |

|           |      | BIT-ORIENTED FILE REGIST     | ER OPER | RATION | IS     |        |      |          |       |

| BCF       | f, b | Bit Clear f                  | 1       | 01     | 00bb   | bfff   | ffff |          | 1,2   |

| BSF       | f, b | Bit Set f                    | 1       | 01     | 01bb   | bfff   | ffff |          | 1,2   |

| BTFSC     | f, b | Bit Test f, Skip if Clear    | 1 (2)   | 01     | 10bb   | bfff   | ffff |          | 3     |

| BTFSS     | f, b | Bit Test f, Skip if Set      | 1 (2)   | 01     | 11bb   | bfff   | ffff |          | 3     |

|           |      | LITERAL AND CONTROL          | OPERAT  | IONS   |        |        |      |          |       |

| ADDLW     | k    | Add literal and W            | 1       | 11     | 111x   | kkkk   | kkkk | C,DC,Z   |       |

| ANDLW     | k    | AND literal with W           | 1       | 11     | 1001   | kkkk   | kkkk | Z        |       |

| CALL      | k    | Call subroutine              | 2       | 10     | 0kkk   | kkkk   | kkkk |          |       |

| CLRWDT    | -    | Clear Watchdog Timer         | 1       | 00     | 0000   | 0110   | 0100 | TO,PD    |       |

| GOTO      | k    | Go to address                | 2       | 10     | 1kkk   | kkkk   | kkkk |          |       |

| IORLW     | k    | Inclusive OR literal with W  | 1       | 11     | 1000   | kkkk   | kkkk | Z        |       |

| MOVLW     | k    | Move literal to W            | 1       | 11     | 00xx   | kkkk   | kkkk |          |       |

| RETFIE    | -    | Return from interrupt        | 2       | 00     | 0000   | 0000   | 1001 |          |       |

| RETLW     | k    | Return with literal in W     | 2       | 11     | 01xx   | kkkk   | kkkk |          |       |

| RETURN    | -    | Return from Subroutine       | 2       | 00     | 0000   | 0000   | 1000 | <u> </u> |       |

| SLEEP     | -    | Go into Standby mode         | 1       | 00     | 0000   | 0110   | 0011 | TO,PD    |       |

| SUBLW     | k    | Subtract W from literal      | 1       | 11     | 110x   | kkkk   | kkkk | C,DC,Z   |       |

| XORLW     | k    | Exclusive OR literal with W  | 1       | 11     | 1010   | kkkk   | kkkk | Z        |       |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

**Note:** Additional information on the mid-range instruction set is available in the "PIC® Mid-Range MCU Family Reference Manual" (DS33023).

<sup>2:</sup> If this instruction is executed on the TMR0 register (and where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 module.

<sup>3:</sup> If the Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                               |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSS f,b                                                                                                                                                   |

| Operands:        | $0 \le f \le 127$<br>$0 \le b < 7$                                                                                                                                    |

| Operation:       | skip if $(f < b >) = 1$                                                                                                                                               |

| Status Affected: | None                                                                                                                                                                  |

| Description:     | If bit 'b' in register 'f' = 0, the next instruction is executed. If bit 'b' = 1, then the next instruction is discarded and a NOP is executed instead, making this a |

2 Tcy instruction.

| CLRF             | Clear f                                                        |

|------------------|----------------------------------------------------------------|

| Syntax:          | [label] CLRF f                                                 |

| Operands:        | $0 \leq f \leq 127$                                            |

| Operation:       | $00h \rightarrow (f),$ $1 \rightarrow Z$                       |

| Status Affected: | Z                                                              |

| Description:     | The contents of register 'f' are cleared and the Z bit is set. |

|                  |                                                                |

| BTFSC            | Bit Test, Skip if Clear                                                                                                                                                                                |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                    |

| Operands:        | $0 \le f \le 127$ $0 \le b \le 7$                                                                                                                                                                      |

| Operation:       | skip if $(f < b >) = 0$                                                                                                                                                                                |

| Status Affected: | None                                                                                                                                                                                                   |

| Description:     | If bit 'b' in register 'f' = 1, the next instruction is executed.  If bit 'b', in register 'f', = 0, the next instruction is discarded and a NOP is executed instead, making this a 2 Tcy instruction. |

| CLRW             | Clear W                                     |

|------------------|---------------------------------------------|

| Syntax:          | [ label ] CLRW                              |

| Operands:        | None                                        |

| Operation:       | $00h \rightarrow (W),$ $1 \rightarrow Z$    |

| Status Affected: | Z                                           |

| Description:     | W register is cleared. Zero bit (Z) is set. |

|                  |                                             |

| CALL             | Call Subroutine                                                                                                                                                                                                             |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] CALL k                                                                                                                                                                                                            |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                        |

| Operation:       | (PC) + 1 → TOS,<br>k → PC<10:0>,<br>(PCLATH<4:3>) → PC<12:11>                                                                                                                                                               |

| Status Affected: | None                                                                                                                                                                                                                        |

| Description:     | Call subroutine. First, return address (PC + 1) is pushed onto the stack. The eleven-bit immediate address is loaded into PC bits <10:0>. The upper bits of the PC are loaded from PCLATH. CALL is a two-cycle instruction. |

| CLRWDT                      | Clear Watchdog Timer                                                                                                  |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Syntax:                     | [ label ] CLRWDT                                                                                                      |

| Operands:                   | None                                                                                                                  |

| Operation: Status Affected: | 00h → WDT,<br>0 → WDT prescaler,<br>1 → $\overline{TO}$ ,<br>1 → $\overline{PD}$<br>$\overline{TO}$ , $\overline{PD}$ |

| Description:                | CLRWDT instruction resets the Watchdog Timer. It also resets the prescaler of the WDT. Status bits TO and PD are set. |

# 18.2 DC Characteristics: Power-Down and Supply Current PIC16F87/88 (Industrial, Extended) PIC16LF87/88 (Industrial)

| PIC16LF8     |                          |                    | rd Oper | _          | •                                                                                                        | s otherwise state<br>\( \leq +85°C \) for indus | • |  |

|--------------|--------------------------|--------------------|---------|------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------|---|--|

| PIC16F87     |                          | rd Oper<br>ng temp | _       | -40°C ≤ TA | s otherwise states $\Delta \le +85^{\circ}\text{C}$ for indus $\Delta \le +125^{\circ}\text{C}$ for exte | trial                                           |   |  |

| Param<br>No. | Device                   | Тур                | Max     | Units      | Conditions                                                                                               |                                                 |   |  |

|              | Power-Down Current (IPD) | (1)                |         |            |                                                                                                          |                                                 |   |  |

|              | PIC16LF87/88             | 0.1                | 0.4     | μА         | -40°C                                                                                                    |                                                 |   |  |

|              |                          | 0.1                | 0.4     | μΑ         | +25°C                                                                                                    | VDD = 2.0V                                      |   |  |

|              |                          | 0.4                | 1.5     | μΑ         | +85°C                                                                                                    |                                                 |   |  |

|              | PIC16LF87/88             | 0.3                | 0.5     | μΑ         | -40°C                                                                                                    |                                                 |   |  |

|              |                          | 0.3                | 0.5     | μА         | +25°C                                                                                                    | VDD = 3.0V                                      |   |  |

|              |                          | 0.7                | 1.7     | μΑ         | +85°C                                                                                                    |                                                 |   |  |

|              | All devices              | 0.6                | 1.0     | μА         | -40°C                                                                                                    |                                                 |   |  |

|              |                          | 0.6                | 1.0     | μΑ         | +25°C                                                                                                    | VDD = 5.0V                                      |   |  |

|              |                          | 1.2                | 5.0     | μΑ         | +85°C                                                                                                    |                                                 |   |  |

|              | Extended devices         | 6                  | 28      | μΑ         | +125°C                                                                                                   |                                                 |   |  |

**Legend:** Shading of rows is to assist in readability of the table.

- Note 1: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or Vss and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

- 2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;

MCLR = VDD; WDT enabled/disabled as specified.

3: For RC oscillator configurations, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

# 18.2 DC Characteristics: Power-Down and Supply Current PIC16F87/88 (Industrial, Extended) PIC16LF87/88 (Industrial) (Continued)

| PIC16LF      |                           |                                                                                                                                                                                                                                     | rd Oper | •     | •          | s otherwise state | •                                |  |  |

|--------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------|------------|-------------------|----------------------------------|--|--|

| PIC16F8      |                           | Standard Operating Conditions (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for extended |         |       |            |                   |                                  |  |  |

| Param<br>No. | Device                    | Тур                                                                                                                                                                                                                                 | Max     | Units | Conditions |                   |                                  |  |  |

|              | Supply Current (IDD)(2,3) |                                                                                                                                                                                                                                     |         |       |            |                   |                                  |  |  |

|              | All devices               | 1.8                                                                                                                                                                                                                                 | 2.3     | mA    | -40°C      |                   |                                  |  |  |

|              |                           | 1.6                                                                                                                                                                                                                                 | 2.2     | mA    | +25°C      | VDD = 4.0V        |                                  |  |  |

|              |                           | 1.3                                                                                                                                                                                                                                 | 2.2     | mA    | +85°C      |                   | 5 00 MH-                         |  |  |

|              | All devices               | 3.0                                                                                                                                                                                                                                 | 4.2     | mA    | -40°C      |                   | Fosc = 20 MHz<br>(HS Oscillator) |  |  |

|              |                           | 2.5                                                                                                                                                                                                                                 | 4.0     | mA    | +25°C      | VDD = 5.0V        | (i.ie estimator)                 |  |  |

|              |                           | 2.5                                                                                                                                                                                                                                 | 4.0     | mA    | +85°C      | VUU ≅ 5.0V        |                                  |  |  |

|              | Extended devices          | 3.0                                                                                                                                                                                                                                 | 5.0     | mA    | +85°C      |                   |                                  |  |  |

**Legend:** Shading of rows is to assist in readability of the table.

- Note 1: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or Vss and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

- 2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;

MCLR = VDD; WDT enabled/disabled as specified.

3: For RC oscillator configurations, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

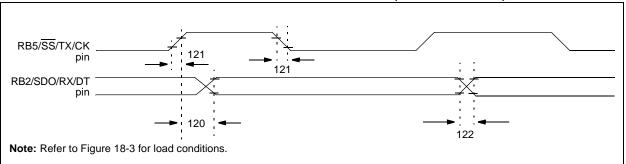

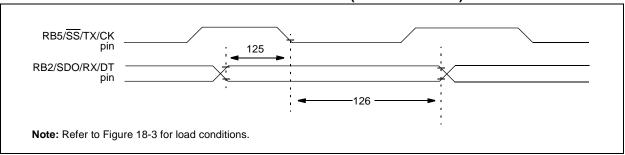

#### FIGURE 18-16: AUSART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

TABLE 18-11: AUSART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Param<br>No. | Sym                                   | Characte                     | Min                   | Тур† | Max | Units | Conditions |  |

|--------------|---------------------------------------|------------------------------|-----------------------|------|-----|-------|------------|--|

| 120          | TckH2dtV                              | SYNC XMIT (MASTER & SLAVE)   | PIC16 <b>F</b> 87/88  | _    | _   | 80    | ns         |  |

|              |                                       | Clock High to Data Out Valid | PIC16 <b>LF</b> 87/88 | _    | _   | 100   | ns         |  |

| 121          | Tckrf                                 | Clock Out Rise Time and Fall | PIC16 <b>F</b> 87/88  | _    | _   | 45    | ns         |  |

| Time (N      | Time (Master mode)                    | PIC16 <b>LF</b> 87/88        | _                     | _    | 50  | ns    |            |  |

| 122          | 122 Tdtrf Data Out Rise Time and Fall | PIC16 <b>F</b> 87/88         | _                     | _    | 45  | ns    |            |  |

| Time         | PIC16 <b>LF</b> 87/88                 | _                            | _                     | 50   | ns  |       |            |  |

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**TABLE 18-12: AUSART SYNCHRONOUS RECEIVE REQUIREMENTS**

| Param<br>No. | Sym      | Characteristic                         | Min | Тур† | Max | Units | Conditions |

|--------------|----------|----------------------------------------|-----|------|-----|-------|------------|

| 125          | TdtV2ckL | SYNC RCV (MASTER & SLAVE)              | 4.5 |      |     |       |            |

|              |          | Data Setup before CK ↓ (DT setup time) | 15  | _    | _   | ns    |            |

| 126          | TckL2dtl | Data Hold after CK ↓ (DT hold time)    | 15  | _    |     | ns    |            |

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

| RB5/SS/TX/CK Pin                             | 66      | Reading Flash Program Memory                 | 32    |

|----------------------------------------------|---------|----------------------------------------------|-------|

| RB6/AN5/PGC/T1OSO/T1CKI Pin                  |         | Saving STATUS, W and PCLATH Registers in RAM |       |

| RB7/AN6/PGD/T10SI Pin                        | _       | 142                                          |       |

| Simplified PWM                               |         | Writing a 16-Bit Free Running Timer          | 76    |

| SSP in I <sup>2</sup> C Mode                 |         | Writing to Data EEPROM                       |       |

| SSP in SPI Mode                              |         | Writing to Flash Program Memory              |       |

|                                              |         |                                              |       |

| System Clock                                 |         | Code Protection                              |       |

| Timer0/WDT Prescaler                         |         | Comparator Module                            |       |

| Timer1                                       |         | Analog Input Connection Considerations       |       |

| Timer2                                       |         | Associated Registers                         |       |

| Watchdog Timer (WDT)                         | 143     | Configuration                                |       |

| BOR. See Brown-out Reset.                    |         | Effects of a Reset                           |       |

| BRGH Bit                                     |         | External Reference Signal                    |       |

| Brown-out Reset (BOR)131, 134, 1             | •       | Internal Reference Signal                    |       |

| BOR Status (BOR Bit)                         | 26      | Interrupts                                   | . 126 |

| C                                            |         | Operation                                    |       |

| C                                            |         | Operation During Sleep                       | . 127 |

| C Compilers                                  |         | Outputs                                      | . 125 |

| MPLAB C18                                    | 160     | Reference                                    | . 125 |

| Capture/Compare/PWM (CCP)                    | 83      | Response Time                                | . 125 |

| Capture Mode                                 | 84      | Comparator Specifications                    | . 177 |

| CCP Pin Configuration                        |         | Comparator Voltage Reference                 |       |

| Software Interrupt                           |         | Associated Registers                         |       |

| Timer1 Mode Selection                        |         | Computed GOTO                                |       |

| Capture, Compare and Timer1 Associated Regis |         | Configuration Bits                           |       |

| CCP Prescaler                                |         | Crystal and Ceramic Resonators               |       |

| CCP Timer Resources                          |         | Customer Change Notification Service         |       |

| CCP1IF                                       |         | Customer Notification Service                |       |

| CCPR1                                        |         |                                              |       |

| CCPR1H:CCPR1L                                | -       | Customer Support                             |       |

|                                              |         | CVRCON Register                              | 17    |

| Compare Mode                                 |         | D                                            |       |

| CCP Pin Configuration                        |         | _                                            | 00    |

| Software Interrupt Mode                      |         | Data EEPROM Memory                           |       |

| Special Event Trigger                        |         | Associated Registers                         |       |

| Special Event Trigger Output of CCP1         |         | EEADR Register                               |       |

| Timer1 Mode Selection                        |         | EEADRH Register                              |       |

| PWM and Timer2 Associated Registers          |         | EECON1 Register                              |       |

| PWM Mode                                     |         | EECON2 Register                              |       |

| Example Frequencies/Resolutions              |         | EEDATA Register                              |       |

| Operation Setup                              |         | EEDATH Register                              |       |

| CCP1CON Register                             |         | Operation During Code-Protect                |       |

| CCP1M0 Bit                                   | 83      | Protection Against Spurious Writes           | 36    |

| CCP1M1 Bit                                   | 83      | Reading                                      | 31    |

| CCP1M2 Bit                                   | 83      | Write Complete Flag (EEIF Bit)               | 29    |

| CCP1M3 Bit                                   | 83      | Writing                                      | 31    |

| CCP1X Bit                                    | 83      | Data Memory                                  |       |

| CCP1Y Bit                                    | 83      | Special Function Registers                   | 16    |

| CCPR1H Register                              | 16, 83  | DC and AC Characteristics                    |       |

| CCPR1L Register                              |         | Graphs and Tables                            | . 193 |

| Clock Sources                                |         | DC Characteristics                           |       |

| Selection Using OSCCON Register              |         | Internal RC Accuracy                         | 174   |

| Clock Switching                              |         | PIC16F87/88, PIC16LF87/88                    |       |

| Transition and the Watchdog Timer            |         | Power-Down and Supply Current                |       |

| Transition Sequence                          |         | Supply Voltage                               |       |

| CMCON Register                               |         | Development Support                          |       |

|                                              | 17      | Device Differences                           |       |

| Code Examples                                | 27      |                                              |       |

| Call of a Subroutine in Page 1 from Page 0   |         | Device Overview                              |       |

| Changing Between Capture Prescalers          |         | Direct Addressing                            | 28    |

| Changing Prescaler Assignment From WDT to T  | ımeru . |                                              |       |

| 71                                           |         |                                              |       |

| Erasing a Flash Program Memory Row           |         |                                              |       |

| Implementing a Real-Time Clock Using a Time  |         |                                              |       |

| rupt Service                                 | 79      |                                              |       |

| Indirect Addressing                          |         |                                              |       |

| Initializing PORTA                           | 53      |                                              |       |

| Reading a 16-Bit Free Running Timer          | 76      |                                              |       |

| Reading Data EEPROM                          | 31      |                                              |       |