Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 16                                                                      |

| Program Memory Size        | 7KB (4K x 14)                                                           |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 256 x 8                                                                 |

| RAM Size                   | 368 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                               |

| Data Converters            | A/D 7x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 28-VQFN Exposed Pad                                                     |

| Supplier Device Package    | 28-QFN (6x6)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f88-i-ml |

|                                | File<br>Address | Д                                                    | File<br>ddress | <i>P</i>                                   | File<br>Address |                                            | File<br>Addre |

|--------------------------------|-----------------|------------------------------------------------------|----------------|--------------------------------------------|-----------------|--------------------------------------------|---------------|

| Indirect addr.(*)              | 00h             | Indirect addr.(*)                                    | 80h            | Indirect addr.(*)                          | 100h            | Indirect addr.(*)                          | 180           |

| TMR0                           | 01h             | OPTION_REG                                           | 81h            | TMR0                                       | 101h            | OPTION_REG                                 | 181           |

| PCL                            | 02h             | PCL                                                  | 82h            | PCL                                        | 102h            | PCL                                        | 182           |

| STATUS                         | 03h             | STATUS                                               | 83h            | STATUS                                     | 103h            | STATUS                                     | 183           |

| FSR                            | 04h             | FSR                                                  | 84h            | FSR                                        | 104h            | FSR                                        | 184           |

| PORTA                          | 05h             | TRISA                                                | 85h            | WDTCON                                     | 105h            |                                            | 185           |

| PORTB                          | 06h             | TRISB                                                | 86h            | PORTB                                      | 106h            | TRISB                                      | 186           |

|                                | 07h             |                                                      | 87h            |                                            | 107h            |                                            | 187           |

|                                | 08h             |                                                      | 88h            |                                            | 108h            |                                            | 188           |

|                                | 09h             |                                                      | 89h            |                                            | 109h            |                                            | 189           |

| PCLATH                         | 0Ah             | PCLATH                                               | 8Ah            | PCLATH                                     | 10Ah            | PCLATH                                     | 18A           |

| INTCON                         | 0Bh             | INTCON                                               | 8Bh            | INTCON                                     | 10Bh            | INTCON                                     | 18E           |

| PIR1                           | 0Ch             | PIE1                                                 | 8Ch            | EEDATA                                     | 10Ch            | EECON1                                     | 180           |

| PIR2                           | 0Dh             | PIE2                                                 | 8Dh            | EEADR                                      | 10Dh            | EECON2                                     | 180           |

| TMR1L                          | 0Eh             | PCON                                                 | 8Eh            | EEDATH                                     | 10Eh            | Reserved <sup>(1)</sup>                    | 18E           |

| TMR1H                          | 0Fh             | OSCCON                                               | 8Fh            | EEADRH                                     | 10Fh            | Reserved <sup>(1)</sup>                    | 18F           |

| T1CON                          | 10h             | OSCTUNE                                              | 90h            |                                            | 110h            |                                            | 190           |

| TMR2                           | 11h             |                                                      | 91h            |                                            |                 |                                            |               |

| T2CON                          | 12h             | PR2                                                  | 92h            |                                            |                 |                                            |               |

| SSPBUF                         | 13h             | SSPADD                                               | 93h            |                                            |                 |                                            |               |

| SSPCON                         | 14h             | SSPSTAT                                              | 94h            |                                            |                 |                                            |               |

| CCPR1L                         | 15h             |                                                      | 95h            |                                            |                 |                                            |               |

| CCPR1H                         | 16h             |                                                      | 96h            | General                                    |                 | General                                    |               |

| CCP1CON                        | 17h             |                                                      | 97h            | Purpose                                    |                 | Purpose                                    |               |

| RCSTA                          | 18h             | TXSTA                                                | 98h            | Register                                   |                 | Register                                   |               |

| TXREG                          | 19h             | SPBRG                                                | 99h            | 16 Bytes                                   |                 | 16 Bytes                                   |               |

| RCREG                          | 1Ah             |                                                      | 9Ah            |                                            |                 |                                            |               |

|                                | 1Bh             | ANSEL                                                | 9Bh            |                                            |                 |                                            |               |

|                                | 1Ch             | CMCON                                                | 9Ch            |                                            |                 |                                            |               |

|                                | 1Dh             | CVRCON                                               | 9Dh            |                                            |                 |                                            |               |

| ADRESH                         | 1Eh             | ADRESL                                               | 9Eh            |                                            |                 |                                            |               |

| ADCON0                         | 1Fh             | ADCON1                                               | 9Fh            |                                            | 11Fh            |                                            | 19F           |

| General<br>Purpose<br>Register | 20h             | General<br>Purpose<br>Register<br>80 Bytes           | A0h<br>EFh     | General<br>Purpose<br>Register<br>80 Bytes | 120h            | General<br>Purpose<br>Register<br>80 Bytes | 1A0           |

| 96 Bytes                       |                 |                                                      | F0h            |                                            | 170h            |                                            | 1F0           |

|                                |                 | accesses<br>70h-7Fh                                  |                | accesses<br>70h-7Fh                        |                 | accesses<br>70h-7Fh                        |               |

|                                | 7Fh             |                                                      | FFh            | Davids C                                   | 17Fh            | Danis C                                    | 1FF           |

| Bank 0                         |                 | Bank 1                                               |                | Bank 2                                     |                 | Bank 3                                     |               |

| * Not a                        | physical r      | I data memory loc<br>register.<br>reserved, maintair |                |                                            |                 |                                            |               |

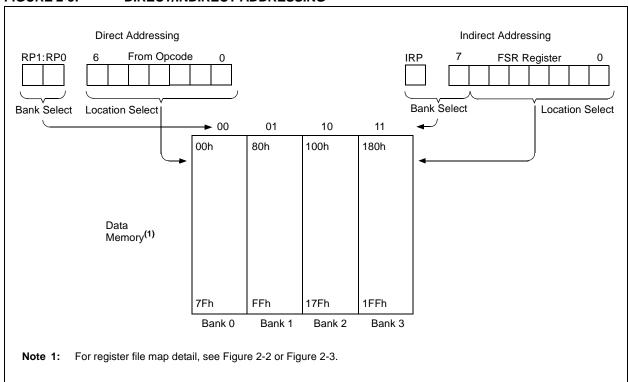

### 2.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses the register pointed to by the File Select Register, FSR. Reading the INDF register itself, indirectly (FSR = 0) will read 00h. Writing to the INDF register indirectly results in a no operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 2-5.

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-2.

#### **EXAMPLE 2-2:** INDIRECT ADDRESSING

```

MOVIW 0x20

;initialize pointer

MOVWF FSR

;to RAM

INDF

NEXT

CLRF

;clear INDF register

INCF

FSR, F ;inc pointer

BTFSS FSR, 4 ;all done?

GOTO

NEXT

;no clear next

CONTINUE

;yes continue

```

#### FIGURE 2-5: DIRECT/INDIRECT ADDRESSING

### 4.0 OSCILLATOR CONFIGURATIONS

#### 4.1 Oscillator Types

The PIC16F87/88 can be operated in eight different oscillator modes. The user can program three configuration bits (FOSC2:FOSC0) to select one of these eight modes (modes 5-8 are new PIC16 oscillator configurations):

| 1. | LP     | Low-Power Crystal                                            |

|----|--------|--------------------------------------------------------------|

| 2. | XT     | Crystal/Resonator                                            |

| 3. | HS     | High-Speed Crystal/Resonator                                 |

| 4. | RC     | External Resistor/Capacitor with Fosc/4 output on RA6        |

| 5. | RCIO   | External Resistor/Capacitor with I/O on RA6                  |

| 6. | INTIO1 | Internal Oscillator with Fosc/4 output on RA6 and I/O on RA7 |

| 7. | INTIO2 | Internal Oscillator with I/O on RA6 and RA7                  |

| 8. | ECIO   | External Clock with I/O on RA6                               |

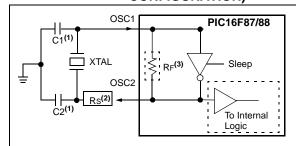

### 4.2 Crystal Oscillator/Ceramic Resonators

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1/CLKI and OSC2/CLKO pins to establish oscillation (see Figure 4-1 and Figure 4-2). The PIC16F87/88 oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturer's specifications.

FIGURE 4-1: CRYSTAL OPERATION

(HS, XT, OR LP

OSCILLATOR

CONFIGURATION)

Note1: See Table 4-1 for typical values of C1 and C2.

- 2: A series resistor (Rs) may be required for AT strip cut crystals.

- 3: RF varies with the crystal chosen (typically between 2 M $\Omega$  to 10 M $\Omega).$

TABLE 4-1: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR (FOR DESIGN GUIDANCE ONLY)

| Osc Type | Crystal<br>Freq |       | al Capacitor Values<br>Tested: |  |  |

|----------|-----------------|-------|--------------------------------|--|--|

|          | rreq            | C1    | C2                             |  |  |

| LP       | 32 kHz          | 33 pF | 33 pF                          |  |  |

| XT       | 200 kHz         | 56 pF | 56 pF                          |  |  |

|          | 1 MHz           | 15 pF | 15 pF                          |  |  |

|          | 4 MHz           | 15 pF | 15 pF                          |  |  |

| HS       | 4 MHz           | 15 pF | 15 pF                          |  |  |

|          | 8 MHz           | 15 pF | 15 pF                          |  |  |

|          | 20 MHz          | 15 pF | 15 pF                          |  |  |

#### Capacitor values are for design guidance only.

These capacitors were tested with the crystals listed below for basic start-up and operation. These values were not optimized.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes following this table for additional information.

- **Note 1:** Higher capacitance increases the stability of oscillator but also increases the start-up time.

- 2: Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values of external components.

- **3:** Rs may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specification.

- **4:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

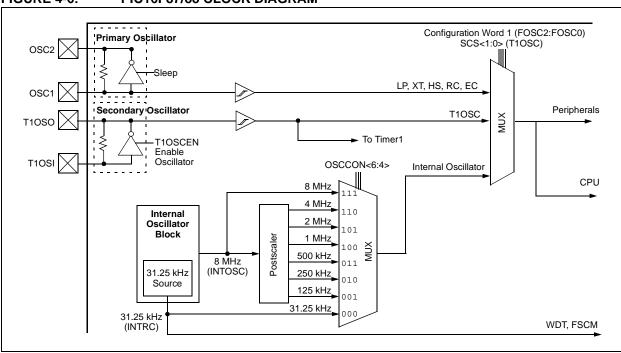

### 4.6 Clock Sources and Oscillator Switching

The PIC16F87/88 devices include a feature that allows the system clock source to be switched from the main oscillator to an alternate low-frequency clock source. PIC16F87/88 devices offer three alternate clock sources. When enabled, these give additional options for switching to the various power-managed operating modes.

Essentially, there are three clock sources for these devices:

- · Primary oscillators

- · Secondary oscillators

- Internal oscillator block (INTRC)

The **primary oscillators** include the External Crystal and Resonator modes, the External RC modes, the External Clock mode and the internal oscillator block. The particular mode is defined on POR by the contents of Configuration Word 1. The details of these modes are covered earlier in this chapter.

The **secondary oscillators** are those external sources not connected to the OSC1 or OSC2 pins. These sources may continue to operate even after the controller is placed in a power-managed mode.

PIC16F87/88 devices offer the Timer1 oscillator as a secondary oscillator. This oscillator continues to run when a SLEEP instruction is executed and is often the time base for functions such as a real-time clock.

Most often, a 32.768 kHz watch crystal is connected between the RB6/T1OSO and RB7/T1OSI pins. Like the LP mode oscillator circuit, loading capacitors are also connected from each pin to ground. The Timer1 oscillator is discussed in greater detail in **Section 7.6** "Timer1 Oscillator".

In addition to being a primary clock source, the **internal oscillator block** is available as a power-managed mode clock source. The 31.25 kHz INTRC source is also used as the clock source for several special features, such as the WDT, Fail-Safe Clock Monitor, Power-up Timer and Two-Speed Start-up.

The clock sources for the PIC16F87/88 devices are shown in Figure 4-6. See **Section 7.0** "**Timer1 Module**" for further details of the Timer1 oscillator. See **Section 15.1** "**Configuration Bits**" for Configuration register details.

#### 4.6.1 OSCCON REGISTER

The OSCCON register (Register 4-2) controls several aspects of the system clock's operation, both in full power operation and in power-managed modes.

The System Clock Select bits, SCS1:SCS0, select the clock source that is used when the device is operating in power-managed modes. When the bits are cleared (SCS<1:0> = 00), the system clock source comes from the main oscillator that is selected by the

FOSC2:FOSC0 configuration bits in Configuration Word 1 register. When the bits are set in any other manner, the system clock source is provided by the Timer1 oscillator (SCS1:SCS0 = 01) or from the internal oscillator block (SCS1:SCS0 = 10). After a Reset, SCS<1:0> are always set to '00'.

Note: The instruction to immediately follow the modification of SCS<1:0> will have an instruction time (TcY) based on the previous clock source. This should be taken into consideration when developing time dependant code.

The Internal Oscillator Select bits, IRCF2:IRCF0, select the frequency output of the internal oscillator block that is used to drive the system clock. The choices are the INTRC source (31.25 kHz), the INTOSC source (8 MHz) or one of the six frequencies derived from the INTOSC postscaler (125 kHz to 4 MHz). Changing the configuration of these bits has an immediate change on the multiplexor's frequency output.

The OSTS and IOFS bits indicate the status of the primary oscillator and INTOSC source; these bits are set when their respective oscillators are stable. In particular, OSTS indicates that the Oscillator Start-up Timer has timed out.

#### 4.6.2 CLOCK SWITCHING

Clock switching will occur for the following reasons:

- The FCMEN (CONFIG2<0>) bit is set, the device is running from the primary oscillator and the primary oscillator fails. The clock source will be the internal RC oscillator.

- The FCMEN bit is set, the device is running from the T1OSC and T1OSC fails. The clock source will be the internal RC oscillator.

- Following a wake-up due to a Reset or a POR, when the device is configured for Two-Speed Start-up mode, switching will occur between the INTRC and the system clock defined by the FOSC<2:0> bits.

- A wake-up from Sleep occurs due to an interrupt or WDT wake-up and Two-Speed Start-up is enabled. If the primary clock is XT, HS or LP, the clock will switch between the INTRC and the primary system clock after 1024 clocks (OST) and 8 clocks of the primary oscillator. This is conditional upon the SCS bits being set equal to '00'.

- SCS bits are modified from their original value.

- · IRCF bits are modified from their original value.

Note: Because the SCS bits are cleared on any Reset, no clock switching will occur on a Reset unless the Two-Speed Start-up is enabled and the primary clock is XT, HS or LP. The device will wait for the primary clock to become stable before execution begins (Two-Speed Start-up disabled).

#### FIGURE 4-6: PIC16F87/88 CLOCK DIAGRAM

#### 4.6.4 MODIFYING THE IRCF BITS

The IRCF bits can be modified at any time regardless of which clock source is currently being used as the system clock. The internal oscillator allows users to change the frequency during run time. This is achieved by modifying the IRCF bits in the OSCCON register. The sequence of events that occur after the IRCF bits are modified is dependent upon the initial value of the IRCF bits before they are modified. If the INTRC (31.25 kHz. IRCF < 2:0 > = 000) is running and the IRCF bits are modified to any other value than '000', a 4 ms (approx.) clock switch delay is turned on. Code execution continues at a higher than expected frequency while the new frequency stabilizes. Time sensitive code should wait for the IOFS bit in the OSCCON register to become set before continuing. This bit can be monitored to ensure that the frequency is stable before using the system clock in time critical applications.

If the IRCF bits are modified while the internal oscillator is running at any other frequency than INTRC (31.25 kHz, IRCF<2:0>  $\neq$  000), there is no need for a 4 ms (approx.) clock switch delay. The new INTOSC frequency will be stable immediately after the **eight** falling edges. The IOFS bit will remain set after clock switching occurs.

Note: Caution must be taken when modifying the IRCF bits using BCF or BSF instructions. It is possible to modify the IRCF bits to a frequency that may be out of the VDD specification range; for example, VDD = 2.0V and IRCF = 111 (8 MHz).

#### 4.6.5 CLOCK TRANSITION SEQUENCE

Following are three different sequences for switching the internal RC oscillator frequency.

- Clock before switch: 31.25 kHz (IRCF<2:0> = 000)

- IRCF bits are modified to an INTOSC/INTOSC postscaler frequency.

- The clock switching circuitry waits for a falling edge of the current clock, at which point CLKO is held low.

- The clock switching circuitry then waits for eight falling edges of requested clock, after which it switches CLKO to this new clock source.

- The IOFS bit is clear to indicate that the clock is unstable and a 4 ms (approx.) delay is started. Time dependent code should wait for IOFS to become set.

- 5. Switchover is complete.

- Clock before switch: One of INTOSC/INTOSC postscaler (IRCF<2:0> ≠ 000)

- 1. IRCF bits are modified to INTRC (IRCF<2:0> = 000).

- The clock switching circuitry waits for a falling edge of the current clock, at which point CLKO is held low.

- The clock switching circuitry then waits for eight falling edges of requested clock, after which it switches CLKO to this new clock source.

- 4. Oscillator switchover is complete.

#### 4.7 Power-Managed Modes

#### 4.7.1 RC RUN MODE

When SCS bits are configured to run from the INTRC, a clock transition is generated if the system clock is not already using the INTRC. The event will clear the OSTS bit, switch the system clock from the primary system clock (if SCS<1:0> = 00) determined by the value contained in the configuration bits, or from the T1OSC (if SCS<1:0> = 01) to the INTRC clock option and shut down the primary system clock to conserve power. Clock switching will not occur if the primary system clock is already configured as INTRC.

If the system clock does not come from the INTRC (31.25 kHz) when the SCS bits are changed and the IRCF bits in the OSCCON register are configured for a frequency other than INTRC, the frequency may not be stable immediately. The IOFS bit (OSCCON<2>) will be set when the INTOSC or postscaler frequency is stable, after 4 ms (approx.).

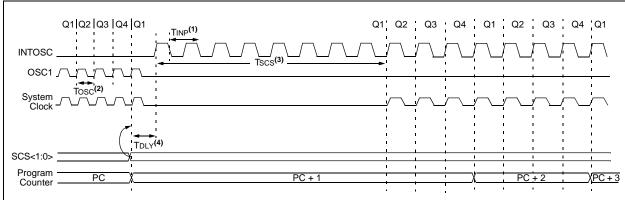

After a clock switch has been executed, the OSTS bit is cleared, indicating a low-power mode and the device does not run from the primary system clock. The internal Q clocks are held in the Q1 state until eight falling edge clocks are counted on the INTRC oscillator. After the eight clock periods have transpired, the clock input to the Q clocks is released and operation resumes (see Figure 4-7).

- **Note 1:** TINP = 32  $\mu$ s typical.

- 2: Tosc = 50 ns minimum.

- 3: TSCS = 8 TINP.

- 4: TDLY = 1 TINP.

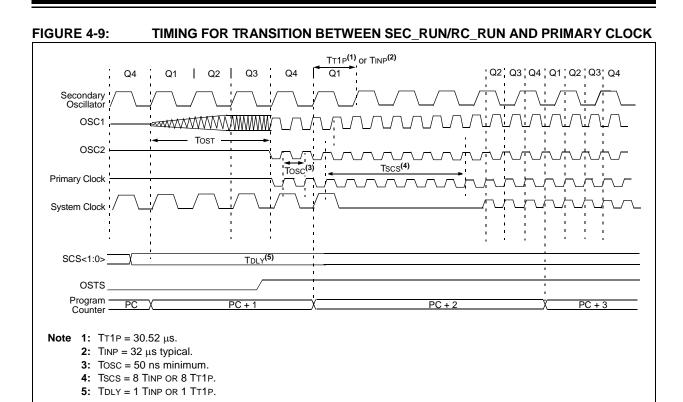

### 4.7.3 SEC\_RUN/RC\_RUN TO PRIMARY CLOCK SOURCE

When switching from a SEC\_RUN or RC\_RUN mode back to the primary system clock, following a change of SCS<1:0> to '00', the sequence of events that takes place will depend upon the value of the FOSC bits in the Configuration register. If the primary clock source is configured as a crystal (HS, XT or LP), then the transition will take place after 1024 clock cycles. This is necessary because the crystal oscillator has been powered down until the time of the transition. In order to provide the system with a reliable clock when the changeover has occurred, the clock will not be released to the changeover circuit until the 1024 count has expired.

During the oscillator start-up time, the system clock comes from the current system clock. Instruction execution and/or peripheral operation continues using the currently selected oscillator as the CPU clock source, until the necessary clock count has expired, to ensure that the primary system clock is stable.

To know when the OST has expired, the OSTS bit should be monitored. OSTS = 1 indicates that the Oscillator Start-up Timer has timed out and the system clock comes from the primary clock source.

Following the oscillator start-up time, the internal Q clocks are held in the Q1 state until eight falling edge clocks are counted from the primary system clock. The clock input to the Q clocks is then released and operation resumes with the primary system clock determined by the FOSC bits (see Figure 4-10).

When in SEC\_RUN mode, the act of clearing the T1OSCEN bit in the T1CON register will cause SCS<0> to be cleared, which causes the SCS<1:0> bits to revert to '00' or '10' depending on what SCS<1> is. Although the T1OSCEN bit was cleared, T1OSC will be enabled and instruction execution will continue until the OST time-out for the main system clock is complete. At that time, the system clock will switch from the T1OSC to the primary clock or the INTRC. Following this, the T1 oscillator will be shut down.

Note:

If the primary system clock is either RC or EC, an internal delay timer (5-10  $\mu s)$  will suspend operation after exiting Secondary Clock mode to allow the CPU to become ready for code execution.

### 4.7.3.1 Returning to Primary Clock Source Sequence

Changing back to the primary oscillator from SEC\_RUN or RC\_RUN can be accomplished by either changing SCS<1:0> to '00', or clearing the T1OSCEN bit in the T1CON register (if T1OSC was the secondary clock).

The sequence of events that follows is the same for both modes:

- If the primary system clock is configured as EC, RC or INTRC, then the OST time-out is skipped. Skip to step 3.

- If the primary system clock is configured as an external oscillator (HS, XT, LP), then the OST will be active, waiting for 1024 clocks of the primary system clock.

- 3. On the following Q1, the device holds the system clock in Q1.

- The device stays in Q1 while eight falling edges of the primary system clock are counted.

- 5. Once the eight counts transpire, the device begins to run from the primary oscillator.

- If the secondary clock was INTRC and the primary is not INTRC, the INTRC will be shut down to save current providing that the INTRC is not being used for any other function, such as WDT or Fail-Safe Clock monitoring.

- 7. If the secondary clock was T1OSC, the T1OSC will continue to run if T1OSCEN is still set; otherwise, the T1 oscillator will be shut down.

### PIC16F87/88

### 4.7.4 EXITING SLEEP WITH AN INTERRUPT

Any interrupt, such as WDT or INT0, will cause the part to leave the Sleep mode.

The SCS bits are unaffected by a SLEEP command and are the same before and after entering and leaving Sleep. The clock source used after an exit from Sleep is determined by the SCS bits.

#### 4.7.4.1 Sequence of Events

#### If SCS<1:0> = 00:

- 1. The device is held in Sleep until the CPU start-up time-out is complete.

- 2. If the primary system clock is configured as an external oscillator (HS, XT, LP), then the OST will be active waiting for 1024 clocks of the primary system clock. While waiting for the OST, the device will be held in Sleep unless Two-Speed Start-up is enabled. The OST and CPU start-up timers run in parallel. Refer to Section 15.12.3 "Two-Speed Clock Start-up Mode" for details on Two-Speed Start-up.

- After both the CPU start-up and OST timers have timed out, the device will exit Sleep and begin instruction execution with the primary clock defined by the FOSC bits.

#### If SCS<1:0> = 01 or 10:

- The device is held in Sleep until the CPU start-up time-out is complete.

- After the CPU start-up timer has timed out, the device will exit Sleep and begin instruction execution with the selected oscillator mode.

Note: If a user changes SCS<1:0> just before entering Sleep mode, the system clock used when exiting Sleep mode could be different than the system clock used when entering Sleep mode.

As an example, if SCS<1:0> = 01 and T1OSC is the system clock and the following instructions are executed:

BCF OSCCON, SCS0 SLEEP

then a clock change event is executed. If the primary oscillator is XT, LP or HS, the core will continue to run off T1OSC and execute the SLEEP command.

When Sleep is exited, the part will resume operation with the primary oscillator after the OST has expired.

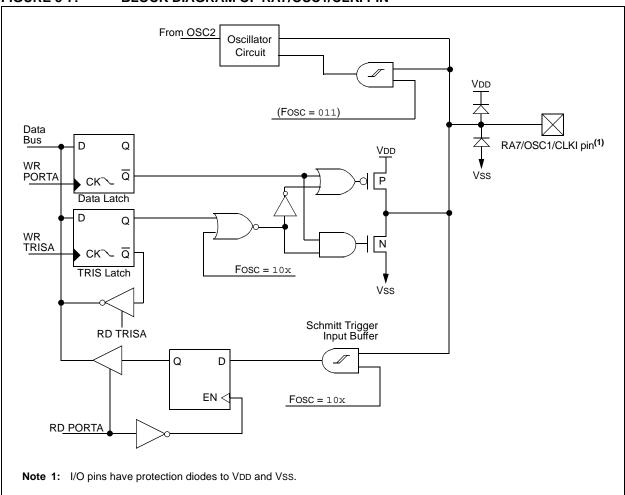

FIGURE 5-7: BLOCK DIAGRAM OF RA7/OSC1/CLKI PIN

#### **EXAMPLE 6-1: CHANGING THE PRESCALER ASSIGNMENT FROM WDT TO TIMER0**

CLRWDT ; Clear WDT and prescaler

BANKSEL OPTION\_REG ; Select Bank of OPTION\_REG

MOVLW b'xxxx0xxx' ; Select TMR0, new prescale

MOVWF OPTION\_REG ; value and clock source

#### TABLE 6-1: REGISTERS ASSOCIATED WITH TIMERO

| Address               | Name       | Bit 7     | Bit 6      | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|-----------------------|------------|-----------|------------|--------|--------|-------|--------|--------|-------|----------------------|---------------------------------|

| 01h,101h              | TMR0       | Timer0 Mo | dule Regis | ter    |        |       |        |        |       | xxxx xxxx            | uuuu uuuu                       |

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON     | GIE       | PEIE       | TMR0IE | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF  | 0000 000x            | 0000 000u                       |

| 81h,181h              | OPTION_REG | RBPU      | INTEDG     | T0CS   | T0SE   | PSA   | PS2    | PS1    | PS0   | 1111 1111            | 1111 1111                       |

**Legend:** x = unknown, u = unchanged. Shaded cells are not used by Timer0.

The maximum PWM resolution (bits) for a given PWM frequency is given by the following formula.

#### **EQUATION 9-3:**

Resolution

$$=$$

$\frac{\log(\frac{FOSC}{FPWM})}{\log(2)}$  bits

**Note:** If the PWM duty cycle value is longer than the PWM period, the CCP1 pin will not be cleared.

#### 9.3.3 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- 3. Make the CCP1 pin an output by clearing the TRISB<x> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

Note: The TRISB bit (0 or 3) is dependant upon the setting of configuration bit 12 (CCPMX).

TABLE 9-3: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 20 MHz

| PWM Frequency              | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|----------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                  | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8         | 7         | 6.6       |

#### TABLE 9-4: REGISTERS ASSOCIATED WITH PWM AND TIMER2

| Address              | Name    | Bit 7                                | Bit 6               | Bit 5         | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value<br>POR, |      | all o | e on<br>ther<br>sets |

|----------------------|---------|--------------------------------------|---------------------|---------------|---------|---------|--------|---------|---------|---------------|------|-------|----------------------|

| 0Bh,8Bh<br>10Bh,18Bh | INTCON  | GIE                                  | PEIE                | TMR0IE        | INT0IE  | RBIE    | TMR0IF | INT0IF  | RBIF    | 0000          | x000 | 0000  | 000u                 |

| 0Ch                  | PIR1    | _                                    | ADIF <sup>(1)</sup> | RCIF          | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | -000          | 0000 | -000  | 0000                 |

| 8Ch                  | PIE1    | _                                    | ADIE <sup>(1)</sup> | RCIE          | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | -000          | 0000 | -000  | 0000                 |

| 86h                  | TRISB   | PORTI                                | 3 Data Dired        | ction Registe | er      |         |        |         |         | 1111          | 1111 | 1111  | 1111                 |

| 11h                  | TMR2    | Timer2                               | Module Reg          | gister        |         |         |        |         |         | 0000          | 0000 | 0000  | 0000                 |

| 92h                  | PR2     | Timer2                               | Period Regi         | ster          |         |         |        |         |         | 1111          | 1111 | 1111  | 1111                 |

| 12h                  | T2CON   | _                                    | TOUTPS3             | TOUTPS2       | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000          | 0000 | -000  | 0000                 |

| 15h                  | CCPR1L  | Capture/Compare/PWM Register 1 (LSB) |                     |               |         |         |        |         | xxxx    | xxxx          | uuuu | uuuu  |                      |

| 16h                  | CCPR1H  | Capture/Compare/PWM Register 1 (MSB) |                     |               |         |         |        |         | xxxx    | xxxx          | uuuu | uuuu  |                      |

| 17h                  | CCP1CON | _                                    | _                   | CCP1X         | CCP1Y   | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0  | 00            | 0000 | 00    | 0000                 |

**Legend:** x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PWM and Timer2.

Note 1: This bit is only implemented on the PIC16F88. The bit will read '0' on the PIC16F87.

#### PIC16F87/88

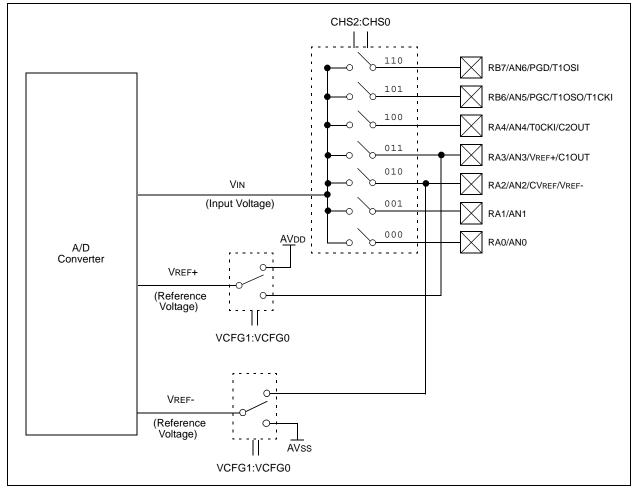

The ADRESH:ADRESL registers contain the result of the A/D conversion. When the A/D conversion is complete, the result is loaded into the A/D Result register pair, the GO/DONE bit (ADCON0<2>) is cleared and A/D Interrupt Flag bit, ADIF, is set. The block diagram of the A/D module is shown in Figure 12-1.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as inputs.

To determine sample time, see **Section 12.1 "A/D Acquisition Requirements"**. After this sample time has elapsed, the A/D conversion can be started.

These steps should be followed for doing an A/D conversion:

- 1. Configure the A/D module:

- · Configure analog/digital I/O (ANSEL)

- · Configure voltage reference (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D conversion clock (ADCON0)

- Turn on A/D module (ADCON0)

- 2. Configure A/D interrupt (if desired):

- · Clear ADIF bit

- · Set ADIE bit

- · SET PEIE bit

- · Set GIE bit

- 3. Wait the required acquisition time.

- 4. Start conversion:

- Set GO/DONE bit (ADCON0)

- 5. Wait for A/D conversion to complete, by either:

- Polling for the GO/DONE bit to be cleared (with interrupts disabled); OR

- · Waiting for the A/D interrupt

- Read A/D Result register pair (ADRESH:ADRESL), clear bit ADIF if required.

- For next conversion, go to step 1 or step 2 as required. The A/D conversion time per bit is defined as TAD. A minimum wait of 2 TAD is required before the next acquisition starts.

FIGURE 12-1: A/D BLOCK DIAGRAM

### 17.2 MPLAB C Compilers for Various Device Families

The MPLAB C Compiler code development systems are complete ANSI C compilers for Microchip's PIC18, PIC24 and PIC32 families of microcontrollers and the dsPIC30 and dsPIC33 families of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

### 17.3 HI-TECH C for Various Device Families

The HI-TECH C Compiler code development systems are complete ANSI C compilers for Microchip's PIC family of microcontrollers and the dsPIC family of digital signal controllers. These compilers provide powerful integration capabilities, omniscient code generation and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

The compilers include a macro assembler, linker, preprocessor, and one-step driver, and can run on multiple platforms.

#### 17.4 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel® standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

#### 17.5 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

## 17.6 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC devices. MPLAB C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command line interface

- · Rich directive set

- Flexible macro language

- MPLAB IDE compatibility

# 18.2 DC Characteristics: Power-Down and Supply Current PIC16F87/88 (Industrial, Extended) PIC16LF87/88 (Industrial) (Continued)

|              | PIC16LF87/88<br>(Industrial)                                                                                                                                                                                                        |     |     | rating Co | •      | ss otherwise stated<br>A ≤ +85°C for indus | •                                         |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----------|--------|--------------------------------------------|-------------------------------------------|--|--|

| PIC16F8      | Standard Operating Conditions (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for extended |     |     |           |        |                                            |                                           |  |  |

| Param<br>No. | Device                                                                                                                                                                                                                              | Тур | Max | Units     |        | Condi                                      | tions                                     |  |  |

|              | Supply Current (IDD) <sup>(2,3)</sup>                                                                                                                                                                                               |     |     |           |        |                                            |                                           |  |  |

|              | PIC16LF87/88                                                                                                                                                                                                                        | 8   | 20  | μА        | -40°C  |                                            |                                           |  |  |

|              |                                                                                                                                                                                                                                     | 7   | 15  | μΑ        | +25°C  | VDD = 2.0V                                 |                                           |  |  |

|              |                                                                                                                                                                                                                                     | 7   | 15  | μΑ        | +85°C  |                                            |                                           |  |  |

|              | PIC16LF87/88                                                                                                                                                                                                                        | 16  | 30  | μΑ        | -40°C  |                                            | _                                         |  |  |

|              |                                                                                                                                                                                                                                     | 14  | 25  | μΑ        | +25°C  | VDD = 3.0V                                 | Fosc = 31.25 kHz<br>( <b>RC_RUN</b> mode, |  |  |

|              |                                                                                                                                                                                                                                     | 14  | 25  | μΑ        | +85°C  |                                            | Internal RC Oscillator)                   |  |  |

|              | All devices                                                                                                                                                                                                                         | 32  | 40  | μΑ        | -40°C  |                                            | ,                                         |  |  |

|              |                                                                                                                                                                                                                                     | 29  | 35  | μΑ        | +25°C  | VDD = 5.0V                                 |                                           |  |  |

|              |                                                                                                                                                                                                                                     | 29  | 35  | μΑ        | +85°C  | VDD = 3.0 V                                |                                           |  |  |

|              | Extended devices                                                                                                                                                                                                                    | 35  | 45  | μΑ        | +125°C |                                            |                                           |  |  |

|              | PIC16LF87/88                                                                                                                                                                                                                        | 132 | 160 | μΑ        | -40°C  |                                            |                                           |  |  |

|              |                                                                                                                                                                                                                                     | 126 | 155 | μΑ        | +25°C  | VDD = 2.0V                                 |                                           |  |  |

|              |                                                                                                                                                                                                                                     | 126 | 155 | μΑ        | +85°C  |                                            |                                           |  |  |

|              | PIC16LF87/88                                                                                                                                                                                                                        | 260 | 310 | μΑ        | -40°C  |                                            |                                           |  |  |

|              |                                                                                                                                                                                                                                     | 230 | 300 | μΑ        | +25°C  | VDD = 3.0V                                 | Fosc = 1 MHz<br>( <b>RC RUN</b> mode,     |  |  |

|              | All devices                                                                                                                                                                                                                         | 230 | 300 | μΑ        | +85°C  |                                            | Internal RC Oscillator)                   |  |  |

|              |                                                                                                                                                                                                                                     | 560 | 690 | μΑ        | -40°C  |                                            |                                           |  |  |

|              |                                                                                                                                                                                                                                     | 500 | 650 | μА        | +25°C  | VDD = 5.0V                                 |                                           |  |  |

|              |                                                                                                                                                                                                                                     | 500 | 650 | μΑ        | +85°C  | VDD = 3.0 V                                |                                           |  |  |

|              | Extended devices                                                                                                                                                                                                                    | 570 | 710 | μΑ        | +125°C |                                            |                                           |  |  |

**Legend:** Shading of rows is to assist in readability of the table.

- Note 1: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or Vss and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

- 2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;

MCLR = VDD; WDT enabled/disabled as specified.

3: For RC oscillator configurations, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in  $k\Omega$ .

### 18.4 DC Characteristics: PIC16F87/88 (Industrial, Extended) PIC16LF87/88 (Industrial)

| DC CH        | ARACT | ERISTICS                     | Standard Operating Conditions (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for extended  Operating voltage VDD range as described in DC Specification, Section 18.1 "DC Characteristics: Supply Voltage". |      |          |       |                                                                                                                                                       |  |  |

|--------------|-------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Param<br>No. | Sym   | Characteristic               | Min                                                                                                                                                                                                                                                                                                                                                   | Тур† | Max      | Units | Conditions                                                                                                                                            |  |  |

|              | VIL   | Input Low Voltage            |                                                                                                                                                                                                                                                                                                                                                       |      |          |       |                                                                                                                                                       |  |  |

|              |       | I/O ports:                   |                                                                                                                                                                                                                                                                                                                                                       |      |          |       |                                                                                                                                                       |  |  |

| D030         |       | with TTL buffer              | Vss                                                                                                                                                                                                                                                                                                                                                   | _    | 0.15 VDD | V     | For entire VDD range                                                                                                                                  |  |  |

| D030A        |       |                              | Vss                                                                                                                                                                                                                                                                                                                                                   | _    | 0.8V     | V     | $4.5V \le VDD \le 5.5V$                                                                                                                               |  |  |

| D031         |       | with Schmitt Trigger buffer  | Vss                                                                                                                                                                                                                                                                                                                                                   | _    | 0.2 VDD  | V     |                                                                                                                                                       |  |  |

| D032         |       | MCLR, OSC1 (in RC mode)      | Vss                                                                                                                                                                                                                                                                                                                                                   | _    | 0.2 VDD  | V     | (Note 1)                                                                                                                                              |  |  |

| D033         |       | OSC1 (in XT and LP mode)     | Vss                                                                                                                                                                                                                                                                                                                                                   | _    | 0.3V     | V     |                                                                                                                                                       |  |  |

|              |       | OSC1 (in HS mode)            | Vss                                                                                                                                                                                                                                                                                                                                                   | _    | 0.3 VDD  | V     |                                                                                                                                                       |  |  |

|              |       | Ports RB1 and RB4:           |                                                                                                                                                                                                                                                                                                                                                       |      |          |       |                                                                                                                                                       |  |  |

| D034         |       | with Schmitt Trigger buffer  | Vss                                                                                                                                                                                                                                                                                                                                                   | _    | 0.3 VDD  | V     | For entire VDD range                                                                                                                                  |  |  |

|              | VIH   | Input High Voltage           |                                                                                                                                                                                                                                                                                                                                                       |      |          |       |                                                                                                                                                       |  |  |

|              |       | I/O ports:                   |                                                                                                                                                                                                                                                                                                                                                       |      |          |       |                                                                                                                                                       |  |  |

| D040         |       | with TTL buffer              | 2.0                                                                                                                                                                                                                                                                                                                                                   | _    | Vdd      | V     | $4.5V \le VDD \le 5.5V$                                                                                                                               |  |  |

| D040A        |       |                              | 0.25 VDD + 0.8V                                                                                                                                                                                                                                                                                                                                       | _    | Vdd      | V     | For entire VDD range                                                                                                                                  |  |  |

| D041         |       | with Schmitt Trigger buffer  | 0.8 VDD                                                                                                                                                                                                                                                                                                                                               | _    | Vdd      | V     | For entire VDD range                                                                                                                                  |  |  |

| D042         |       | MCLR                         | 0.8 VDD                                                                                                                                                                                                                                                                                                                                               | _    | Vdd      | V     |                                                                                                                                                       |  |  |

| D042A        |       | OSC1 (in XT and LP mode)     | 1.6V                                                                                                                                                                                                                                                                                                                                                  | _    | Vdd      | V     |                                                                                                                                                       |  |  |

|              |       | OSC1 (in HS mode)            | 0.7 VDD                                                                                                                                                                                                                                                                                                                                               | _    | VDD      | V     |                                                                                                                                                       |  |  |

| D043         |       | OSC1 (in RC mode)            | 0.9 VDD                                                                                                                                                                                                                                                                                                                                               | _    | Vdd      | V     | (Note 1)                                                                                                                                              |  |  |

|              |       | Ports RB1 and RB4:           |                                                                                                                                                                                                                                                                                                                                                       |      |          |       |                                                                                                                                                       |  |  |

| D044         |       | with Schmitt Trigger buffer  | 0.7 VDD                                                                                                                                                                                                                                                                                                                                               | _    | Vdd      | V     | For entire VDD range                                                                                                                                  |  |  |

| D070         | IPURB | PORTB Weak Pull-up Current   | 50                                                                                                                                                                                                                                                                                                                                                    | 250  | 400      | μΑ    | VDD = 5V, VPIN = VSS                                                                                                                                  |  |  |

|              | lı∟   | Input Leakage Current (Notes | 2, 3)                                                                                                                                                                                                                                                                                                                                                 |      |          |       |                                                                                                                                                       |  |  |

| D060         |       | I/O ports                    | _                                                                                                                                                                                                                                                                                                                                                     |      | ±1       | μА    | Vss ≤ VPIN ≤ VDD, pin at high-impedance                                                                                                               |  |  |

| D061         |       | MCLR                         | _                                                                                                                                                                                                                                                                                                                                                     | _    | ±5       | μΑ    | $Vss \le VPIN \le VDD$                                                                                                                                |  |  |

| D063         |       | OSC1                         | _                                                                                                                                                                                                                                                                                                                                                     | _    | ±5       | μА    | $\label{eq:VSS} \begin{array}{l} \text{VSS} \leq \text{VPIN} \leq \text{VDD, XT, HS} \\ \text{and LP oscillator} \\ \text{configuration} \end{array}$ |  |  |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1/CLKI pin is a Schmitt Trigger input. It is not recommended that the PIC16F87/88 be driven with external clock in RC mode.

<sup>2:</sup> The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

<sup>3:</sup> Negative current is defined as current sourced by the pin.

### PIC16F87/88

TABLE 18-10: I<sup>2</sup>C™ BUS DATA REQUIREMENTS

| Param.<br>No. | Symbol  | Characte             | eristic      | Min         | Max  | Units | Conditions                           |

|---------------|---------|----------------------|--------------|-------------|------|-------|--------------------------------------|

| 100*          | THIGH   | Clock High Time      | 100 kHz mode | 4.0         | _    | μS    |                                      |

|               |         |                      | 400 kHz mode | 0.6         | _    | μS    |                                      |

|               |         |                      | SSP Module   | 1.5 TcY     | _    |       |                                      |

| 101*          | TLOW    | Clock Low Time       | 100 kHz mode | 4.7         | _    | μS    |                                      |

|               |         |                      | 400 kHz mode | 1.3         | _    | μS    |                                      |

|               |         |                      | SSP Module   | 1.5 TcY     | _    |       |                                      |

| 102*          | TR      | SDA and SCL Rise     | 100 kHz mode | _           | 1000 | ns    |                                      |

|               |         | Time                 | 400 kHz mode | 20 + 0.1 CB | 300  | ns    | CB is specified to be from 10-400 pF |

| 103*          | TF      | SDA and SCL Fall     | 100 kHz mode | _           | 300  | ns    |                                      |

|               |         | Time                 | 400 kHz mode | 20 + 0.1 CB | 300  | ns    | CB is specified to be from 10-400 pF |

| 90*           | Tsu:sta | Start Condition      | 100 kHz mode | 4.7         | -    | μS    | Only relevant for                    |

|               |         | Setup Time           | 400 kHz mode | 0.6         | _    | μS    | Repeated Start condition             |

| 91*           | THD:STA | Start Condition Hold | 100 kHz mode | 4.0         | _    | μS    | After this period, the first         |

|               |         | Time                 | 400 kHz mode | 0.6         | _    | μS    | clock pulse is generated             |

| 106*          | THD:DAT | Data Input Hold      | 100 kHz mode | 0           |      | ns    |                                      |

|               |         | Time                 | 400 kHz mode | 0           | 0.9  | μS    |                                      |

| 107*          | TSU:DAT | Data Input Setup     | 100 kHz mode | 250         |      | ns    | (Note 2)                             |

|               |         | Time                 | 400 kHz mode | 100         |      | ns    |                                      |

| 92*           | Tsu:sto | Stop Condition       | 100 kHz mode | 4.7         | 1    | μS    |                                      |

|               |         | Setup Time           | 400 kHz mode | 0.6         |      | μS    |                                      |

| 109*          | TAA     | Output Valid from    | 100 kHz mode | _           | 3500 | ns    | (Note 1)                             |

|               |         | Clock                | 400 kHz mode | _           | _    | ns    |                                      |

| 110*          | TBUF    | Bus Free Time        | 100 kHz mode | 4.7         | _    | μS    | Time the bus must be free            |

|               |         |                      | 400 kHz mode | 1.3         | 1    | μS    | before a new transmission can start  |

|               | Св      | Bus Capacitive Load  | ling         | _           | 400  | pF    |                                      |

<sup>\*</sup> These parameters are characterized but not tested.

- **Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of Start or Stop conditions.

- 2: A Fast mode (400 kHz) I<sup>2</sup>C<sup>TM</sup> bus device can be used in a Standard mode (100 kHz) I<sup>2</sup>C bus system, but the requirement, TSU:DAT ≥ 250 ns, must then be met. This will automatically be the case if the device does not stretch the low period of the SCL signal. If such a device does stretch the low period of the SCL signal, it must output the next data bit to the SDA line, TR max. + TSU:DAT = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification), before the SCL line is released.

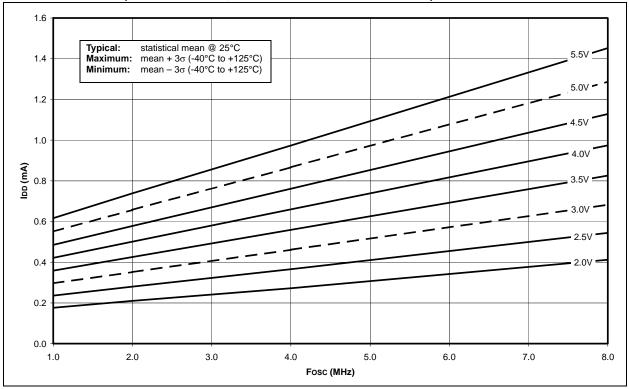

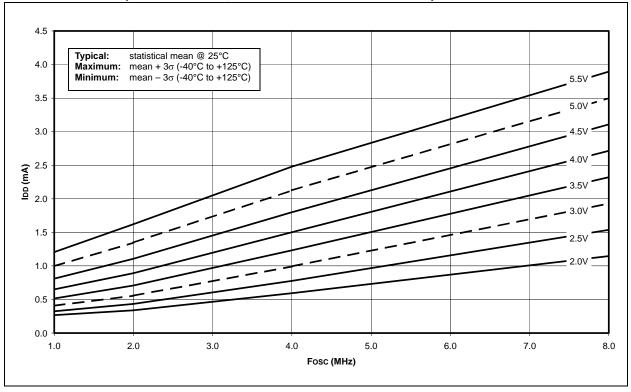

FIGURE 19-7: TYPICAL IDD vs. VDD, -40°C TO +125°C, 1 MHz TO 8 MHz (RC\_RUN MODE, ALL PERIPHERALS DISABLED)

FIGURE 19-8: MAXIMUM IDD vs. VDD, -40°C TO +125°C, 1 MHz TO 8 MHz (RC\_RUN MODE, ALL PERIPHERALS DISABLED)

#### **INDEX**

| A                                                                 | Baud Rate Generator (BRG)                 | 101      |

|-------------------------------------------------------------------|-------------------------------------------|----------|

| A/D                                                               | Baud Rate Formula                         | 101      |

| Acquisition Requirements119                                       | Baud Rates, Asynchronous Mode (BRGH       | = 0) 102 |

| ADIF Bit118                                                       | Baud Rates, Asynchronous Mode (BRGH       | = 1) 102 |

| Analog-to-Digital Converter115                                    | High Baud Rate Select (BRGH Bit)          | 99       |

| Associated Registers122                                           | INTRC Baud Rates, Asynchronous Mode       | (BRGH =  |

| Calculating Acquisition Time                                      | 0)                                        | 103      |

| Configuring Analog Port Pins121                                   | INTRC Baud Rates, Asynchronous Mode       | (BRGH =  |

| • •                                                               | 1)                                        | 103      |

| Configuring the Interrupt                                         | INTRC Operation                           | 101      |

| Configuring the Module118 Conversion Clock120                     | Low-Power Mode Operation                  |          |

|                                                                   | Sampling                                  |          |

| Conversions                                                       | Clock Source Select (CSRC Bit)            |          |

| Converter Characteristics                                         | Continuous Receive Enable (CREN Bit)      |          |

| Delays119                                                         | Framing Error (FERR Bit)                  |          |

| Effects of a Reset                                                | Mode Select (SYNC Bit)                    |          |

| GO/DONE Bit                                                       | Receive Data, 9th bit (RX9D Bit)          |          |

| Internal Sampling Switch (Rss) Impedance119                       | Receive Enable, 9-bit (RX9 Bit)           |          |