Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Active                                                                 |

| Core Processor             | PIC                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 20MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                  |

| Number of I/O              | 16                                                                     |

| Program Memory Size        | 7KB (4K x 14)                                                          |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 256 x 8                                                                |

| RAM Size                   | 368 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                              |

| Data Converters            | A/D 7x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Through Hole                                                           |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                |

| Supplier Device Package    | 18-PDIP                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f88-i-p |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1.0   | Device Overview                                                              | 5     |

|-------|------------------------------------------------------------------------------|-------|

| 2.0   | Memory Organization                                                          |       |

| 3.0   | Data EEPROM and Flash Program Memory                                         | 27    |

| 4.0   | Oscillator Configurations                                                    | 35    |

| 5.0   | I/O Ports                                                                    |       |

| 6.0   | Timer0 Module                                                                | 67    |

| 7.0   | Timer1 Module                                                                | 71    |

| 8.0   | Timer2 Module                                                                | 79    |

| 9.0   | Capture/Compare/PWM (CCP) Module                                             | 81    |

| 10.0  | Synchronous Serial Port (SSP) Module                                         | 87    |

| 11.0  | Addressable Universal Synchronous Asynchronous Receiver Transmitter (AUSART) | 97    |

| 12.0  | Analog-to-Digital Converter (A/D) Module                                     | . 113 |

|       | Comparator Module                                                            |       |

|       | Comparator Voltage Reference Module                                          |       |

| 15.0  | Special Features of the CPU                                                  | . 129 |

| 16.0  | Instruction Set Summary                                                      | . 149 |

| 17.0  | Development Support                                                          | . 157 |

| 18.0  | Electrical Characteristics                                                   | . 161 |

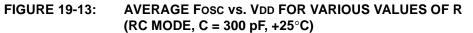

| 19.0  | DC and AC Characteristics Graphs and Tables                                  | . 191 |

| 20.0  | Packaging Information                                                        | . 205 |

| Appe  | ndix A: Revision History                                                     | . 215 |

| Appe  | ndix B: Device Differences                                                   | . 215 |

| INDE  | X                                                                            | . 217 |

| The I | Aicrochip Web Site                                                           | . 225 |

| Custo | omer Change Notification Service                                             | . 225 |

| Custo | omer Support                                                                 | . 225 |

| Read  | er Response                                                                  | . 226 |

| PIC1  | 6F87/88 Product Identification System                                        | . 227 |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# 6.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- Interrupt-on-overflow from FFh to 00h

- Edge select for external clock

Additional information on the Timer0 module is available in the "*PIC*<sup>®</sup> *Mid-Range MCU Family Reference Manual*" (DS33023).

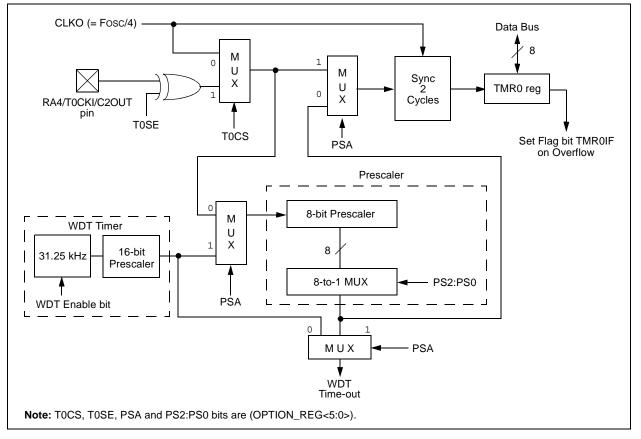

Figure 6-1 is a block diagram of the Timer0 module and the prescaler shared with the WDT.

### 6.1 Timer0 Operation

Timer0 operation is controlled through the OPTION\_REG register (see Register 2-2). Timer mode is selected by clearing bit T0CS (OPTION\_REG<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting bit T0CS (OPTION\_REG<5>). In Counter mode, Timer0 will increment, either on every rising or falling edge of pin RA4/ T0CKI/C2OUT. The incrementing edge is determined by the Timer0 Source Edge Select bit, T0SE (OPTION\_REG<4>). Clearing bit T0SE selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 6.3 "Using Timer0 with an External Clock".

The prescaler is mutually, exclusively shared between the Timer0 module and the Watchdog Timer. The prescaler is not readable or writable. **Section 6.4** "**Prescaler**" details the operation of the prescaler.

# 6.2 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets bit TMR0IF (INTCON<2>). The interrupt can be masked by clearing bit TMR0IE (INTCON<5>). Bit TMR0IF must be cleared in software by the Timer0 module Interrupt Service Routine before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from Sleep, since the timer is shut off during Sleep.

#### FIGURE 6-1: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

© 2002-2013 Microchip Technology Inc.

# 7.0 TIMER1 MODULE

The Timer1 module is a 16-bit timer/counter consisting of two 8-bit registers (TMR1H and TMR1L) which are readable and writable. The TMR1 register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 interrupt, if enabled, is generated on overflow which is latched in interrupt flag bit, TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing TMR1 interrupt enable bit, TMR1IE (PIE1<0>).

The Timer1 oscillator can be used as a secondary clock source in low-power modes. When the T1RUN bit is set along with SCS<1:0> = 01, the Timer1 oscillator is providing the system clock. If the Fail-Safe Clock Monitor is enabled and the Timer1 oscillator fails while providing the system clock, polling the T1RUN bit will indicate whether the clock is being provided by the Timer1 oscillator or another source.

Timer1 can also be used to provide Real-Time Clock (RTC) functionality to applications with only a minimal addition of external components and code overhead.

# 7.1 Timer1 Operation

Timer1 can operate in one of three modes:

- as a Timer

- as a Synchronous Counter

- as an Asynchronous Counter

The operating mode is determined by the clock select bit, TMR1CS (T1CON<1>).

In Timer mode, Timer1 increments every instruction cycle. In Counter mode, it increments on every rising edge of the external clock input.

Timer1 can be enabled/disabled by setting/clearing control bit, TMR1ON (T1CON<0>).

Timer1 also has an internal "Reset input". This Reset can be generated by the CCP1 module as the special event trigger (see **Section 9.1** "**Capture Mode**"). Register 7-1 shows the Timer1 Control register.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RB6/PGC/T1OSO/T1CKI and RB7/PGD/ T1OSI pins become inputs. That is, the TRISB<7:6> value is ignored and these pins read as '0'.

Additional information on timer modules is available in the "*PIC*<sup>®</sup> *Mid-Range MCU Family Reference Manual*" (DS33023).

| REGISTER 7-1: | T1CON: T                                                                                                                                                                              | IMER1 CC                    | NTROL RE                                        | EGISTER (A    | DDRESS 1     | 0h)        |                |        |  |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------------------------------------------------|---------------|--------------|------------|----------------|--------|--|--|--|--|

|               | U-0                                                                                                                                                                                   | R-0                         | R/W-0                                           | R/W-0         | R/W-0        | R/W-0      | R/W-0          | R/W-0  |  |  |  |  |

|               | _                                                                                                                                                                                     | T1RUN                       | T1CKPS1                                         | T1CKPS0       | T1OSCEN      | T1SYNC     | TMR1CS         | TMR10N |  |  |  |  |

|               | bit 7                                                                                                                                                                                 |                             |                                                 |               |              |            |                | bit 0  |  |  |  |  |

| bit 7         | Unimplom                                                                                                                                                                              | ented: Read                 |                                                 |               |              |            |                |        |  |  |  |  |

| bit 6         | -                                                                                                                                                                                     |                             |                                                 | ic hit        |              |            |                |        |  |  |  |  |

| bit 0         | bit 6 <b>T1RUN</b> : Timer1 System Clock Status bit<br>1 = System clock is derived from Timer1 oscillator<br>0 = System clock is derived from another source                          |                             |                                                 |               |              |            |                |        |  |  |  |  |

| bit 5-4       | T1CKPS<1                                                                                                                                                                              | I:0>: Timer1                | Input Clock                                     | Prescale Sele | ect bits     |            |                |        |  |  |  |  |

|               | bit 5-4 <b>T1CKPS&lt;1:0&gt;:</b> Timer1 Input Clock Prescale Select bits<br>11 = 1:8 Prescale value<br>10 = 1:4 Prescale value<br>01 = 1:2 Prescale value<br>00 = 1:1 Prescale value |                             |                                                 |               |              |            |                |        |  |  |  |  |

| bit 3         | T1OSCEN: Timer1 Oscillator Enable Control bit                                                                                                                                         |                             |                                                 |               |              |            |                |        |  |  |  |  |

|               | <ul> <li>1 = Oscillator is enabled</li> <li>0 = Oscillator is shut off (the oscillator inverter is turned off to eliminate power drain)</li> </ul>                                    |                             |                                                 |               |              |            |                |        |  |  |  |  |

| bit 2         | T1SYNC: 1                                                                                                                                                                             | Fimer1 Exter                | nal Clock Inp                                   | out Synchroni | zation Contr | ol bit     |                |        |  |  |  |  |

|               | 0 = Synchr<br><u>TMR1CS =</u>                                                                                                                                                         | synchronize<br>onize exterr | e external clo<br>al clock inpu<br>er1 uses the |               | when TMR1    | ICS = 0.   |                |        |  |  |  |  |

| bit 1         | TMR1CS:                                                                                                                                                                               | Timer1 Cloc                 | k Source Sel                                    | ect bit       |              |            |                |        |  |  |  |  |

|               | <ul> <li>1 = External clock from pin RB6/AN5<sup>(1)</sup>/PGC/T1OSO/T1CKI (on the rising edge)</li> <li>0 = Internal clock (Fosc/4)</li> </ul>                                       |                             |                                                 |               |              |            |                |        |  |  |  |  |

|               | Note 1:                                                                                                                                                                               | Available o                 | n PIC16F88                                      | devices only. |              |            |                |        |  |  |  |  |

| bit 0         | <b>TMR1ON:</b><br>1 = Enable<br>0 = Stops                                                                                                                                             |                             |                                                 |               |              |            |                |        |  |  |  |  |

|               | <b>Legend:</b><br>R = Reada                                                                                                                                                           | able bit                    | W = W                                           | /ritable bit  | U = Unimp    | lemented b | bit, read as ' | ·0'    |  |  |  |  |

'1' = Bit is set

'0' = Bit is cleared

-n = Value at POR

x = Bit is unknown

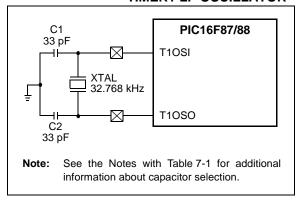

# 7.6 Timer1 Oscillator

A crystal oscillator circuit is built between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low-power oscillator, rated up to 32.768 kHz. It will continue to run during all power-managed modes. It is primarily intended for a 32 kHz crystal. The circuit for a typical LP oscillator is shown in Figure 7-3. Table 7-1 shows the capacitor selection for the Timer1 oscillator.

The user must provide a software time delay to ensure proper oscillator start-up.

Note: The Timer1 oscillator shares the T1OSI and T1OSO pins with the PGD and PGC pins used for programming and debugging. When using the Timer1 oscillator, In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) may not function correctly (high voltage or low voltage), or the In-Circuit Debugger (ICD) may not communicate with the controller. As a result of using either ICSP or ICD, the Timer1 crystal may be damaged. If ICSP or ICD operations are required, the crystal should be disconnected from the circuit (disconnect either lead) or installed after programming. The oscillator loading capacitors may remain in-circuit during ICSP or ICD operation.

#### FIGURE 7-3: EXTERNAL COMPONENTS FOR THE TIMER1 LP OSCILLATOR

# TABLE 7-1:CAPACITOR SELECTION FOR<br/>THE TIMER1 OSCILLATOR

| Osc Type | Freq   | C1    | C2    |

|----------|--------|-------|-------|

| LP       | 32 kHz | 33 pF | 33 pF |

- **Note 1:** Microchip suggests this value as a starting point in validating the oscillator circuit.

- **2:** Higher capacitance increases the stability of the oscillator but also increases the start-up time.

- 3: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- 4: Capacitor values are for design guidance only.

# 7.7 Timer1 Oscillator Layout Considerations

The Timer1 oscillator circuit draws very little power during operation. Due to the low-power nature of the oscillator, it may also be sensitive to rapidly changing signals in close proximity.

The oscillator circuit, shown in Figure 7-3, should be located as close as possible to the microcontroller. There should be no circuits passing within the oscillator circuit boundaries other than Vss or VDD.

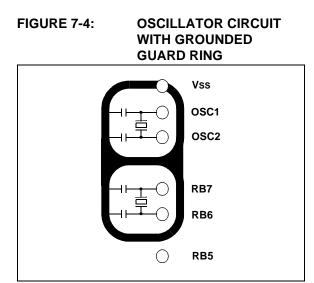

If a high-speed circuit must be located near the oscillator, a grounded guard ring around the oscillator circuit, as shown in Figure 7-4, may be helpful when used on a single-sided PCB or in addition to a ground plane.

| REGISTER 8-1: | T2CON:                                  | TIMER2 CO                                 | ONTROL R        | EGISTER (A     | ADDRESS  | 12h)      |              |         |

|---------------|-----------------------------------------|-------------------------------------------|-----------------|----------------|----------|-----------|--------------|---------|

|               | U-0                                     | R/W-0                                     | R/W-0           | R/W-0          | R/W-0    | R/W-0     | R/W-0        | R/W-0   |

|               |                                         | TOUTPS3                                   | TOUTPS2         | TOUTPS1        | TOUTPS0  | TMR2ON    | T2CKPS1      | T2CKPS0 |

|               | bit 7                                   |                                           |                 |                |          |           |              | bit 0   |

| bit 7         | Unimpler                                | n <b>ented:</b> Rea                       | <b>d as</b> '0' |                |          |           |              |         |

| bit 6-3       | TOUTPS                                  | <b>:3:0&gt;:</b> Timer2                   | 2 Output Pos    | stscale Select | bits     |           |              |         |

|               | 0001 = 1:                               | 1 Postscale<br>2 Postscale<br>3 Postscale |                 |                |          |           |              |         |

|               | •                                       |                                           |                 |                |          |           |              |         |

|               | •                                       |                                           |                 |                |          |           |              |         |

|               | 1111 <b>= 1</b> :                       | 16 Postscale                              |                 |                |          |           |              |         |

| bit 2         | <b>TMR2ON</b><br>1 = Timer<br>0 = Timer |                                           | oit             |                |          |           |              |         |

| bit 1-0       |                                         |                                           | 2 Clock Pres    | cale Select bi | its      |           |              |         |

|               | 00 = Pres<br>01 = Pres                  | caler is 1                                |                 |                |          |           |              |         |

|               | Legend:                                 |                                           |                 |                |          |           |              | ]       |

|               | R = Read                                | lable bit                                 | VV = V          | Writable bit   | U = Unim | plemented | bit, read as | '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|-------------------|------------------|----------------------|--------------------|

|                   |                  |                      |                    |

|                   |                  |                      |                    |

# TABLE 8-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

| Address                 | Name   | Bit 7 | Bit 6                                                 | Bit 5   | Bit 4  | Bit 3 | Bit 2  | Bit 1         | Bit 0  | Value<br>POR, B |     |      | e on<br>other<br>sets |

|-------------------------|--------|-------|-------------------------------------------------------|---------|--------|-------|--------|---------------|--------|-----------------|-----|------|-----------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON | GIE   | PEIE                                                  | TMR0IE  | INTOIE | RBIE  | TMR0IF | <b>INT0IF</b> | RBIF   | 0000 0          | 00x | 0000 | 000u                  |

| 0Ch                     | PIR1   | _     | ADIF <sup>(1)</sup>                                   | RCIF    | TXIF   | SSPIF | CCP1IF | TMR2IF        | TMR1IF | -000 0          | 000 | -000 | 0000                  |

| 8Ch                     | PIE1   | _     | ADIE <sup>(1)</sup>                                   | RCIE    | TXIE   | SSPIE | CCP1IE | TMR2IE        | TMR1IE | -000 0          | 000 | -000 | 0000                  |

| 11h                     | TMR2   | Timer | 2 Module R                                            | egister |        |       |        |               |        | 0000 0          | 000 | 0000 | 0000                  |

| 12h                     | T2CON  | —     | - TOUTPS3 TOUTPS2 TOUTPS1 TOUTPS0 TMR2ON T2CKPS1 T2CK |         |        |       |        |               |        | -000 0          | 000 | -000 | 0000                  |

| 92h                     | PR2    | Timer | 2 Period Re                                           |         | 1111 1 | 111   | 1111   | 1111          |        |                 |     |      |                       |

$\label{eq:logend: Legend: Legend: u = unchanged, - = unimplemented, read as `0'. Shaded cells are not used by the Timer2 module.$

Note 1: This bit is only implemented on the PIC16F88. The bit will read '0' on the PIC16F87.

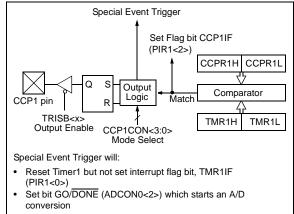

# 9.2 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the CCP1 pin is:

- Driven high

- Driven low

- · Remains unchanged

The action on the pin is based on the value of control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time, interrupt flag bit, CCP1IF, is set.

### FIGURE 9-2: COMPARE MODE OPERATION BLOCK DIAGRAM

#### 9.2.1 CCP PIN CONFIGURATION

The user must configure the CCP1 pin as an output by clearing the TRISB<x> bit.

- Note 1: Clearing the CCP1CON register will force the CCP1 compare output latch to the default low level. This is not the data latch.

- 2: The TRISB bit (0 or 3) is dependent upon the setting of configuration bit 12 (CCPMX).

### 9.2.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 9.2.3 SOFTWARE INTERRUPT MODE

When generate software interrupt is chosen, the CCP1 pin is not affected. Only a CCP interrupt is generated (if enabled).

#### 9.2.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated that may be used to initiate an action.

The special event trigger output of CCP1 resets the TMR1 register pair and starts an A/D conversion (if the A/D module is enabled). This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

Note: The special event trigger from the CCP1 module will not set interrupt flag bit TMR1IF (PIR1<0>).

#### TABLE 9-2: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE AND TIMER1

| Address              | Name    | Bit 7  | Bit 6                                | Bit 5         | Bit 4         | Bit 3       | Bit 2        | Bit 1    | Bit 0  |      | e on<br>BOR | Value on<br>all other<br>Resets |      |

|----------------------|---------|--------|--------------------------------------|---------------|---------------|-------------|--------------|----------|--------|------|-------------|---------------------------------|------|

| 0Bh,8Bh<br>10BH,18Bh | INTCON  | GIE    | PEIE                                 | TMR0IE        | INTOIE        | RBIE        | TMR0IF       | INTOIF   | RBIF   | 0000 | 000x        | 0000                            | 000u |

| 0Ch                  | PIR1    | _      | ADIF <sup>(1)</sup>                  | RCIF          | TXIF          | SSPIF       | CCP1IF       | TMR2IF   | TMR1IF | -000 | 0000        | -000                            | 0000 |

| 8Ch                  | PIE1    | _      | ADIE <sup>(1)</sup>                  | RCIE          | TXIE          | SSPIE       | CCP1IE       | TMR2IE   | TMR1IE | -000 | 0000        | -000                            | 0000 |

| 86h                  | TRISB   | PORT   | B Data Di                            | irection Re   | gister        |             |              |          |        | 1111 | 1111        | 1111                            | 1111 |

| 0Eh                  | TMR1L   | Holdin | g Registe                            | er for the Le | east Signific | ant Byte of | the 16-bit   | TMR1 Reg | gister | xxxx | xxxx        | uuuu                            | uuuu |

| 0Fh                  | TMR1H   | Holdin | g Registe                            | r for the M   | ost Signific  | ant Byte of | the 16-bit 7 | FMR1 Reg | ister  | xxxx | xxxx        | uuuu                            | uuuu |

| 10h                  | T1CON   | —      | T1RUN                                | T1CKPS1       | T1CKPS0       | T1OSCEN     | T1SYNC       | TMR1CS   | TMR1ON | -000 | 0000        | -uuu                            | uuuu |

| 15h                  | CCPR1L  | Captu  | Capture/Compare/PWM Register 1 (LSB) |               |               |             |              |          |        |      | xxxx        | uuuu                            | uuuu |

| 16h                  | CCPR1H  | Captu  | apture/Compare/PWM Register 1 (MSB)  |               |               |             |              |          |        |      | xxxx        | uuuu                            | uuuu |

| 17h                  | CCP1CON |        | —                                    | CCP1X         | CCP1Y         | CCP1M3      | CCP1M2       | CCP1M1   | CCP1M0 | 00   | 0000        | 00                              | 0000 |

**Note 1:** This bit is only implemented on the PIC16F88. The bit will read '0' on the PIC16F87.

| REGISTER 10-2: | SSPCON:                       | SYNCHR                | ONOUS SER                                      | IAL PORT                 | CONTROL         | REGISTE      | R (ADDRE      | SS 14h)      |

|----------------|-------------------------------|-----------------------|------------------------------------------------|--------------------------|-----------------|--------------|---------------|--------------|

|                | R/W-0                         | R/W-0                 | R/W-0                                          | R/W-0                    | R/W-0           | R/W-0        | R/W-0         | R/W-0        |

|                | WCOL                          | SSPOV                 | SSPEN <sup>(1)</sup>                           | CKP                      | SSPM3           | SSPM2        | SSPM1         | SSPM0        |

|                | bit 7                         |                       |                                                |                          |                 |              |               | bit 0        |

| bit 7          | WCOL: W                       | rite Collisior        | Detect bit                                     |                          |                 |              |               |              |

|                |                               |                       | e the SSPBUF                                   | -<br>register fai        | led because     | the SSP m    | odule is bu   | sy           |

|                | (must                         | be cleared            | in software)                                   | C C                      |                 |              |               |              |

|                | 0 = No col                    |                       | <b>a b b c</b>                                 |                          |                 |              |               |              |

| bit 6          | In SPI mod                    |                       | rflow Indicator                                | Dit                      |                 |              |               |              |

|                |                               |                       | eived while the                                | SSPBUF re                | aister is still | holdina the  | previous da   | ata. In case |

|                | of ove                        | rflow, the d          | ata in SSPSR                                   | is lost. Ove             | rflow can or    | ly occur in  | Slave mode    | e. The user  |

|                |                               |                       | PBUF, even if                                  |                          |                 |              |               |              |

|                |                               |                       | w bit is not se<br>SPBUF regist                |                          | i new recep     | uon (and tra | ansmission)   | is initiated |

|                | 0 = No over                   | erflow                | 0                                              |                          |                 |              |               |              |

|                | In I <sup>2</sup> C mod       |                       |                                                |                          |                 | r            |               | 00001/-      |

|                | •                             |                       | while the SSI                                  | •                        |                 | • .          | •             |              |

|                | 0 = No over                   |                       |                                                |                          |                 |              |               |              |

| bit 5          | SSPEN: S                      | ynchronous            | Serial Port Er                                 | nable bit <sup>(1)</sup> |                 |              |               |              |

|                | In SPI mod                    |                       |                                                |                          |                 |              |               |              |

|                |                               |                       | t and configure<br>rt and configur             |                          |                 |              | t pins        |              |

|                | In I <sup>2</sup> C mod       | -                     | it and coningui                                | es triese pir            | 13 a3 1/0 p01   | t pins       |               |              |

|                | 1 = Enable                    | es the serial         | port and confi                                 |                          |                 |              | rial port pin | 5            |

|                |                               | -                     | rt and configur                                |                          |                 | -            |               |              |

|                | Note 1:                       | In both mo<br>output. | odes, when en                                  | abled, these             | e pins must l   | be properly  | configured    | as input or  |

| bit 4          |                               | k Polarity S          | elect bit                                      |                          |                 |              |               |              |

|                | In SPI mod                    |                       | on falling edge                                | , receive or             | ricing odgo     | Idlo ototo f | or clock is c | high loval   |

|                |                               |                       | on rising edge                                 |                          |                 |              |               |              |

|                | <u>In I<sup>2</sup>C Slav</u> | <u>e mode:</u>        |                                                |                          |                 |              |               |              |

|                | SCK release                   |                       |                                                |                          |                 |              |               |              |

|                | 1 = Enable<br>0 = Holds (     |                       | lock stretch). (                               | Used to ens              | sure data set   | up time.)    |               |              |

| bit 3-0        | SSPM<3:0                      | >: Synchro            | nous Serial Po                                 | ort Mode Se              | lect bits       | . ,          |               |              |

|                |                               |                       | ode, clock = O                                 |                          |                 |              |               |              |

|                |                               |                       | ode, clock = O<br>ode, clock = O               |                          |                 |              |               |              |

|                |                               |                       | ode, clock = O<br>ode, clock = Tl              |                          | 2               |              |               |              |

|                | 0100 = SP                     | I Slave mo            | de, clock = SC                                 | K pin. SS pi             | in control en   |              |               |              |

|                |                               |                       | de, clock = SC<br>le, 7-bit addre              |                          | n control dis   | abled. SS c  | an be used    | as I/O pin.  |

|                |                               |                       | de, 7-bit addres                               |                          |                 |              |               |              |

|                | $1011 = I^2C$                 | Firmware              | Controlled Ma                                  | ster mode (              |                 |              |               |              |

|                |                               |                       | le, 7-bit addres                               |                          |                 |              |               |              |

|                |                               |                       | <b>le, 10-bit addr</b><br>L00, 1101 <b>=</b> R |                          | n anu stop i    |              |               |              |

|                |                               | ,, .                  | .,                                             |                          |                 |              |               |              |

|                | Legend:                       |                       |                                                |                          |                 |              |               |              |

|                | R = Reada                     | ble bit               | W = W                                          | ritable bit              | U = Unim        | plemented    | bit, read as  | '0'          |

| Legena.           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| BAUD        | I      | Fosc = 8 M | Hz                          | Fosc = 4 MHz |            |                             |        | Fosc = 2 M | Hz                          |       | Fosc = 1 MHz |                             |  |  |

|-------------|--------|------------|-----------------------------|--------------|------------|-----------------------------|--------|------------|-----------------------------|-------|--------------|-----------------------------|--|--|

| RATE<br>(K) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD        | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD | %<br>ERROR   | SPBRG<br>value<br>(decimal) |  |  |

| 0.3         | NA     | _          | _                           | 0.300        | 0          | 207                         | 0.300  | 0          | 103                         | 0.300 | 0            | 51                          |  |  |

| 1.2         | 1.202  | +0.16      | 103                         | 1.202        | +0.16      | 51                          | 1.202  | +0.16      | 25                          | 1.202 | +0.16        | 12                          |  |  |

| 2.4         | 2.404  | +0.16      | 51                          | 2.404        | +0.16      | 25                          | 2.404  | +0.16      | 12                          | 2.232 | -6.99        | 6                           |  |  |

| 9.6         | 9.615  | +0.16      | 12                          | 8.929        | -6.99      | 6                           | 10.417 | +8.51      | 2                           | NA    | _            | _                           |  |  |

| 19.2        | 17.857 | -6.99      | 6                           | 20.833       | +8.51      | 2                           | NA     | _          | _                           | NA    | _            | _                           |  |  |

| 28.8        | 31.250 | +8.51      | 3                           | 31.250       | +8.51      | 1                           | 31.250 | +8.51      | 0                           | NA    | _            | _                           |  |  |

| 38.4        | 41.667 | +8.51      | 2                           | NA           | _          | _                           | NA     | _          | _                           | NA    | _            | _                           |  |  |

| 57.6        | 62.500 | +8.51      | 1                           | 62.500       | 8.51       | 0                           | NA     | _          | _                           | NA    | _            | _                           |  |  |

# TABLE 11-5: INTRC BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 0)

# TABLE 11-6:INTRC BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 1)

| BAUD        | Fosc = 8 MHz |            |                             | Fosc = 4 MHz |            |                             |        | Fosc = 2 M | Hz                          |        | Fosc = 1 MHz |                             |  |  |

|-------------|--------------|------------|-----------------------------|--------------|------------|-----------------------------|--------|------------|-----------------------------|--------|--------------|-----------------------------|--|--|

| RATE<br>(K) | KBAUD        | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD        | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR   | SPBRG<br>value<br>(decimal) |  |  |

| 0.3         | NA           | _          | _                           | NA           | _          | _                           | NA     | _          | _                           | 0.300  | 0            | 207                         |  |  |

| 1.2         | NA           | _          | —                           | 1.202        | +0.16      | 207                         | 1.202  | +0.16      | 103                         | 1.202  | +0.16        | 51                          |  |  |

| 2.4         | 2.404        | +0.16      | 207                         | 2.404        | +0.16      | 103                         | 2.404  | +0.16      | 51                          | 2.404  | +0.16        | 25                          |  |  |

| 9.6         | 9.615        | +0.16      | 51                          | 9.615        | +0.16      | 25                          | 9.615  | +0.16      | 12                          | 8.929  | -6.99        | 6                           |  |  |

| 19.2        | 19.231       | +0.16      | 25                          | 19.231       | +0.16      | 12                          | 17.857 | -6.99      | 6                           | 20.833 | +8.51        | 2                           |  |  |

| 28.8        | 29.412       | +2.12      | 16                          | 27.778       | -3.55      | 8                           | 31.250 | +8.51      | 3                           | 31.250 | +8.51        | 1                           |  |  |

| 38.4        | 38.462       | +0.16      | 12                          | 35.714       | -6.99      | 6                           | 41.667 | +8.51      | 2                           | NA     | _            | _                           |  |  |

| 57.6        | 55.556       | -3.55      | 8                           | 62.500       | +8.51      | 3                           | 62.500 | +8.51      | 1                           | 62.500 | +8.51        | 0                           |  |  |

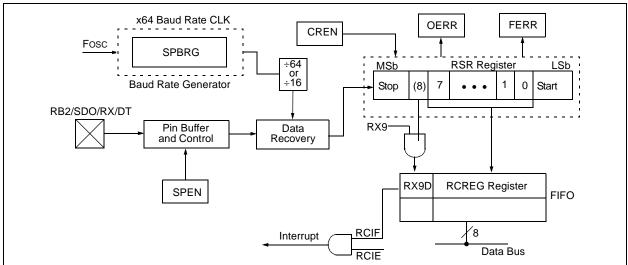

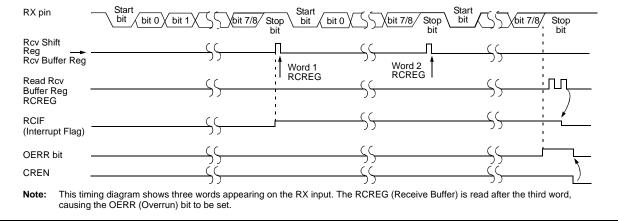

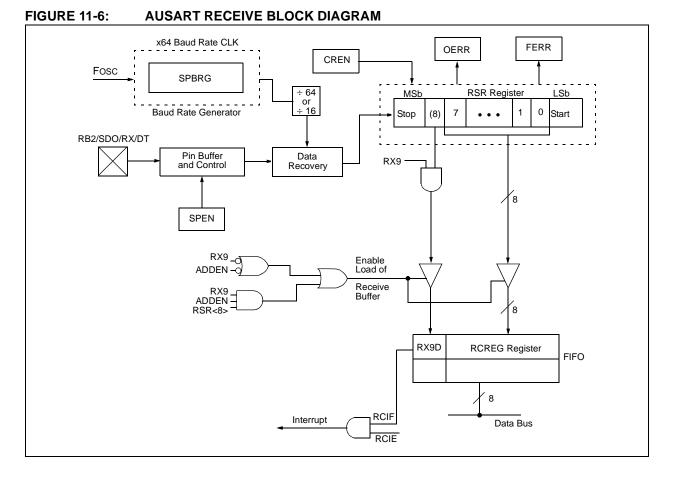

#### 11.2.2 AUSART ASYNCHRONOUS RECEIVER

The receiver block diagram is shown in Figure 11-4. The data is received on the RB2/SDO/RX/DT pin and drives the data recovery block. The data recovery block is actually a high-speed shifter, operating at x16 times the baud rate; whereas, the main receive serial shifter operates at the bit rate or at Fosc.

Once Asynchronous mode is selected, reception is enabled by setting bit CREN (RCSTA<4>).

The heart of the receiver is the Receive (Serial) Shift Register (RSR). After sampling the Stop bit, the received data in the RSR is transferred to the RCREG register (if it is empty). If the transfer is complete, flag bit, RCIF (PIR1<5>), is set. The actual interrupt can be enabled/disabled by setting/clearing enable bit RCIE (PIE1<5>). Flag bit RCIF is a read-only bit which is cleared by the hardware. It is cleared when the RCREG register has been read and is empty. The RCREG is a double-buffered register (i.e., it is a two-deep FIFO). It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting to the RSR register. On the detection of the Stop bit of the third byte, if the RCREG register is still full, the Overrun Error bit, OERR (RCSTA<1>), will be set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Overrun bit OERR has to be cleared in software. This is done by resetting the receive logic (CREN is cleared and then set). If bit OERR is set, transfers from the RSR register to the RCREG register are inhibited and no further data will be received. It is, therefore, essential to clear error bit OERR if it is set. Framing Error bit, FERR (RCSTA<2>), is set if a Stop bit is detected as clear. Bit FERR and the 9th receive bit are buffered the same way as the receive data. Reading the RCREG will load bits RX9D and FERR with new values: therefore, it is essential for the user to read the RCSTA register, before reading the RCREG register, in order not to lose the old FERR and RX9D information.

# 11.2.3 SETTING UP 9-BIT MODE WITH ADDRESS DETECT

When setting up an asynchronous reception with address detect enabled:

- Initialize the SPBRG register for the appropriate baud rate. If a high-speed baud rate is desired, set bit BRGH.

- Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- If interrupts are desired, then set enable bit RCIE.

- Set bit RX9 to enable 9-bit reception.

- Set ADDEN to enable address detect.

- Enable the reception by setting enable bit CREN.

- Flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit and determine if any error occurred during reception.

- Read the 8-bit received data by reading the RCREG register to determine if the device is being addressed.

- If any error occurred, clear the error by clearing enable bit CREN.

- If the device has been addressed, clear the ADDEN bit to allow data bytes and address bytes to be read into the receive buffer and interrupt the CPU.

### 13.7 Comparator Operation During Sleep

When a comparator is active and the device is placed in Sleep mode, the comparator remains active and the interrupt is functional, if enabled. This interrupt will wake-up the device from Sleep mode when enabled. While the comparator is powered up, higher Sleep currents than shown in the power-down current specification will occur. Each operational comparator will consume additional current, as shown in the comparator specifications. To minimize power consumption while in Sleep mode, turn off the comparators, CM<2:0> = 111, before entering Sleep. If the device wakes up from Sleep, the contents of the CMCON register are not affected.

# 13.8 Effects of a Reset

A device Reset forces the CMCON register to its Reset state, causing the comparator module to be in the Comparator Off mode, CM<2:0> = 111.

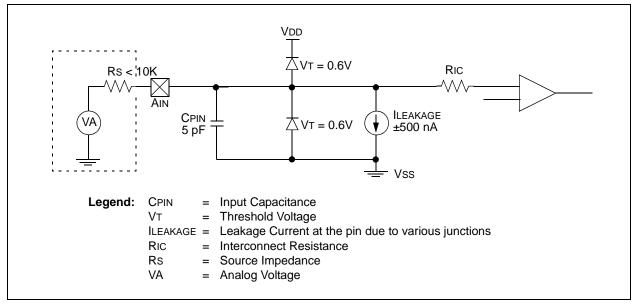

### 13.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 13-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up condition may occur. A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

#### FIGURE 13-4: ANALOG INPUT MODEL

| Address                 | Name                              | Bit 7  | Bit 6  | Bit 5                 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR        | Value on<br>all other<br>Resets |

|-------------------------|-----------------------------------|--------|--------|-----------------------|--------|--------|--------|--------|--------|------------------------|---------------------------------|

| 9Ch                     | CMCON                             | C2OUT  | C10UT  | C2INV                 | C1INV  | CIS    | CM2    | CM1    | CM0    | 0000 0111              | 0000 0111                       |

| 9Dh                     | CVRCON                            | CVREN  | CVROE  | CVRR                  | —      | CVR3   | CVR2   | CVR1   | CVR0   | 000- 0000              | 000- 0000                       |

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON                            | GIE    | PEIE   | TMR0IE                | INTOIE | RBIE   | TMR0IF | INTOIF | RBIF   | 0000 000x              | 0000 000u                       |

| 0Dh                     | PIR2                              | OSFIF  | CMIF   | _                     | EEIF   | —      | —      | —      | —      | 00-0                   | 00-0                            |

| 8Dh                     | PIE2                              | OSFIE  | CMIE   | _                     | EEIE   | —      | _      | _      | _      | 00-0                   | 00-0                            |

| 05h                     | PORTA<br>(PIC16F87)<br>(PIC16F88) |        | RA6    | RA5                   | RA4    | RA3    | RA2    | RA1    | RA0    | xxxx 0000<br>xxx0 0000 | uuuu 0000<br>uuu0 0000          |

| 85h                     | TRISA                             | TRISA7 | TRISA6 | TRISA5 <sup>(1)</sup> | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1111 1111              | 1111 1111                       |

#### TABLE 13-1: REGISTERS ASSOCIATED WITH THE COMPARATOR MODULE

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the comparator module.

Note 1: Pin 5 is an input only; the state of the TRISA5 bit has no effect and will always read '1'.

# 18.1 DC Characteristics: Supply Voltage PIC16F87/88 (Industrial, Extended) PIC16LF87/88 (Industrial)

| PIC16LF87/88<br>(Industrial) |                       |                                                                     |      | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial                                                                                                                                    |      |       |                                                        |  |  |  |

|------------------------------|-----------------------|---------------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------------------------------------------------------|--|--|--|

| PIC16F87/88                  |                       |                                                                     |      | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \\ \mbox{-}40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for extended} \end{array}$ |      |       |                                                        |  |  |  |

| Param<br>No.                 | Symbol Characteristic |                                                                     |      | Тур                                                                                                                                                                                                                                                                   | Max  | Units | Conditions                                             |  |  |  |

|                              | Vdd                   | Supply Voltage                                                      |      |                                                                                                                                                                                                                                                                       |      |       |                                                        |  |  |  |

| D001                         |                       | PIC16LF87/88                                                        | 2.0  | _                                                                                                                                                                                                                                                                     | 5.5  | V     | HS, XT, RC and LP Oscillator mode                      |  |  |  |

| D001                         |                       | PIC16F87/88                                                         | 4.0  |                                                                                                                                                                                                                                                                       | 5.5  | V     |                                                        |  |  |  |

| D002                         | Vdr                   | RAM Data Retention<br>Voltage <sup>(1)</sup>                        | 1.5  | —                                                                                                                                                                                                                                                                     | —    | V     |                                                        |  |  |  |

| D003                         | VPOR                  | VDD Start Voltage<br>to ensure internal<br>Power-on Reset signal    | _    | _                                                                                                                                                                                                                                                                     | 0.7  | V     | See Section 15.4 "Power-on Reset (POR)"<br>for details |  |  |  |

| D004                         | SVDD                  | <b>VDD Rise Rate</b><br>to ensure internal<br>Power-on Reset signal | 0.05 | _                                                                                                                                                                                                                                                                     | —    | V/ms  | See Section 15.4 "Power-on Reset (POR)"<br>for details |  |  |  |

|                              | VBOR                  | Brown-out Reset Voltage                                             |      | •                                                                                                                                                                                                                                                                     |      | •     |                                                        |  |  |  |

| D005                         |                       | PIC16LF87/88                                                        | 3.65 |                                                                                                                                                                                                                                                                       | 4.35 | V     |                                                        |  |  |  |

| D005                         |                       | PIC16F87/88                                                         | 3.65 |                                                                                                                                                                                                                                                                       | 4.35 | V     | Fmax = 14 MHz <sup>(2)</sup>                           |  |  |  |

**Legend:** Shading of rows is to assist in readability of the table.

Note 1: This is the limit to which VDD can be lowered in Sleep mode, or during a device Reset, without losing RAM data.

2: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

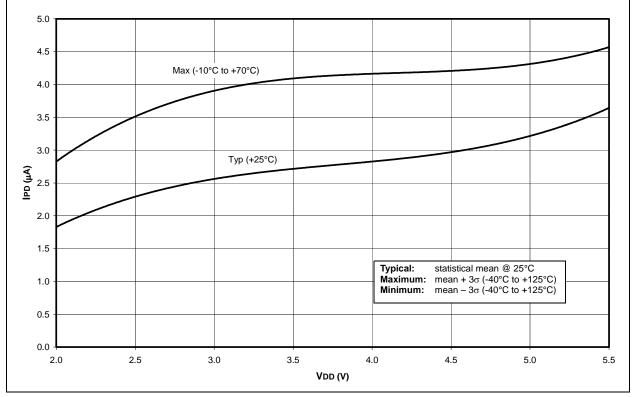

# 18.2 DC Characteristics: Power-Down and Supply Current PIC16F87/88 (Industrial, Extended) PIC16LF87/88 (Industrial)

| PIC16LF8<br>(Indus | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |                                                                                                                                                                                         |       |            |        |                          |  |  |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|--------|--------------------------|--|--|--|

| PIC16F87<br>(Indus |                                                                                                                                    | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |       |            |        |                          |  |  |  |

| Param<br>No.       | Тур                                                                                                                                | Max                                                                                                                                                                                     | Units | Conditions |        |                          |  |  |  |

|                    | Power-Down Current (IPD)                                                                                                           | (1)                                                                                                                                                                                     |       |            |        |                          |  |  |  |

|                    | PIC16LF87/88                                                                                                                       | 0.1                                                                                                                                                                                     | 0.4   | μΑ         | -40°C  | VDD = 2.0V<br>VDD = 3.0V |  |  |  |

|                    |                                                                                                                                    | 0.1                                                                                                                                                                                     | 0.4   | μΑ         | +25°C  |                          |  |  |  |

|                    |                                                                                                                                    | 0.4                                                                                                                                                                                     | 1.5   | μΑ         | +85°C  |                          |  |  |  |

|                    | PIC16LF87/88                                                                                                                       | 0.3                                                                                                                                                                                     | 0.5   | μΑ         | -40°C  |                          |  |  |  |

|                    |                                                                                                                                    | 0.3                                                                                                                                                                                     | 0.5   | μΑ         | +25°C  |                          |  |  |  |

|                    |                                                                                                                                    | 0.7                                                                                                                                                                                     | 1.7   | μΑ         | +85°C  |                          |  |  |  |

|                    | All devices                                                                                                                        | 0.6                                                                                                                                                                                     | 1.0   | μΑ         | -40°C  | VDD = 5.0V               |  |  |  |

|                    |                                                                                                                                    | 0.6                                                                                                                                                                                     | 1.0   | μΑ         | +25°C  |                          |  |  |  |

|                    |                                                                                                                                    | 1.2                                                                                                                                                                                     | 5.0   | μΑ         | +85°C  | vuu ≅ 5.0v               |  |  |  |

|                    | Extended devices                                                                                                                   | 6                                                                                                                                                                                       | 28    | μΑ         | +125°C |                          |  |  |  |

Legend: Shading of rows is to assist in readability of the table.

**Note 1:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or VSs and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

- OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;

- $\overline{\text{MCLR}}$  = VDD; WDT enabled/disabled as specified.

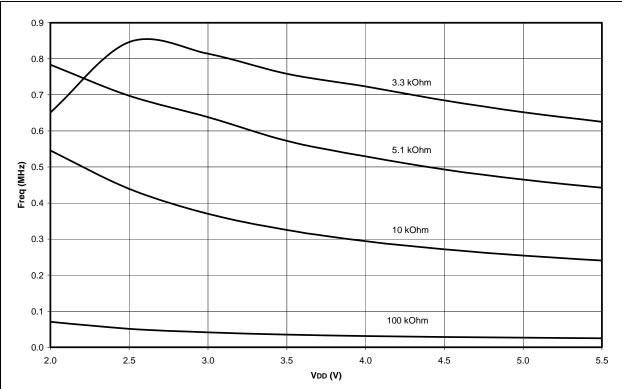

- 3: For RC oscillator configurations, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

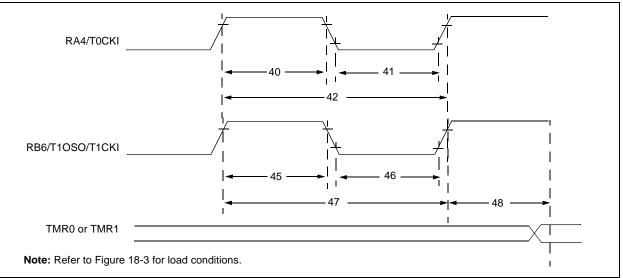

#### **FIGURE 18-8:** TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

| TABLE 18-6: | TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS |

|-------------|-----------------------------------------------|

|-------------|-----------------------------------------------|

| Param<br>No. | Symbol    |                                   | Characteristic                      |                       | Min                                       | Тур† | Мах    | Units | Conditions                         |  |

|--------------|-----------|-----------------------------------|-------------------------------------|-----------------------|-------------------------------------------|------|--------|-------|------------------------------------|--|

| 40*          | Tt0H      | T0CKI High P                      | ulse Width                          | No Prescaler          | 0.5 TCY + 20                              |      | —      | ns    | Must also meet                     |  |

|              |           |                                   |                                     | With Prescaler        | 10                                        | _    | —      | ns    | parameter 42                       |  |

| 41*          | Tt0L      | T0CKI Low Pu                      | Ilse Width                          | No Prescaler          | 0.5 TCY + 20                              | _    | —      | ns    | Must also meet<br>parameter 42     |  |

|              |           |                                   |                                     | With Prescaler        | 10                                        |      | _      | ns    |                                    |  |

| 42*          | Tt0P      | T0CKI Period                      |                                     | No Prescaler          | Tcy + 40                                  |      | _      | ns    |                                    |  |

|              |           |                                   |                                     | With Prescaler        | Greater of:<br>20 or <u>Tcy + 40</u><br>N |      |        | ns    | N = prescale value<br>(2, 4,, 256) |  |

| 45*          | Tt1H      | T1CKI High                        | Synchronous, Prescaler = 1          |                       | 0.5 TCY + 20                              | _    | —      | ns    | Must also meet                     |  |

|              |           | Time                              | Synchronous,                        | PIC16 <b>F</b> 87/88  | 15                                        | _    | —      | ns    | parameter 47                       |  |

|              |           |                                   | Prescaler = 2, 4, 8                 | PIC16 <b>LF</b> 87/88 | 25                                        |      | _      | ns    |                                    |  |

|              |           |                                   | Asynchronous                        | PIC16 <b>F</b> 87/88  | 30                                        |      | _      | ns    |                                    |  |

|              |           |                                   |                                     | PIC16 <b>LF</b> 87/88 | 50                                        |      | _      | ns    |                                    |  |

| 46*          | Tt1L      | T1CKI Low<br>Time                 | Synchronous, Pres                   | scaler = 1            | 0.5 TCY + 20                              |      | _      | ns    | Must also meet<br>parameter 47     |  |

|              |           |                                   | Synchronous,<br>Prescaler = 2, 4, 8 | PIC16 <b>F</b> 87/88  | 15                                        | _    | —      | ns    |                                    |  |

|              |           |                                   |                                     | PIC16 <b>LF</b> 87/88 | 25                                        | _    | —      | ns    |                                    |  |

|              |           |                                   | Asynchronous                        | PIC16 <b>F</b> 87/88  | 30                                        | _    | —      | ns    |                                    |  |

|              |           |                                   |                                     | PIC16 <b>LF</b> 87/88 | 50                                        | _    | —      | ns    |                                    |  |

| 47* Tt1P     | Tt1P      | T1CKI Input<br>Period             | Synchronous                         | PIC16 <b>F</b> 87/88  | Greater of:<br>30 or <u>Tcy + 40</u><br>N | _    | _      | ns    | N = prescale value<br>(1, 2, 4, 8) |  |

|              |           |                                   |                                     | PIC16 <b>LF</b> 87/88 | Greater of:<br>50 or <u>Tcy + 40</u><br>N |      |        |       | N = prescale value<br>(1, 2, 4, 8) |  |

|              |           |                                   | Asynchronous                        | PIC16 <b>F</b> 87/88  | 60                                        |      | _      | ns    |                                    |  |

|              |           |                                   |                                     | PIC16 <b>LF</b> 87/88 | 100                                       |      | _      | ns    |                                    |  |

|              | Ft1       | Timer1 Oscilla<br>(Oscillator ena | DC                                  |                       | 32.768                                    | kHz  |        |       |                                    |  |

| 48           | TCKEZtmr1 | Delay from Ext                    | ernal Clock Edge to                 | Timer Increment       | 2 Tosc                                    | _    | 7 Tosc | _     |                                    |  |

t Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

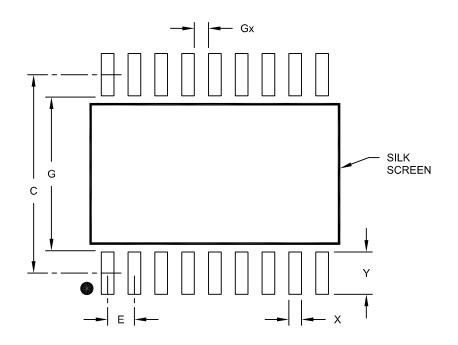

18-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

|                       | Units  | MILLIMETERS |      |      |  |  |

|-----------------------|--------|-------------|------|------|--|--|

| Dimension             | Limits | MIN         | NOM  | MAX  |  |  |

| Contact Pitch         | E      | 1.27 BSC    |      |      |  |  |

| Contact Pad Spacing   | С      |             | 9.40 |      |  |  |

| Contact Pad Width     | Х      |             |      | 0.60 |  |  |

| Contact Pad Length    | Y      |             |      | 2.00 |  |  |

| Distance Between Pads | Gx     | 0.67        |      |      |  |  |

| Distance Between Pads | G      | 7.40        |      |      |  |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2051A

NOTES: