Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 16                                                                      |

| Program Memory Size        | 7KB (4K x 14)                                                           |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 256 x 8                                                                 |

| RAM Size                   | 368 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                               |

| Data Converters            | A/D 7x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                          |

| Supplier Device Package    | 18-SOIC                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f88-i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| Address              | Name                  | Bit 7       | Bit 6                      | Bit 5                     | Bit 4         | Bit 3          | Bit 2           | Bit 1        | Bit 0    | Value on:<br>POR, BOR | Details<br>on<br>page |

|----------------------|-----------------------|-------------|----------------------------|---------------------------|---------------|----------------|-----------------|--------------|----------|-----------------------|-----------------------|

| Bank 1               |                       |             |                            |                           |               |                |                 |              |          |                       |                       |

| 80h <sup>(2)</sup>   | INDF                  | Addressin   | g this locatio             | n uses conte              | nts of FSR to | address data   | memory (not     | a physical r | egister) | 0000 0000             | 26, 135               |

| 81h                  | OPTION_REG            | RBPU        | INTEDG                     | T0CS                      | T0SE          | PSA            | PS2             | PS1          | PS0      | 1111 1111             | 18, 69                |

| 82h <sup>(2)</sup>   | PCL                   | Program C   | Counter (PC)               | Least Signif              | icant Byte    |                |                 |              |          | 0000 0000             | 135                   |

| 83h <sup>(2)</sup>   | STATUS                | IRP         | RP1                        | RP0                       | TO            | PD             | Z               | DC           | С        | 0001 1xxx             | 17                    |

| 84h <sup>(2)</sup>   | FSR                   | Indirect Da | ata Memory /               | Address Poir              | iter          |                |                 |              |          | xxxx xxxx             | 135                   |

| 85h                  | TRISA                 | TRISA7      | TRISA6                     | TRISA5 <sup>(3)</sup>     | PORTA Data    | a Direction Re | gister (TRISA   | <4:0>)       |          | 1111 1111             | 52, 126               |

| 86h                  | TRISB                 | PORTB D     | ata Direction              | Register                  |               |                |                 |              |          | 1111 1111             | 58, 85                |

| 87h                  | _                     | Unimplem    | ented                      |                           |               |                |                 |              |          | _                     | _                     |

| 88h                  | _                     | Unimplem    | ented                      |                           |               |                |                 |              |          | _                     | _                     |

| 89h                  | _                     | Unimplem    | ented                      |                           |               |                |                 |              |          | _                     | _                     |

| 8Ah <sup>(1,2)</sup> | PCLATH                | _           | _                          | _                         | Write Buffer  | for the Upper  | 5 bits of the F | Program Cou  | unter    | 0 0000                | 135                   |

| 8Bh <sup>(2)</sup>   | INTCON                | GIE         | PEIE                       | TMR0IE                    | INT0IE        | RBIE           | TMR0IF          | INT0IF       | RBIF     | 0000 000x             | 19, 69,<br>77         |

| 8Ch                  | PIE1                  | _           | ADIE <sup>(4)</sup>        | RCIE                      | TXIE          | SSPIE          | CCP1IE          | TMR2IE       | TMR1IE   | -000 0000             | 20, 80                |

| 8Dh                  | PIE2                  | OSFIE       | CMIE                       | _                         | EEIE          | _              | _               | _            | _        | 00-0                  | 22, 34                |

| 8Eh                  | PCON                  | _           | _                          | _                         | _             | _              | _               | POR          | BOR      | 0q                    | 24                    |

| 8Fh                  | OSCCON                | _           | IRCF2                      | IRCF1                     | IRCF0         | OSTS           | IOFS            | SCS1         | SCS0     | -000 0000             | 40                    |

| 90h                  | OSCTUNE               | _           | _                          | TUN5                      | TUN4          | TUN3           | TUN2            | TUN1         | TUN0     | 00 0000               | 38                    |

| 91h                  | _                     | Unimplem    | ented                      |                           |               |                |                 |              |          | _                     | _                     |

| 92h                  | PR2                   | Timer2 Pe   | riod Registe               | Ī                         |               |                |                 |              |          | 1111 1111             | 80, 85                |

| 93h                  | SSPADD                | Synchrono   | ous Serial Po              | ort (I <sup>2</sup> C™ mo | de) Address F | Register       |                 |              |          | 0000 0000             | 95                    |

| 94h                  | SSPSTAT               | SMP         | CKE                        | D/Ā                       | Р             | S              | R/W             | UA           | BF       | 0000 0000             | 88, 95                |

| 95h                  | 1                     | Unimplem    | ented                      |                           |               |                |                 |              |          | _                     |                       |

| 96h                  | _                     | Unimplem    | ented                      |                           |               |                |                 |              |          | _                     | _                     |

| 97h                  | _                     | Unimplem    | ented                      |                           |               |                |                 |              |          | _                     | _                     |

| 98h                  | TXSTA                 | CSRC        | TX9                        | TXEN                      | SYNC          | _              | BRGH            | TRMT         | TX9D     | 0000 -010             | 97, 99                |

| 99h                  | SPBRG                 | Baud Rate   | Generator F                | Register                  |               |                |                 |              |          | 0000 0000             | 99, 103               |

| 9Ah                  | 1                     | Unimplem    | ented                      |                           |               |                |                 |              |          | _                     |                       |

| 9Bh                  | ANSEL <sup>(4)</sup>  | _           | ANS6                       | ANS5                      | ANS4          | ANS3           | ANS2            | ANS1         | ANS0     | -111 1111             | 120                   |

| 9Ch                  | CMCON                 | C2OUT       | C1OUT                      | C2INV                     | C1INV         | CIS            | CM2             | CM1          | CM0      | 0000 0111             | 121,<br>126, 128      |

| 9Dh                  | CVRCON                | CVREN       | CVROE                      | CVRR                      | _             | CVR3           | CVR2            | CVR1         | CVR0     | 000- 0000             | 126, 128              |

| 9Eh                  | ADRESL <sup>(4)</sup> | A/D Resul   | D Result Register Low Byte |                           |               |                |                 |              |          | xxxx xxxx             | 120                   |

| 9Fh                  | ADCON1 <sup>(4)</sup> | ADFM        | ADCS2                      | VCFG1                     | VCFG0         | _              | _               | _            | _        | 0000                  | 52, 115,<br>120       |

$\begin{array}{ll} \textbf{Legend:} & \text{$\mathbf{x}$ = unknown, $\mathbf{u}$ = unchanged, $\mathbf{q}$ = value depends on condition, $\mathbf{r}$ = unimplemented, read as '0', $\mathbf{r}$ = reserved.} \\ & \textbf{Shaded locations are unimplemented, read as '0'.} \end{array}$

**Note** 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for PC<12:8>, whose contents are transferred to the upper byte of the program counter.

- 2: These registers can be addressed from any bank.

- 3: RA5 is an input only; the state of the TRISA5 bit has no effect and will always read '1'.

- 4: PIC16F88 device only.

### 2.2.2.7 PIR2 Register

The PIR2 register contains the flag bit for the EEPROM write operation interrupt.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit, or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

### REGISTER 2-7: PIR2: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 2 (ADDRESS 0Dh)

| R/W-0 | R/W-0 | U-0 | R/W-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|-----|-------|-----|-----|-----|-------|

| OSFIF | CMIF  | _   | EEIF  | _   | _   | _   | _     |

| bit 7 |       |     |       |     |     |     | bit 0 |

bit 7 OSFIF: Oscillator Fail Interrupt Flag bit

1 = System oscillator failed, clock input has changed to INTRC (must be cleared in software)

0 = System clock operating

bit 6 **CMIF:** Comparator Interrupt Flag bit

1 = Comparator input has changed (must be cleared in software)

0 = Comparator input has not changed

bit 5 Unimplemented: Read as '0'

bit 4 **EEIF:** EEPROM Write Operation Interrupt Flag bit

1 = The write operation completed (must be cleared in software)

0 = The write operation is not complete or has not been started

bit 3-0 Unimplemented: Read as '0'

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

## 3.5 Reading Flash Program Memory

To read a program memory location, the user must write two bytes of the address to the EEADR and EEADRH registers, set the EEPGD control bit (EECON1<7>) and then set control bit RD (EECON1<0>). Once the read control bit is set, the program memory Flash controller will use the second instruction cycle to read the data. This causes the second instruction immediately following the "BSF EECON1, RD" instruction to be ignored. The data is available in the very next cycle in the EEDATA and EEDATH registers; therefore, it can be read as two bytes in the following instructions. EEDATA and EEDATH registers will hold this value until another read or until it is written to by the user (during a write operation).

#### **EXAMPLE 3-3:** FLASH PROGRAM READ

```

; Select Bank of EEADRH

BANKSEL EEADRH

MOVF

ADDRH, W

MOVWF

EEADRH

; MS Byte of Program

; Address to read

MOVF

ADDRL, W

; LS Byte of Program

MOVWF

EEADR

; Address to read

; Select Bank of EECON1

BANKSEL EECON1

BSF

EECON1, EEPGD; Point to PROGRAM

; memory

; EE Read

BSF

EECON1, RD

MOP

; Any instructions

; here are ignored as

NOP

; program memory is

; read in second cycle

; after BSF EECON1,RD

; Select Bank of EEDATA

BANKSEL EEDATA

MOVF

EEDATA, W

; DATAL = EEDATA

MOVWF

DATAL

; DATAH = EEDATH

MOVF

EEDATH, W

MOVWF

DATAH

```

## 3.6 Erasing Flash Program Memory

The minimum erase block is 32 words. Only through the use of an external programmer, or through ICSP control, can larger blocks of program memory be bulk erased. Word erase in the Flash array is not supported.

When initiating an erase sequence from the micro-controller itself, a block of 32 words of program memory is erased. The Most Significant 11 bits of the EEADRH:EEADR point to the block being erased. EEADR< 4:0> are ignored.

The EECON1 register commands the erase operation. The EEPGD bit must be set to point to the Flash program memory. The WREN bit must be set to enable write operations. The FREE bit is set to select an erase operation.

For protection, the write initiate sequence for EECON2 must be used.

After the "BSF EECON1, WR" instruction, the processor requires two cycles to setup the erase operation. The user must place two NOP instructions after the WR bit is set. The processor will halt internal operations for the typical 2 ms, only during the cycle in which the erase takes place. This is not Sleep mode, as the clocks and peripherals will continue to run. After the erase cycle, the processor will resume operation with the third instruction after the EECON1 write instruction.

## 3.6.1 FLASH PROGRAM MEMORY ERASE SEQUENCE

The sequence of events for erasing a block of internal program memory location is:

- Load EEADRH:EEADR with address of row being erased.

- Set EEPGD bit to point to program memory, set WREN bit to enable writes and set FREE bit to enable the erase.

- 3. Disable interrupts.

- 4. Write 55h to EECON2.

- 5. Write AAh to EECON2.

- Set the WR bit. This will begin the row erase cycle.

- The CPU will stall for duration of the erase.

## 3.8 Protection Against Spurious Write

There are conditions when the device should not write to the data EEPROM memory. To protect against spurious EEPROM writes, various mechanisms have been built-in. On power-up, WREN is cleared. Also, the Power-up Timer (72 ms duration) prevents an EEPROM write.

The write initiate sequence and the WREN bit together help prevent an accidental write during brown-out, power glitch or software malfunction.

## 3.9 Operation During Code-Protect

When the data EEPROM is code-protected, the microcontroller can read and write to the EEPROM normally. However, all external access to the EEPROM is disabled. External write access to the program memory is also disabled.

When program memory is code-protected, the micro-controller can read and write to program memory normally, as well as execute instructions. Writes by the device may be selectively inhibited to regions of the memory depending on the setting of bits WRT1:WRT0 of the Configuration Word (see Section 15.1 "Configuration Bits" for additional information). External access to the memory is also disabled.

TABLE 3-1: REGISTERS/BITS ASSOCIATED WITH DATA EEPROM AND FLASH PROGRAM MEMORIES

| Address | Name   | Bit 7  | Bit 6     | Bit 5      | Bit 4                               | Bit 3        | Bit 2       | Bit 1        | Bit 0     | Value on<br>Power-on<br>Reset | Value on<br>all other<br>Resets |

|---------|--------|--------|-----------|------------|-------------------------------------|--------------|-------------|--------------|-----------|-------------------------------|---------------------------------|

| 10Ch    | EEDATA | EEPROM | 1/Flash D | ata Regist | er Low E                            | Byte         |             |              |           | xxxx xxxx                     | uuuu uuuu                       |

| 10Dh    | EEADR  | EEPROM | 1/Flash A | ddress Re  | gister Lo                           | w Byte       |             |              |           | xxxx xxxx                     | uuuu uuuu                       |

| 10Eh    | EEDATH | _      | _         | EEPROM/    | EPROM/Flash Data Register High Byte |              |             |              |           | xx xxxx                       | uu uuuu                         |

| 10Fh    | EEADRH | _      | _         | _          | _                                   | EEPROM/      | Flash Addre | ess Register | High Byte | xxxx                          | uuuu                            |

| 18Ch    | EECON1 | EEPGD  | _         | _          | FREE                                | WRERR        | WREN        | WR           | RD        | xx x000                       | xx q000                         |

| 18Dh    | EECON2 | EEPROM | 1 Control | Register 2 | (not a p                            | hysical regi | ster)       |              |           |                               |                                 |

| 0Dh     | PIR2   | OSFIF  | CMIF      | _          | EEIF                                | _            | _           | _            | _         | 00-0                          | 00-0                            |

| 8Dh     | PIE2   | OSFIE  | CMIE      | _          | EEIE                                | _            | _           | _            | _         | 00-0                          | 00-0                            |

**Legend:** x = unknown, u = unchanged, - = unimplemented, read as '0', q = value depends upon condition. Shaded cells are not used by data EEPROM or Flash program memory.

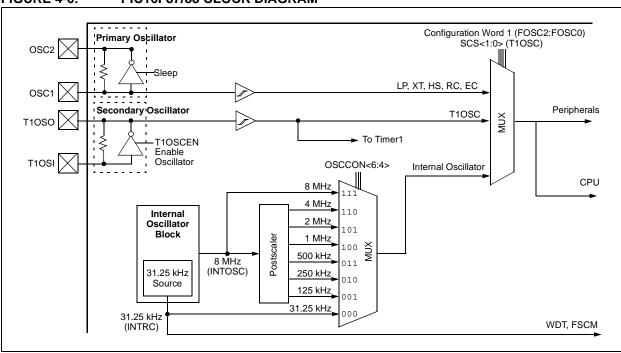

## FIGURE 4-6: PIC16F87/88 CLOCK DIAGRAM

#### 4.6.4 MODIFYING THE IRCF BITS

The IRCF bits can be modified at any time regardless of which clock source is currently being used as the system clock. The internal oscillator allows users to change the frequency during run time. This is achieved by modifying the IRCF bits in the OSCCON register. The sequence of events that occur after the IRCF bits are modified is dependent upon the initial value of the IRCF bits before they are modified. If the INTRC (31.25 kHz. IRCF < 2:0 > = 000) is running and the IRCF bits are modified to any other value than '000', a 4 ms (approx.) clock switch delay is turned on. Code execution continues at a higher than expected frequency while the new frequency stabilizes. Time sensitive code should wait for the IOFS bit in the OSCCON register to become set before continuing. This bit can be monitored to ensure that the frequency is stable before using the system clock in time critical applications.

If the IRCF bits are modified while the internal oscillator is running at any other frequency than INTRC (31.25 kHz, IRCF<2:0>  $\neq$  000), there is no need for a 4 ms (approx.) clock switch delay. The new INTOSC frequency will be stable immediately after the **eight** falling edges. The IOFS bit will remain set after clock switching occurs.

Note: Caution must be taken when modifying the IRCF bits using BCF or BSF instructions. It is possible to modify the IRCF bits to a frequency that may be out of the VDD specification range; for example, VDD = 2.0V and IRCF = 111 (8 MHz).

#### 4.6.5 CLOCK TRANSITION SEQUENCE

Following are three different sequences for switching the internal RC oscillator frequency.

- Clock before switch: 31.25 kHz (IRCF<2:0> = 000)

- IRCF bits are modified to an INTOSC/INTOSC postscaler frequency.

- The clock switching circuitry waits for a falling edge of the current clock, at which point CLKO is held low.

- The clock switching circuitry then waits for eight falling edges of requested clock, after which it switches CLKO to this new clock source.

- The IOFS bit is clear to indicate that the clock is unstable and a 4 ms (approx.) delay is started. Time dependent code should wait for IOFS to become set.

- 5. Switchover is complete.

- Clock before switch: One of INTOSC/INTOSC postscaler (IRCF<2:0> ≠ 000)

- 1. IRCF bits are modified to INTRC (IRCF<2:0> = 000).

- The clock switching circuitry waits for a falling edge of the current clock, at which point CLKO is held low.

- The clock switching circuitry then waits for eight falling edges of requested clock, after which it switches CLKO to this new clock source.

- 4. Oscillator switchover is complete.

### REGISTER 7-1: T1CON: TIMER1 CONTROL REGISTER (ADDRESS 10h)

| U-0   | R-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|---------|---------|---------|--------|--------|--------|

| 1     | T1RUN | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N |

| bit 7 |       |         |         |         |        |        | bit 0  |

bit 7 Unimplemented: Read as '0'

bit 6 T1RUN: Timer1 System Clock Status bit

1 = System clock is derived from Timer1 oscillator0 = System clock is derived from another source

bit 5-4 T1CKPS<1:0>: Timer1 Input Clock Prescale Select bits

11 = 1:8 Prescale value 10 = 1:4 Prescale value 01 = 1:2 Prescale value 00 = 1:1 Prescale value

bit 3 T10SCEN: Timer1 Oscillator Enable Control bit

1 = Oscillator is enabled

0 = Oscillator is shut off (the oscillator inverter is turned off to eliminate power drain)

bit 2 T1SYNC: Timer1 External Clock Input Synchronization Control bit

TMR1CS = 1

1 = Do not synchronize external clock input

0 = Synchronize external clock input

TMR1CS = 0:

This bit is ignored. Timer1 uses the internal clock when TMR1CS = 0.

bit 1 TMR1CS: Timer1 Clock Source Select bit

1 = External clock from pin RB6/AN5<sup>(1)</sup>/PGC/T1OSO/T1CKI (on the rising edge)

0 = Internal clock (Fosc/4)

Note 1: Available on PIC16F88 devices only.

bit 0 TMR10N: Timer1 On bit

1 = Enables Timer1

0 = Stops Timer1

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

## 7.8 Resetting Timer1 Using a CCP Trigger Output

If the CCP1 module is configured in Compare mode to generate a "special event trigger" signal (CCP1M3:CCP1M0 = 1011), the signal will reset Timer1 and start an A/D conversion (if the A/D module is enabled).

**Note:** The special event triggers from the CCP1 module will not set interrupt flag bit, TMR1IF (PIR1<0>).

Timer1 must be configured for either Timer or Synchronized Counter mode to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this Reset operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1, the write will take precedence.

In this mode of operation, the CCPR1H:CCPR1L register pair effectively becomes the period register for Timer1.

# 7.9 Resetting Timer1 Register Pair (TMR1H, TMR1L)

TMR1H and TMR1L registers are not reset to 00h on a POR, or any other Reset, except by the CCP1 special event triggers.

T1CON register is reset to 00h on a Power-on Reset or a Brown-out Reset, which shuts off the timer and leaves a 1:1 prescale. In all other Resets, the register is unaffected.

#### 7.10 Timer1 Prescaler

The prescaler counter is cleared on writes to the TMR1H or TMR1L registers.

## 7.11 Using Timer1 as a Real-Time Clock

Adding an external LP oscillator to Timer1 (such as the one described in **Section 7.6** "Timer1 Oscillator") gives users the option to include RTC functionality to their applications. This is accomplished with an inexpensive watch crystal to provide an accurate time base and several lines of application code to calculate the time. When operating in Sleep mode and using a battery or supercapacitor as a power source, it can completely eliminate the need for a separate RTC device and battery backup.

The application code routine, RTCisr, shown in Example 7-3, demonstrates a simple method to increment a counter at one-second intervals using an Interrupt Service Routine. Incrementing the TMR1 register pair to overflow triggers the interrupt and calls the routine, which increments the seconds counter by one; additional counters for minutes and hours are incremented as the previous counter overflows.

Since the register pair is 16 bits wide, counting up to overflow the register directly from a 32.768 kHz clock would take 2 seconds. To force the overflow at the required one-second intervals, it is necessary to preload it; the simplest method is to set the MSb of TMR1H with a BSF instruction. Note that the TMR1L register is never preloaded or altered; doing so may introduce cumulative error over many cycles.

For this method to be accurate, Timer1 must operate in Asynchronous mode and the Timer1 overflow interrupt must be enabled (PIE1<0> = 1), as shown in the routine, RTCinit. The Timer1 oscillator must also be enabled and running at all times.

# 11.1 AUSART Baud Rate Generator (BRG)

The BRG supports both the Asynchronous and Synchronous modes of the AUSART. It is a dedicated 8-bit Baud Rate Generator. The SPBRG register controls the period of a free running 8-bit timer. In Asynchronous mode, bit BRGH (TXSTA<2>) also controls the baud rate. In Synchronous mode, bit BRGH is ignored. Table 11-1 shows the formula for computation of the baud rate for different AUSART modes which only apply in Master mode (internal clock).

Given the desired baud rate and Fosc, the nearest integer value for the SPBRG register can be calculated using the formula in Table 11-1. From this, the error in baud rate can be determined.

It may be advantageous to use the high baud rate (BRGH = 1) even for slower baud clocks. This is because the Fosc/(16(X + 1)) equation can reduce the baud rate error in some cases.

Writing a new value to the SPBRG register causes the BRG timer to be reset (or cleared). This ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

#### 11.1.1 AUSART AND INTRC OPERATION

The PIC16F87/88 has an 8 MHz INTRC that can be used as the system clock, thereby eliminating the need for external components to provide the clock source. When the INTRC provides the system clock, the AUSART module will also use the INTRC as its system clock. Table 11-1 shows some of the INTRC frequencies that can be used to generate the AUSART module's baud rate.

#### 11.1.2 LOW-POWER MODE OPERATION

The system clock is used to generate the desired baud rate; however, when a low-power mode is entered, the low-power clock source may be operating at a different frequency than in full power execution. In Sleep mode, no clocks are present. This may require the value in SPBRG to be adjusted.

#### 11.1.3 SAMPLING

The data on the RB2/SDO/RX/DT pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin.

TABLE 11-1: BAUD RATE FORMULA

| SYNC | BRGH = 0 (Low Speed)                        | BRGH = 1 (High Speed)        |

|------|---------------------------------------------|------------------------------|

| 0    | (Asynchronous) Baud Rate = Fosc/(64(X + 1)) | Baud Rate = Fosc/(16(X + 1)) |

| 1    | (Synchronous) Baud Rate = Fosc/(4(X + 1))   | N/A                          |

**Legend:** X = value in SPBRG (0 to 255)

TABLE 11-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Address | Name  | Bit 7    | Bit 6     | Bit 5      | Bit 4 | Bit 3 | Bit 2     | Bit 1     | Bit 0 | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|-------|----------|-----------|------------|-------|-------|-----------|-----------|-------|-----------------------|---------------------------------|

| 98h     | TXSTA | CSRC     | TX9       | TXEN       | SYNC  | _     | BRGH      | TRMT      | TX9D  | 0000 -010             | 0000 -010                       |

| 18h     | RCSTA | SPEN     | RX9       | SREN       | CREN  | ADDEN | FERR      | OERR      | RX9D  | 0000 000x             | 0000 000x                       |

| 99h     | SPBRG | Baud Rat | te Genera | ator Regis | ter   |       | 0000 0000 | 0000 0000 |       |                       |                                 |

**Legend:** x = unknown, -= unimplemented, read as '0'. Shaded cells are not used by the BRG.

When setting up an asynchronous reception, follow these steps:

- Initialize the SPBRG register for the appropriate baud rate. If a high-speed baud rate is desired, set bit BRGH (Section 11.1 "AUSART Baud Rate Generator (BRG)").

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- If interrupts are desired, then set enable bit RCIE.

- 4. If 9-bit reception is desired, then set bit RX9.

- 5. Enable the reception by setting bit CREN.

- Flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE is set.

- 7. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREG register.

- If any error occurred, clear the error by clearing enable bit CREN.

- 10. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

### TABLE 11-8: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Address                | Name   | Bit 7   | Bit 6                                                    | Bit 5      | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|------------------------|--------|---------|----------------------------------------------------------|------------|--------|-------|--------|--------|--------|-----------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE     | PEIE                                                     | TMR0IE     | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF   | 0000 000x             | 0000 000u                       |

| 0Ch                    | PIR1   | _       | ADIF <sup>(1)</sup>                                      | RCIF       | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | -000 0000             | -000 0000                       |

| 18h                    | RCSTA  | SPEN    | RX9                                                      | SREN       | CREN   | ADDEN | FERR   | OERR   | RX9D   | 0000 000x             | 0000 000x                       |

| 1Ah                    | RCREG  | AUSART  | Receive D                                                | ata Regist | er     |       |        |        |        | 0000 0000             | 0000 0000                       |

| 8Ch                    | PIE1   | _       | ADIE <sup>(1)</sup> RCIE TXIE SSPIE CCP1IE TMR2IE TMR1IE |            |        |       |        |        | TMR1IE | -000 0000             | -000 0000                       |

| 98h                    | TXSTA  | CSRC    | TX9                                                      | TXEN       | SYNC   | _     | BRGH   | TRMT   | TX9D   | 0000 -010             | 0000 -010                       |

| 99h                    | SPBRG  | Baud Ra | te Generato                                              | r Registe  | r      | •     |        | •      |        | 0000 0000             | 0000 0000                       |

**Legend:** x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception.

Note 1: This bit is only implemented on the PIC16F88. The bit will read '0' on the PIC16F87.

## 11.3.2 AUSART SYNCHRONOUS MASTER RECEPTION

Once Synchronous mode is selected, reception is enabled by setting either enable bit SREN (RCSTA<5>), or enable bit CREN (RCSTA<4>). Data is sampled on the RB2/SDO/RX/DT pin on the falling edge of the clock. If enable bit SREN is set, then only a single word is received. If enable bit CREN is set, the reception is continuous until CREN is cleared. If both bits are set, CREN takes precedence.

After clocking the last bit, the received data in the Receive Shift Register (RSR) is transferred to the RCREG register (if it is empty). When the transfer is complete, interrupt flag bit, RCIF (PIR1<5>), is set. The actual interrupt can be enabled/disabled by setting/ clearing enable bit RCIE (PIE1<5>).

Flag bit RCIF is a read-only bit which is reset by the hardware. In this case, it is reset when the RCREG register has been read and is empty. The RCREG is a double-buffered register (i.e., it is a two-deep FIFO). It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting into the RSR register. On the clocking of the last bit of the third byte, if the RCREG register is still full, then Overrun Error bit, OERR (RCSTA<1>), is set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Bit OERR has to be cleared in software (by clearing bit CREN). If bit OERR is set, transfers from the RSR to the RCREG are inhibited, so it is essential to clear bit OERR if it is set. The ninth receive bit is buffered the same way as the

receive data. Reading the RCREG register will load bit RX9D with a new value, therefore, it is essential for the user to read the RCSTA register, before reading RCREG, in order not to lose the old RX9D information.

When setting up a synchronous master reception:

- Initialize the SPBRG register for the appropriate baud rate (Section 11.1 "AUSART Baud Rate Generator (BRG)").

- Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Ensure bits CREN and SREN are clear.

- 4. If interrupts are desired, then set enable bit RCIE.

- 5. If 9-bit reception is desired, then set bit RX9.

- 6. If a single reception is required, set bit SREN. For continuous reception, set bit CREN.

- 7. Interrupt flag bit, RCIF, will be set when reception is complete and an interrupt will be generated if enable bit, RCIE, was set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- Read the 8-bit received data by reading the RCREG register.

- If any error occurred, clear the error by clearing bit CREN.

- 11. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

TABLE 11-11: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

| Address                | Name   | Bit 7   | Bit 6               | Bit 5       | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value<br>POR, E |      | Valu<br>all o<br>Res | ther |

|------------------------|--------|---------|---------------------|-------------|--------|-------|--------|--------|--------|-----------------|------|----------------------|------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE     | PEIE                | TMR0IE      | INTOIE | RBIE  | TMR0IF | INT0IF | RBIF   | 0000            | 000x | 0000                 | 000u |

| 0Ch                    | PIR1   | _       | ADIF <sup>(1)</sup> | RCIF        | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | -000            | 0000 | -000                 | 0000 |

| 18h                    | RCSTA  | SPEN    | RX9                 | SREN        | CREN   | ADDEN | FERR   | OERR   | RX9D   | 0000            | x000 | 0000                 | 000x |

| 1Ah                    | RCREG  | AUSART  | Receive             | Data Regi   | ster   |       |        |        |        | 0000            | 0000 | 0000                 | 0000 |

| 8Ch                    | PIE1   | _       | ADIE <sup>(1)</sup> | RCIE        | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE | -000            | 0000 | -000                 | 0000 |

| 98h                    | TXSTA  | CSRC    | TX9                 | TXEN        | SYNC   | _     | BRGH   | TRMT   | TX9D   | 0000 -          | -010 | 0000                 | -010 |

| 99h                    | SPBRG  | Baud Ra | te Genera           | ator Regist | er     |       |        |        |        | 0000            | 0000 | 0000                 | 0000 |

$\textbf{Legend:} \qquad \textbf{x} = \text{unknown, -= unimplemented, read as '0'}. \label{eq:x} Shaded cells are not used for synchronous master reception.}$

Note 1: This bit is only implemented on the PIC16F88. The bit will read '0' on the PIC16F87.

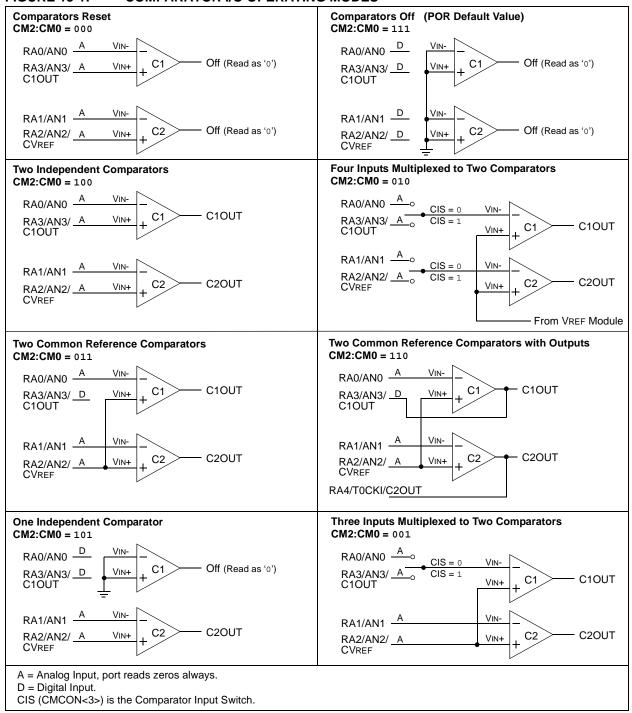

### 13.1 Comparator Configuration

There are eight modes of operation for the comparators. The CMCON register is used to select these modes. Figure 13-1 shows the eight possible modes. The TRISA register controls the data direction of the comparator pins for each mode. If the Comparator mode is changed, the comparator output level may not be valid for the specified mode change delay shown in Section 18.0 "Electrical Characteristics".

Comparator interrupts should be disabled during a Comparator mode change; otherwise, a false interrupt may occur.

Note:

#### FIGURE 13-1: COMPARATOR I/O OPERATING MODES

# 13.7 Comparator Operation During Sleep

When a comparator is active and the device is placed in Sleep mode, the comparator remains active and the interrupt is functional, if enabled. This interrupt will wake-up the device from Sleep mode when enabled. While the comparator is powered up, higher Sleep currents than shown in the power-down current specification will occur. Each operational comparator will consume additional current, as shown in the comparator specifications. To minimize power consumption while in Sleep mode, turn off the comparators, CM<2:0>=111, before entering Sleep. If the device wakes up from Sleep, the contents of the CMCON register are not affected.

#### 13.8 Effects of a Reset

A device Reset forces the CMCON register to its Reset state, causing the comparator module to be in the Comparator Off mode, CM<2:0> = 111.

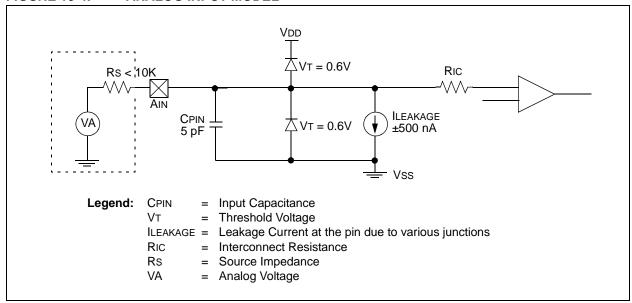

## 13.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 13-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up condition may occur. A maximum source impedance of  $10~\text{k}\Omega$  is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

FIGURE 13-4: ANALOG INPUT MODEL

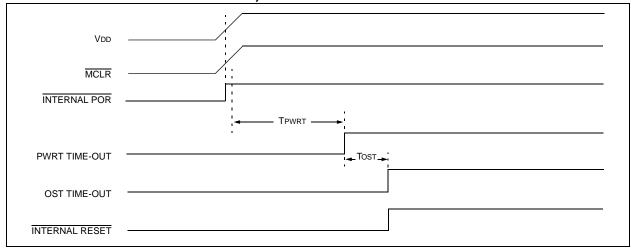

#### 15.8 Time-out Sequence

On power-up, the time-out sequence is as follows: the PWRT delay starts (if enabled) when a POR occurs. Then, OST starts counting 1024 oscillator cycles when PWRT ends (LP, XT, HS). When the OST ends, the device comes out of Reset.

If MCLR is kept low long enough, all delays will expire. Bringing MCLR high will begin execution immediately. This is useful for testing purposes, or to synchronize more than one PIC16F87/88 device operating in parallel.

Table 15-3 shows the Reset conditions for the STATUS, PCON and PC registers, while Table 15-4 shows the Reset conditions for all the registers.

# 15.9 Power Control/Status Register (PCON)

The Power Control/Status Register, PCON, has two bits to indicate the type of Reset that last occurred.

Bit 0 is Brown-out Reset Status bit,  $\overline{\text{BOR}}$ . Bit  $\overline{\text{BOR}}$  is unknown on a Power-on Reset. It must then be set by the user and checked on subsequent Resets to see if bit  $\overline{\text{BOR}}$  cleared, indicating a Brown-out Reset occurred. When the Brown-out Reset is disabled, the state of the  $\overline{\text{BOR}}$  bit is unpredictable.

Bit 1 is POR (Power-on Reset Status bit). It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

**TABLE 15-1: TIME-OUT IN VARIOUS SITUATIONS**

| Oscillator    | Power-ı             | up                     | Brown-out Reset     |                        |                        |  |  |

|---------------|---------------------|------------------------|---------------------|------------------------|------------------------|--|--|

| Configuration | PWRTE = 0           | PWRTE = 1              | PWRTE = 0           | PWRTE = 1              | Sleep                  |  |  |

| XT, HS, LP    | TPWRT + 1024 • Tosc | 1024 • Tosc            | TPWRT + 1024 • Tosc | 1024 • Tosc            | 1024 • Tosc            |  |  |

| EXTRC, INTRC  | Tpwrt               | 5-10 μs <sup>(1)</sup> | Tpwrt               | 5-10 μs <sup>(1)</sup> | 5-10 μs <sup>(1)</sup> |  |  |

| T1OSC         | _                   | _                      | _                   | _                      | 5-10 μs <sup>(1)</sup> |  |  |

Note 1: CPU start-up is always invoked on POR, BOR and wake-up from Sleep. The 5-10  $\mu$ s delay is based on a 1 MHz system clock.

TABLE 15-2: STATUS BITS AND THEIR SIGNIFICANCE

| POR | BOR | TO | PD |                                                         |

|-----|-----|----|----|---------------------------------------------------------|

| 0   | х   | 1  | 1  | Power-on Reset                                          |

| 0   | х   | 0  | х  | Illegal, TO is set on POR                               |

| 0   | х   | х  | 0  | Illegal, PD is set on POR                               |

| 1   | 0   | 1  | 1  | Brown-out Reset                                         |

| 1   | 1   | 0  | 1  | WDT Reset                                               |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |

| 1   | 1   | u  | u  | MCLR Reset during Normal Operation                      |

| 1   | 1   | 1  | 0  | MCLR Reset during Sleep or Interrupt Wake-up from Sleep |

**Legend:** u = unchanged, x = unknown

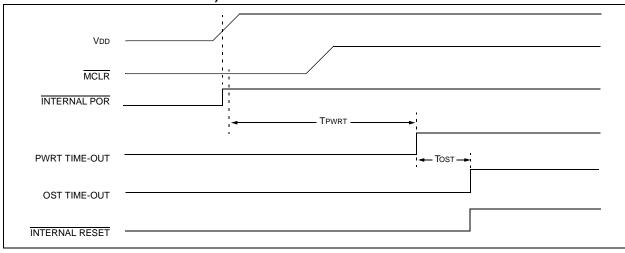

FIGURE 15-3: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD THROUGH PULL-UP RESISTOR)

FIGURE 15-4: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD THROUGH RC NETWORK): CASE 1

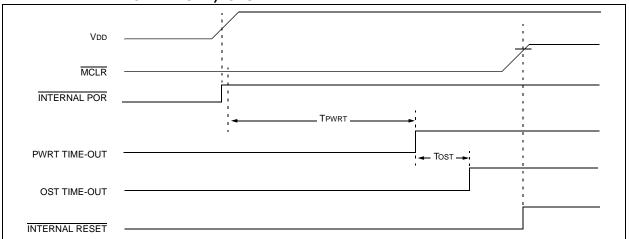

FIGURE 15-5: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD THROUGH RC NETWORK): CASE 2

#### 15.10.1 INT INTERRUPT

External interrupt on the RB0/INT pin is edge-triggered, either rising if bit INTEDG (OPTION\_REG<6>) is set, or falling if the INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, flag bit, INT0IF (INTCON<1>), is set. This interrupt can be disabled by clearing enable bit INT0IE (INTCON<4>). Flag bit INT0IF must be cleared in software in the Interrupt Service Routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from Sleep, if bit INT0IE was set prior to going into Sleep. The status of global interrupt enable bit GIE decides whether or not the processor branches to the interrupt vector, following wake-up. See Section 15.13 "Power-Down Mode (Sleep)" for details on Sleep mode.

#### 15.10.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit TMR0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit TMR0IE (INTCON<5>), see **Section 6.0 "Timer0 Module"**.

#### 15.10.3 PORTB INTCON CHANGE

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit RBIE (INTCON<4>), see Section 3.2 "EECON1 and EECON2 Registers".

## 15.11 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (i.e., W, STATUS registers).

Since the upper 16 bytes of each bank are common in the PIC16F87/88 devices, temporary holding registers W\_TEMP, STATUS\_TEMP and PCLATH\_TEMP should be placed in here. These 16 locations don't require banking and therefore, make it easier for context save and restore. The same code shown in Example 15-1 can be used.

#### **EXAMPLE 15-1:** SAVING STATUS, W AND PCLATH REGISTERS IN RAM

```

MOVWF

W TEMP

;Copy W to TEMP register

SWAPF

STATUS, W

;Swap status to be saved into W

CLRF

STATUS

; bank 0, regardless of current bank, Clears IRP, RP1, RP0

STATUS_TEMP

MOVWF

; Save status to bank zero STATUS TEMP register

;Only required if using page 1

MOVF

PCLATH, W

PCLATH TEMP

MOVWF

;Save PCLATH into W

CLRF

PCLATH

; Page zero, regardless of current page

:(ISR)

: (Insert user code here)

MOVF

PCLATH_TEMP, W

; Restore PCLATH

MOVWF

PCLATH

; Move W into PCLATH

SWAPF

STATUS_TEMP, W

;Swap STATUS_TEMP register into W

; (sets bank to original state)

MOVWF

STATUS

; Move W into STATUS register

SWAPF

W TEMP, F

;Swap W TEMP

;Swap W_TEMP into W

SWAPF

W_TEMP, W

```

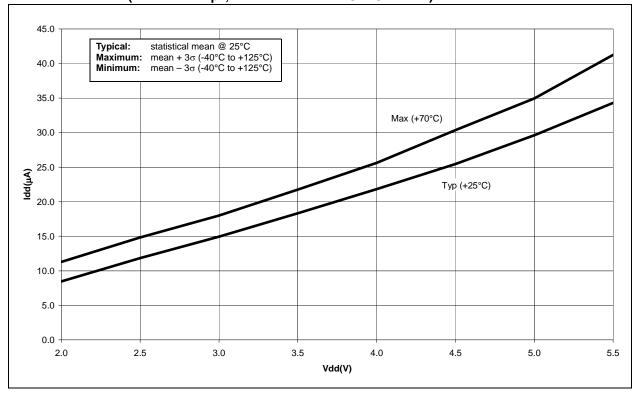

FIGURE 19-9: IDD vs. VDD, SEC\_RUN MODE, -10°C TO +125°C, 32.768 kHz (XTAL 2 x 22 pF, ALL PERIPHERALS DISABLED)

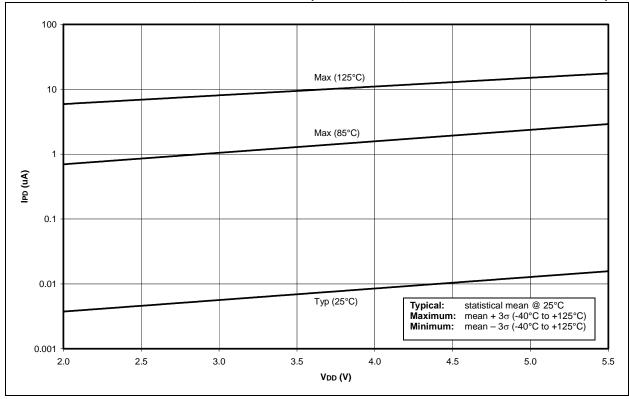

FIGURE 19-10: IPD vs. VDD, -40°C TO +125°C (SLEEP MODE, ALL PERIPHERALS DISABLED)

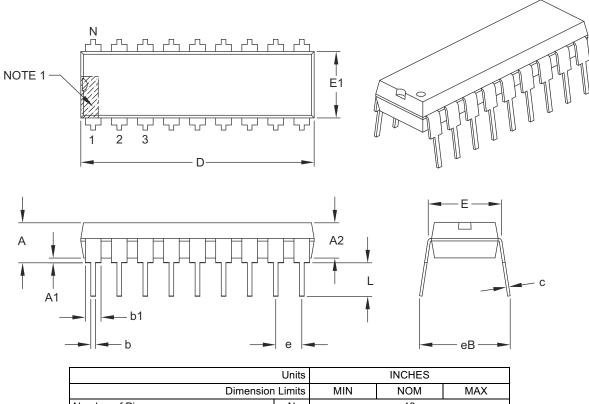

## 18-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units            |      | INCHES   |      |

|----------------------------|------------------|------|----------|------|

|                            | Dimension Limits | MIN  | NOM      | MAX  |

| Number of Pins             | N                |      | 18       |      |

| Pitch                      | е                |      | .100 BSC |      |

| Top to Seating Plane       | A                | _    | _        | .210 |

| Molded Package Thickness   | A2               | .115 | .130     | .195 |

| Base to Seating Plane      | A1               | .015 | -        | -    |

| Shoulder to Shoulder Width | E                | .300 | .310     | .325 |

| Molded Package Width       | E1               | .240 | .250     | .280 |

| Overall Length             | D                | .880 | .900     | .920 |

| Tip to Seating Plane       | L                | .115 | .130     | .150 |

| Lead Thickness             | С                | .008 | .010     | .014 |

| Upper Lead Width           | b1               | .045 | .060     | .070 |

| Lower Lead Width           | b                | .014 | .018     | .022 |

| Overall Row Spacing §      | eB               | _    | _        | .430 |

### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-007B

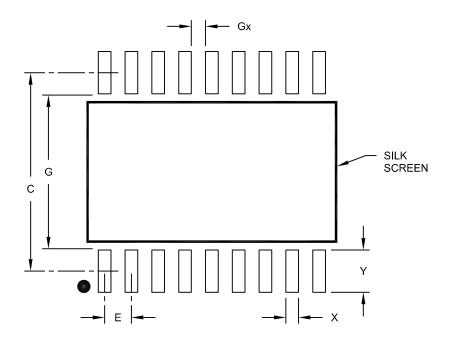

## 18-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

**RECOMMENDED LAND PATTERN**

| Units                 |    | MILLIMETERS |          |      |

|-----------------------|----|-------------|----------|------|

| Dimension Limits      |    | MIN         | NOM      | MAX  |

| Contact Pitch         | E  |             | 1.27 BSC |      |

| Contact Pad Spacing   | С  |             | 9.40     |      |

| Contact Pad Width     | Х  |             |          | 0.60 |

| Contact Pad Length    | Υ  |             |          | 2.00 |

| Distance Between Pads | Gx | 0.67        |          |      |

| Distance Between Pads |    | 7.40        |          | ·    |

#### Notes:

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2051A

<sup>1.</sup> Dimensioning and tolerancing per ASME Y14.5M

# PIC16F87/88

| TMR1 Overflow Interrupt Enable (TMR1IE Bit)22             | P                                                 |    |

|-----------------------------------------------------------|---------------------------------------------------|----|

| TMR2 to PR2 Match Interrupt Enable (TMR2IE Bit)22         | Packaging Information2                            | 07 |

| Interrupts, Flag Bits                                     | Marking                                           |    |

| A/D Converter Interrupt Flag (ADIF Bit)23                 | Paging, Program Memory                            |    |

| AUSART Receive Interrupt Flag (RCIF Bit)23                | PCL Register 16, 17,                              |    |

| AUSART Transmit Interrupt Flag (TXIF Bit)23               | PCLATH Register                                   |    |

| CCP1 Interrupt Flag (CCP1IF Bit)23                        | PCON Register                                     |    |

| Comparator Interrupt Flag (CMIF Bit)25                    | BOR Bit                                           |    |

| EEPROM Write Operation Interrupt Flag (EEIF Bit)25        | POR Bit                                           |    |

| Interrupt-on-Change (RB7:RB4) Flag (RBIF Bit) 21, 142     | PIE1 Register                                     |    |

| Oscillator Fail Interrupt Flag (OSFIF Bit)25              | ADIE Bit                                          |    |

| RB0/INT Flag (INT0IF Bit)21                               | CCP1IE Bit                                        |    |

| Synchronous Serial Port (SSP) Interrupt Flag (SSPIF Bit)  | RCIE Bit                                          |    |

| 23                                                        | SSPIE Bit                                         |    |

| TMR0 Overflow Flag (TMR0IF Bit)142                        | TMR1IE Bit                                        |    |

| TMR1 Overflow Interrupt Flag (TMR1IF Bit)23               | TMR2IE Bit                                        |    |

| TMR2 to PR2 Interrupt Flag (TMR2IF Bit)23                 | TXIE Bit                                          |    |

| INTRC Modes                                               | PIE2 Register                                     |    |

| Adjustment40                                              | CMIE Bit                                          |    |

| L                                                         | EEIE Bit                                          |    |

| _                                                         | OSFIE Bit                                         |    |

| Loading of PC27                                           | Pinout Descriptions                               |    |

| Low Voltage ICSP Programming150                           | PIC16F87/88                                       | 10 |

| M                                                         | PIR1 Register                                     |    |

|                                                           | ADIF Bit                                          |    |

| Master Clear (MCLR)                                       | CCP1IF Bit                                        |    |

| MCLR Reset, Normal Operation134, 137                      | RCIF Bit                                          |    |

| MCLR Reset, Sleep134, 137                                 | SSPIF Bit                                         |    |

| Operation and ESD Protection                              | TMR1IF Bit                                        |    |

| Memory Organization                                       | TMR2IF Bit                                        |    |

| Data Memory13                                             | TXIF Bit                                          |    |

| Program Memory13                                          | PIR2 Register                                     |    |

| Microchip Internet Web Site                               | CMIF Bit                                          |    |

| MPLAB ASM30 Assembler, Linker, Librarian160               | EEIF Bit                                          |    |

| MPLAB Integrated Development Environment Software .159    | OSFIF Bit                                         |    |

| MPLAB PM3 Device Programmer                               | POP                                               |    |

| MPLAB REAL ICE In-Circuit Emulator System161              | POR. See Power-on Reset.                          |    |

| MPLINK Object Linker/MPLIB Object Librarian160            | PORTA                                             | 10 |

| 0                                                         | Associated Register Summary                       |    |

|                                                           | PORTA Register                                    |    |

| Opcode Field Descriptions151                              | PORTB                                             |    |

| OPTION_REG Register INTEDG Bit                            | Associated Register Summary                       |    |

| PS2:PS0 Bits                                              | PORTB Register16,                                 |    |

|                                                           | Pull-up Enable (RBPU Bit)                         |    |

| PSA Bit                                                   | RB0/INT Edge Select (INTEDG Bit)                  | 20 |

| RBPU Bit                                                  | RB0/INT Pin, External1                            |    |

| TOCS Bit                                                  | RB2/SDO/RX/DT Pin100, 1                           |    |

| TOSE Bit                                                  | RB5/SS/TX/CK Pin1                                 | 00 |

| OSCCON Register                                           | RB7:RB4 Interrupt-on-Change1                      |    |

| Oscillator Configuration                                  | RB7:RB4 Interrupt-on-Change Enable (RBIE Bit) 1   |    |

| ECIO                                                      | RB7:RB4 Interrupt-on-Change Flag (RBIF Bit) 21, 1 |    |

| EXTRC136                                                  | TRISB Register                                    |    |

| HS37, 136                                                 | Postscaler, WDT                                   | •  |

| INTIO1                                                    | Assignment (PSA Bit)                              | 20 |

| INTIO237                                                  | Rate Select (PS2:PS0 Bits)                        |    |

| INTRC                                                     | Power-Down Mode. See Sleep.                       |    |

| LP37, 136                                                 | Power-Managed Modes                               | 45 |

| RC                                                        | RC_RUN                                            |    |

| RCIO                                                      | SEC_RUN                                           |    |

| XT37, 136                                                 | SEC_RUN/RC_RUN to Primary Clock Source            |    |

| Oscillator Control Register                               | Power-on Reset (POR) 131, 134, 135, 1             |    |

| Modifying IRCF Bits                                       | POR Status (POR Bit)                              |    |

| Oscillator Delay upon Power-up, Wake-up and Clock Switch- | Power Control (PCON) Register 1                   |    |

| ing                                                       | Power-Down (PD Bit)                               |    |

| Oscillator Start-up Timer (OST)                           | Time-out (TO Bit)                                 |    |

| Oscillator Switching                                      | Power-up Timer (PWRT)131, 1                       |    |

| OSCTUNE Register17                                        | 1 34137 up 1111101 (1 **1111)                     | -  |

## PIC16F87/88

### READER RESPONSE

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| RE:  | Reader Response                         | Total Pages Sent                                      |

|------|-----------------------------------------|-------------------------------------------------------|

| Fror | m: Name                                 |                                                       |

|      | Company                                 |                                                       |

|      | Telephone: ()                           |                                                       |

| Арр  | olication (optional):                   |                                                       |

| Wou  | uld you like a reply?YN                 |                                                       |

| Dev  | rice: PIC16F87/88                       | Literature Number: DS30487D                           |

| Que  | estions:                                |                                                       |

| 1.   | What are the best features of this doc  | ument?                                                |

|      |                                         |                                                       |

| 2.   | How does this document meet your ha     | ardware and software development needs?               |

|      |                                         |                                                       |

| 3.   | Do you find the organization of this do | cument easy to follow? If not, why?                   |

|      |                                         |                                                       |

| 4.   | What additions to the document do yo    | ou think would enhance the structure and subject?     |

|      |                                         |                                                       |

| 5.   | What deletions from the document co     | uld be made without affecting the overall usefulness? |

|      |                                         |                                                       |

| 6.   | Is there any incorrect or misleading in | formation (what and where)?                           |

|      |                                         |                                                       |

| 7.   | How would you improve this documer      | nt?                                                   |

|      |                                         |                                                       |