Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 16                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 368 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | A/D 7x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                           |

| Supplier Device Package    | 18-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f88t-i-so |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name                    | PDIP/<br>SOIC<br>Pin# | SSOP<br>Pin# | QFN<br>Pin# | l/O/P<br>Type | Buffer<br>Type    | Description                                                                                                        |

|-----------------------------|-----------------------|--------------|-------------|---------------|-------------------|--------------------------------------------------------------------------------------------------------------------|

|                             |                       |              |             |               |                   | PORTB is a bidirectional I/O port. PORTB can be<br>software programmed for internal weak pull-up on all<br>inputs. |

| RB0/INT/CCP1 <sup>(5)</sup> | 6                     | 7            | 7           |               |                   |                                                                                                                    |

| RB0                         |                       |              |             | I/O           | TTL               | Bidirectional I/O pin.                                                                                             |

| INT                         |                       |              |             | I             | ST <sup>(1)</sup> | External interrupt pin.                                                                                            |

| CCP1                        |                       |              |             | I/O           | ST                | Capture input, Compare output, PWM output.                                                                         |

| RB1/SDI/SDA                 | 7                     | 8            | 8           |               |                   |                                                                                                                    |

| RB1<br>SDI                  |                       |              |             | I/O<br>I      | TTL<br>ST         | Bidirectional I/O pin.<br>SPI data in.                                                                             |

| SDA                         |                       |              |             | 1/0           | ST                | $I^2 C^{TM}$ data.                                                                                                 |

| RB2/SDO/RX/DT               | 8                     | 9            | 9           | 1/0           | 01                |                                                                                                                    |

| RB2                         | 0                     | 9            | 9           | I/O           | TTL               | Bidirectional I/O pin.                                                                                             |

| SDO                         |                       |              |             | 0             | ST                | SPI data out.                                                                                                      |

| RX                          |                       |              |             | I             |                   | AUSART asynchronous receive.                                                                                       |

| DT                          |                       |              |             | I/O           |                   | AUSART synchronous detect.                                                                                         |

| RB3/PGM/CCP1 <sup>(5)</sup> | 9                     | 10           | 10          |               |                   |                                                                                                                    |

| RB3                         |                       |              |             | I/O           | TTL               | Bidirectional I/O pin.                                                                                             |

| PGM                         |                       |              |             | I/O           | ST                | Low-Voltage ICSP™ Programming enable pin.                                                                          |

| CCP1                        |                       |              |             | I             | ST                | Capture input, Compare output, PWM output.                                                                         |

| RB4/SCK/SCL                 | 10                    | 11           | 12          |               |                   |                                                                                                                    |

| RB4<br>SCK                  |                       |              |             | 1/0<br>1/0    | TTL<br>ST         | Bidirectional I/O pin. Interrupt-on-change pin.<br>Synchronous serial clock input/output for SPI.                  |

| SCL                         |                       |              |             | 1/0           | ST                | Synchronous serial clock input/output for SP1.                                                                     |

| RB5/SS/TX/CK                | 11                    | 12           | 13          | •             | 01                | Cynonionous senarolook inpartor r C.                                                                               |

| RB5                         | 1 11                  | 12           | 15          | I/O           | TTL               | Bidirectional I/O pin. Interrupt-on-change pin.                                                                    |

| SS                          |                       |              |             | 1/0           | TTL               | Slave select for SPI in Slave mode.                                                                                |

| TX                          |                       |              |             | 0             |                   | AUSART asynchronous transmit.                                                                                      |

| СК                          |                       |              |             | I/O           |                   | AUSART synchronous clock.                                                                                          |

| RB6/AN5/PGC/T1OSO/          | 12                    | 13           | 15          |               |                   |                                                                                                                    |

| T1CKI                       |                       |              |             |               |                   |                                                                                                                    |

|                             |                       |              |             | I/O           | TTL               | Bidirectional I/O pin. Interrupt-on-change pin.                                                                    |

| AN5 <sup>(4)</sup><br>PGC   |                       |              |             | I<br>I/O      | ST <sup>(2)</sup> | Analog input channel 5.<br>In-Circuit Debugger and programming clock pin.                                          |

| T10S0                       |                       |              |             | 0             | ST                | Timer1 oscillator output.                                                                                          |

| T1CKI                       |                       |              |             | I             | ST                | Timer1 external clock input.                                                                                       |

| RB7/AN6/PGD/T1OSI           | 13                    | 14           | 16          |               |                   |                                                                                                                    |

| RB7                         |                       | 17           | 10          | I/O           | TTL               | Bidirectional I/O pin. Interrupt-on-change pin.                                                                    |

| AN6 <sup>(4)</sup>          |                       |              |             | I             |                   | Analog input channel 6.                                                                                            |

| PGD                         |                       |              |             | I             | ST <sup>(2)</sup> | In-Circuit Debugger and ICSP programming data pi                                                                   |

| T1OSI                       |                       |              |             | Ι             | ST                | Timer1 oscillator input.                                                                                           |

| Vss                         | 5                     | 5, 6         | 3, 5        | Р             | -                 | Ground reference for logic and I/O pins.                                                                           |

| VDD                         | 14                    | 15, 16       | 17, 19      | Р             | -                 | Positive supply for logic and I/O pins.                                                                            |

| TABLE 1-2: | PIC16F87/88 PINOUT DESCRIPTION ( | (CONTINUED) |

|------------|----------------------------------|-------------|

|            |                                  |             |

- = Not used TTL = TTL Input ST = Schmitt Trigger Input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

4: PIC16F88 devices only.

5: The CCP1 pin is determined by the CCPMX bit in Configuration Word 1 register.

#### 2.2.2.6 PIE2 Register

The PIE2 register contains the individual enable bit for the EEPROM write operation interrupt.

| REGISTER 2-6: | PIE2: PEF                 | RIPHERAL                              | INTERRUP      | T ENABLE      | REGISTE      | R 2 (ADD  | RESS 8DI     | ו)     |

|---------------|---------------------------|---------------------------------------|---------------|---------------|--------------|-----------|--------------|--------|

|               | R/W-0                     | R/W-0                                 | U-0           | R/W-0         | U-0          | U-0       | U-0          | U-0    |

|               | OSFIE                     | CMIE                                  | —             | EEIE          | —            | —         |              | _      |

|               | bit 7                     |                                       |               |               |              |           |              | bit 0  |

| bit 7         | OSFIE: Os                 | cillator Fail In                      | terrupt Enab  | le bit        |              |           |              |        |

|               | 1 = Enable<br>0 = Disable |                                       |               |               |              |           |              |        |

| bit 6         | CMIE: Corr                | CMIE: Comparator Interrupt Enable bit |               |               |              |           |              |        |

|               | 1 = Enabled               |                                       |               |               |              |           |              |        |

|               | 0 = Disable               |                                       |               |               |              |           |              |        |

| bit 5         | Unimplem                  | ented: Read                           | <b>as</b> '0' |               |              |           |              |        |

| bit 4         | EEIE: EEP                 | ROM Write C                           | peration Inte | errupt Enable | bit          |           |              |        |

|               | 1 = Enable<br>0 = Disable |                                       |               |               |              |           |              |        |

| bit 3-0       | Unimplem                  | ented: Read                           | <b>as</b> '0' |               |              |           |              |        |

|               |                           |                                       |               |               |              |           |              |        |

|               | Legend:                   |                                       |               |               |              |           |              |        |

|               | R = Reada                 | ble bit                               | W = W         | ritable bit   | U = Unimp    | olemented | bit, read as | '0'    |

|               | -n = Value                | at POR                                | '1' = Bi      | t is set      | '0' = Bit is | cleared   | x = Bit is u | nknown |

#### 4.6.3 CLOCK TRANSITION AND WDT

When clock switching is performed, the Watchdog Timer is disabled because the Watchdog ripple counter is used as the Oscillator Start-up Timer.

Once the clock transition is complete (i.e., new oscillator selection switch has occurred), the Watchdog counter is re-enabled with the counter reset. This allows the user to synchronize the Watchdog Timer to the start of execution at the new clock frequency.

| Note: | The OST is only used when switching to |

|-------|----------------------------------------|

|       | XT, HS and LP Oscillator modes.        |

#### REGISTER 4-2: OSCCON: OSCILLATOR CONTROL REGISTER (ADDRESS 8Fh)

| U-0   | R/W-0 | R/W-0 | R/W-0 | R-0                 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|---------------------|-------|-------|-------|

| -     | IRCF2 | IRCF1 | IRCF0 | OSTS <sup>(1)</sup> | IOFS  | SCS1  | SCS0  |

| bit 7 |       |       |       |                     |       |       | bit 0 |

- bit 7 Unimplemented: Read as '0'

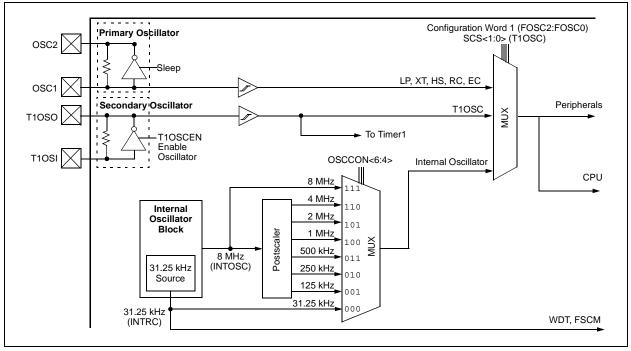

- bit 6-4 IRCF<2:0>: Internal RC Oscillator Frequency Select bits

- 000 = 31.25 kHz

- 001 = 125 kHz

- 010 = 250 kHz

- 011 = 500 kHz

- 100 = 1 MHz

- 101 = 2 MHz

- 110 = 4 MHz

- 111 = 8 MHz

#### bit 3 **OSTS:** Oscillator Start-up Time-out Status bit<sup>(1)</sup>

- 1 = Device is running from the primary system clock

- 0 = Device is running from T1OSC or INTRC as a secondary system clock

- Note 1: Bit resets to '0' with Two-Speed Start-up mode and LP, XT or HS selected as the oscillator mode.

- bit 2 **IOFS:** INTOSC Frequency Stable bit

- 1 = Frequency is stable

- 0 = Frequency is not stable

- bit 1-0 SCS<1:0>: Oscillator Mode Select bits

- 00 = Oscillator mode defined by FOSC<2:0>

- 01 = T1OSC is used for system clock

- 10 = Internal RC is used for system clock

- 11 = Reserved

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 4.6.4 MODIFYING THE IRCF BITS

The IRCF bits can be modified at any time regardless of which clock source is currently being used as the system clock. The internal oscillator allows users to change the frequency during run time. This is achieved by modifying the IRCF bits in the OSCCON register. The sequence of events that occur after the IRCF bits are modified is dependent upon the initial value of the IRCF bits before they are modified. If the INTRC (31.25 kHz, IRCF < 2:0 > = 000) is running and the IRCF bits are modified to any other value than '000', a 4 ms (approx.) clock switch delay is turned on. Code execution continues at a higher than expected frequency while the new frequency stabilizes. Time sensitive code should wait for the IOFS bit in the OSCCON register to become set before continuing. This bit can be monitored to ensure that the frequency is stable before using the system clock in time critical applications.

If the IRCF bits are modified while the internal oscillator is running at any other frequency than INTRC (31.25 kHz, IRCF<2:0>  $\neq$  000), there is no need for a 4 ms (approx.) clock switch delay. The new INTOSC frequency will be stable immediately after the **eight** falling edges. The IOFS bit will remain set after clock switching occurs.

| Note: | Caution must be taken when modifying the    |

|-------|---------------------------------------------|

|       | IRCF bits using BCF or BSF instructions. It |

|       | is possible to modify the IRCF bits to a    |

|       | frequency that may be out of the VDD spec-  |

|       | ification range; for example, VDD = 2.0V    |

|       | and IRCF = 111 (8 MHz).                     |

#### 4.6.5 CLOCK TRANSITION SEQUENCE

Following are three different sequences for switching the internal RC oscillator frequency.

- Clock before switch: 31.25 kHz (IRCF<2:0> = 000)

- 1. IRCF bits are modified to an INTOSC/INTOSC postscaler frequency.

- The clock switching circuitry waits for a falling edge of the current clock, at which point CLKO is held low.

- 3. The clock switching circuitry then waits for eight falling edges of requested clock, after which it switches CLKO to this new clock source.

- The IOFS bit is clear to indicate that the clock is unstable and a 4 ms (approx.) delay is started. Time dependent code should wait for IOFS to become set.

- 5. Switchover is complete.

- Clock before switch: One of INTOSC/INTOSC postscaler (IRCF<2:0> ≠ 000)

- 1. IRCF bits are modified to INTRC (IRCF<2:0> = 000).

- 2. The clock switching circuitry waits for a falling edge of the current clock, at which point CLKO is held low.

- 3. The clock switching circuitry then waits for eight falling edges of requested clock, after which it switches CLKO to this new clock source.

- 4. Oscillator switchover is complete.

#### 4.7 **Power-Managed Modes**

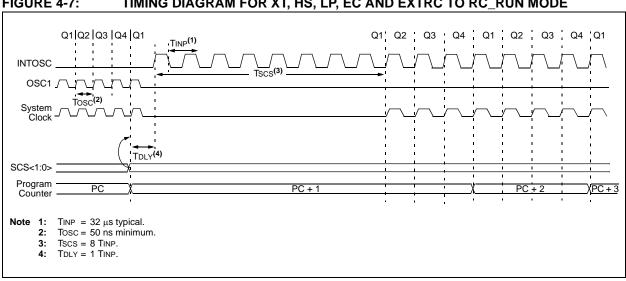

#### 4.7.1 RC RUN MODE

When SCS bits are configured to run from the INTRC, a clock transition is generated if the system clock is not already using the INTRC. The event will clear the OSTS bit, switch the system clock from the primary system clock (if SCS < 1:0 > = 0.0) determined by the value contained in the configuration bits, or from the T1OSC (if SCS<1:0> = 01) to the INTRC clock option and shut down the primary system clock to conserve power. Clock switching will not occur if the primary system clock is already configured as INTRC.

If the system clock does not come from the INTRC (31.25 kHz) when the SCS bits are changed and the IRCF bits in the OSCCON register are configured for a frequency other than INTRC, the frequency may not be stable immediately. The IOFS bit (OSCCON<2>) will be set when the INTOSC or postscaler frequency is stable, after 4 ms (approx.).

After a clock switch has been executed, the OSTS bit is cleared, indicating a low-power mode and the device does not run from the primary system clock. The internal Q clocks are held in the Q1 state until eight falling edge clocks are counted on the INTRC oscillator. After the eight clock periods have transpired, the clock input to the Q clocks is released and operation resumes (see Figure 4-7).

#### FIGURE 4-7: TIMING DIAGRAM FOR XT, HS, LP, EC AND EXTRC TO RC\_RUN MODE

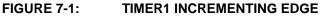

### 7.2 Timer1 Operation in Timer Mode

Timer mode is selected by clearing the TMR1CS (T1CON<1>) bit. In this mode, the input clock to the timer is FOSC/4. The synchronize control bit, T1SYNC (T1CON<2>), has no effect since the internal clock is always in sync.

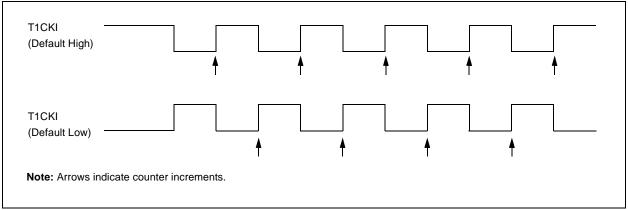

#### 7.3 Timer1 Counter Operation

Timer1 may operate in Asynchronous or Synchronous mode, depending on the setting of the TMR1CS bit.

When Timer1 is being incremented via an external source, increments occur on a rising edge. After Timer1 is enabled in Counter mode, the module must first have a falling edge before the counter begins to increment.

#### 7.4 Timer1 Operation in Synchronized Counter Mode

Counter mode is selected by setting bit TMR1CS. In this mode, the timer increments on every rising edge of clock input on pin RB7/PGD/T1OSI when bit T1OSCEN is set, or on pin RB6/PGC/T1OSO/T1CKI when bit T1OSCEN is cleared.

If  $\overline{\text{T1SYNC}}$  is cleared, then the external clock input is synchronized with internal phase clocks. The synchronization is done after the prescaler stage. The prescaler stage is an asynchronous ripple counter.

In this configuration, during Sleep mode, Timer1 will not increment even if the external clock is present since the synchronization circuit is shut off. The prescaler, however, will continue to increment.

| REGISTER 10-2: | SSPCON:                       | SYNCHR                | ONOUS SER                                      | IAL PORT                 | CONTROL         | REGISTE      | R (ADDRE      | SS 14h)      |

|----------------|-------------------------------|-----------------------|------------------------------------------------|--------------------------|-----------------|--------------|---------------|--------------|

|                | R/W-0                         | R/W-0                 | R/W-0                                          | R/W-0                    | R/W-0           | R/W-0        | R/W-0         | R/W-0        |

|                | WCOL                          | SSPOV                 | SSPEN <sup>(1)</sup>                           | CKP                      | SSPM3           | SSPM2        | SSPM1         | SSPM0        |

|                | bit 7                         |                       |                                                |                          |                 |              |               | bit 0        |

| bit 7          | WCOL: W                       | rite Collisior        | Detect bit                                     |                          |                 |              |               |              |

|                |                               |                       | e the SSPBUF                                   | -<br>register fai        | led because     | the SSP m    | odule is bu   | sy           |

|                | (must                         | be cleared            | in software)                                   | C C                      |                 |              |               |              |

|                | 0 = No col                    |                       | <b>a b b c</b>                                 |                          |                 |              |               |              |

| bit 6          | In SPI mod                    |                       | rflow Indicator                                | Dit                      |                 |              |               |              |

|                |                               |                       | eived while the                                | SSPBUF re                | aister is still | holdina the  | previous da   | ata. In case |

|                | of ove                        | rflow, the d          | ata in SSPSR                                   | is lost. Ove             | rflow can or    | ly occur in  | Slave mode    | e. The user  |

|                |                               |                       | PBUF, even if                                  |                          |                 |              |               |              |

|                |                               |                       | w bit is not se<br>SPBUF regist                |                          | i new recep     | uon (and tra | ansmission)   | is initiated |

|                | 0 = No over                   | erflow                | 0                                              |                          |                 |              |               |              |

|                | In I <sup>2</sup> C mod       |                       |                                                |                          |                 | r            |               | 00001/-      |

|                | •                             |                       | while the SSI                                  | •                        |                 | • .          | •             |              |

|                | 0 = No over                   |                       |                                                |                          |                 |              |               |              |

| bit 5          | SSPEN: S                      | ynchronous            | Serial Port Er                                 | nable bit <sup>(1)</sup> |                 |              |               |              |

|                | In SPI mod                    |                       |                                                |                          |                 |              |               |              |

|                |                               |                       | t and configure<br>rt and configur             |                          |                 |              | t pins        |              |

|                | In I <sup>2</sup> C mod       | -                     | it and coningui                                | es triese pir            | 13 a3 1/0 p01   | t pins       |               |              |

|                | 1 = Enable                    | es the serial         | port and confi                                 |                          |                 |              | rial port pin | 5            |

|                |                               | -                     | rt and configur                                |                          |                 | -            |               |              |

|                | Note 1:                       | In both mo<br>output. | odes, when en                                  | abled, these             | e pins must l   | be properly  | configured    | as input or  |

| bit 4          |                               | k Polarity S          | elect bit                                      |                          |                 |              |               |              |

|                | In SPI mod                    |                       | on falling edge                                | , receive or             | ricina odao     | Idlo ototo f | or clock is c | high loval   |

|                |                               |                       | on rising edge                                 |                          |                 |              |               |              |

|                | <u>In I<sup>2</sup>C Slav</u> | <u>e mode:</u>        |                                                |                          |                 |              |               |              |

|                | SCK release                   |                       |                                                |                          |                 |              |               |              |

|                | 1 = Enable<br>0 = Holds (     |                       | lock stretch). (                               | Used to ens              | sure data set   | up time.)    |               |              |

| bit 3-0        | SSPM<3:0                      | >: Synchro            | nous Serial Po                                 | ort Mode Se              | lect bits       | . ,          |               |              |

|                |                               |                       | ode, clock = O                                 |                          |                 |              |               |              |

|                |                               |                       | ode, clock = O<br>ode, clock = O               |                          |                 |              |               |              |

|                |                               |                       | ode, clock = O<br>ode, clock = Tl              |                          | 2               |              |               |              |

|                | 0100 = SP                     | I Slave mo            | de, clock = SC                                 | K pin. SS pi             | in control en   |              |               |              |

|                |                               |                       | de, clock = SC<br>le, 7-bit addre              |                          | n control dis   | abled. SS c  | an be used    | as I/O pin.  |

|                |                               |                       | de, 7-bit addres                               |                          |                 |              |               |              |

|                | $1011 = I^2C$                 | Firmware              | Controlled Ma                                  | ster mode (              |                 |              |               |              |

|                |                               |                       | le, 7-bit addres                               |                          |                 |              |               |              |

|                |                               |                       | <b>le, 10-bit addr</b><br>L00, 1101 <b>=</b> R |                          | n anu stop i    |              |               |              |

|                |                               | ,,                    | .,                                             |                          |                 |              |               |              |

|                | Legend:                       |                       |                                                |                          |                 |              |               |              |

|                | R = Reada                     | ble bit               | W = W                                          | ritable bit              | U = Unim        | plemented    | bit, read as  | '0'          |

| Legena.           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

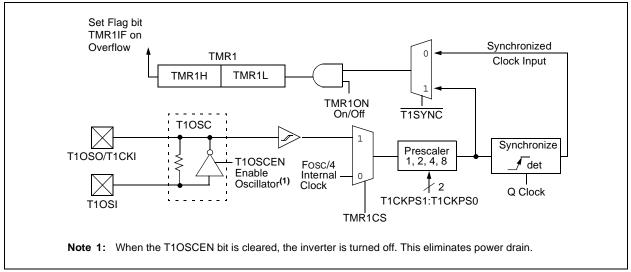

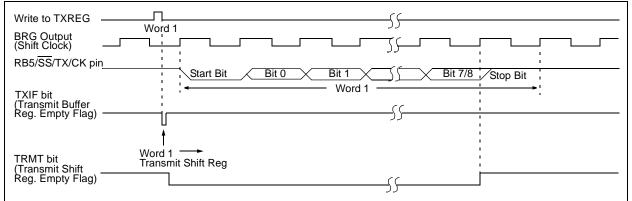

When setting up an asynchronous transmission, follow these steps:

- Initialize the SPBRG register for the appropriate baud rate. If a high-speed baud rate is desired, set bit BRGH (Section 11.1 "AUSART Baud Rate Generator (BRG)").

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set transmit bit TX9.

- 5. Enable the transmission by setting bit TXEN which will also set bit TXIF.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Load data to the TXREG register (starts transmission).

- 8. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

#### FIGURE 11-2: ASYNCHRONOUS MASTER TRANSMISSION

#### FIGURE 11-3: ASYNCHRONOUS MASTER TRANSMISSION (BACK TO BACK)

#### TABLE 11-7: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| 0000 x0 | 000u                                                                                              |

|---------|---------------------------------------------------------------------------------------------------|

|         |                                                                                                   |

| 00 -000 | 0000                                                                                              |

| 0000 xC | 000x                                                                                              |

| 00 0000 | 0000                                                                                              |

| 00 -000 | 0000                                                                                              |

| 10 0000 | -010                                                                                              |

| 00 0000 | 0000                                                                                              |

|         | DOX         0000           DOO         0000           DOO         -000           DOO         0000 |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous transmission.

Note 1: This bit is only implemented on the PIC16F88. The bit will read '0' on the PIC16F87.

## 13.0 COMPARATOR MODULE

The comparator module contains two analog comparators. The inputs to the comparators are multiplexed with I/O port pins RA0 through RA3, while the outputs are multiplexed to pins RA3 and RA4. The on-chip Voltage Reference (Section 14.0 "Comparator Voltage Reference Module") can also be an input to the comparators.

The CMCON register (Register 13-1) controls the comparator input and output multiplexors. A block diagram of the various comparator configurations is shown in Figure 13-1.

| REGISTER 13-1: | CMCON: COMPARATOR MODULE CONTROL REGISTER (ADDRESS 9Ch) |

|----------------|---------------------------------------------------------|

|----------------|---------------------------------------------------------|

|         | R-0                                                                 | R-0                                             | R/W-0        | R/W-0      | R/W-0      | R/W-1     | R/W-1          | R/W-1 |  |

|---------|---------------------------------------------------------------------|-------------------------------------------------|--------------|------------|------------|-----------|----------------|-------|--|

|         | C2OUT                                                               | C10UT                                           | C2INV        | C1INV      | CIS        | CM2       | CM1            | CM0   |  |

|         | bit 7                                                               |                                                 |              |            | •          |           |                | bit 0 |  |

| bit 7   | C2OUT: Con<br>When C2INV                                            | -                                               | Output bit   |            |            |           |                |       |  |

|         | 1 = C2 VIN+<br>0 = C2 VIN+                                          | > C2 VIN-                                       |              |            |            |           |                |       |  |

|         | <u>When C2INV</u><br>1 = C2 VIN+                                    | < C2 VIN-                                       |              |            |            |           |                |       |  |

|         | 0 = C2 VIN+                                                         |                                                 |              |            |            |           |                |       |  |

| bit 6   | C1OUT: Con                                                          | •                                               | output bit   |            |            |           |                |       |  |

|         | <u>When C1INV</u><br>1 = C1 VIN+<br>0 = C1 VIN+                     | > C1 VIN-                                       |              |            |            |           |                |       |  |

|         | <u>When C1INV</u><br>1 = C1 VIN+<br>0 = C1 VIN+                     | <u>/ = 1:</u><br>< C1 Vin-                      |              |            |            |           |                |       |  |

| bit 5   | C2INV: Com                                                          | C2INV: Comparator 2 Output Inversion bit        |              |            |            |           |                |       |  |

|         | 1 = C2 outpu<br>0 = C2 outpu                                        | it inverted                                     | -            |            |            |           |                |       |  |

| bit 4   | C1INV: Com                                                          | parator 1 Ou                                    | utput Invers | ion bit    |            |           |                |       |  |

|         | 1 = C1 outpu<br>0 = C1 outpu                                        |                                                 | ed           |            |            |           |                |       |  |

| bit 3   | CIS: Compare<br><u>When CM2:C</u><br>1 = C1 VIN- c<br>0 = C1 VIN- c | CMO = 001:                                      | RA3          |            |            |           |                |       |  |

|         | 0 = C1 VIN- 0                                                       | connects to I<br>connects to I<br>connects to I | RA2<br>RA0   |            |            |           |                |       |  |

| bit 2-0 |                                                                     | connects to I                                   |              |            |            |           |                |       |  |

| DIL 2-0 | <b>CM&lt;2:0&gt;:</b> C                                             |                                                 |              |            |            |           |                |       |  |

|         | Legend:                                                             |                                                 |              |            |            |           |                |       |  |

|         | R = Readabl                                                         | e bit                                           | W = Wr       | itable bit | U = Unimpl | emented b | it, read as '  | 0'    |  |

|         | 1                                                                   |                                                 |              |            |            |           | <b>—</b> · · · |       |  |

'1' = Bit is set

'0' = Bit is cleared

-n = Value at POR

x = Bit is unknown

#### 13.7 Comparator Operation During Sleep

When a comparator is active and the device is placed in Sleep mode, the comparator remains active and the interrupt is functional, if enabled. This interrupt will wake-up the device from Sleep mode when enabled. While the comparator is powered up, higher Sleep currents than shown in the power-down current specification will occur. Each operational comparator will consume additional current, as shown in the comparator specifications. To minimize power consumption while in Sleep mode, turn off the comparators, CM<2:0> = 111, before entering Sleep. If the device wakes up from Sleep, the contents of the CMCON register are not affected.

### 13.8 Effects of a Reset

A device Reset forces the CMCON register to its Reset state, causing the comparator module to be in the Comparator Off mode, CM<2:0> = 111.

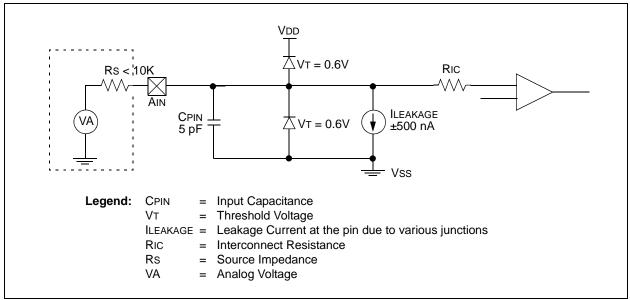

### 13.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 13-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up condition may occur. A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

#### FIGURE 13-4: ANALOG INPUT MODEL

# PIC16F87/88

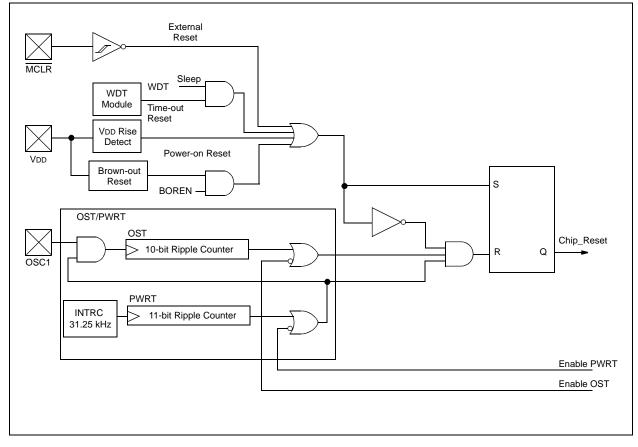

### 15.2 Reset

The PIC16F87/88 differentiates between various kinds of Reset:

- Power-on Reset (POR)

- MCLR Reset during normal operation

- MCLR Reset during Sleep

- WDT Reset during normal operation

- WDT wake-up during Sleep

- Brown-out Reset (BOR)

Some registers are not affected in any Reset condition. Their status is unknown on POR and unchanged in any other Reset. Most other registers are reset to a "Reset state" on Power-on Reset (POR), on the MCLR and WDT Reset, on MCLR Reset during Sleep and Brownout Reset (BOR). They are not affected by a WDT wake-up which is viewed as the resumption of normal operation. The TO and PD bits are set or cleared differently in different Reset situations, as indicated in Table 15-3. These bits are used in software to determine the nature of the Reset. Upon a POR, BOR or wake-up from Sleep, the CPU requires approximately 5-10  $\mu$ s to become ready for code execution. This delay runs in parallel with any other timers. See Table 15-4 for a full description of Reset states of all registers.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 15-1.

#### FIGURE 15-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

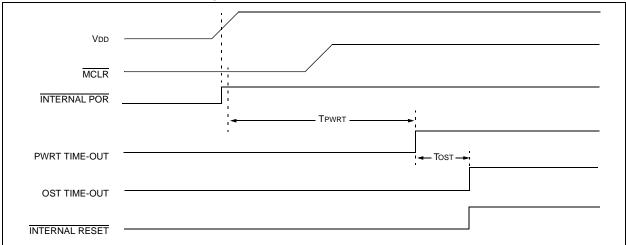

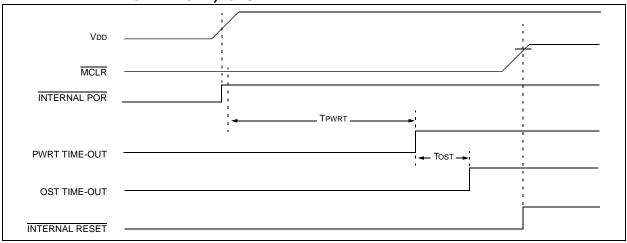

#### FIGURE 15-5: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD THROUGH RC NETWORK): CASE 2

# PIC16F87/88

| SUBLW            | Subtract W from Literal                                                                                                        | XORLW            | Exclusive OR Literal with W                                                                                              |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] SUBLW k                                                                                                       | Syntax:          | [label] XORLW k                                                                                                          |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                              | Operands:        | $0 \leq k \leq 255$                                                                                                      |  |  |  |

| Operation:       | $k - (W) \rightarrow (W)$                                                                                                      | Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                            |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                       | Status Affected: | Z                                                                                                                        |  |  |  |

| Description:     | The W register is subtracted (two's complement method) from the eight-bit literal 'k'. The result is placed in the W register. | Description:     | The contents of the W registern<br>are XOR'ed with the eight-bit<br>literal 'k'. The result is placed<br>the W register. |  |  |  |

| SUBWF            | Subtract W from f                                                                                                                                                                       | XORWF            | Exclusive OR W with f                                                                                                                                                     |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [label] SUBWF f,d                                                                                                                                                                       | Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                                                |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                             | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                         |  |  |

| Operation:       | (f) – (W) $\rightarrow$ (destination)                                                                                                                                                   | Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                 |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                                | Status Affected: | Z                                                                                                                                                                         |  |  |

| Description:     | Subtract (two's complement<br>method) W register from register 'f'.<br>If 'd' = 0, the result is stored in the<br>W register. If 'd' = 1, the result is<br>stored back in register 'f'. | Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' = 0, the result is stored in the W register. If 'd' = 1, the result is stored back in register 'f'. |  |  |

| SWAPF            | Swap Nibbles in f                                                                                                                                            |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] SWAPF f,d                                                                                                                                   |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                            |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                      |

| Status Affected: | None                                                                                                                                                         |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' = 0, the result is placed in W register. If 'd' = 1, the result is placed in register 'f'. |

DS30487D-page 156

### 18.2 DC Characteristics: Power-Down and Supply Current PIC16F87/88 (Industrial, Extended) PIC16LF87/88 (Industrial) (Continued)

| PIC16LF8<br>(Indus |                                                                                                                                                                                         | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |     |       |            |            |                                  |  |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|-------|------------|------------|----------------------------------|--|

| PIC16F87<br>(Indus | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |                                                                                                                                    |     |       |            |            |                                  |  |

| Param<br>No.       | Device                                                                                                                                                                                  | Тур                                                                                                                                | Max | Units | Conditions |            |                                  |  |

|                    | Supply Current (IDD) <sup>(2,3)</sup>                                                                                                                                                   |                                                                                                                                    |     |       |            |            |                                  |  |

|                    | All devices                                                                                                                                                                             | 1.8                                                                                                                                | 2.3 | mA    | -40°C      |            |                                  |  |

|                    |                                                                                                                                                                                         | 1.6                                                                                                                                | 2.2 | mA    | +25°C      | VDD = 4.0V |                                  |  |

|                    |                                                                                                                                                                                         | 1.3                                                                                                                                | 2.2 | mA    | +85°C      |            |                                  |  |

|                    | All devices                                                                                                                                                                             | 3.0                                                                                                                                | 4.2 | mA    | -40°C      |            | Fosc = 20 MHz<br>(HS Oscillator) |  |

|                    |                                                                                                                                                                                         | 2.5                                                                                                                                | 4.0 | mA    | +25°C      | VDD = 5.0V |                                  |  |

|                    |                                                                                                                                                                                         | 2.5                                                                                                                                | 4.0 | mA    | +85°C      | vuu = 5.0v |                                  |  |

|                    | Extended devices                                                                                                                                                                        | 3.0                                                                                                                                | 5.0 | mA    | +85°C      |            |                                  |  |

Legend: Shading of rows is to assist in readability of the table.

**Note 1:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or VSS and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

$\frac{OSC1}{MCLR}$  = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;  $\frac{MCLR}{MCLR}$  = VDD; WDT enabled/disabled as specified.

**3:** For RC oscillator configurations, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

## 18.2 DC Characteristics: Power-Down and Supply Current PIC16F87/88 (Industrial, Extended) PIC16LF87/88 (Industrial) (Continued)

| PIC16LF87/88<br>(Industrial)          |                                       |                                                      | rd Oper |    |        | ss otherwise state<br>$A \le +85^{\circ}C$ for indus |                                           |  |

|---------------------------------------|---------------------------------------|------------------------------------------------------|---------|----|--------|------------------------------------------------------|-------------------------------------------|--|

| PIC16F87/88<br>(Industrial, Extended) |                                       | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |         |    |        |                                                      |                                           |  |

| Param<br>No.                          | Тур                                   | Max                                                  | Units   |    | Condi  | tions                                                |                                           |  |

|                                       | Supply Current (IDD) <sup>(2,3)</sup> |                                                      |         |    |        |                                                      |                                           |  |

|                                       | PIC16LF87/88                          | 8                                                    | 20      | μA | -40°C  |                                                      |                                           |  |

|                                       |                                       | 7                                                    | 15      | μA | +25°C  | VDD = 2.0V                                           |                                           |  |

|                                       |                                       | 7                                                    | 15      | μΑ | +85°C  |                                                      |                                           |  |

|                                       | PIC16LF87/88                          | 16                                                   | 30      | μΑ | -40°C  |                                                      |                                           |  |

|                                       |                                       | 14                                                   | 25      | μΑ | +25°C  | VDD = 3.0V                                           | Fosc = 31.25 kHz<br>( <b>RC RUN</b> mode, |  |

|                                       |                                       | 14                                                   | 25      | μA | +85°C  |                                                      | Internal RC Oscillator)                   |  |

|                                       | All devices                           | 32                                                   | 40      | μΑ | -40°C  |                                                      | ,<br>,                                    |  |

|                                       |                                       | 29                                                   | 35      | μΑ | +25°C  |                                                      |                                           |  |

|                                       |                                       | 29                                                   | 35      | μA | +85°C  | VDD = 0.0V                                           |                                           |  |

|                                       | Extended devices                      | 35                                                   | 45      | μΑ | +125°C |                                                      |                                           |  |

|                                       | PIC16LF87/88                          | 132                                                  | 160     | μΑ | -40°C  | _                                                    |                                           |  |

|                                       |                                       | 126                                                  | 155     | μΑ | +25°C  | VDD = 2.0V                                           |                                           |  |

|                                       |                                       | 126                                                  | 155     | μA | +85°C  |                                                      |                                           |  |

|                                       | PIC16LF87/88                          | 260                                                  | 310     | μΑ | -40°C  |                                                      |                                           |  |

|                                       |                                       | 230                                                  | 300     | μΑ | +25°C  | VDD = 3.0V                                           | Fosc = 1 MHz<br>( <b>RC RUN</b> mode,     |  |

|                                       |                                       | 230                                                  | 300     | μΑ | +85°C  |                                                      | Internal RC Oscillator)                   |  |

|                                       | All devices                           | 560                                                  | 690     | μΑ | -40°C  |                                                      |                                           |  |

|                                       |                                       | 500                                                  | 650     | μΑ | +25°C  | VDD = 5.0V                                           |                                           |  |

|                                       |                                       | 500<br>570                                           | 650     | μΑ | +85°C  | VDD - 0.0V                                           |                                           |  |

|                                       | Extended devices                      |                                                      | 710     | μA | +125°C |                                                      |                                           |  |

Legend: Shading of rows is to assist in readability of the table.

**Note 1:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or VSs and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;

- MCLR = VDD; WDT enabled/disabled as specified.

- 3: For RC oscillator configurations, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

18.4

### DC Characteristics: PIC16F87/88 (Industrial, Extended) PIC16LF87/88 (Industrial) (Continued)

|              | ARACT | ERISTICS                                   | Operating temp<br>Operating volta | perature<br>age VDD | -40°<br>-40°<br>range as | $C \le TA \le C \le TA \le C \le TA \le C$ descrit | ss otherwise stated)<br>≤ +85°C for industrial<br>≤ +125°C for extended<br>bed in DC Specification,<br>pply Voltage". |

|--------------|-------|--------------------------------------------|-----------------------------------|---------------------|--------------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Param<br>No. | Sym   | Characteristic                             | Min                               | Тур†                | Max                      | Units                                              | Conditions                                                                                                            |

|              | Vol   | Output Low Voltage                         |                                   |                     |                          |                                                    |                                                                                                                       |

| D080         |       | I/O ports                                  | —                                 | —                   | 0.6                      | V                                                  | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +125°C                                                                          |

| D083         |       | OSC2/CLKO<br>(RC oscillator configuration) | _                                 | -                   | 0.6                      | V                                                  | IOL = 1.6 mA, VDD = 4.5V,<br>-40°C to +125°C                                                                          |

|              | Vон   | Output High Voltage                        | •                                 |                     |                          |                                                    |                                                                                                                       |

| D090         |       | I/O ports (Note 3)                         | VDD - 0.7                         | -                   | _                        | V                                                  | IOH = -3.0 mA, VDD = 4.5V,<br>-40°С to +125°С                                                                         |

| D092         |       | OSC2/CLKO<br>(RC oscillator configuration) | Vdd - 0.7                         | —                   | —                        | V                                                  | IOH = -1.3 mA, VDD = 4.5V,<br>-40°С to +125°С                                                                         |

|              |       | Capacitive Loading Specs on                | Output Pins                       |                     |                          |                                                    |                                                                                                                       |

| D100         | Cosc2 | OSC2 pin                                   | _                                 | —                   | 15                       | pF                                                 | In XT, HS and LP modes<br>when external clock is used<br>to drive OSC1                                                |

| D101         | Сю    | All I/O pins and OSC2<br>(in RC mode)      | —                                 | -                   | 50                       | pF                                                 |                                                                                                                       |

| D102         | Св    | SCL, SDA in I <sup>2</sup> C™ mode         | —                                 | —                   | 400                      | pF                                                 |                                                                                                                       |

|              |       | Data EEPROM Memory                         | •                                 |                     |                          |                                                    |                                                                                                                       |

| D120         | ED    | Endurance                                  | 100K<br>10K                       | 1M<br>100K          | _                        | E/W<br>E/W                                         | -40°C to 85°C<br>+85°C to +125°C                                                                                      |

| D121         | Vdrw  | VDD for Read/Write                         | Vmin                              | -                   | 5.5                      | V                                                  | Using EECON to read/write,<br>VMIN = min. operating voltage                                                           |

| D122         | TDEW  | Erase/Write Cycle Time                     | —                                 | 4                   | 8                        | ms                                                 |                                                                                                                       |

|              |       | Program Flash Memory                       |                                   |                     |                          |                                                    |                                                                                                                       |

| D130         | Eр    | Endurance                                  | 10K<br>1K                         | 100K<br>10K         | _                        | E/W<br>E/W                                         | -40°C to 85°C<br>+85°C to +125°C                                                                                      |

| D131         | Vpr   | VDD for Read                               | Vmin                              | —                   | 5.5                      | V                                                  |                                                                                                                       |

| D132A        |       | VDD for Erase/Write                        | Vmin                              | —                   | 5.5                      | V                                                  | Using EECON to read/write,<br>VMIN = min. operating voltage                                                           |

| D133         | TPE   | Erase Cycle Time                           | —                                 | 2                   | 4                        | ms                                                 |                                                                                                                       |

| D134         | TPW   | Write Cycle Time                           | —                                 | 2                   | 4                        | ms                                                 |                                                                                                                       |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1/CLKI pin is a Schmitt Trigger input. It is not recommended that the PIC16F87/88 be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

# PIC16F87/88

| Param<br>No. | Symbol   | Charac                                | Min                   | Тур†       | Max | Units        | Conditions |          |

|--------------|----------|---------------------------------------|-----------------------|------------|-----|--------------|------------|----------|

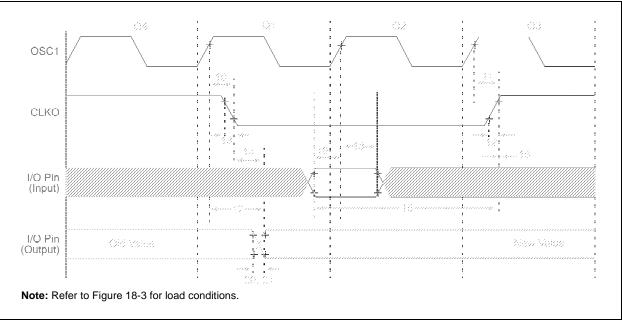

| 10*          | TosH2ckL | OSC1 ↑ to CLKO ↓                      |                       | —          | 75  | 200          | ns         | (Note 1) |

| 11*          | TosH2ckH | OSC1 ↑ to CLKO ↑                      |                       | —          | 75  | 200          | ns         | (Note 1) |

| 12*          | TckR     | CLKO Rise Time                        |                       | —          | 35  | 100          | ns         | (Note 1) |

| 13*          | TckF     | CLKO Fall Time                        |                       | _          | 35  | 100          | ns         | (Note 1) |

| 14*          | TckL2ioV | CLKO ↓ to Port Out Valid              |                       | —          | _   | 0.5 TCY + 20 | ns         | (Note 1) |

| 15*          | TioV2ckH | Port In Valid before CLKC             | )↑                    | Tosc + 200 | —   | —            | ns         | (Note 1) |

| 16*          | TckH2iol | Port In Hold after CLKO ↑             | 0                     | _          | —   | ns           | (Note 1)   |          |

| 17*          | TosH2ioV | OSC1 ↑ (Q1 cycle) to Por              | _                     | 100        | 255 | ns           |            |          |

| 18*          | TosH2iol | OSC1 ↑ (Q2 cycle) to                  | PIC16 <b>F</b> 87/88  | 100        | —   | —            | ns         |          |

|              |          | Port Input Invalid (I/O in hold time) | PIC16 <b>LF</b> 87/88 | 200        | —   | —            | ns         |          |

| 19*          | TioV2osH | Port Input Valid to OSC1              | ↑ (I/O in setup time) | 0          | _   | —            | ns         |          |

| 20*          | TIOR     | Port Output Rise Time                 | PIC16 <b>F</b> 87/88  | _          | 10  | 40           | ns         |          |

|              |          |                                       | PIC16 <b>LF</b> 87/88 | —          | _   | 145          | ns         |          |

| 21*          | TIOF     | Port Output Fall Time                 | PIC16 <b>F</b> 87/88  | _          | 10  | 40           | ns         |          |

|              |          |                                       | PIC16 <b>LF</b> 87/88 | —          | _   | 145          | ns         |          |

| 22††*        | TINP     | INT Pin High or Low Time              | Тсү                   | —          | —   | ns           |            |          |

| 23††*        | Trbp     | RB7:RB4 Change INT Hig                | gh or Low Time        | Тсү        | —   | —            | ns         |          |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

t These parameters are asynchronous events not related to any internal clock edges.

**Note 1:** Measurements are taken in RC mode where CLKO output is 4 x Tosc.

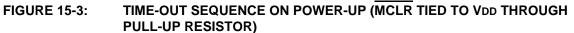

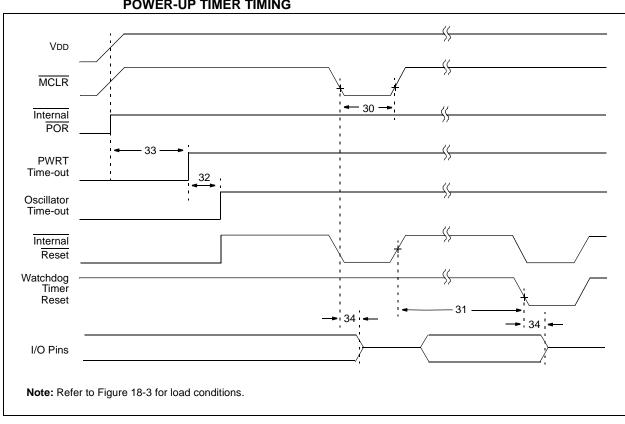

# FIGURE 18-6: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

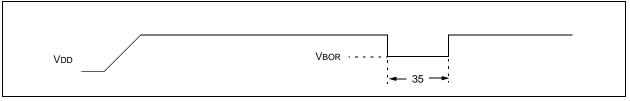

#### FIGURE 18-7: BROWN-OUT RESET TIMING

# TABLE 18-5:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER<br/>AND BROWN-OUT RESET REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                                                                   | Min  | Тур†      | Max  | Units | Conditions               |

|------------------|-------|----------------------------------------------------------------------------------|------|-----------|------|-------|--------------------------|

| 30               | TmcL  | MCLR Pulse Width (Low)                                                           | 2    | _         | —    | μS    | VDD = 5V, -40°C to +85°C |

| 31*              | Twdt  | Watchdog Timer Time-out Period<br>(16-bit prescaler = 0100 and no<br>postscaler) | 13.6 | 16        | 18.4 | ms    | VDD = 5V, -40°C to +85°C |

| 32               | Tost  | Oscillation Start-up Timer Period                                                | _    | 1024 Tosc | —    | —     | Tosc = OSC1 period       |

| 33*              | TPWRT | Power-up Timer Period                                                            | 61.2 | 72        | 82.8 | ms    | VDD = 5V, -40°C to +85°C |