## E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 16                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 368 x 8                                                                  |

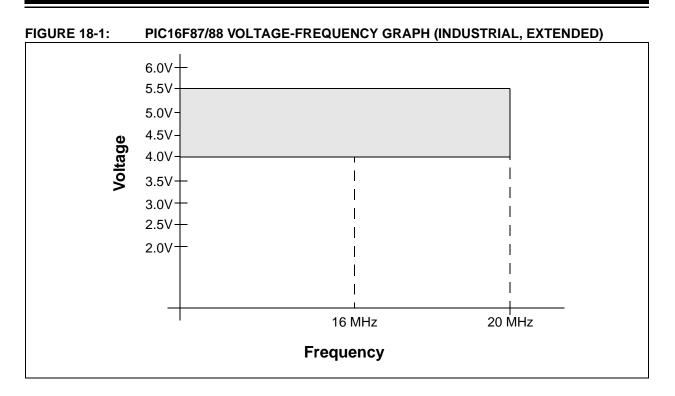

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | A/D 7x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                           |

| Supplier Device Package    | 20-SSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f88t-i-ss |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.2.2.7 PIR2 Register

The PIR2 register contains the flag bit for the EEPROM write operation interrupt.

| Note: | Interrupt flag bits are set when an interrupt |  |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|--|

|       | condition occurs, regardless of the state of  |  |  |  |  |  |

|       | its corresponding enable bit, or the global   |  |  |  |  |  |

|       | enable bit, GIE (INTCON<7>). User             |  |  |  |  |  |

|       | software should ensure the appropriate        |  |  |  |  |  |

|       | interrupt flag bits are clear prior to        |  |  |  |  |  |

|       | enabling an interrupt.                        |  |  |  |  |  |

#### REGISTER 2-7: PIR2: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 2 (ADDRESS 0Dh)

| R/W-0 | R/W-0 | U-0 | R/W-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|-----|-------|-----|-----|-----|-------|

| OSFIF | CMIF  | —   | EEIF  | —   | —   | —   | —     |

| bit 7 |       |     |       |     |     |     | bit 0 |

| bit 7   | <b>OSFIF:</b> Oscillator Fail Interrupt Flag bit<br>1 = System oscillator failed, clock input has changed to INTRC (must be cleared in software)<br>0 = System clock operating |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | CMIF: Comparator Interrupt Flag bit                                                                                                                                            |

|         | <ul><li>1 = Comparator input has changed (must be cleared in software)</li><li>0 = Comparator input has not changed</li></ul>                                                  |

| bit 5   | Unimplemented: Read as '0'                                                                                                                                                     |

| bit 4   | EEIF: EEPROM Write Operation Interrupt Flag bit                                                                                                                                |

|         | <ul><li>1 = The write operation completed (must be cleared in software)</li><li>0 = The write operation is not complete or has not been started</li></ul>                      |

| bit 3-0 | Unimplemented: Read as '0'                                                                                                                                                     |

|         |                                                                                                                                                                                |

|         | Legend:                                                                                                                                                                        |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

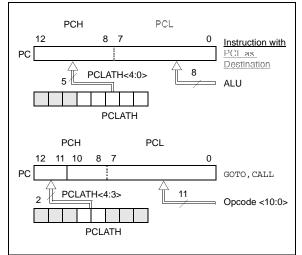

#### 2.3 PCL and PCLATH

The Program Counter (PC) is 13 bits wide. The low byte comes from the PCL register which is a readable and writable register. The upper bits (PC<12:8>) are not readable but are indirectly writable through the PCLATH register. On any Reset, the upper bits of the PC will be cleared. Figure 2-4 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### FIGURE 2-4: LOADING OF PC IN DIFFERENT SITUATIONS

#### 2.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to the application note, *AN556, "Implementing a Table Read*".

#### 2.3.2 STACK

The PIC16F87/88 family has an 8-level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the Stack Pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- **Note 1:** There are no status bits to indicate stack overflow or stack underflow conditions.

- 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions, or the vectoring to an interrupt address.

#### 2.4 Program Memory Paging

All PIC16F87/88 devices are capable of addressing a continuous 8K word block of program memory. The CALL and GOTO instructions provide only 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction, the upper 2 bits of the address are provided by PCLATH<4:3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bits are programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is popped off the stack. Therefore, manipulation of the PCLATH<4:3> bits is not required for the RETURN instructions (which POPs the address from the stack).

| Note: | The contents of the PCLATH register are    |

|-------|--------------------------------------------|

|       | unchanged after a RETURN or RETFIE         |

|       | instruction is executed. The user must     |

|       | rewrite the contents of the PCLATH regis-  |

|       | ter for any subsequent subroutine calls or |

|       | GOTO instructions.                         |

Example 2-1 shows the calling of a subroutine in page 1 of the program memory. This example assumes that PCLATH is saved and restored by the Interrupt Service Routine (if interrupts are used).

#### EXAMPLE 2-1: CALL OF A SUBROUTINE IN PAGE 1 FROM PAGE 0

|         | ORG 0x500<br>BCF PCLATH, 4 |                                |

|---------|----------------------------|--------------------------------|

|         | BSF PCLATH, 3              | ;Select page 1<br>;(800h-FFFh) |

|         | CALL SUB1_P1               | ;Call subroutine in            |

|         | :                          | ;page 1 (800h-FFFh)            |

|         | :                          |                                |

|         | ORG 0x900                  | ;page 1 (800h-FFFh)            |

| SUB1_P1 |                            |                                |

|         | :                          | ;called subroutine             |

|         |                            | ;page 1 (800h-FFFh)            |

|         | :                          |                                |

|         | RETURN                     | ;return to                     |

|         |                            | ;Call subroutine               |

|         |                            | ; in page 0                    |

|         |                            | ;(000h-7FFh)                   |

|         |                            |                                |

#### 3.3 Reading Data EEPROM Memory

To read a data memory location, the user must write the address to the EEADR register, clear the EEPGD control bit (EECON1<7>) and then set control bit RD (EECON1<0>). The data is available in the very next cycle in the EEDATA register; therefore, it can be read in the next instruction (see Example 3-1). EEDATA will hold this value until another read or until it is written to by the user (during a write operation).

The steps to reading the EEPROM data memory are:

- 1. Write the address to EEADR. Make sure that the address is not larger than the memory size of the device.

- 2. Clear the EEPGD bit to point to EEPROM data memory.

- 3. Set the RD bit to start the read operation.

- 4. Read the data from the EEDATA register.

|         |         | 0/(1)  |                       |

|---------|---------|--------|-----------------------|

| BANKSEL | EEADR   | ;      | Select Bank of EEADR  |

| MOVF    | ADDR, W | ;      |                       |

| MOVWF   | EEADR   | ;      | Data Memory Address   |

|         |         | ;      | to read               |

| BANKSEL | EECON1  | ;      | Select Bank of EECON1 |

| BCF     | EECON1, | EEPGD; | Point to Data memory  |

| BSF     | EECON1, | RD ;   | EE Read               |

| BANKSEL | EEDATA  | ;      | Select Bank of EEDATA |

| MOVF    | EEDATA, | W;     | W = EEDATA            |

|         |         |        |                       |

#### EXAMPLE 3-1: DATA EEPROM READ

#### 3.4 Writing to Data EEPROM Memory

To write an EEPROM data location, the user must first write the address to the EEADR register and the data to the EEDATA register. Then, the user must follow a specific write sequence to initiate the write for each byte.

The write will not initiate if the write sequence is not exactly followed (write 55h to EECON2, write AAh to EECON2, then set WR bit) for each byte. We strongly recommend that interrupts be disabled during this code segment (see Example 3-2).

Additionally, the WREN bit in EECON1 must be set to enable write. This mechanism prevents accidental writes to data EEPROM due to errant (unexpected) code execution (i.e., lost programs). The user should keep the WREN bit clear at all times except when updating EEPROM. The WREN bit is not cleared by hardware

After a write sequence has been initiated, clearing the WREN bit will not affect this write cycle. The WR bit will be inhibited from being set unless the WREN bit is set. At the completion of the write cycle, the WR bit is cleared in hardware and the EE Write Complete Interrupt Flag bit (EEIF) is set. The user can either enable this interrupt or poll this bit. EEIF must be cleared by software.

The steps to write to EEPROM data memory are:

- 1. If step 10 is not implemented, check the WR bit to see if a write is in progress.

- 2. Write the address to EEADR. Make sure that the address is not larger than the memory size of the device.

- 3. Write the 8-bit data value to be programmed in the EEDATA register.

- 4. Clear the EEPGD bit to point to EEPROM data memory.

- 5. Set the WREN bit to enable program operations.

- 6. Disable interrupts (if enabled).

- 7. Execute the special five instruction sequence:

Write 55h to EECON2 in two steps (first to W, then to EECON2).

Write AAh to EECON2 in two steps (first to W, then to EECON2).

Set the WR bit.

- 8. Enable interrupts (if using interrupts).

- 9. Clear the WREN bit to disable program operations.

- 10. At the completion of the write cycle, the WR bit is cleared and the EEIF interrupt flag bit is set (EEIF must be cleared by firmware). If step 1 is not implemented, then firmware should check for EEIF to be set, or WR to clear, to indicate the end of the program cycle.

#### EXAMPLE 3-2: DATA EEPROM WRITE

| -  |                      |                         |          |       |   |                   |

|----|----------------------|-------------------------|----------|-------|---|-------------------|

|    |                      | BANKSEL                 | EECON1   |       | ' | Select Bank of    |

|    |                      | DEEGO                   | DDCOM1   | MD    | ' | EECON1            |

|    |                      |                         |          |       |   | Wait for write    |

|    |                      | GOTO                    | •        |       |   | to complete       |

|    |                      | BANKSEL                 | EEADR    |       | ' | Select Bank of    |

|    |                      | MOLTE                   | 1000 11  |       | ' | EEADR             |

|    |                      |                         | ADDR, W  |       | ; |                   |

|    |                      | MOVWF                   | EEADR    |       |   | Data Memory       |

|    |                      |                         |          | _     | ; | Address to write  |

|    |                      |                         | VALUE, N |       | ; |                   |

|    |                      | MOVWF                   | EEDATA   |       |   | Data Memory Value |

|    |                      |                         |          |       | ' | to write          |

|    |                      | BANKSEL                 | EECON1   |       | ' | Select Bank of    |

|    |                      |                         |          |       | ' | EECON1            |

|    |                      | BCF                     | EECON1,  | EEPGD | ; | Point to DATA     |

|    |                      |                         |          |       |   | memory            |

|    |                      | BSF                     | EECON1,  | WREN  | ; | Enable writes     |

|    |                      |                         |          |       |   |                   |

| ١. | _                    | BCF                     | INTCON,  | GIE   | ; | Disable INTs.     |

| Ш  |                      | MOVLW                   |          |       | ; |                   |

| Ш  | g g                  | MOVWF                   | EECON2   |       | ; | Write 55h         |

| Ш  | Required<br>Sequence | MOVWF<br>MOVLW<br>MOVWF | AAh      |       | ; |                   |

| Ш  | sed %                | MOVWF                   | EECON2   |       | ; | Write AAh         |

| Ш  | E 0)                 |                         |          | WR    | ; | Set WR bit to     |

| l  |                      |                         |          |       | ; | begin write       |

|    |                      | BSF                     | INTCON,  | GIE   | ; | Enable INTs.      |

|    |                      | BCF                     | EECON1,  | WREN  | ; | Disable writes    |

| 1  |                      |                         |          |       |   |                   |

#### 3.5 Reading Flash Program Memory

To read a program memory location, the user must write two bytes of the address to the EEADR and EEADRH registers, set the EEPGD control bit (EECON1<7>) and then set control bit RD (EECON1<0>). Once the read control bit is set, the program memory Flash controller will use the second instruction cycle to read the data. This causes the second instruction immediately following the "BSF EECON1, RD" instruction to be ignored. The data is available in the very next cycle in the EEDATA and EEDATH registers; therefore, it can be read as two bytes in the following instructions. EEDATA and EED-ATH registers will hold this value until another read or until it is written to by the user (during a write operation).

#### EXAMPLE 3-3: FLASH PROGRAM READ

| ſ | BANKSEL | EEADRH   |       | ; | Select Bank of EEADRH |

|---|---------|----------|-------|---|-----------------------|

|   | MOVF    | ADDRH, V | V.    | ; |                       |

|   | MOVWF   | EEADRH   |       | ; | MS Byte of Program    |

|   |         |          |       | ; | Address to read       |

|   | MOVF    | ADDRL, V | V     | ; |                       |

|   | MOVWF   | EEADR    |       | ; | LS Byte of Program    |

|   |         |          |       | ; | Address to read       |

|   | BANKSEL | EECON1   |       | ; | Select Bank of EECON1 |

|   | BSF     | EECON1,  | EEPGD | ; | Point to PROGRAM      |

|   |         |          |       | ; | memory                |

|   | BSF     | EECON1,  | RD    | ; | EE Read               |

|   |         |          |       | ; |                       |

|   | NOP     |          |       | ; | Any instructions      |

|   |         |          |       | ; | here are ignored as   |

|   | NOP     |          |       | ; | program memory is     |

|   |         |          |       | ; | read in second cycle  |

|   |         |          |       | ; | after BSF EECON1,RD   |

|   | BANKSEL | EEDATA   |       | ; | Select Bank of EEDATA |

|   | MOVF    | EEDATA,  | W     | ; | DATAL = EEDATA        |

|   | MOVWF   | DATAL    |       | ; |                       |

|   | MOVF    | EEDATH,  | W     | ; | DATAH = EEDATH        |

|   | MOVWF   | DATAH    |       | ; |                       |

| I |         |          |       |   |                       |

#### 3.6 Erasing Flash Program Memory

The minimum erase block is 32 words. Only through the use of an external programmer, or through ICSP control, can larger blocks of program memory be bulk erased. Word erase in the Flash array is not supported.

When initiating an erase sequence from the microcontroller itself, a block of 32 words of program memory is erased. The Most Significant 11 bits of the EEADRH:EEADR point to the block being erased. EEADR< 4:0> are ignored.

The EECON1 register commands the erase operation. The EEPGD bit must be set to point to the Flash program memory. The WREN bit must be set to enable write operations. The FREE bit is set to select an erase operation.

For protection, the write initiate sequence for EECON2 must be used.

After the "BSF EECON1, WR" instruction, the processor requires two cycles to setup the erase operation. The user must place two NOP instructions after the WR bit is set. The processor will halt internal operations for the typical 2 ms, only during the cycle in which the erase takes place. This is not Sleep mode, as the clocks and peripherals will continue to run. After the erase cycle, the processor will resume operation with the third instruction after the EECON1 write instruction.

#### 3.6.1 FLASH PROGRAM MEMORY ERASE SEQUENCE

The sequence of events for erasing a block of internal program memory location is:

- 1. Load EEADRH:EEADR with address of row being erased.

- Set EEPGD bit to point to program memory, set WREN bit to enable writes and set FREE bit to enable the erase.

- 3. Disable interrupts.

- 4. Write 55h to EECON2.

- 5. Write AAh to EECON2.

- 6. Set the WR bit. This will begin the row erase cycle.

- 7. The CPU will stall for duration of the erase.

#### 4.0 OSCILLATOR CONFIGURATIONS

#### 4.1 Oscillator Types

The PIC16F87/88 can be operated in eight different oscillator modes. The user can program three configuration bits (FOSC2:FOSC0) to select one of these eight modes (modes 5-8 are new PIC16 oscillator configurations):

- 1. LP Low-Power Crystal

- 2. XT Crystal/Resonator

- 3. HS High-Speed Crystal/Resonator

- 4. RC External Resistor/Capacitor with Fosc/4 output on RA6

- 5. RCIO External Resistor/Capacitor with I/O on RA6

- 6. INTIO1 Internal Oscillator with Fosc/4 output on RA6 and I/O on RA7

- 7. INTIO2 Internal Oscillator with I/O on RA6 and RA7

- 8. ECIO External Clock with I/O on RA6

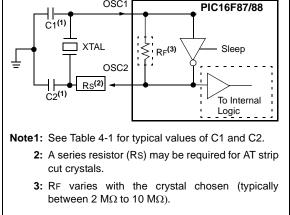

#### 4.2 Crystal Oscillator/Ceramic Resonators

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1/CLKI and OSC2/CLKO pins to establish oscillation (see Figure 4-1 and Figure 4-2). The PIC16F87/88 oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturer's specifications.

# TABLE 4-1:CAPACITOR SELECTION FOR<br/>CRYSTAL OSCILLATOR (FOR<br/>DESIGN GUIDANCE ONLY)

| Osc Type | Crystal | Typical Capacitor Values<br>Tested: |       |  |  |

|----------|---------|-------------------------------------|-------|--|--|

|          | Freq    | C1                                  | C2    |  |  |

| LP       | 32 kHz  | 33 pF                               | 33 pF |  |  |

| XT       | 200 kHz | 56 pF                               | 56 pF |  |  |

|          | 1 MHz   | 15 pF                               | 15 pF |  |  |

|          | 4 MHz   | 15 pF                               | 15 pF |  |  |

| HS       | 4 MHz   | 15 pF                               | 15 pF |  |  |

|          | 8 MHz   | 15 pF                               | 15 pF |  |  |

|          | 20 MHz  | 15 pF                               | 15 pF |  |  |

#### Capacitor values are for design guidance only.

These capacitors were tested with the crystals listed below for basic start-up and operation. These values were not optimized.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes following this table for additional information.

- Note 1: Higher capacitance increases the stability of oscillator but also increases the start-up time.

- 2: Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values of external components.

- **3:** Rs may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specification.

- **4:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

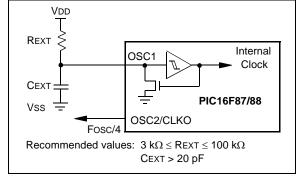

#### 4.4 RC Oscillator

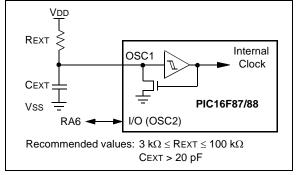

For timing insensitive applications, the "RC" and "RCIO" device options offer additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal manufacturing variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 4-4 shows how the R/C combination is connected.

In the RC Oscillator mode, the oscillator frequency divided by 4 is available on the OSC2 pin. This signal may be used for test purposes or to synchronize other logic.

The RCIO Oscillator mode (Figure 4-5) functions like the RC mode, except that the OSC2 pin becomes an additional general purpose I/O pin. The I/O pin becomes bit 6 of PORTA (RA6).

#### FIGURE 4-5: RCIO OSCILLATOR MODE

#### 4.5 Internal Oscillator Block

The PIC16F87/88 devices include an internal oscillator block which generates two different clock signals; either can be used as the system's clock source. This can eliminate the need for external oscillator circuits on the OSC1 and/or OSC2 pins.

The main output (INTOSC) is an 8 MHz clock source which can be used to directly drive the system clock. It also drives the INTOSC postscaler which can provide a range of six clock frequencies from 125 kHz to 4 MHz.

The other clock source is the internal RC oscillator (INTRC) which provides a 31.25 kHz (32  $\mu s$  nominal period) output. The INTRC oscillator is enabled by selecting the INTRC as the system clock source or when any of the following are enabled:

- Power-up Timer

- Watchdog Timer

- Two-Speed Start-up

- Fail-Safe Clock Monitor

These features are discussed in greater detail in Section 15.0 "Special Features of the CPU".

The clock source frequency (INTOSC direct, INTRC direct or INTOSC postscaler) is selected by configuring the IRCF bits of the OSCCON register (page 40).

| Note: | Throughout this data sheet, when referring specifically to a generic clock source, the |

|-------|----------------------------------------------------------------------------------------|

|       |                                                                                        |

|       | term "INTRC" may also be used to refer to                                              |

|       | the clock modes using the internal oscillator                                          |

|       | block. This is regardless of whether the                                               |

|       | actual frequency used is INTOSC (8 MHz),                                               |

|       | the INTOSC postscaler or INTRC                                                         |

|       | (31.25 kHz).                                                                           |

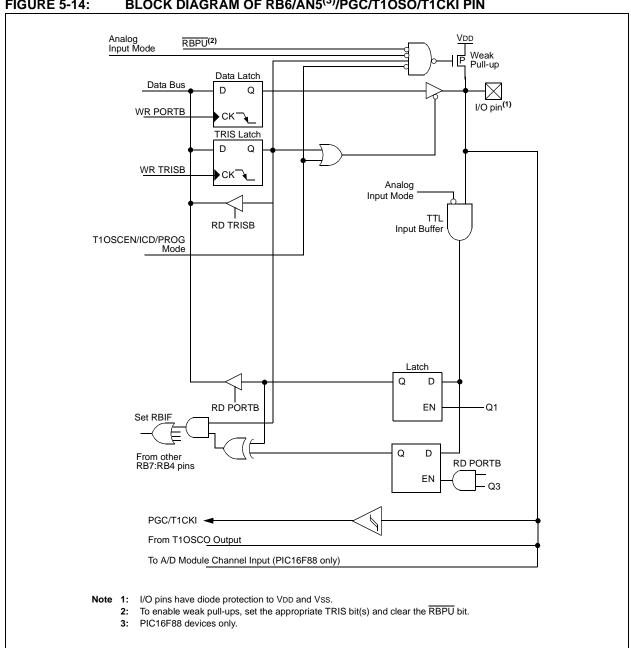

BLOCK DIAGRAM OF RB6/AN5<sup>(3)</sup>/PGC/T1OSO/T1CKI PIN FIGURE 5-14:

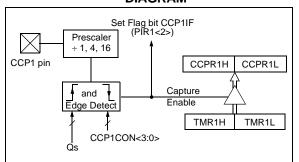

#### 9.1 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on the CCP1 pin. An event is defined as:

- Every falling edge

- Every rising edge

- Every 4th rising edge

- Every 16th rising edge

An event is selected by control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit, CCP1IF (PIR1<2>), is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value is overwritten by the new captured value.

#### 9.1.1 CCP PIN CONFIGURATION

In Capture mode, the CCP1 pin should be configured as an input by setting the TRISB<x> bit.

- **Note 1:** If the CCP1 pin is configured as an output, a write to the port can cause a capture condition.

- 2: The TRISB bit (0 or 3) is dependent upon the setting of configuration bit 12 (CCPMX).

#### FIGURE 9-1:

#### CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 9.1.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

#### 9.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit CCP1IE (PIE1<2>) clear to avoid false interrupts and should clear the flag bit, CCP1IF, following any such change in operating mode.

#### 9.1.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. This means that any Reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore, the first capture may be from a non-zero prescaler. Example 9-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

#### EXAMPLE 9-1: CHANGING BETWEEN CAPTURE PRESCALERS

| ;Turn CCP module off                   |

|----------------------------------------|

| <code>I_PS</code> ;Load the W reg with |

| ;the new prescaler                     |

| ;move value and CCP ON                 |

| ;Load CCP1CON with this                |

| ;value                                 |

|                                        |

NOTES:

#### 10.3.2 MASTER MODE OPERATION

Master mode operation is supported in firmware using interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset, or when the SSP module is disabled. The Stop (P) and Start (S) bits will toggle based on the Start and Stop conditions. Control of the I<sup>2</sup>C bus may be taken when the P bit is set, or the bus is Idle and both the S and P bits are clear.

In Master mode operation, the SCL and SDA lines are manipulated in firmware by clearing the corresponding TRISB<4,1> bit(s). The output level is always low, irrespective of the value(s) in PORTB<4,1>. So, when transmitting data, a '1' data bit must have the TRISB<1> bit set (input) and a '0' data bit must have the TRISB<1> bit cleared (output). The same scenario is true for the SCL line with the TRISB<4> bit. Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the I<sup>2</sup>C module.

The following events will cause the SSP Interrupt Flag bit, SSPIF, to be set (SSP Interrupt if enabled):

- · Start condition

- Stop condition

- Data transfer byte transmitted/received

Master mode operation can be done with either the Slave mode Idle (SSPM3:SSPM0 = 1011), or with the Slave mode active. When both Master mode operation and Slave modes are used, the software needs to differentiate the source(s) of the interrupt.

For more information on Master mode operation, see Application Note AN554, "Software Implementation of  $l^2 C^{TM}$  Bus Master".

#### 10.3.3 MULTI-MASTER MODE OPERATION

In Multi-Master mode operation, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset, or when the SSP module is disabled. The Stop (P) and Start (S) bits will toggle based on the Start and Stop conditions. Control of the I<sup>2</sup>C bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is Idle and both the S and P bits clear. When the bus is busy, enabling the SSP interrupt will generate the interrupt when the Stop condition occurs.

In Multi-Master mode operation, the SDA line must be monitored to see if the signal level is the expected output level. This check only needs to be done when a high level is output. If a high level is expected and a low level is present, the device needs to release the SDA and SCL lines (set TRISB<4,1>). There are two stages where this arbitration can be lost:

- Address Transfer

- Data Transfer

When the slave logic is enabled, the slave device continues to receive. If arbitration was lost during the address transfer stage, communication to the device may be in progress. If addressed, an ACK pulse will be generated. If arbitration was lost during the data transfer stage, the device will need to retransfer the data at a later time.

For more information on Multi-Master mode operation, see Application Note AN578, "Use of the SSP Module in the of  $l^2 C^{TM}$  Multi-Master Environment".

|                        | ABEL 10-3. REGISTERS ASSOCIATED WITH C OFERATION |                                                          |                                                                  |        |        |       |        |        |        |              |             |       |                       |

|------------------------|--------------------------------------------------|----------------------------------------------------------|------------------------------------------------------------------|--------|--------|-------|--------|--------|--------|--------------|-------------|-------|-----------------------|

| Address                | Name                                             | Bit 7                                                    | Bit 6                                                            | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Valu<br>POR, | e on<br>BOR | all o | e on<br>other<br>sets |

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON                                           | GIE                                                      | PEIE                                                             | TMR0IE | INT0IE | RBIE  | TMR0IF | INTOIF | RBIF   | 0000         | 000x        | 0000  | 000u                  |

| 0Ch                    | PIR1                                             |                                                          | ADIF <sup>(1)</sup>                                              | RCIF   | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | -000         | 0000        | -000  | 0000                  |

| 8Ch                    | PIE1                                             |                                                          | ADIE <sup>(1)</sup>                                              | RCIE   | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE | -000         | 0000        | -000  | 0000                  |

| 13h                    | SSPBUF                                           | Synchronous Serial Port Receive Buffer/Transmit Register |                                                                  |        |        |       |        |        | xxxx   | xxxx         | uuuu        | uuuu  |                       |

| 93h                    | SSPADD                                           | Synchron                                                 | Synchronous Serial Port (I <sup>2</sup> C mode) Address Register |        |        |       |        |        |        | 0000         | 0000        | 0000  | 0000                  |

| 14h                    | SSPCON                                           | WCOL                                                     | SSPOV                                                            | SSPEN  | CKP    | SSPM3 | SSPM2  | SSPM1  | SSPM0  | 0000         | 0000        | 0000  | 0000                  |

| 94h                    | SSPSTAT                                          | SMP <sup>(2)</sup>                                       | CKE <sup>(2)</sup>                                               | D/A    | Р      | S     | R/W    | UA     | BF     | 0000         | 0000        | 0000  | 0000                  |

| 86h                    | TRISB                                            | PORTB Data Direction Register                            |                                                                  |        |        |       |        |        | 1111   | 1111         | 1111        | 1111  |                       |

TABLE 10-3: REGISTERS ASSOCIATED WITH I<sup>2</sup>C<sup>™</sup> OPERATION

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'.

Shaded cells are not used by SSP module in SPI mode.

Note 1: This bit is only implemented on the PIC16F88. The bit will read '0' on the PIC16F87.

**2:** Maintain these bits clear in  $I^2C^{TM}$  mode.

NOTES:

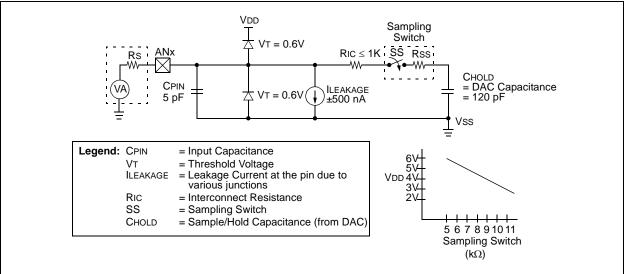

#### 12.1 A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 12-2. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), see Figure 12-2. The maximum recommended impedance for analog sources is 10 k $\Omega$ . As the impedance is decreased, the

# acquisition time may be decreased. After the analog input channel is selected (changed), this acquisition must be done before the conversion can be started.

To calculate the minimum acquisition time, Equation 12-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified resolution.

To calculate the minimum acquisition time, TACQ, see the "*PIC*<sup>®</sup> *Mid-Range MCU Family Reference Manual*" (DS33023).

#### EQUATION 12-1: ACQUISITION TIME

| TACQ | = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient                                                                                                                            |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Тс   | = TAMP + TC + TCOFF<br>= $2 \mu s + TC + [(Temperature -25^{\circ}C)(0.05 \mu s/^{\circ}C)]$<br>= CHOLD (RIC + RSS + RS) In(1/2047)<br>= -120 pF (1 k $\Omega$ + 7 k $\Omega$ + 10 k $\Omega$ ) In(0.0004885) |

| TACQ | = $16.47 \ \mu s$<br>= $2 \ \mu s + 16.47 \ \mu s + [(50^{\circ}C - 25^{\circ}C)(0.05 \ \mu s/^{\circ}C)]$<br>= $19.72 \ \mu s$                                                                               |

Note 1: The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- **2:** The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is 10 k $\Omega$ . This is required to meet the pin leakage specification.

- **4:** After a conversion has completed, a 2.0 TAD delay must complete before acquisition can begin again. During this time, the holding capacitor is not connected to the selected A/D input channel.

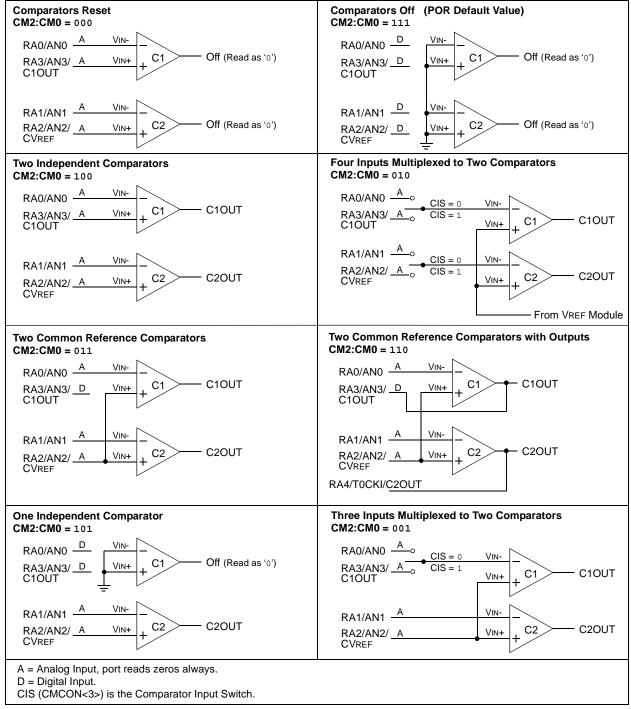

#### 13.1 Comparator Configuration

There are eight modes of operation for the comparators. The CMCON register is used to select these modes. Figure 13-1 shows the eight possible modes. The TRISA register controls the data direction of the comparator pins for each mode. If the Comparator mode is changed, the comparator output level may not be valid for the specified mode change delay shown in **Section 18.0 "Electrical Characteristics"**.

# Note: Comparator interrupts should be disabled during a Comparator mode change; otherwise, a false interrupt may occur.

| Address                 | Name                              | Bit 7  | Bit 6  | Bit 5                 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR        | Value on<br>all other<br>Resets |

|-------------------------|-----------------------------------|--------|--------|-----------------------|--------|--------|--------|--------|--------|------------------------|---------------------------------|

| 9Ch                     | CMCON                             | C2OUT  | C10UT  | C2INV                 | C1INV  | CIS    | CM2    | CM1    | CM0    | 0000 0111              | 0000 0111                       |

| 9Dh                     | CVRCON                            | CVREN  | CVROE  | CVRR                  | —      | CVR3   | CVR2   | CVR1   | CVR0   | 000- 0000              | 000- 0000                       |

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON                            | GIE    | PEIE   | TMR0IE                | INTOIE | RBIE   | TMR0IF | INTOIF | RBIF   | 0000 000x              | 0000 000u                       |

| 0Dh                     | PIR2                              | OSFIF  | CMIF   | _                     | EEIF   | —      | —      | —      | —      | 00-0                   | 00-0                            |

| 8Dh                     | PIE2                              | OSFIE  | CMIE   | _                     | EEIE   | —      | _      | _      | _      | 00-0                   | 00-0                            |

| 05h                     | PORTA<br>(PIC16F87)<br>(PIC16F88) |        | RA6    | RA5                   | RA4    | RA3    | RA2    | RA1    | RA0    | xxxx 0000<br>xxx0 0000 | uuuu 0000<br>uuu0 0000          |

| 85h                     | TRISA                             | TRISA7 | TRISA6 | TRISA5 <sup>(1)</sup> | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1111 1111              | 1111 1111                       |

#### TABLE 13-1: REGISTERS ASSOCIATED WITH THE COMPARATOR MODULE

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the comparator module.

Note 1: Pin 5 is an input only; the state of the TRISA5 bit has no effect and will always read '1'.

| SUBLW            | Subtract W from Literal                                                                                                        | XORLW            | Exclusive OR Literal with W                                                                                                |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] SUBLW k                                                                                                       | Syntax:          | [label] XORLW k                                                                                                            |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                              | Operands:        | $0 \leq k \leq 255$                                                                                                        |  |  |  |  |

| Operation:       | $k - (W) \rightarrow (W)$                                                                                                      | Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                              |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                       | Status Affected: | Z                                                                                                                          |  |  |  |  |

| Description:     | The W register is subtracted (two's complement method) from the eight-bit literal 'k'. The result is placed in the W register. | Description:     | The contents of the W register<br>are XOR'ed with the eight-bit<br>literal 'k'. The result is placed in<br>the W register. |  |  |  |  |

| SUBWF            | Subtract W from f                                                                                                                                                   | XORWF            | Exclusive OR W with f                                                                                                                                                     |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [label] SUBWF f,d                                                                                                                                                   | Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                                                |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                         | Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                        |  |  |

| Operation:       | (f) – (W) $\rightarrow$ (destination)                                                                                                                               | Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                 |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                            | Status Affected: | Z                                                                                                                                                                         |  |  |

| Description:     | ription:Subtract (two's complement<br>method) W register from register 'f'.<br>If 'd' = 0, the result is stored in the<br>W register. If 'd' = 1, the result is<br> |                  | Exclusive OR the contents of the W register with register 'f'. If 'd' = 0, the result is stored in the W register. If 'd' = 1, the result is stored back in register 'f'. |  |  |

| SWAPF            | Swap Nibbles in f                                                                                                                                            |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] SWAPF f,d                                                                                                                                   |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                            |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                      |

| Status Affected: | None                                                                                                                                                         |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' = 0, the result is placed in W register. If 'd' = 1, the result is placed in register 'f'. |

DS30487D-page 156

### TABLE 18-13: A/D CONVERTER CHARACTERISTICS: PIC16F87/88 (INDUSTRIAL, EXTENDED) PIC16LF87/88 (INDUSTRIAL)

| Param<br>No. | Sym   | Characteristic                                    |              | Min         | Тур†                      | Max         | Units | Conditions                                                                                                                                    |

|--------------|-------|---------------------------------------------------|--------------|-------------|---------------------------|-------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| A01          | NR    | Resolution                                        |              | _           | _                         | 10-bit      | bit   | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                                                  |

| A03          | EIL   | Integral Linearity Error                          |              | —           | —                         | <±1         | LSb   | $\begin{array}{l} VREF=VDD=5.12V,\\ VSS\leqVAIN\leqVREF \end{array}$                                                                          |

| A04          | Edl   | Differential Linearity Error                      |              | —           | —                         | <±1         | LSb   | $\begin{array}{l} VREF=VDD=5.12V,\\ VSS\leqVAIN\leqVREF \end{array}$                                                                          |

| A06          | EOFF  | Offset Error                                      |              | —           |                           | <±2         | LSb   | VREF = VDD = 5.12V,<br>VSS $\leq$ VAIN $\leq$ VREF                                                                                            |

| A07          | Egn   | Gain Error                                        |              | _           | —                         | <±1         | LSb   | VREF = VDD = 5.12V,<br>VSS $\leq$ VAIN $\leq$ VREF                                                                                            |

| A10          | _     | Monotonicity                                      |              | —           | guaranteed <sup>(3)</sup> | —           | _     | $VSS \leq VAIN \leq VREF$                                                                                                                     |

| A20          | Vref  | Reference Voltage<br>(VREF+ – VREF-)              |              | 2.0         | —                         | VDD + 0.3   | V     |                                                                                                                                               |

| A21          | Vref+ | Reference Voltag                                  | e High       | AVDD – 2.5V |                           | AVDD + 0.3V | V     |                                                                                                                                               |

| A22          | VREF- | Reference Voltag                                  | e Low        | AVss-0.3V   |                           | VREF+-2.0V  | V     |                                                                                                                                               |

| A25          | VAIN  | Analog Input Volt                                 | age          | Vss - 0.3V  | —                         | VREF + 0.3V | V     |                                                                                                                                               |

| A30          | Zain  | Recommended Impedance of<br>Analog Voltage Source |              | —           | —                         | 2.5         | kΩ    | (Note 4)                                                                                                                                      |

| A40          | IAD   | A/D Conversion                                    | PIC16F87/88  | —           | 220                       | —           | μΑ    | Average current                                                                                                                               |

|              |       | Current (VDD)                                     | PIC16LF87/88 | —           | 90                        | —           | μΑ    | consumption when A/D is on (Note 1)                                                                                                           |

| A50          | IREF  | VREF Input Current (Note 2)                       |              | _           | _                         | 5           | μA    | During VAIN acquisition.<br>Based on differential of VHOLD<br>to VAIN to charge CHOLD,<br>see Section 12.1 "A/D<br>Acquisition Requirements". |

|              |       |                                                   |              | —           | —                         | 150         | μA    | During A/D conversion cycle                                                                                                                   |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** When A/D is off, it will not consume any current other than minor leakage current. The power-down current specification includes any such leakage from the A/D module.

2: VREF current is from RA3 pin or VDD pin, whichever is selected as reference input.

3: The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

4: Maximum allowed impedance for analog voltage source is 10 kΩ. This requires higher acquisition time.

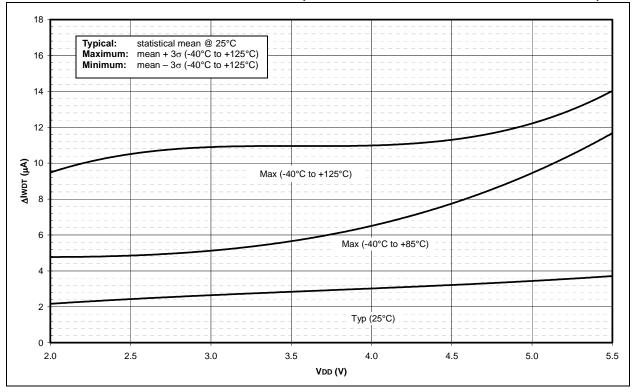

FIGURE 19-15: △IPD WDT, -40°C TO +125°C (SLEEP MODE, ALL PERIPHERALS DISABLED)

NOTES: