# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 10MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 16                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 368 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | <u>.</u>                                                                 |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                           |

| Supplier Device Package    | 20-SSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf87-i-ss |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.0 DATA EEPROM AND FLASH PROGRAM MEMORY

The data EEPROM and Flash program memory are readable and writable during normal operation (over the full VDD range). This memory is not directly mapped in the register file space. Instead, it is indirectly addressed through the Special Function Registers. There are six SFRs used to read and write this memory:

- EECON1

- EECON2

- EEDATA

- EEDATH

- EEADR

- EEADRH

This section focuses on reading and writing data EEPROM and Flash program memory during normal operation. Refer to the appropriate device programming specification document for serial programming information.

When interfacing the data memory block, EEDATA holds the 8-bit data for read/write and EEADR holds the address of the EEPROM location being accessed. The PIC16F87/88 devices have 256 bytes of data EEPROM with an address range from 00h to 0FFh. When writing to unimplemented locations, the charge pump will be turned off.

When interfacing the program memory block, the EED-ATA and EEDATH registers form a two-byte word that holds the 14-bit data for read/write and the EEADR and EEADRH registers form a two-byte word that holds the 13-bit address of the EEPROM location being accessed. The PIC16F87/88 devices have 4K words of program Flash with an address range from 0000h to 0FFFh. Addresses above the range of the respective device will wraparound to the beginning of program memory.

The EEPROM data memory allows single byte read and write. The Flash program memory allows singleword reads and four-word block writes. Program memory writes must first start with a 32-word block erase, then write in 4-word blocks. A byte write in data EEPROM memory automatically erases the location and writes the new data (erase before write).

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump, rated to operate over the voltage range of the device for byte or word operations.

When the device is code-protected, the CPU may continue to read and write the data EEPROM memory. Depending on the settings of the write-protect bits, the device may or may not be able to write certain blocks of the program memory; however, reads of the program memory are allowed. When code-protected, the device programmer can no longer access data or program memory; this does NOT inhibit internal reads or writes.

### 3.1 EEADR and EEADRH

The EEADRH:EEADR register pair can address up to a maximum of 256 bytes of data EEPROM, or up to a maximum of 8K words of program EEPROM. When selecting a data address value, only the LSB of the address is written to the EEADR register. When selecting a program address value, the MSB of the address is written to the EEADRH register and the LSB is written to the EEADR register.

If the device contains less memory than the full address reach of the address register pair, the Most Significant bits of the registers are not implemented. For example, if the device has 128 bytes of data EEPROM, the Most Significant bit of EEADR is not implemented on access to data EEPROM.

#### 3.2 EECON1 and EECON2 Registers

EECON1 is the control register for memory accesses.

Control bit EEPGD determines if the access will be a program or data memory access. When clear, as it is when reset, any subsequent operations will operate on the data memory. When set, any subsequent operations will operate on the program memory.

Control bits, RD and WR, initiate read and write, respectively. These bits cannot be cleared, only set in software. They are cleared in hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write or erase operation. On power-up, the WREN bit is clear. The WRERR bit is set when a write (or erase) operation is interrupted by a MCLR, or a WDT Time-out Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and rewrite the location. The data and address will be unchanged in the EEDATA and EEADR registers.

Interrupt flag bit, EEIF in the PIR2 register, is set when the write is complete. It must be cleared in software.

EECON2 is not a physical register. Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the EEPROM write sequence.

| EXAMPLE 3-4: | ERASING A FLASH PROGRAM MEMORY RC | W |

|--------------|-----------------------------------|---|

|--------------|-----------------------------------|---|

|           | BANKSEL | EEADRH        | ; Select Bank of EEADRH                                |

|-----------|---------|---------------|--------------------------------------------------------|

|           | MOVF    | ADDRH, W      | ;                                                      |

|           | MOVWF   | EEADRH        | ; MS Byte of Program Address to Erase                  |

|           | MOVF    | ADDRL, W      | ;                                                      |

|           | MOVWF   | EEADR         | ; LS Byte of Program Address to Erase                  |

| ERASE ROW |         |               |                                                        |

| _         | BANKSEL | EECON1        | ; Select Bank of EECON1                                |

|           | BSF     | EECON1, EEPGD | ; Point to PROGRAM memory                              |

|           | BSF     | EECON1, WREN  | ; Enable Write to memory                               |

|           | BSF     | EECON1, FREE  | ; Enable Row Erase operation                           |

| ;         |         |               |                                                        |

|           | BCF     | INTCON, GIE   | ; Disable interrupts (if using)                        |

|           | MOVLW   | 55h           | ;                                                      |

|           | MOVWF   | EECON2        | ; Write 55h                                            |

|           | MOVLW   | AAh           | i                                                      |

|           | MOVWF   | EECON2        | ; Write AAh                                            |

|           | BSF     | EECON1, WR    | ; Start Erase (CPU stall)                              |

|           | NOP     |               | ; Any instructions here are ignored as processor       |

|           |         |               | ; halts to begin Erase sequence                        |

|           | NOP     |               | ; processor will stop here and wait for Erase complete |

|           |         |               | ; after Erase processor continues with 3rd instruction |

|           | BCF     | EECON1, FREE  | ; Disable Row Erase operation                          |

|           | BCF     | EECON1, WREN  | ; Disable writes                                       |

|           | BSF     | INTCON, GIE   | ; Enable interrupts (if using)                         |

|           |         |               |                                                        |

### 4.0 OSCILLATOR CONFIGURATIONS

#### 4.1 Oscillator Types

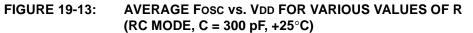

The PIC16F87/88 can be operated in eight different oscillator modes. The user can program three configuration bits (FOSC2:FOSC0) to select one of these eight modes (modes 5-8 are new PIC16 oscillator configurations):

- 1. LP Low-Power Crystal

- 2. XT Crystal/Resonator

- 3. HS High-Speed Crystal/Resonator

- 4. RC External Resistor/Capacitor with Fosc/4 output on RA6

- 5. RCIO External Resistor/Capacitor with I/O on RA6

- 6. INTIO1 Internal Oscillator with Fosc/4 output on RA6 and I/O on RA7

- 7. INTIO2 Internal Oscillator with I/O on RA6 and RA7

- 8. ECIO External Clock with I/O on RA6

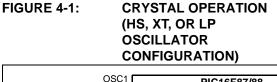

### 4.2 Crystal Oscillator/Ceramic Resonators

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1/CLKI and OSC2/CLKO pins to establish oscillation (see Figure 4-1 and Figure 4-2). The PIC16F87/88 oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturer's specifications.

# TABLE 4-1:CAPACITOR SELECTION FOR<br/>CRYSTAL OSCILLATOR (FOR<br/>DESIGN GUIDANCE ONLY)

| Osc Type | Crystal | Typical Capacitor Values<br>Tested: |       |  |  |

|----------|---------|-------------------------------------|-------|--|--|

|          | Freq    | C1                                  | C2    |  |  |

| LP       | 32 kHz  | 33 pF                               | 33 pF |  |  |

| XT       | 200 kHz | 56 pF                               | 56 pF |  |  |

|          | 1 MHz   | 15 pF                               | 15 pF |  |  |

|          | 4 MHz   | 15 pF                               | 15 pF |  |  |

| HS       | 4 MHz   | 15 pF                               | 15 pF |  |  |

|          | 8 MHz   | 15 pF                               | 15 pF |  |  |

|          | 20 MHz  | 15 pF                               | 15 pF |  |  |

#### Capacitor values are for design guidance only.

These capacitors were tested with the crystals listed below for basic start-up and operation. These values were not optimized.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes following this table for additional information.

- Note 1: Higher capacitance increases the stability of oscillator but also increases the start-up time.

- 2: Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values of external components.

- **3:** Rs may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specification.

- **4:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

The maximum PWM resolution (bits) for a given PWM frequency is given by the following formula.

#### **EQUATION 9-3:**

Resolution =

$$\frac{\log(\frac{\text{FOSC}}{\text{FPWM}})}{\log(2)}$$

Note: If the PWM duty cycle value is longer than the PWM period, the CCP1 pin will not be cleared.

#### 9.3.3 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- Make the CCP1 pin an output by clearing the TRISB<x> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

#### TABLE 9-3:EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 20 MHz

| PWM Frequency              | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|----------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                  | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8         | 7         | 6.6       |

#### TABLE 9-4: REGISTERS ASSOCIATED WITH PWM AND TIMER2

bits

| Address              | Name    | Bit 7                                | Bit 6                                | Bit 5         | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value<br>POR, |      | all o | e on<br>ther<br>sets |

|----------------------|---------|--------------------------------------|--------------------------------------|---------------|---------|---------|--------|---------|---------|---------------|------|-------|----------------------|

| 0Bh,8Bh<br>10Bh,18Bh | INTCON  | GIE                                  | PEIE                                 | TMR0IE        | INTOIE  | RBIE    | TMR0IF | INTOIF  | RBIF    | 0000          | 000x | 0000  | 000u                 |

| 0Ch                  | PIR1    | _                                    | ADIF <sup>(1)</sup>                  | RCIF          | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | -000          | 0000 | -000  | 0000                 |

| 8Ch                  | PIE1    | _                                    | ADIE <sup>(1)</sup>                  | RCIE          | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | -000          | 0000 | -000  | 0000                 |

| 86h                  | TRISB   | PORT                                 | B Data Direc                         | ction Registe | er      |         |        |         |         | 1111          | 1111 | 1111  | 1111                 |

| 11h                  | TMR2    | Timer2                               | Module Reg                           | gister        |         |         |        |         |         | 0000          | 0000 | 0000  | 0000                 |

| 92h                  | PR2     | Timer2                               | Period Regi                          | ster          |         |         |        |         |         | 1111          | 1111 | 1111  | 1111                 |

| 12h                  | T2CON   |                                      | TOUTPS3                              | TOUTPS2       | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000          | 0000 | -000  | 0000                 |

| 15h                  | CCPR1L  | Captur                               | Capture/Compare/PWM Register 1 (LSB) |               |         |         |        |         |         | xxxx          | xxxx | uuuu  | uuuu                 |

| 16h                  | CCPR1H  | Capture/Compare/PWM Register 1 (MSB) |                                      |               |         |         |        | xxxx    | xxxx    | uuuu          | uuuu |       |                      |

| 17h                  | CCP1CON | _                                    | _                                    | CCP1X         | CCP1Y   | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0  | 00            | 0000 | 00    | 0000                 |

$\label{eq:logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical_logistical$

**Note 1:** This bit is only implemented on the PIC16F88. The bit will read '0' on the PIC16F87.

<sup>5.</sup> Configure the CCP1 module for PWM operation.

Note: The TRISB bit (0 or 3) is dependant upon the setting of configuration bit 12 (CCPMX).

| REGISTER 10-2: | SSPCON:                                                                                                               | SYNCHR                | ONOUS SER                                      | IAL PORT                 | CONTROL         | REGISTE      | R (ADDRE      | SS 14h)      |  |

|----------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------------------------------|--------------------------|-----------------|--------------|---------------|--------------|--|

|                | R/W-0                                                                                                                 | R/W-0                 | R/W-0                                          | R/W-0                    | R/W-0           | R/W-0        | R/W-0         | R/W-0        |  |

|                | WCOL                                                                                                                  | SSPOV                 | SSPEN <sup>(1)</sup>                           | CKP                      | SSPM3           | SSPM2        | SSPM1         | SSPM0        |  |

|                | bit 7                                                                                                                 |                       |                                                |                          |                 |              |               | bit 0        |  |

| bit 7          | WCOL: W                                                                                                               | rite Collisior        | Detect bit                                     |                          |                 |              |               |              |  |

|                |                                                                                                                       |                       | e the SSPBUF                                   | -<br>register fai        | led because     | the SSP m    | odule is bu   | sy           |  |

|                | (must                                                                                                                 | be cleared            | in software)                                   | C                        |                 |              |               |              |  |

|                | 0 = No col                                                                                                            |                       | <b>a b b c</b>                                 |                          |                 |              |               |              |  |

| bit 6          | In SPI mod                                                                                                            |                       | rflow Indicator                                | Dit                      |                 |              |               |              |  |

|                |                                                                                                                       |                       | eived while the                                | SSPBUF re                | aister is still | holdina the  | previous da   | ata. In case |  |

|                | of ove                                                                                                                | rflow, the d          | ata in SSPSR                                   | is lost. Ove             | rflow can or    | ly occur in  | Slave mode    | e. The user  |  |

|                |                                                                                                                       |                       | PBUF, even if                                  |                          |                 |              |               |              |  |

|                |                                                                                                                       |                       | w bit is not se<br>SPBUF regist                |                          | i new recep     | uon (and tra | ansmission)   | is initiated |  |

|                | 0 = No over                                                                                                           | erflow                | 0                                              |                          |                 |              |               |              |  |

|                | In I <sup>2</sup> C mod                                                                                               |                       |                                                |                          |                 | r            |               | 00001/-      |  |

|                | •                                                                                                                     |                       | while the SSI                                  | •                        |                 | • .          | •             |              |  |

|                | 0 = No over                                                                                                           |                       |                                                |                          |                 |              |               |              |  |

| bit 5          | SSPEN: S                                                                                                              | ynchronous            | Serial Port Er                                 | nable bit <sup>(1)</sup> |                 |              |               |              |  |

|                | In SPI mod                                                                                                            |                       |                                                |                          |                 |              |               |              |  |

|                |                                                                                                                       |                       | t and configure<br>rt and configur             |                          |                 |              | t pins        |              |  |

|                | In I <sup>2</sup> C mod                                                                                               | -                     | it and coningui                                | es triese pir            | 13 a3 1/0 p01   | t pins       |               |              |  |

|                | 1 = Enable                                                                                                            | es the serial         | port and confi                                 |                          |                 |              | rial port pin | 5            |  |

|                |                                                                                                                       | -                     | rt and configur                                |                          |                 | -            |               |              |  |

|                | Note 1:                                                                                                               | In both mo<br>output. | odes, when en                                  | abled, these             | e pins must l   | be properly  | configured    | as input or  |  |

| bit 4          |                                                                                                                       | k Polarity S          | elect bit                                      |                          |                 |              |               |              |  |

|                | In SPI mod                                                                                                            |                       | on falling edge                                | , receive or             | ricina odao     | Idlo ototo f | or clock is c | high loval   |  |

|                |                                                                                                                       |                       | on rising edge                                 |                          |                 |              |               |              |  |

|                | <u>In I<sup>2</sup>C Slav</u>                                                                                         | <u>e mode:</u>        |                                                |                          |                 |              |               |              |  |

|                | SCK release                                                                                                           |                       |                                                |                          |                 |              |               |              |  |

|                | 1 = Enable<br>0 = Holds (                                                                                             |                       | lock stretch). (                               | Used to ens              | sure data set   | up time.)    |               |              |  |

| bit 3-0        | SSPM<3:0                                                                                                              | >: Synchro            | nous Serial Po                                 | ort Mode Se              | lect bits       | . ,          |               |              |  |

|                |                                                                                                                       |                       | ode, clock = O                                 |                          |                 |              |               |              |  |

|                |                                                                                                                       |                       | ode, clock = O<br>ode, clock = O               |                          |                 |              |               |              |  |

|                |                                                                                                                       |                       | ode, clock = O<br>ode, clock = Tl              |                          | 2               |              |               |              |  |

|                | 0100 = SP                                                                                                             | I Slave mo            | de, clock = SC                                 | K pin. SS pi             | in control en   |              |               |              |  |

|                | 0101 = SPI Slave mode, clock = SCK pin. $\overline{SS}$ pin control disabled. $\overline{SS}$ can be used as I/O pin. |                       |                                                |                          |                 |              |               |              |  |

|                | 0110 = I <sup>2</sup> C Slave mode, 7-bit address<br>0111 = I <sup>2</sup> C Slave mode, 10-bit address               |                       |                                                |                          |                 |              |               |              |  |

|                | $1011 = I^2C$                                                                                                         | Firmware              | Controlled Ma                                  | ster mode (              |                 |              |               |              |  |

|                |                                                                                                                       |                       | le, 7-bit addres                               |                          |                 |              |               |              |  |

|                |                                                                                                                       |                       | <b>le, 10-bit addr</b><br>L00, 1101 <b>=</b> R |                          | n anu stop i    |              |               |              |  |

|                |                                                                                                                       | ,, .                  | .,                                             |                          |                 |              |               |              |  |

|                | Legend:                                                                                                               |                       |                                                |                          |                 |              |               |              |  |

|                | R = Reada                                                                                                             | ble bit               | W = W                                          | ritable bit              | U = Unim        | plemented    | bit, read as  | '0'          |  |

| Legena.           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

© 2002-2013 Microchip Technology Inc.

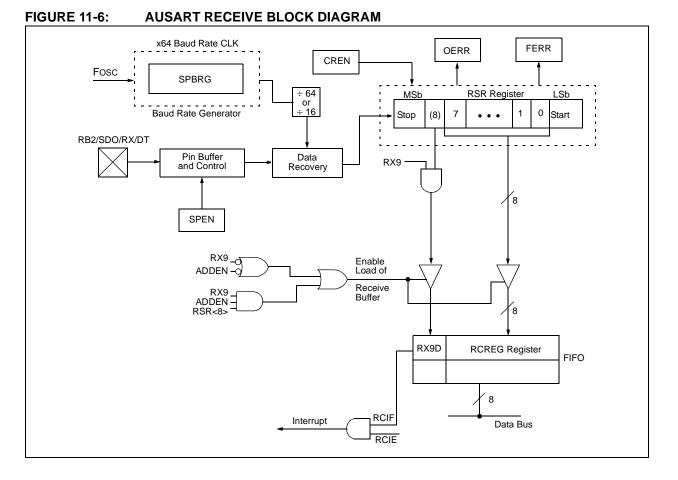

### 11.2.3 SETTING UP 9-BIT MODE WITH ADDRESS DETECT

When setting up an asynchronous reception with address detect enabled:

- Initialize the SPBRG register for the appropriate baud rate. If a high-speed baud rate is desired, set bit BRGH.

- Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- If interrupts are desired, then set enable bit RCIE.

- Set bit RX9 to enable 9-bit reception.

- Set ADDEN to enable address detect.

- Enable the reception by setting enable bit CREN.

- Flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit and determine if any error occurred during reception.

- Read the 8-bit received data by reading the RCREG register to determine if the device is being addressed.

- If any error occurred, clear the error by clearing enable bit CREN.

- If the device has been addressed, clear the ADDEN bit to allow data bytes and address bytes to be read into the receive buffer and interrupt the CPU.

| Address                 | Name                              | Bit 7  | Bit 6  | Bit 5                 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR        | Value on<br>all other<br>Resets |

|-------------------------|-----------------------------------|--------|--------|-----------------------|--------|--------|--------|--------|--------|------------------------|---------------------------------|

| 9Ch                     | CMCON                             | C2OUT  | C10UT  | C2INV                 | C1INV  | CIS    | CM2    | CM1    | CM0    | 0000 0111              | 0000 0111                       |

| 9Dh                     | CVRCON                            | CVREN  | CVROE  | CVRR                  | —      | CVR3   | CVR2   | CVR1   | CVR0   | 000- 0000              | 000- 0000                       |

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON                            | GIE    | PEIE   | TMR0IE                | INTOIE | RBIE   | TMR0IF | INTOIF | RBIF   | 0000 000x              | 0000 000u                       |

| 0Dh                     | PIR2                              | OSFIF  | CMIF   | _                     | EEIF   | —      | —      | —      | —      | 00-0                   | 00-0                            |

| 8Dh                     | PIE2                              | OSFIE  | CMIE   | _                     | EEIE   | —      | _      | _      | _      | 00-0                   | 00-0                            |

| 05h                     | PORTA<br>(PIC16F87)<br>(PIC16F88) |        | RA6    | RA5                   | RA4    | RA3    | RA2    | RA1    | RA0    | xxxx 0000<br>xxx0 0000 | uuuu 0000<br>uuu0 0000          |

| 85h                     | TRISA                             | TRISA7 | TRISA6 | TRISA5 <sup>(1)</sup> | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1111 1111              | 1111 1111                       |

#### TABLE 13-1: REGISTERS ASSOCIATED WITH THE COMPARATOR MODULE

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the comparator module.

Note 1: Pin 5 is an input only; the state of the TRISA5 bit has no effect and will always read '1'.

#### 15.8 Time-out Sequence

On power-up, the time-out sequence is as follows: the PWRT delay starts (if enabled) when a POR occurs. Then, OST starts counting 1024 oscillator cycles when PWRT ends (LP, XT, HS). When the OST ends, the device comes out of Reset.

If MCLR is kept low long enough, all delays will expire. Bringing MCLR high will begin execution immediately. This is useful for testing purposes, or to synchronize more than one PIC16F87/88 device operating in parallel.

Table 15-3 shows the Reset conditions for the STATUS, PCON and PC registers, while Table 15-4 shows the Reset conditions for all the registers.

#### 15.9 Power Control/Status Register (PCON)

The Power Control/Status Register, PCON, has two bits to indicate the type of Reset that last occurred.

Bit 0 is Brown-out Reset Status bit, BOR. Bit BOR is unknown on a Power-on Reset. It must then be set by the user and checked on subsequent Resets to see if bit BOR cleared, indicating a Brown-out Reset occurred. When the Brown-out Reset is disabled, the state of the BOR bit is unpredictable.

Bit 1 is POR (Power-on Reset Status bit). It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

| Oscillator    | Power-u             | qu                     | Brown-out           | Wake-up from           |                        |  |  |

|---------------|---------------------|------------------------|---------------------|------------------------|------------------------|--|--|

| Configuration | PWRTE = 0           | <b>PWRTE</b> = 1       | PWRTE = 0           | <b>PWRTE =</b> 1       | Sleep                  |  |  |

| XT, HS, LP    | TPWRT + 1024 • Tosc | 1024 • Tosc            | TPWRT + 1024 • Tosc | 1024 • Tosc            | 1024 • Tosc            |  |  |

| EXTRC, INTRC  | Tpwrt               | 5-10 μs <sup>(1)</sup> | TPWRT               | 5-10 μs <sup>(1)</sup> | 5-10 μs <sup>(1)</sup> |  |  |

| T1OSC         | —                   | —                      | —                   | —                      | 5-10 μs <sup>(1)</sup> |  |  |

#### TABLE 15-1: TIME-OUT IN VARIOUS SITUATIONS

**Note 1:** CPU start-up is always invoked on POR, BOR and wake-up from Sleep. The 5-10 μs delay is based on a 1 MHz system clock.

#### TABLE 15-2: STATUS BITS AND THEIR SIGNIFICANCE

| POR | BOR | то | PD |                                                         |

|-----|-----|----|----|---------------------------------------------------------|

| 0   | x   | 1  | 1  | Power-on Reset                                          |

| 0   | x   | 0  | x  | Illegal, TO is set on POR                               |

| 0   | x   | x  | 0  | Illegal, PD is set on POR                               |

| 1   | 0   | 1  | 1  | Brown-out Reset                                         |

| 1   | 1   | 0  | 1  | WDT Reset                                               |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |

| 1   | 1   | u  | u  | MCLR Reset during Normal Operation                      |

| 1   | 1   | 1  | 0  | MCLR Reset during Sleep or Interrupt Wake-up from Sleep |

**Legend:** u = unchanged, x = unknown

| SUBLW            | Subtract W from Literal                                                                                                        | XORLW            | Exclusive OR Literal with W                                                                                                |

|------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] SUBLW k                                                                                                       | Syntax:          | [label] XORLW k                                                                                                            |

| Operands:        | $0 \le k \le 255$                                                                                                              | Operands:        | $0 \leq k \leq 255$                                                                                                        |

| Operation:       | $k - (W) \rightarrow (W)$                                                                                                      | Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                              |

| Status Affected: | C, DC, Z                                                                                                                       | Status Affected: | Z                                                                                                                          |

| Description:     | The W register is subtracted (two's complement method) from the eight-bit literal 'k'. The result is placed in the W register. | Description:     | The contents of the W register<br>are XOR'ed with the eight-bit<br>literal 'k'. The result is placed in<br>the W register. |

| SUBWF            | Subtract W from f                                                                                                                                                                       | XORWF            | Exclusive OR W with f                                                                                                                                                     |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SUBWF f,d                                                                                                                                                                       | Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                                                |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                             | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                         |

| Operation:       | (f) – (W) $\rightarrow$ (destination)                                                                                                                                                   | Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                 |

| Status Affected: | C, DC, Z                                                                                                                                                                                | Status Affected: | Z                                                                                                                                                                         |

| Description:     | Subtract (two's complement<br>method) W register from register 'f'.<br>If 'd' = 0, the result is stored in the<br>W register. If 'd' = 1, the result is<br>stored back in register 'f'. | Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' = 0, the result is stored in the W register. If 'd' = 1, the result is stored back in register 'f'. |

| SWAPF            | Swap Nibbles in f                                                                                                                                            |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] SWAPF f,d                                                                                                                                   |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                            |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                      |

| Status Affected: | None                                                                                                                                                         |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' = 0, the result is placed in W register. If 'd' = 1, the result is placed in register 'f'. |

DS30487D-page 156

### 17.11 PICkit 2 Development Programmer/Debugger and PICkit 2 Debug Express

The PICkit<sup>™</sup> 2 Development Programmer/Debugger is a low-cost development tool with an easy to use interface for programming and debugging Microchip's Flash families of microcontrollers. The full featured Windows® programming interface supports baseline (PIC10F, PIC12F5xx, PIC16F5xx), midrange (PIC12F6xx, PIC16F), PIC18F, PIC24, dsPIC30, dsPIC33, and PIC32 families of 8-bit, 16-bit, and 32-bit microcontrollers, and many Microchip Serial EEPROM products. With Microchip's powerful MPLAB Integrated Development Environment (IDE) the PICkit<sup>™</sup> 2 enables in-circuit debugging on most PIC<sup>®</sup> microcontrollers. In-Circuit-Debugging runs, halts and single steps the program while the PIC microcontroller is embedded in the application. When halted at a breakpoint, the file registers can be examined and modified.

The PICkit 2 Debug Express include the PICkit 2, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

#### 17.12 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an MMC card for file storage and data applications.

### 17.13 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

### 18.1 DC Characteristics: Supply Voltage PIC16F87/88 (Industrial, Extended) PIC16LF87/88 (Industrial)

| PIC16LF87/88<br>(Industrial)          |        |                                                                     |      | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |      |       |                                                        |  |  |  |

|---------------------------------------|--------|---------------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------------------------------------------------------|--|--|--|

| PIC16F87/88<br>(Industrial, Extended) |        |                                                                     |      | $\label{eq:conditions} \begin{tabular}{lllllllllllllllllllllllllllllllllll$                                                        |      |       |                                                        |  |  |  |

| Param<br>No.                          | Symbol | Characteristic                                                      | Min  | Тур                                                                                                                                | Max  | Units | Conditions                                             |  |  |  |

|                                       | Vdd    | Supply Voltage                                                      |      |                                                                                                                                    |      |       |                                                        |  |  |  |

| D001                                  |        | PIC16LF87/88                                                        | 2.0  | _                                                                                                                                  | 5.5  | V     | HS, XT, RC and LP Oscillator mode                      |  |  |  |

| D001                                  |        | PIC16F87/88                                                         | 4.0  |                                                                                                                                    | 5.5  | V     |                                                        |  |  |  |

| D002                                  | Vdr    | RAM Data Retention<br>Voltage <sup>(1)</sup>                        | 1.5  | —                                                                                                                                  | —    | V     |                                                        |  |  |  |

| D003                                  | VPOR   | VDD Start Voltage<br>to ensure internal<br>Power-on Reset signal    | _    | _                                                                                                                                  | 0.7  | V     | See Section 15.4 "Power-on Reset (POR)"<br>for details |  |  |  |

| D004                                  | SVDD   | <b>VDD Rise Rate</b><br>to ensure internal<br>Power-on Reset signal | 0.05 | _                                                                                                                                  | —    | V/ms  | See Section 15.4 "Power-on Reset (POR)"<br>for details |  |  |  |

|                                       | VBOR   | Brown-out Reset Voltage                                             |      | •                                                                                                                                  |      | •     |                                                        |  |  |  |

| D005                                  |        | PIC16LF87/88                                                        | 3.65 |                                                                                                                                    | 4.35 | V     |                                                        |  |  |  |

| D005                                  |        | PIC16F87/88                                                         | 3.65 |                                                                                                                                    | 4.35 | V     | Fmax = 14 MHz <sup>(2)</sup>                           |  |  |  |

**Legend:** Shading of rows is to assist in readability of the table.

Note 1: This is the limit to which VDD can be lowered in Sleep mode, or during a device Reset, without losing RAM data.

2: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

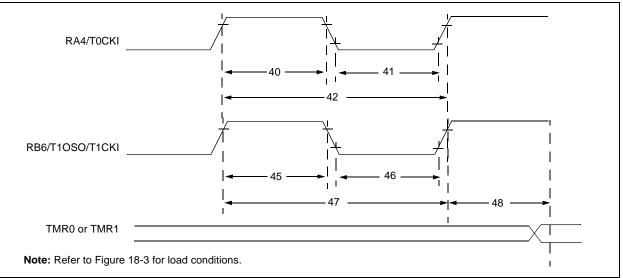

#### **FIGURE 18-8:** TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

| TABLE 18-6: | TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS |

|-------------|-----------------------------------------------|

|-------------|-----------------------------------------------|

| Param<br>No. | Symbol    |                        | Characteristic                                      |                       | Min                                       | Тур† | Max    | Units | Conditions                         |

|--------------|-----------|------------------------|-----------------------------------------------------|-----------------------|-------------------------------------------|------|--------|-------|------------------------------------|

| 40* Tt0H     |           | T0CKI High Pulse Width |                                                     | No Prescaler          | 0.5 TCY + 20                              |      | —      | ns    | Must also meet                     |

|              |           |                        |                                                     | With Prescaler        | 10                                        | _    | —      | ns    | parameter 42                       |

| 41*          | Tt0L      | T0CKI Low Pu           | T0CKI Low Pulse Width                               |                       | 0.5 TCY + 20                              | _    | —      | ns    | Must also meet                     |

|              |           |                        |                                                     | With Prescaler        | 10                                        |      | _      | ns    | parameter 42                       |

| 42*          | Tt0P      | T0CKI Period           |                                                     | No Prescaler          | Tcy + 40                                  |      | _      | ns    |                                    |

|              |           |                        |                                                     | With Prescaler        | Greater of:<br>20 or <u>Tcy + 40</u><br>N |      |        | ns    | N = prescale value<br>(2, 4,, 256) |

| 45*          | Tt1H      | T1CKI High             | Synchronous, Pres                                   | scaler = 1            | 0.5 TCY + 20                              | _    | —      | ns    | Must also meet                     |

|              |           | Time                   | Synchronous,                                        | PIC16 <b>F</b> 87/88  | 15                                        | _    | —      | ns    | parameter 47                       |

|              |           |                        | Prescaler = 2, 4, 8                                 | PIC16 <b>LF</b> 87/88 | 25                                        |      | _      | ns    |                                    |

|              |           |                        | Asynchronous                                        | PIC16 <b>F</b> 87/88  | 30                                        |      | _      | ns    |                                    |

|              |           |                        |                                                     | PIC16 <b>LF</b> 87/88 | 50                                        |      | _      | ns    |                                    |

| 46*          | Tt1L      | T1CKI Low              | Synchronous, Pres                                   | scaler = 1            | 0.5 TCY + 20                              |      | _      | ns    | Must also meet                     |

|              |           | Time                   | Synchronous,<br>Prescaler = 2, 4, 8<br>Asynchronous | PIC16 <b>F</b> 87/88  | 15                                        | _    | —      | ns    | parameter 47                       |

|              |           |                        |                                                     | PIC16 <b>LF</b> 87/88 | 25                                        | _    | —      | ns    |                                    |

|              |           |                        |                                                     | PIC16 <b>F</b> 87/88  | 30                                        | _    | —      | ns    | -                                  |

|              |           |                        |                                                     | PIC16 <b>LF</b> 87/88 | 50                                        | _    | —      | ns    |                                    |

| 47*          | Tt1P      | T1CKI Input<br>Period  | Synchronous                                         | PIC16 <b>F</b> 87/88  | Greater of:<br>30 or <u>Tcy + 40</u><br>N | _    | _      | ns    | N = prescale value<br>(1, 2, 4, 8) |

|              |           |                        |                                                     | PIC16 <b>LF</b> 87/88 | Greater of:<br>50 or <u>Tcy + 40</u><br>N |      |        |       | N = prescale value<br>(1, 2, 4, 8) |

|              |           |                        | Asynchronous                                        | PIC16 <b>F</b> 87/88  | 60                                        |      | _      | ns    |                                    |

|              |           |                        |                                                     | PIC16 <b>LF</b> 87/88 | 100                                       |      | _      | ns    |                                    |

|              | Ft1       |                        | tor Input Frequency<br>abled by setting bit T       | -                     | DC                                        |      | 32.768 | kHz   |                                    |

| 48           | TCKEZtmr1 | Delay from Ext         | ernal Clock Edge to                                 | Timer Increment       | 2 Tosc                                    | _    | 7 Tosc | —     |                                    |

t Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

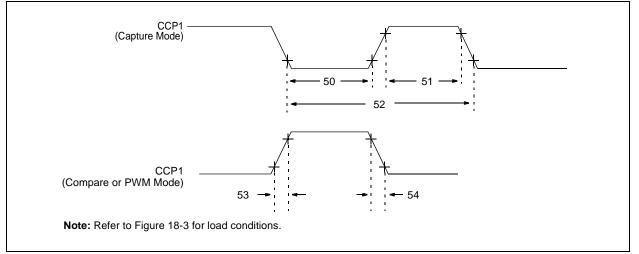

| Param<br>No. | Symbol         |                        | Characteristic                |                       | Min                    | Тур† | Max | Units | Conditions                         |

|--------------|----------------|------------------------|-------------------------------|-----------------------|------------------------|------|-----|-------|------------------------------------|

| 50*          | TccL           | CCP1                   | No Prescaler                  |                       | 0.5 Tcy + 20           | —    |     | ns    |                                    |

|              | Input Low Time |                        | Input Low Time With Prescaler |                       | 10                     | —    | —   | ns    |                                    |

|              |                |                        |                               | PIC16 <b>LF</b> 87/88 | 20                     | —    | _   | ns    |                                    |

| 51*          | TccH           | TccH CCP1 No Prescaler |                               |                       | 0.5 TCY + 20           |      | _   | ns    |                                    |

|              |                | Input High Time        | With Prescaler                | PIC16 <b>F</b> 87/88  | 10                     |      | _   | ns    |                                    |

|              |                |                        |                               | PIC16 <b>LF</b> 87/88 | 20                     |      | _   | ns    |                                    |

| 52*          | TccP           | CCP1 Input Perio       | riod                          |                       | <u>3 Tcy + 40</u><br>N | —    | _   |       | N = prescale<br>value (1, 4 or 16) |

| 53*          | TccR           | CCP1 Output Ris        | se Time                       | PIC16 <b>F</b> 87/88  | _                      | 10   | 25  | ns    |                                    |

|              |                |                        |                               | PIC16 <b>LF</b> 87/88 | —                      | 25   | 50  | ns    |                                    |

| 54*          | TccF           | CCP1 Output Fa         | ll Time                       | PIC16 <b>F</b> 87/88  | —                      | 10   | 25  | ns    |                                    |

|              |                |                        |                               | PIC16 <b>LF</b> 87/88 | —                      | 25   | 45  | ns    |                                    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

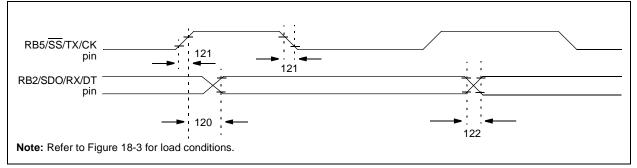

#### FIGURE 18-16: AUSART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

#### TABLE 18-11: AUSART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Param<br>No. | Sym                       | Characteristic                           |                       |   | Тур† | Max | Units | Conditions |

|--------------|---------------------------|------------------------------------------|-----------------------|---|------|-----|-------|------------|

| 120          | TckH2dtV                  | <u>SYNC XMIT (MASTER &amp;</u><br>SLAVE) | PIC16 <b>F</b> 87/88  | _ | _    | 80  | ns    |            |

|              | Clock High to Data Out Va | Clock High to Data Out Valid             | PIC16 <b>LF</b> 87/88 | — | _    | 100 | ns    |            |

| 121          | Tckrf                     | Clock Out Rise Time and Fall             | PIC16 <b>F</b> 87/88  | _ | _    | 45  | ns    |            |

|              |                           | Time (Master mode)                       | PIC16 <b>LF</b> 87/88 | _ | -    | 50  | ns    |            |

| 122          | Tdtrf                     | Data Out Rise Time and Fall              | PIC16 <b>F</b> 87/88  | — | _    | 45  | ns    |            |

|              |                           | Time                                     | PIC16 <b>LF</b> 87/88 | _ | _    | 50  | ns    |            |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

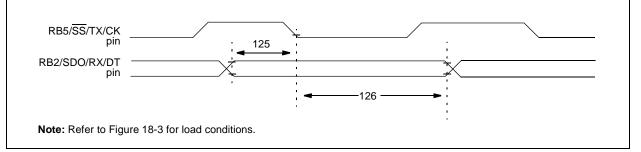

#### FIGURE 18-17: AUSART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

#### TABLE 18-12: AUSART SYNCHRONOUS RECEIVE REQUIREMENTS

| Param<br>No. | Sym      | Characteristic                                    | Min | Тур† | Max | Units | Conditions |

|--------------|----------|---------------------------------------------------|-----|------|-----|-------|------------|

| 125          | TdtV2ckL | SYNC RCV (MASTER & SLAVE)                         |     |      |     |       |            |

|              |          | Data Setup before CK $\downarrow$ (DT setup time) | 15  | —    |     | ns    |            |

| 126          | TckL2dtl | Data Hold after CK $\downarrow$ (DT hold time)    | 15  |      | —   | ns    |            |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

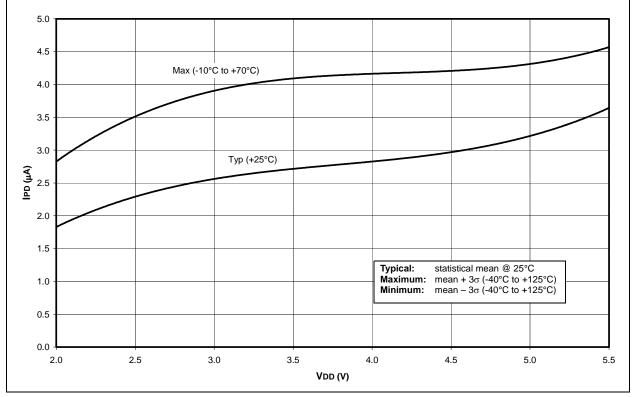

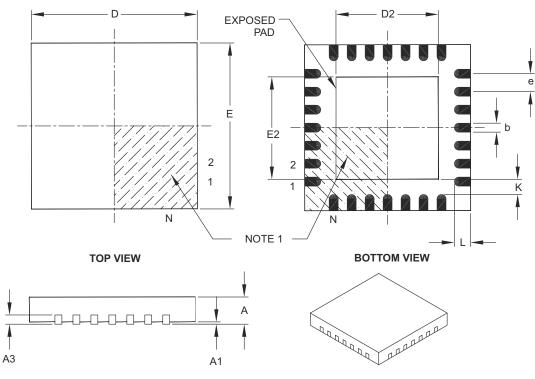

# 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units    | MILLIMETERS     |          |      |  |  |

|------------------------|----------|-----------------|----------|------|--|--|

| Dimensio               | n Limits | MIN             | NOM      | MAX  |  |  |

| Number of Pins         | Ν        |                 | 28       |      |  |  |

| Pitch                  | е        |                 | 0.65 BSC |      |  |  |

| Overall Height         | А        | 0.80            | 0.90     | 1.00 |  |  |

| Standoff               | A1       | 0.00            | 0.02     | 0.05 |  |  |

| Contact Thickness      | A3       | 0.20 REF        |          |      |  |  |

| Overall Width          | Е        |                 | 6.00 BSC |      |  |  |

| Exposed Pad Width      | E2       | 3.65            | 3.70     | 4.20 |  |  |

| Overall Length         | D        |                 | 6.00 BSC |      |  |  |

| Exposed Pad Length     | D2       | 3.65            | 3.70     | 4.20 |  |  |

| Contact Width          | b        | b 0.23 0.30 0.3 |          |      |  |  |

| Contact Length         | L        | 0.50 0.55 0.70  |          |      |  |  |

| Contact-to-Exposed Pad | К        | 0.20            | -        | -    |  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-105B

NOTES: