Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                  |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 10MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 16                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-QFN (6x6)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf87t-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name                    | PDIP/<br>SOIC<br>Pin# | SSOP<br>Pin# | QFN<br>Pin# | l/O/P<br>Type | Buffer<br>Type    | Description                                                                                                        |

|-----------------------------|-----------------------|--------------|-------------|---------------|-------------------|--------------------------------------------------------------------------------------------------------------------|

|                             |                       |              |             |               |                   | PORTB is a bidirectional I/O port. PORTB can be<br>software programmed for internal weak pull-up on all<br>inputs. |

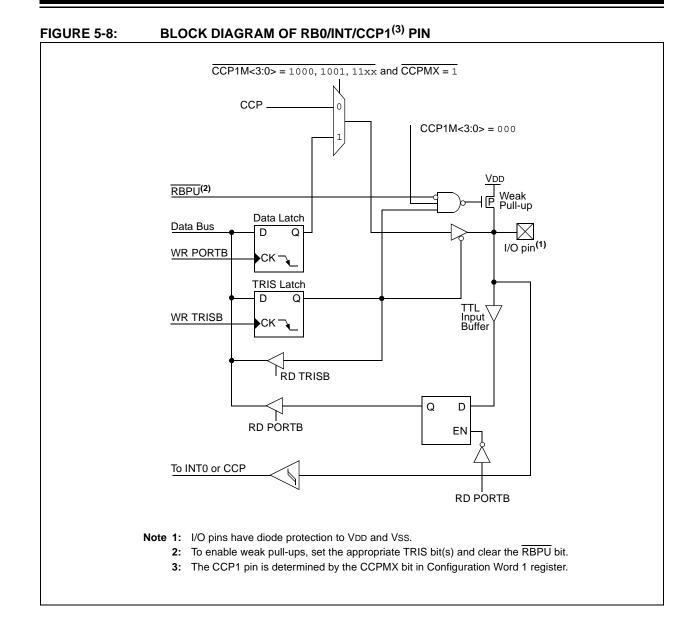

| RB0/INT/CCP1 <sup>(5)</sup> | 6                     | 7            | 7           |               |                   |                                                                                                                    |

| RB0                         |                       |              |             | I/O           | TTL               | Bidirectional I/O pin.                                                                                             |

| INT                         |                       |              |             | I             | ST <sup>(1)</sup> | External interrupt pin.                                                                                            |

| CCP1                        |                       |              |             | I/O           | ST                | Capture input, Compare output, PWM output.                                                                         |

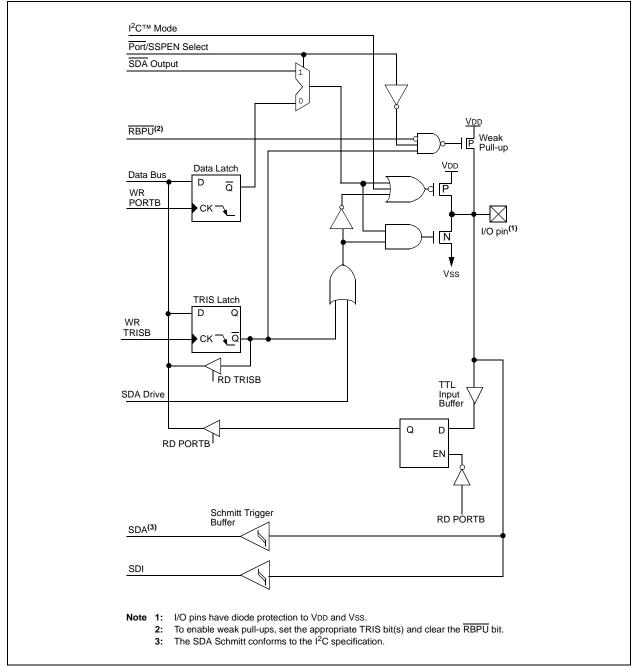

| RB1/SDI/SDA                 | 7                     | 8            | 8           |               |                   |                                                                                                                    |

| RB1<br>SDI                  |                       |              |             | I/O<br>I      | TTL<br>ST         | Bidirectional I/O pin.<br>SPI data in.                                                                             |

| SDA                         |                       |              |             | 1/0           | ST                | $I^2 C^{TM}$ data.                                                                                                 |

| RB2/SDO/RX/DT               | 8                     | 9            | 9           | 1/0           | 01                |                                                                                                                    |

| RB2                         | 0                     | 9            | 9           | I/O           | TTL               | Bidirectional I/O pin.                                                                                             |

| SDO                         |                       |              |             | 0             | ST                | SPI data out.                                                                                                      |

| RX                          |                       |              |             | I             |                   | AUSART asynchronous receive.                                                                                       |

| DT                          |                       |              |             | I/O           |                   | AUSART synchronous detect.                                                                                         |

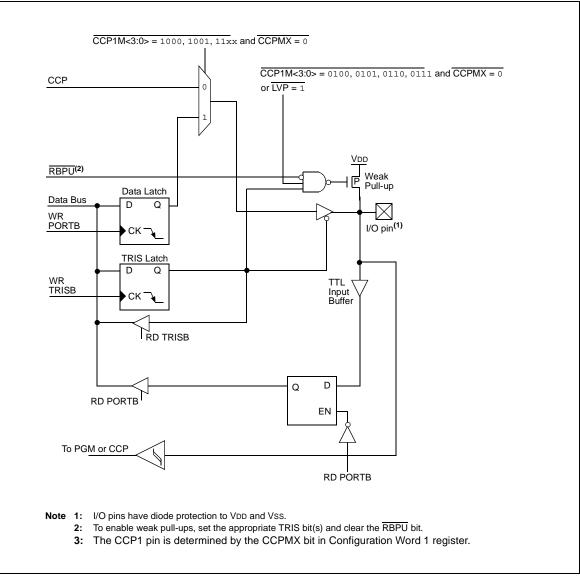

| RB3/PGM/CCP1 <sup>(5)</sup> | 9                     | 10           | 10          |               |                   |                                                                                                                    |

| RB3                         |                       |              |             | I/O           | TTL               | Bidirectional I/O pin.                                                                                             |

| PGM                         |                       |              |             | I/O           | ST                | Low-Voltage ICSP™ Programming enable pin.                                                                          |

| CCP1                        |                       |              |             | I             | ST                | Capture input, Compare output, PWM output.                                                                         |

| RB4/SCK/SCL                 | 10                    | 11           | 12          |               |                   |                                                                                                                    |

| RB4<br>SCK                  |                       |              |             | 1/0<br>1/0    | TTL<br>ST         | Bidirectional I/O pin. Interrupt-on-change pin.<br>Synchronous serial clock input/output for SPI.                  |

| SCL                         |                       |              |             | 1/0           | ST                | Synchronous serial clock input/output for SP1.                                                                     |

| RB5/SS/TX/CK                | 11                    | 12           | 13          | •             | 01                | Cynonionous senarolook inpartor r C.                                                                               |

| RB5                         | 1 11                  | 12           | 15          | I/O           | TTL               | Bidirectional I/O pin. Interrupt-on-change pin.                                                                    |

| SS                          |                       |              |             | 1/0           | TTL               | Slave select for SPI in Slave mode.                                                                                |

| TX                          |                       |              |             | 0             |                   | AUSART asynchronous transmit.                                                                                      |

| СК                          |                       |              |             | I/O           |                   | AUSART synchronous clock.                                                                                          |

| RB6/AN5/PGC/T1OSO/          | 12                    | 13           | 15          |               |                   |                                                                                                                    |

| T1CKI                       |                       |              |             |               |                   |                                                                                                                    |

|                             |                       |              |             | I/O           | TTL               | Bidirectional I/O pin. Interrupt-on-change pin.                                                                    |

| AN5 <sup>(4)</sup><br>PGC   |                       |              |             | I<br>I/O      | ST <sup>(2)</sup> | Analog input channel 5.<br>In-Circuit Debugger and programming clock pin.                                          |

| T10S0                       |                       |              |             | 0             | ST                | Timer1 oscillator output.                                                                                          |

| T1CKI                       |                       |              |             | I             | ST                | Timer1 external clock input.                                                                                       |

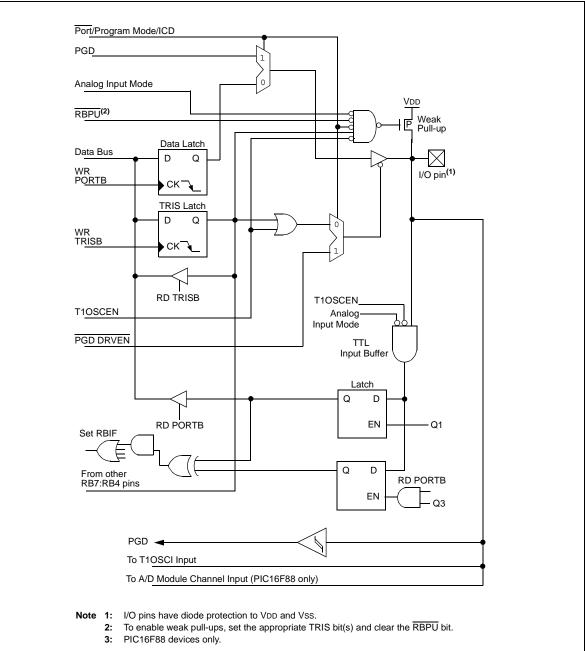

| RB7/AN6/PGD/T1OSI           | 13                    | 14           | 16          |               |                   |                                                                                                                    |

| RB7                         |                       | 17           | 10          | I/O           | TTL               | Bidirectional I/O pin. Interrupt-on-change pin.                                                                    |

| AN6 <sup>(4)</sup>          |                       |              |             | I             |                   | Analog input channel 6.                                                                                            |

| PGD                         |                       |              |             | I             | ST <sup>(2)</sup> | In-Circuit Debugger and ICSP programming data pi                                                                   |

| T1OSI                       |                       |              |             | Ι             | ST                | Timer1 oscillator input.                                                                                           |

| Vss                         | 5                     | 5, 6         | 3, 5        | Р             | -                 | Ground reference for logic and I/O pins.                                                                           |

| VDD                         | 14                    | 15, 16       | 17, 19      | Р             | -                 | Positive supply for logic and I/O pins.                                                                            |

| TABLE 1-2: | PIC16F87/88 PINOUT DESCRIPTION ( | (CONTINUED) |

|------------|----------------------------------|-------------|

|            |                                  |             |

- = Not used TTL = TTL Input ST = Schmitt Trigger Input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

4: PIC16F88 devices only.

5: The CCP1 pin is determined by the CCPMX bit in Configuration Word 1 register.

| ŀ                  | File<br>Address | A                   | File<br>ddress |                     | File<br>Address | A                       | Fi<br>Add |

|--------------------|-----------------|---------------------|----------------|---------------------|-----------------|-------------------------|-----------|

| Indirect addr.(*)  | 00h             | Indirect addr.(*)   | 80h            | Indirect addr.(*)   | 100h            | Indirect addr.(*)       | 18        |

| TMR0               | 01h             | OPTION_REG          | 81h            | TMR0                | 101h            | OPTION_REG              | 18        |

| PCL                | 02h             | PCL                 | 82h            | PCL                 | 102h            | PCL                     | 18        |

| STATUS             | 03h             | STATUS              | 83h            | STATUS              | 103h            | STATUS                  | 18        |

| FSR                | 04h             | FSR                 | 84h            | FSR                 | 104h            | FSR                     | 1         |

| PORTA              | 05h             | TRISA               | 85h            | WDTCON              | 105h            |                         | 1         |

| PORTB              | 06h             | TRISB               | 86h            | PORTB               | 106h            | TRISB                   | 1         |

|                    | 07h             |                     | 87h            |                     | 107h            |                         | 1         |

|                    | 08h             |                     | 88h            | -                   | 108h            |                         | 1         |

| -                  | 09h             |                     | 89h            |                     | 109h            |                         | 1         |

| PCLATH             | 0Ah             | PCLATH              | 8Ah            | PCLATH              | 10Ah            | PCLATH                  | 1         |

| INTCON             | 0Bh             | INTCON              | 8Bh            | INTCON              | 10Bh            | INTCON                  | 1         |

| PIR1               | 0Ch             | PIE1                | 8Ch            | EEDATA              | 10Ch            | EECON1                  | 1         |

| PIR2               | 0Dh             | PIE2                | 8Dh            | EEADR               | 10Dh            | EECON2                  | 1         |

| TMR1L              | 0Eh             | PCON                | 8Eh            | EEDATH              | 10Eh            | Reserved <sup>(1)</sup> | 1         |

| TMR1H              | 0Fh             | OSCCON              | 8Fh            | EEADRH              | 10Fh            | Reserved <sup>(1)</sup> | 1         |

| T1CON              | 10h             | OSCTUNE             | 90h            |                     | 110h            |                         | 1         |

| TMR2               | 11h             |                     | 91h            |                     |                 |                         |           |

| T2CON              | 12h             | PR2                 | 92h            |                     |                 |                         |           |

| SSPBUF             | 13h             | SSPADD              | 93h            |                     |                 |                         |           |

| SSPCON             | 14h             | SSPSTAT             | 94h            |                     |                 |                         |           |

| CCPR1L             | 15h             |                     | 95h            |                     |                 |                         |           |

| CCPR1H             | 16h             |                     | 96h            | 0                   |                 | Conorol                 |           |

| CCP1CON            | 17h             |                     | 97h            | General<br>Purpose  |                 | General<br>Purpose      |           |

| RCSTA              | 18h             | TXSTA               | 98h            | Register            |                 | Register                |           |

| TXREG              | 19h             | SPBRG               | 99h            | 16 Bytes            |                 | 16 Bytes                |           |

| RCREG              | 1Ah             |                     | 9Ah            |                     |                 |                         |           |

|                    | 1Bh             | ANSEL               | 9Bh            |                     |                 |                         |           |

|                    | 1Ch             | CMCON               | 9Ch            |                     |                 |                         |           |

|                    | 1Dh             | CVRCON              | 9Dh            |                     |                 |                         |           |

| ADRESH             | 1Eh             | ADRESL              | 9Eh            |                     |                 |                         |           |

| ADCON0             | 1Fh             | ADCON1              | 9Fh            |                     | 11Fh            |                         | 1         |

|                    | 20h             |                     | A0h            |                     | 120h            |                         | 1         |

|                    |                 | General             | -              | General             |                 | General                 |           |

|                    |                 | Purpose<br>Register |                | Purpose<br>Register |                 | Purpose<br>Register     |           |

| General<br>Purpose |                 | 80 Bytes            |                | 80 Bytes            |                 | 80 Bytes                |           |

| Register           |                 |                     | EFh            |                     | 16Fh            |                         | 1         |

| 96 Bytes           |                 |                     | F0h            |                     | 170h            |                         | 11        |

| 20 29:00           |                 | accesses            |                | accesses            |                 | accesses                |           |

|                    |                 | 70h-7Fh             |                | 70h-7Fh             |                 | 70h-7Fh                 |           |

|                    | 7Fh             |                     | FFh            |                     | 17Fh            |                         | 1         |

| Bank 0             |                 | Bank 1              |                | Bank 2              |                 | Bank 3                  |           |

**Note 1:** This register is reserved, maintain this register clear.

#### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 2-1. The Special Function Registers can be classified into two sets: core (CPU) and peripheral. Those registers associated with the core functions are described in detail in this section. Those related to the operation of the peripheral features are described in detail in the peripheral feature section.

| Address              | Name                               | Bit 7       | Bit 6               | Bit 5         | Bit 4           | Bit 3                          | Bit 2           | Bit 1        | Bit 0     | Value on:<br>POR, BOR  | Details<br>on<br>page |

|----------------------|------------------------------------|-------------|---------------------|---------------|-----------------|--------------------------------|-----------------|--------------|-----------|------------------------|-----------------------|

| Bank 0               | •                                  | •           |                     | •             | •               | •                              | •               | •            |           | •                      |                       |

| 00h <sup>(2)</sup>   | INDF                               | Addressing  | g this locatio      | n uses conte  | ents of FSR to  | address data                   | memory (not     | a physical r | egister)  | 0000 0000              | 26, 135               |

| 01h                  | TMR0                               | Timer0 Mc   | dule Registe        | ər            |                 |                                |                 |              |           | XXXX XXXX              | 69                    |

| 02h <sup>(2)</sup>   | PCL                                | Program C   | Counter (PC)        | Least Signif  | icant Byte      |                                |                 |              |           | 0000 0000              |                       |

| 03h <sup>(2)</sup>   | STATUS                             | IRP         | RP1                 | RP0           | TO              | PD                             | Z               | DC           | С         | 0001 1xxx              | 17                    |

| 04h <sup>(2)</sup>   | FSR                                | Indirect Da | ata Memory          | Address Poir  | nter            |                                |                 |              |           | xxxx xxxx              | 135                   |

| 05h                  | PORTA                              |             |                     |               |                 | hen read (PIC<br>hen read (PIC |                 |              |           | xxxx 0000<br>xxx0 0000 | 52                    |

| 06h                  | PORTB                              |             |                     |               |                 | hen read (PIC<br>hen read (PIC |                 |              |           | xxxx xxxx<br>00xx xxxx | 58                    |

| 07h                  | —                                  | Unimplem    | ented               |               |                 |                                |                 |              |           | —                      | _                     |

| 08h                  | _                                  | Unimplem    | ented               |               |                 |                                |                 |              |           | _                      | _                     |

| 09h                  | _                                  | Unimplem    | ented               |               |                 |                                |                 |              |           | _                      | _                     |

| 0Ah <sup>(1,2)</sup> | PCLATH                             | _           | _                   | _             | Write Buffer    | for the Upper                  | 5 bits of the F | Program Cou  | unter     | 0 0000                 | 135                   |

| 0Bh <sup>(2)</sup>   | INTCON                             | GIE         | PEIE                | TMR0IE        | INTOIE          | RBIE                           | TMR0IF          | INTOIF       | RBIF      | 0000 000x              | 19, 69,<br>77         |

| 0Ch                  | PIR1                               | _           | ADIF <sup>(4)</sup> | RCIF          | TXIF            | SSPIF                          | CCP1IF          | TMR2IF       | TMR1IF    | -000 0000              | 21, 77                |

| 0Dh                  | PIR2                               | OSFIF       | CMIF                | —             | EEIF            | —                              | _               | _            | _         | 00-0                   | 23, 34                |

| 0Eh                  | TMR1L                              | Holding Re  | egister for th      | e Least Sign  | ificant Byte of | the 16-bit TM                  | IR1 Register    | •            | •         | xxxx xxxx              | 77, 83                |

| 0Fh                  | TMR1H                              | Holding Re  | egister for th      | e Most Signi  | ficant Byte of  | the 16-bit TM                  | R1 Register     |              |           | xxxx xxxx              | 77, 83                |

| 10h                  | T1CON                              | _           | T1RUN               | T1CKPS1       | T1CKPS0         | T1OSCEN                        | T1SYNC          | TMR1CS       | TMR10N    | -000 0000              | 72, 83                |

| 11h                  | TMR2                               | Timer2 Mc   | dule Registe        | er            |                 |                                |                 | •            | •         | 0000 0000              | 80, 85                |

| 12h                  | T2CON                              | _           | TOUTPS3             | TOUTPS2       | TOUTPS1         | TOUTPS0                        | TMR2ON          | T2CKPS1      | T2CKPS0   | -000 0000              | 80, 85                |

| 13h                  | SSPBUF                             | Synchrono   | ous Serial Po       | ort Receive B | uffer/Transmi   | t Register                     |                 |              |           | xxxx xxxx              | 90, 95                |

| 14h                  | SSPCON                             | WCOL        | SSPOV               | SSPEN         | CKP             | SSPM3                          | SSPM2           | SSPM1        | SSPM0     | 0000 0000              | 89, 95                |

| 15h                  | CCPR1L                             | Capture/C   | ompare/PWI          | M Register 1  | (LSB)           |                                |                 |              |           | xxxx xxxx              | 83, 85                |

| 16h                  | CCPR1H                             | Capture/C   | ompare/PWI          | M Register 1  | (MSB)           |                                |                 |              |           | XXXX XXXX              | 83, 85                |

| 17h                  | CCP1CON                            | _           | _                   | CCP1X         | CCP1Y           | CCP1M3                         | CCP1M2          | CCP1M1       | CCP1M0    | 00 0000                | 81, 83                |

| 18h                  | RCSTA                              | SPEN        | RX9                 | SREN          | CREN            | ADDEN                          | FERR            | OERR         | RX9D      | 0000 000x              | 98, 99                |

| 19h                  | TXREG                              | AUSART 1    | Fransmit Dat        | a Register    |                 |                                |                 |              |           | 0000 0000              | 103                   |

| 1Ah                  | RCREG AUSART Receive Data Register |             |                     |               |                 |                                |                 |              | 0000 0000 | 105                    |                       |

| 1Bh                  | _                                  | Unimplem    | ented               |               |                 |                                |                 |              |           | _                      |                       |

| 1Ch                  | _                                  | Unimplem    | ented               |               |                 |                                |                 |              |           | _                      |                       |

| 1Dh                  | —                                  | Unimplem    | ented               |               |                 |                                |                 |              |           | —                      | _                     |

| 1Eh                  | ADRESH <sup>(4)</sup>              | A/D Resul   | t Register Hi       | gh Byte       |                 |                                |                 |              |           | xxxx xxxx              | 120                   |

| 1Fh                  | ADCON0 <sup>(4)</sup>              | ADCS1       | ADCS0               | CHS2          | CHS1            | CHS0                           | GO/DONE         | _            | ADON      | 0000 00-0              | 114, 120              |

TABLE 2-1:

SPECIAL FUNCTION REGISTER SUMMARY

**Legend:** x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for PC<12:8>, whose contents are transferred to the upper byte of the program counter.

2: These registers can be addressed from any bank.

3: RA5 is an input only; the state of the TRISA5 bit has no effect and will always read '1'.

4: PIC16F88 device only.

## 3.3 Reading Data EEPROM Memory

To read a data memory location, the user must write the address to the EEADR register, clear the EEPGD control bit (EECON1<7>) and then set control bit RD (EECON1<0>). The data is available in the very next cycle in the EEDATA register; therefore, it can be read in the next instruction (see Example 3-1). EEDATA will hold this value until another read or until it is written to by the user (during a write operation).

The steps to reading the EEPROM data memory are:

- 1. Write the address to EEADR. Make sure that the address is not larger than the memory size of the device.

- 2. Clear the EEPGD bit to point to EEPROM data memory.

- 3. Set the RD bit to start the read operation.

- 4. Read the data from the EEDATA register.

|         |         | 0/(1)  |                       |

|---------|---------|--------|-----------------------|

| BANKSEL | EEADR   | ;      | Select Bank of EEADR  |

| MOVF    | ADDR, W | ;      |                       |

| MOVWF   | EEADR   | ;      | Data Memory Address   |

|         |         | ;      | to read               |

| BANKSEL | EECON1  | ;      | Select Bank of EECON1 |

| BCF     | EECON1, | EEPGD; | Point to Data memory  |

| BSF     | EECON1, | RD ;   | EE Read               |

| BANKSEL | EEDATA  | ;      | Select Bank of EEDATA |

| MOVF    | EEDATA, | W;     | W = EEDATA            |

|         |         |        |                       |

#### EXAMPLE 3-1: DATA EEPROM READ

## 3.4 Writing to Data EEPROM Memory

To write an EEPROM data location, the user must first write the address to the EEADR register and the data to the EEDATA register. Then, the user must follow a specific write sequence to initiate the write for each byte.

The write will not initiate if the write sequence is not exactly followed (write 55h to EECON2, write AAh to EECON2, then set WR bit) for each byte. We strongly recommend that interrupts be disabled during this code segment (see Example 3-2).

Additionally, the WREN bit in EECON1 must be set to enable write. This mechanism prevents accidental writes to data EEPROM due to errant (unexpected) code execution (i.e., lost programs). The user should keep the WREN bit clear at all times except when updating EEPROM. The WREN bit is not cleared by hardware

After a write sequence has been initiated, clearing the WREN bit will not affect this write cycle. The WR bit will be inhibited from being set unless the WREN bit is set. At the completion of the write cycle, the WR bit is cleared in hardware and the EE Write Complete Interrupt Flag bit (EEIF) is set. The user can either enable this interrupt or poll this bit. EEIF must be cleared by software.

The steps to write to EEPROM data memory are:

- 1. If step 10 is not implemented, check the WR bit to see if a write is in progress.

- 2. Write the address to EEADR. Make sure that the address is not larger than the memory size of the device.

- 3. Write the 8-bit data value to be programmed in the EEDATA register.

- 4. Clear the EEPGD bit to point to EEPROM data memory.

- 5. Set the WREN bit to enable program operations.

- 6. Disable interrupts (if enabled).

- 7. Execute the special five instruction sequence:

Write 55h to EECON2 in two steps (first to W, then to EECON2).

Write AAh to EECON2 in two steps (first to W, then to EECON2).

Set the WR bit.

- 8. Enable interrupts (if using interrupts).

- 9. Clear the WREN bit to disable program operations.

- 10. At the completion of the write cycle, the WR bit is cleared and the EEIF interrupt flag bit is set (EEIF must be cleared by firmware). If step 1 is not implemented, then firmware should check for EEIF to be set, or WR to clear, to indicate the end of the program cycle.

#### EXAMPLE 3-2: DATA EEPROM WRITE

| -  |                      |                         |          |       |   |                   |

|----|----------------------|-------------------------|----------|-------|---|-------------------|

|    |                      | BANKSEL                 | EECON1   |       | ' | Select Bank of    |

|    |                      | DEEGO                   | DDCOM1   | MD    | ' | EECON1            |

|    |                      |                         |          |       |   | Wait for write    |

|    |                      | GOTO                    | •        |       |   | to complete       |

|    |                      | BANKSEL                 | EEADR    |       | ' | Select Bank of    |

|    |                      | MOLTE                   | 1000 11  |       | ' | EEADR             |

|    |                      |                         | ADDR, W  |       | ; |                   |

|    |                      | MOVWF                   | EEADR    |       |   | Data Memory       |

|    |                      |                         |          | _     | ; | Address to write  |

|    |                      |                         | VALUE, N |       | ; |                   |

|    |                      | MOVWF                   | EEDATA   |       |   | Data Memory Value |

|    |                      |                         |          |       | ' | to write          |

|    |                      | BANKSEL                 | EECON1   |       | ' | Select Bank of    |

|    |                      |                         |          |       | ' | EECON1            |

|    |                      | BCF                     | EECON1,  | EEPGD | ; | Point to DATA     |

|    |                      |                         |          |       |   | memory            |

|    |                      | BSF                     | EECON1,  | WREN  | ; | Enable writes     |

|    |                      |                         |          |       |   |                   |

| ١. | _                    | BCF                     | INTCON,  | GIE   | ; | Disable INTs.     |

| Ш  |                      | MOVLW                   |          |       | ; |                   |

| Ш  | g g                  | MOVWF                   | EECON2   |       | ; | Write 55h         |

| Ш  | Required<br>Sequence | MOVWF<br>MOVLW<br>MOVWF | AAh      |       | ; |                   |

| Ш  | sed %                | MOVWF                   | EECON2   |       | ; | Write AAh         |

| Ш  | E 0)                 |                         |          | WR    | ; | Set WR bit to     |

| l  |                      |                         |          |       | ; | begin write       |

|    |                      | BSF                     | INTCON,  | GIE   | ; | Enable INTs.      |

|    |                      | BCF                     | EECON1,  | WREN  | ; | Disable writes    |

| 1  |                      |                         |          |       |   |                   |

## FIGURE 5-11: BLOCK DIAGRAM OF RB3/PGM/CCP1<sup>(3)</sup> PIN

## FIGURE 5-15: BLOCK DIAGRAM OF RB7/AN6<sup>(3)</sup>/PGD/T1OSI PIN

#### 6.3 Using Timer0 with an External Clock

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI, with the internal phase clocks, is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for T0CKI to be high for at least 2 Tosc (and a small RC delay of 20 ns) and low for at least 2 Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

#### 6.4 Prescaler

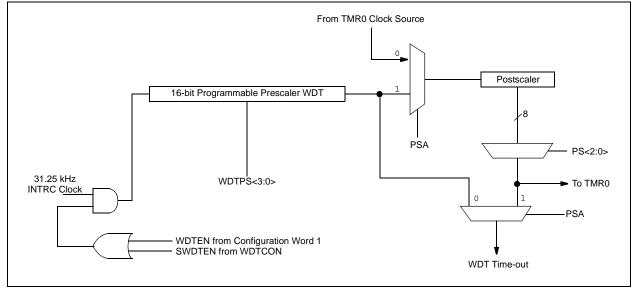

There is only one prescaler available, which is mutually exclusively shared between the Timer0 module and the Watchdog Timer. A prescaler assignment for the Timer0 module means that the prescaler cannot be used by the Watchdog Timer and vice versa. This prescaler is not readable or writable (see Figure 6-1). Note: Although the prescaler can be assigned to either the WDT or Timer0, but not both, a new divide counter is implemented in the WDT circuit to give multiple WDT time-out selections. This allows TMR0 and WDT to each have their own scaler. Refer to Section 15.12 "Watchdog Timer (WDT)" for further details.

The PSA and PS2:PS0 bits (OPTION\_REG<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

| Note: | Writing to TMR0, when the prescaler is  |

|-------|-----------------------------------------|

|       | assigned to Timer0, will clear the      |

|       | prescaler count but will not change the |

|       | prescaler assignment.                   |

### **REGISTER 6-1:** OPTION\_REG: OPTION CONTROL REGISTER (ADDRESS 81h, 181h)

|         | R/W-1       | R/W-1                                                                        | R/W-1           | R/W-1        | R/W-1          | R/W-1     | R/W-1         | R/W-1       |  |

|---------|-------------|------------------------------------------------------------------------------|-----------------|--------------|----------------|-----------|---------------|-------------|--|

|         | RBPU        | INTEDG                                                                       | TOCS            | T0SE         | PSA            | PS2       | PS1           | PS0         |  |

|         | bit 7       | ·                                                                            | ·               |              |                |           |               | bit 0       |  |

| bit 7   | RBPU: PC    | RTB Pull-up                                                                  | Enable bit      |              |                |           |               |             |  |

| bit 6   | INTEDG:     | nterrupt Edge                                                                | Select bit      |              |                |           |               |             |  |

| bit 5   | TOCS: TM    | R0 Clock Sou                                                                 | rce Select bi   | t            |                |           |               |             |  |

|         | 1 = Transit | ion on T0CKI                                                                 | pin             |              |                |           |               |             |  |

|         | 0 = Interna | I instruction a                                                              | ycle clock (C   | LKO)         |                |           |               |             |  |

| bit 4   | TOSE: TMI   | R0 Source Ed                                                                 | ge Select bit   | :            |                |           |               |             |  |

|         | 1 = Increm  | ent on high-to                                                               | o-low transitio | on on T0CKI  | pin            |           |               |             |  |

|         |             | ent on low-to                                                                |                 |              | •              |           |               |             |  |

| bit 3   |             | caler Assignn                                                                | -               |              | •              |           |               |             |  |

|         | 1 = Presca  | ller is assigne                                                              | d to the WD     | г            |                |           |               |             |  |

|         |             | ler is assigne                                                               |                 |              |                |           |               |             |  |

| bit 2-0 | PS<2:0>:    | Prescaler Rat                                                                | e Select bits   |              |                |           |               |             |  |

|         | Bit Value   | TMR0 Rate                                                                    | WDT Rate        |              |                |           |               |             |  |

|         | 000         | 1:2                                                                          | 1:1             |              |                |           |               |             |  |

|         | 001         | 1:4                                                                          | 1:2             |              |                |           |               |             |  |

|         | 010         | 1:8                                                                          | 1:4             |              |                |           |               |             |  |

|         | 011<br>100  | 1:16<br>1:32                                                                 | 1:8<br>1:16     |              |                |           |               |             |  |

|         | 100         | 1:64                                                                         | 1:32            |              |                |           |               |             |  |

|         | 110         | 1:128                                                                        | 1:64            |              |                |           |               |             |  |

|         | 111         | 1 : 256                                                                      | 1 : 128         |              |                |           |               |             |  |

|         | Legend:     |                                                                              |                 |              |                |           |               |             |  |

|         | R = Reada   | ble bit                                                                      | W = Wri         | table bit    | U = Unimpl     | emented b | it. read as ' | 0'          |  |

|         | -n = Value  |                                                                              | '1' = Bit       |              | '0' = Bit is c |           | x = Bit is u  |             |  |

|         |             |                                                                              | i – Dil         | 5 501        |                |           |               | INTOWN      |  |

|         | Note:       | To avoid an ι                                                                | unintended d    | evice Reset, | the instructi  | on sequen | ce shown ir   | n the "PIC® |  |

|         |             | Mid-Range N                                                                  |                 |              |                | •         |               |             |  |

|         |             | changing the prescaler assignment from Timer0 to the WDT. This sequence must |                 |              |                |           |               |             |  |

|         |             | be followed even if the WDT is disabled.                                     |                 |              |                |           |               |             |  |

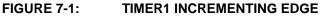

## 7.2 Timer1 Operation in Timer Mode

Timer mode is selected by clearing the TMR1CS (T1CON<1>) bit. In this mode, the input clock to the timer is FOSC/4. The synchronize control bit, T1SYNC (T1CON<2>), has no effect since the internal clock is always in sync.

#### 7.3 Timer1 Counter Operation

Timer1 may operate in Asynchronous or Synchronous mode, depending on the setting of the TMR1CS bit.

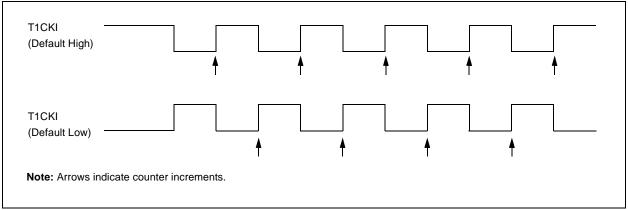

When Timer1 is being incremented via an external source, increments occur on a rising edge. After Timer1 is enabled in Counter mode, the module must first have a falling edge before the counter begins to increment.

#### 7.4 Timer1 Operation in Synchronized Counter Mode

Counter mode is selected by setting bit TMR1CS. In this mode, the timer increments on every rising edge of clock input on pin RB7/PGD/T1OSI when bit T1OSCEN is set, or on pin RB6/PGC/T1OSO/T1CKI when bit T1OSCEN is cleared.

If  $\overline{\text{T1SYNC}}$  is cleared, then the external clock input is synchronized with internal phase clocks. The synchronization is done after the prescaler stage. The prescaler stage is an asynchronous ripple counter.

In this configuration, during Sleep mode, Timer1 will not increment even if the external clock is present since the synchronization circuit is shut off. The prescaler, however, will continue to increment.

## 9.0 CAPTURE/COMPARE/PWM (CCP) MODULE

The Capture/Compare/PWM (CCP) module contains a 16-bit register that can operate as a:

- 16-bit Capture register

- 16-bit Compare register

- PWM Master/Slave Duty Cycle register.

Table 9-1 shows the timer resources of the CCP module modes.

Capture/Compare/PWM Register 1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. The special event trigger is generated by a compare match which will reset Timer1 and start an A/D conversion (if the A/D module is enabled). The CCP module's input/output pin (CCP1) can be configured as RB0 or RB3. This selection is set in bit 12 (CCPMX) of the Configuration Word.

Additional information on the CCP module is available in the "*PIC*<sup>®</sup> *Mid-Range MCU Family Reference Manual*" (DS33023) and in Application Note *AN594*, "*Using the CCP Module*(*s*)" (DS00594).

#### TABLE 9-1: CCP MODE – TIMER RESOURCE

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

#### **REGISTER 9-1: CCP1CON: CAPTURE/COMPARE/PWMCONTROL REGISTER 1 (ADDRESS 17h)**

| CUPIC                       | JN: CAPIC                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | UNIKULK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | EGISIER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I (ADDRE                                                                | 55 I <i>I</i> II) |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------|

| U-0                         | U-0                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W-0                                                                   | R/W-0             |

| —                           | _                                                                                                                                                                                                                                                                                                                                                                                            | CCP1X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CCP1Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CCP1M3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CCP1M2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CCP1M1                                                                  | CCP1M0            |

| bit 7                       |                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                         | bit 0             |

|                             |                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                         |                   |