Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 10MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 16                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 368 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 7x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                           |

| Supplier Device Package    | 18-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf88-i-so |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name                    | PDIP/<br>SOIC<br>Pin# | SSOP<br>Pin# | QFN<br>Pin# | I/O/P<br>Type | Buffer<br>Type    | Description                                                                                                        |  |  |

|-----------------------------|-----------------------|--------------|-------------|---------------|-------------------|--------------------------------------------------------------------------------------------------------------------|--|--|

|                             |                       |              |             |               |                   | PORTB is a bidirectional I/O port. PORTB can be<br>software programmed for internal weak pull-up on all<br>inputs. |  |  |

| RB0/INT/CCP1 <sup>(5)</sup> | 6                     | 7            | 7           |               |                   |                                                                                                                    |  |  |

| RB0                         |                       |              |             | I/O           | TTL               | Bidirectional I/O pin.                                                                                             |  |  |

| INT                         |                       |              |             | I             | ST <sup>(1)</sup> | External interrupt pin.                                                                                            |  |  |

| CCP1                        |                       |              |             | I/O           | ST                | Capture input, Compare output, PWM output.                                                                         |  |  |

| RB1/SDI/SDA                 | 7                     | 8            | 8           |               |                   |                                                                                                                    |  |  |

| RB1<br>SDI                  |                       |              |             | I/O<br>I      | TTL<br>ST         | Bidirectional I/O pin.<br>SPI data in.                                                                             |  |  |

| SDA                         |                       |              |             | 1/0           | ST                | $I^2 C^{TM}$ data.                                                                                                 |  |  |

| RB2/SDO/RX/DT               | 8                     | 9            | 9           | 1/0           | 01                |                                                                                                                    |  |  |

| RB2                         | 0                     | 9            | 9           | I/O           | TTL               | Bidirectional I/O pin.                                                                                             |  |  |

| SDO                         |                       |              |             | 0             | ST                | SPI data out.                                                                                                      |  |  |

| RX                          |                       |              |             | I             |                   | AUSART asynchronous receive.                                                                                       |  |  |

| DT                          |                       |              |             | I/O           |                   | AUSART synchronous detect.                                                                                         |  |  |

| RB3/PGM/CCP1 <sup>(5)</sup> | 9                     | 10           | 10          |               |                   |                                                                                                                    |  |  |

| RB3                         |                       |              |             | I/O           | TTL               | Bidirectional I/O pin.                                                                                             |  |  |

| PGM                         |                       |              |             | I/O           | ST                | Low-Voltage ICSP™ Programming enable pin.                                                                          |  |  |

| CCP1                        |                       |              |             | I             | ST                | Capture input, Compare output, PWM output.                                                                         |  |  |

| RB4/SCK/SCL                 | 10                    | 11           | 12          |               |                   |                                                                                                                    |  |  |

| RB4<br>SCK                  |                       |              |             | 1/0<br>1/0    | TTL<br>ST         | Bidirectional I/O pin. Interrupt-on-change pin.<br>Synchronous serial clock input/output for SPI.                  |  |  |

| SCL                         |                       |              |             | 1/0           | ST                | Synchronous serial clock input/output for SP1.                                                                     |  |  |

| RB5/SS/TX/CK                | 11                    | 12           | 13          | •             | 01                | Cynonionous senarolook inpartor r C.                                                                               |  |  |

| RB5                         | 1 11                  | 12           | 15          | I/O           | TTL               | Bidirectional I/O pin. Interrupt-on-change pin.                                                                    |  |  |

| SS                          |                       |              |             | 1/0           | TTL               | Slave select for SPI in Slave mode.                                                                                |  |  |

| TX                          |                       |              |             | 0             |                   | AUSART asynchronous transmit.                                                                                      |  |  |

| СК                          |                       |              |             | I/O           |                   | AUSART synchronous clock.                                                                                          |  |  |

| RB6/AN5/PGC/T1OSO/          | 12                    | 13           | 15          |               |                   |                                                                                                                    |  |  |

| T1CKI                       |                       |              |             |               |                   |                                                                                                                    |  |  |

|                             |                       |              |             | I/O           | TTL               | Bidirectional I/O pin. Interrupt-on-change pin.                                                                    |  |  |

| AN5 <sup>(4)</sup><br>PGC   |                       |              |             | I<br>I/O      | ST <sup>(2)</sup> | Analog input channel 5.<br>In-Circuit Debugger and programming clock pin.                                          |  |  |

| T10S0                       |                       |              |             | 0             | ST                | Timer1 oscillator output.                                                                                          |  |  |

| T1CKI                       |                       |              |             | I             | ST                | Timer1 external clock input.                                                                                       |  |  |

| RB7/AN6/PGD/T1OSI           | 13                    | 14           | 16          |               |                   |                                                                                                                    |  |  |

| RB7                         |                       | 17           | 10          | I/O           | TTL               | Bidirectional I/O pin. Interrupt-on-change pin.                                                                    |  |  |

| AN6 <sup>(4)</sup>          |                       |              |             | I             |                   | Analog input channel 6.                                                                                            |  |  |

| PGD                         |                       |              |             | I             | ST <sup>(2)</sup> | In-Circuit Debugger and ICSP programming data pi                                                                   |  |  |

| T1OSI                       |                       |              |             | Ι             | ST                | Timer1 oscillator input.                                                                                           |  |  |

| Vss                         | 5                     | 5, 6         | 3, 5        | Р             | -                 | Ground reference for logic and I/O pins.                                                                           |  |  |

| VDD                         | 14                    | 15, 16       | 17, 19      | Р             | -                 | Positive supply for logic and I/O pins.                                                                            |  |  |

| TABLE 1-2: | PIC16F87/88 PINOUT DESCRIPTION ( | (CONTINUED) |

|------------|----------------------------------|-------------|

|            |                                  |             |

- = Not used TTL = TTL Input ST = Schmitt Trigger Input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC Oscillator mode and a CMOS input otherwise.

4: PIC16F88 devices only.

5: The CCP1 pin is determined by the CCPMX bit in Configuration Word 1 register.

| Address               | Name       | Bit 7                    | Bit 6          | Bit 5         | Bit 4         | Bit 3          | Bit 2           | Bit 1         | Bit 0     | Value on:<br>POR, BOR  | Details<br>on<br>page |

|-----------------------|------------|--------------------------|----------------|---------------|---------------|----------------|-----------------|---------------|-----------|------------------------|-----------------------|

| Bank 2                |            |                          |                |               |               |                |                 |               |           |                        |                       |

| 100h <sup>(2)</sup>   | INDF       | Addressing               | g this locatio | n uses conte  | nts of FSR to | address data   | memory (not     | a physical r  | egister)  | 0000 0000              | 26, 135               |

| 101h                  | TMR0       | Timer0 Mc                | dule Registe   | er            |               |                |                 |               |           | xxxx xxxx              | 69                    |

| 102h <sup>(2)</sup>   | PCL        | Program C                | Counter's (PC  | C) Least Sign | ificant Byte  |                |                 |               |           | 0000 0000              | 135                   |

| 103h <sup>(2)</sup>   | STATUS     | IRP                      | RP1            | RP0           | TO            | PD             | Z               | DC            | С         | 0001 1xxx              | 17                    |

| 104h <sup>(2)</sup>   | FSR        | Indirect Da              | ata Memory /   | Address Poin  | iter          |                |                 |               |           | xxxx xxxx              | 135                   |

| 105h                  | WDTCON     | _                        | _              | _             | WDTPS3        | WDTPS2         | WDTPS1          | WDTPS0        | SWDTEN    | 0 1000                 | 142                   |

| 106h                  | PORTB      |                          |                |               |               | hen read (PIC  |                 |               |           | xxxx xxxx<br>00xx xxxx | 58                    |

| 107h                  | _          | Unimplem                 | ented          |               |               |                |                 |               |           | —                      | —                     |

| 108h                  | _          | Unimplem                 | ented          |               |               |                |                 |               |           | _                      |                       |

| 109h                  | —          | Unimplem                 | ented          |               |               |                |                 |               |           | —                      | _                     |

| 10Ah <b>(1,2)</b>     | PCLATH     | _                        | -              | -             | Write Buffer  | for the Upper  | 5 bits of the F | Program Cou   | unter     | 0 0000                 | 135                   |

| 10Bh <sup>(2)</sup>   | INTCON     | GIE                      | PEIE           | TMR0IE        | INT0IE        | RBIE           | TMR0IF          | INTOIF        | RBIF      | 0000 000x              | 19, 69,<br>77         |

| 10Ch                  | EEDATA     | EEPROM/                  | Flash Data F   | Register Low  | Byte          |                |                 |               |           | xxxx xxxx              | 34                    |

| 10Dh                  | EEADR      | EEPROM/                  | Flash Addre    | ss Register L | ow Byte       |                |                 |               |           | xxxx xxxx              | 34                    |

| 10Eh                  | EEDATH     | —                        | _              | EEPROM/F      | lash Data Re  | gister High By | te              |               |           | xx xxxx                | 34                    |

| 10Fh                  | EEADRH     | —                        | —              | —             | —             | EEPROM/Fla     | ash Address F   | Register High | n Byte    | xxxx                   | 34                    |

| Bank 3                |            |                          |                |               |               |                |                 |               |           |                        |                       |

| 180h <sup>(2)</sup>   | INDF       | Addressing               | g this locatio | n uses conte  | nts of FSR to | address data   | memory (not     | a physical r  | egister)  | 0000 0000              | 135                   |

| 181h                  | OPTION_REG | RBPU                     | INTEDG         | TOCS          | TOSE          | PSA            | PS2             | PS1           | PS0       | 1111 1111              | 18, 69                |

| 182h <sup>(2)</sup>   | PCL        | Program C                | Counter (PC)   | Least Signif  | ficant Byte   | •              |                 | •             |           | 0000 0000              | 135                   |

| 183h <sup>(2)</sup>   | STATUS     | IRP                      | RP1            | RP0           | TO            | PD             | Z               | DC            | С         | 0001 1xxx              | 17                    |

| 184h <sup>(2)</sup>   | FSR        | Indirect Da              | ata Memory A   | Address Poin  | ter           | •              |                 | •             |           | xxxx xxxx              | 135                   |

| 185h                  | _          | Unimplem                 | ented          |               |               |                |                 |               |           | _                      | _                     |

| 186h                  | TRISB      | PORTB Da                 | ata Direction  | Register      |               |                |                 |               |           | 1111 1111              | 58, 83                |

| 187h                  | —          | Unimplem                 | ented          |               |               |                |                 |               |           | —                      | _                     |

| 188h                  | —          | Unimplem                 | ented          |               |               |                |                 |               |           | —                      | _                     |

| 189h                  | —          | Unimplem                 | Unimplemented  |               |               |                |                 |               | —         | _                      |                       |

| 18Ah <sup>(1,2)</sup> | PCLATH     | _                        | _              | —             | Write Buffer  | for the Upper  | 5 bits of the F | Program Cou   | unter     | 0 0000                 | 135                   |

| 18Bh <sup>(2)</sup>   | INTCON     | GIE                      | PEIE           | TMR0IE        | INTOIE        | RBIE           | TMR0IF          | INTOIF        | RBIF      | 0000 000x              | 19, 69,<br>77         |

| 18Ch                  | EECON1     | EEPGD                    | _              | —             | FREE          | WRERR          | WREN            | WR            | RD        | xx x000                | 28, 34                |

| 18Dh                  | EECON2     | EEPROM                   | Control Regi   | ster 2 (not a | physical regi | ster)          |                 |               |           |                        | 34                    |

| 18Eh                  | —          | Reserved, maintain clear |                |               |               |                |                 |               |           | 0000 0000              | _                     |

| 18Fh                  | —          | Reserved, maintain clear |                |               |               |                |                 |               | 0000 0000 | _                      |                       |

### TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

**Note 1:** The upper byte of the program counter is not directly accessible. PCLATH is a holding register for PC<12:8>, whose contents are transferred to the upper byte of the program counter.

2: These registers can be addressed from any bank.

3: RA5 is an input only; the state of the TRISA5 bit has no effect and will always read '1'.

4: PIC16F88 device only.

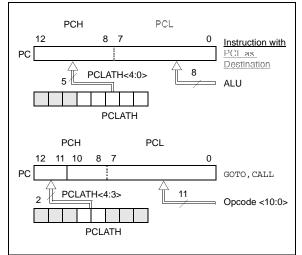

### 2.3 PCL and PCLATH

The Program Counter (PC) is 13 bits wide. The low byte comes from the PCL register which is a readable and writable register. The upper bits (PC<12:8>) are not readable but are indirectly writable through the PCLATH register. On any Reset, the upper bits of the PC will be cleared. Figure 2-4 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### FIGURE 2-4: LOADING OF PC IN DIFFERENT SITUATIONS

#### 2.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to the application note, *AN556, "Implementing a Table Read*".

### 2.3.2 STACK

The PIC16F87/88 family has an 8-level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the Stack Pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- **Note 1:** There are no status bits to indicate stack overflow or stack underflow conditions.

- 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions, or the vectoring to an interrupt address.

## 2.4 Program Memory Paging

All PIC16F87/88 devices are capable of addressing a continuous 8K word block of program memory. The CALL and GOTO instructions provide only 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction, the upper 2 bits of the address are provided by PCLATH<4:3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bits are programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is popped off the stack. Therefore, manipulation of the PCLATH<4:3> bits is not required for the RETURN instructions (which POPs the address from the stack).

| Note: | The contents of the PCLATH register are    |

|-------|--------------------------------------------|

|       | unchanged after a RETURN or RETFIE         |

|       | instruction is executed. The user must     |

|       | rewrite the contents of the PCLATH regis-  |

|       | ter for any subsequent subroutine calls or |

|       | GOTO instructions.                         |

Example 2-1 shows the calling of a subroutine in page 1 of the program memory. This example assumes that PCLATH is saved and restored by the Interrupt Service Routine (if interrupts are used).

#### EXAMPLE 2-1: CALL OF A SUBROUTINE IN PAGE 1 FROM PAGE 0

|         | ORG 0x500<br>BCF PCLATH, 4 |                                |

|---------|----------------------------|--------------------------------|

|         | BSF PCLATH, 3              | ;Select page 1<br>;(800h-FFFh) |

|         | CALL SUB1_P1               | ;Call subroutine in            |

|         | :                          | ;page 1 (800h-FFFh)            |

|         | :                          |                                |

|         | ORG 0x900                  | ;page 1 (800h-FFFh)            |

| SUB1_P1 |                            |                                |

|         | :                          | ;called subroutine             |

|         |                            | ;page 1 (800h-FFFh)            |

|         | :                          |                                |

|         | RETURN                     | ;return to                     |

|         |                            | ;Call subroutine               |

|         |                            | ; in page 0                    |

|         |                            | ;(000h-7FFh)                   |

|         |                            |                                |

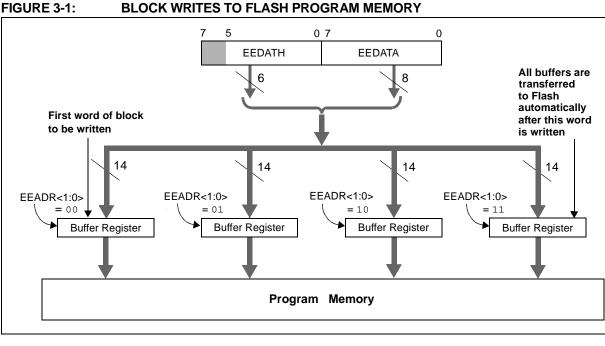

#### 3.7 Writing to Flash Program Memory

Flash program memory may only be written to if the destination address is in a segment of memory that is not write-protected, as defined in bits WRT1:WRT0 of the device Configuration Word (Register 15-1). Flash program memory must be written in four-word blocks. A block consists of four words with sequential addresses, with a lower boundary defined by an address, where EEADR < 1:0 > = 0.0. At the same time, all block writes to program memory are done as writeonly operations. The program memory must first be erased. The write operation is edge-aligned and cannot occur across boundaries.

To write to the program memory, the data must first be loaded into the buffer registers. There are four 14-bit buffer registers and they are addressed by the low 2 bits of EEADR.

The following sequence of events illustrate how to perform a write to program memory:

- Set the EEPGD and WREN bits in the EECON1 register

- ٠ Clear the FREE bit in EECON1

- Write address to EEADRH:EEADR

- Write data to EEDATH:EEDATA

- Write 55 to EECON2

- Write AA to EECON2

- Set WR bit in EECON1

The user must follow the same specific sequence to initiate the write for each word in the program block by writing each program word in sequence (00, 01, 10, 11).

There are 4 buffer register words and all four locations **MUST** be written to with correct data.

After the "BSF EECON1, WR" instruction, if EEADR  $\neq$  xxxxxx11, then a short write will occur. This short write only transfers the data to the buffer register. The WR bit will be cleared in hardware after 1 cycle.

After the "BSF EECON1, WR" instruction, if EEADR = xxxxx11, then a long write will occur. This will simultaneously transfer the data from EEDATH:EEDATA to the buffer registers and begin the write of all four words. The processor will execute the next instruction and then ignore the subsequent instruction. The user should place NOP instructions into the second words. The processor will then halt internal operations for typically 2 msec in which the write takes place. This is not Sleep mode, as the clocks and peripherals will continue to run. After the write cycle, the processor will resume operation with the 3rd instruction after the EECON1 write instruction.

After each long write, the 4 buffer registers will be reset to 3FFF.

#### 4.7.3 SEC\_RUN/RC\_RUN TO PRIMARY CLOCK SOURCE

When switching from a SEC\_RUN or RC\_RUN mode back to the primary system clock, following a change of SCS<1:0> to '00', the sequence of events that takes place will depend upon the value of the FOSC bits in the Configuration register. If the primary clock source is configured as a crystal (HS, XT or LP), then the transition will take place after 1024 clock cycles. This is necessary because the crystal oscillator has been powered down until the time of the transition. In order to provide the system with a reliable clock when the changeover has occurred, the clock will not be released to the changeover circuit until the 1024 count has expired.

During the oscillator start-up time, the system clock comes from the current system clock. Instruction execution and/or peripheral operation continues using the currently selected oscillator as the CPU clock source, until the necessary clock count has expired, to ensure that the primary system clock is stable.

To know when the OST has expired, the OSTS bit should be monitored. OSTS = 1 indicates that the Oscillator Start-up Timer has timed out and the system clock comes from the primary clock source.

Following the oscillator start-up time, the internal Q clocks are held in the Q1 state until eight falling edge clocks are counted from the primary system clock. The clock input to the Q clocks is then released and operation resumes with the primary system clock determined by the FOSC bits (see Figure 4-10).

When in SEC\_RUN mode, the act of clearing the T1OSCEN bit in the T1CON register will cause SCS<0> to be cleared, which causes the SCS<1:0> bits to revert to '00' or '10' depending on what SCS<1> is. Although the T1OSCEN bit was cleared, T1OSC will be enabled and instruction execution will continue until the OST time-out for the main system clock is complete. At that time, the system clock will switch from the T1OSC to the primary clock or the INTRC. Following this, the T1 oscillator will be shut down.

Note: If the primary system clock is either RC or EC, an internal delay timer (5-10 μs) will suspend operation after exiting Secondary Clock mode to allow the CPU to become ready for code execution.

## 4.7.3.1 Returning to Primary Clock Source Sequence

Changing back to the primary oscillator from SEC\_RUN or RC\_RUN can be accomplished by either changing SCS<1:0> to '00', or clearing the T1OSCEN bit in the T1CON register (if T1OSC was the secondary clock).

The sequence of events that follows is the same for both modes:

- If the primary system clock is configured as EC, RC or INTRC, then the OST time-out is skipped. Skip to step 3.

- 2. If the primary system clock is configured as an external oscillator (HS, XT, LP), then the OST will be active, waiting for 1024 clocks of the primary system clock.

- 3. On the following Q1, the device holds the system clock in Q1.

- 4. The device stays in Q1 while eight falling edges of the primary system clock are counted.

- 5. Once the eight counts transpire, the device begins to run from the primary oscillator.

- If the secondary clock was INTRC and the primary is not INTRC, the INTRC will be shut down to save current providing that the INTRC is not being used for any other function, such as WDT or Fail-Safe Clock monitoring.

- If the secondary clock was T1OSC, the T1OSC will continue to run if T1OSCEN is still set; otherwise, the T1 oscillator will be shut down.

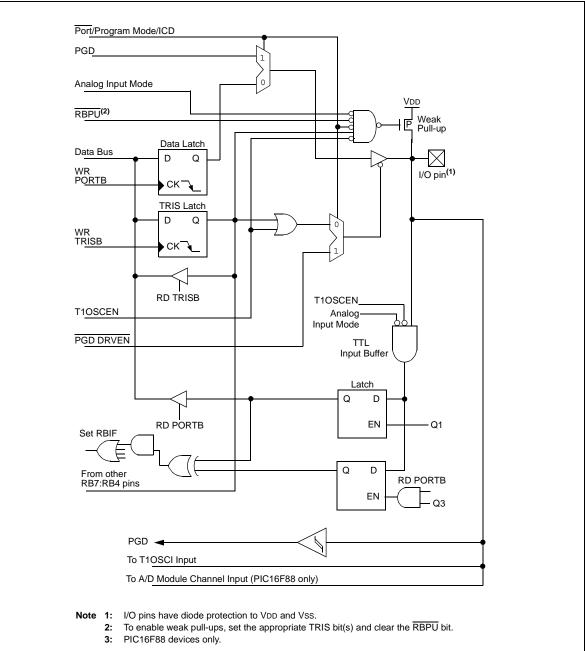

### 5.2 PORTB and the TRISB Register

PORTB is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (OPTION\_REG<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Four of PORTB's pins, RB7:RB4, have an interrupt-onchange feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupton-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RB Port Change Interrupt with Flag bit RBIF (INTCON<0>).

This interrupt can wake the device from Sleep. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

RB0/INT is an external interrupt input pin and is configured using the INTEDG bit (OPTION\_REG<6>).

PORTB is multiplexed with several peripheral functions (see Table 5-3). PORTB pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTB pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modifywrite instructions (BSF, BCF, XORWF) with TRISB as the destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

# PIC16F87/88

## FIGURE 5-15: BLOCK DIAGRAM OF RB7/AN6<sup>(3)</sup>/PGD/T1OSI PIN

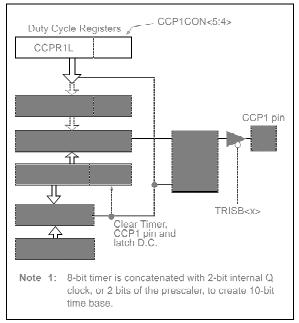

#### 9.3 PWM Mode

In Pulse-Width Modulation (PWM) mode, the CCP1 pin produces up to a 10-bit resolution PWM output. Since the CCP1 pin is multiplexed with the PORTB data latch, the TRISB<x> bit must be cleared to make the CCP1 pin an output.

| Note: | Clearing the CCP1CON register will force  |

|-------|-------------------------------------------|

|       | the CCP1 PWM output latch to the default  |

|       | low level. This is not the PORTB I/O data |

|       | latch.                                    |

Figure 9-3 shows a simplified block diagram of the CCP module in PWM mode.

For a step-by-step procedure on how to set up the CCP module for PWM operation, see **Section 9.3.3 "Setup for PWM Operation"**.

#### FIGURE 9-3: SIMPLIFIED PWM BLOCK DIAGRAM

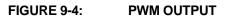

A PWM output (Figure 9-4) has a time base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

#### 9.3.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula.

#### **EQUATION 9-1:**

PWM Period = [(PR2) + 1] • 4 • Tosc • (TMR2 Prescale Value)

PWM frequency is defined as 1/[PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

| Note: | The Timer2 postscaler (see Section 8.0     |

|-------|--------------------------------------------|

|       | "Timer2 Module") is not used in the deter- |

|       | mination of the PWM frequency. The post-   |

|       | scaler could be used to have a servo       |

|       | update rate at a different frequency than  |

|       | the PWM output.                            |

#### 9.3.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available. The CCPR1L contains the eight MSbs and the CCP1CON<5:4> bits contain the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The following equation is used to calculate the PWM duty cycle in time.

#### **EQUATION 9-2:**

CCPR1L and CCP1CON<5:4> can be written to at any time, but the duty cycle value is not latched into CCPR1H until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read-only register.

The CCPR1H register and a 2-bit internal latch are used to double-buffer the PWM duty cycle. This double-buffering is essential for glitchless PWM operation.

When the CCPR1H and 2-bit latch match TMR2, concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 prescaler, the CCP1 pin is cleared.

### 10.0 SYNCHRONOUS SERIAL PORT (SSP) MODULE

#### 10.1 SSP Module Overview

The Synchronous Serial Port (SSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The SSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)

An overview of I<sup>2</sup>C operations and additional information on the SSP module can be found in the "*PIC*<sup>®</sup> *Mid-Range MCU Family Reference Manual*" (DS33023).

Refer to Application Note AN578, "Use of the SSP Module in the  $I^2C^{TM}$  Multi-Master Environment" (DS00578).

#### 10.2 SPI Mode

This section contains register definitions and operational characteristics of the SPI module.

SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO) RB2/SDO/RX/DT

- Serial Data In (SDI)

RB1/SDI/SDA

- Serial Clock (SCK)

RB4/SCK/SCL

Additionally, a fourth pin may be used when in a Slave mode of operation:

Slave Select (SS)

RB5/SS/TX/CK

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits in the SSPCON register (SSPCON<5:0>) and the SSPSTAT register (SSPSTAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Clock Edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- Slave Select mode (Slave mode only)

- Note: Before enabling the module in SPI Slave mode, the state of the clock line (SCK) must match the polarity selected for the Idle state. The clock line can be observed by reading the SCK pin. The polarity of the Idle state is determined by the CKP bit (SSPCON<4>).

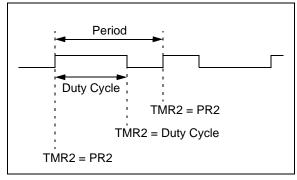

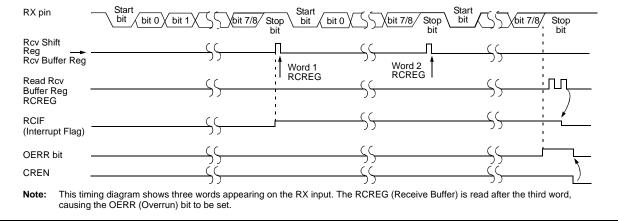

#### 11.2.2 AUSART ASYNCHRONOUS RECEIVER

The receiver block diagram is shown in Figure 11-4. The data is received on the RB2/SDO/RX/DT pin and drives the data recovery block. The data recovery block is actually a high-speed shifter, operating at x16 times the baud rate; whereas, the main receive serial shifter operates at the bit rate or at Fosc.

Once Asynchronous mode is selected, reception is enabled by setting bit CREN (RCSTA<4>).

The heart of the receiver is the Receive (Serial) Shift Register (RSR). After sampling the Stop bit, the received data in the RSR is transferred to the RCREG register (if it is empty). If the transfer is complete, flag bit, RCIF (PIR1<5>), is set. The actual interrupt can be enabled/disabled by setting/clearing enable bit RCIE (PIE1<5>). Flag bit RCIF is a read-only bit which is cleared by the hardware. It is cleared when the RCREG register has been read and is empty. The RCREG is a double-buffered register (i.e., it is a two-deep FIFO). It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting to the RSR register. On the detection of the Stop bit of the third byte, if the RCREG register is still full, the Overrun Error bit, OERR (RCSTA<1>), will be set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Overrun bit OERR has to be cleared in software. This is done by resetting the receive logic (CREN is cleared and then set). If bit OERR is set, transfers from the RSR register to the RCREG register are inhibited and no further data will be received. It is, therefore, essential to clear error bit OERR if it is set. Framing Error bit, FERR (RCSTA<2>), is set if a Stop bit is detected as clear. Bit FERR and the 9th receive bit are buffered the same way as the receive data. Reading the RCREG will load bits RX9D and FERR with new values: therefore, it is essential for the user to read the RCSTA register, before reading the RCREG register, in order not to lose the old FERR and RX9D information.

| Address                 | Name                              | Bit 7  | Bit 6  | Bit 5                 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR        | Value on<br>all other<br>Resets |

|-------------------------|-----------------------------------|--------|--------|-----------------------|--------|--------|--------|--------|--------|------------------------|---------------------------------|

| 9Ch                     | CMCON                             | C2OUT  | C10UT  | C2INV                 | C1INV  | CIS    | CM2    | CM1    | CM0    | 0000 0111              | 0000 0111                       |

| 9Dh                     | CVRCON                            | CVREN  | CVROE  | CVRR                  | —      | CVR3   | CVR2   | CVR1   | CVR0   | 000- 0000              | 000- 0000                       |

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON                            | GIE    | PEIE   | TMR0IE                | INTOIE | RBIE   | TMR0IF | INTOIF | RBIF   | 0000 000x              | 0000 000u                       |

| 0Dh                     | PIR2                              | OSFIF  | CMIF   | _                     | EEIF   | —      | —      | —      | —      | 00-0                   | 00-0                            |

| 8Dh                     | PIE2                              | OSFIE  | CMIE   | _                     | EEIE   | —      | _      | _      | _      | 00-0                   | 00-0                            |

| 05h                     | PORTA<br>(PIC16F87)<br>(PIC16F88) |        | RA6    | RA5                   | RA4    | RA3    | RA2    | RA1    | RA0    | xxxx 0000<br>xxx0 0000 | uuuu 0000<br>uuu0 0000          |

| 85h                     | TRISA                             | TRISA7 | TRISA6 | TRISA5 <sup>(1)</sup> | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1111 1111              | 1111 1111                       |

#### TABLE 13-1: REGISTERS ASSOCIATED WITH THE COMPARATOR MODULE

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the comparator module.

Note 1: Pin 5 is an input only; the state of the TRISA5 bit has no effect and will always read '1'.

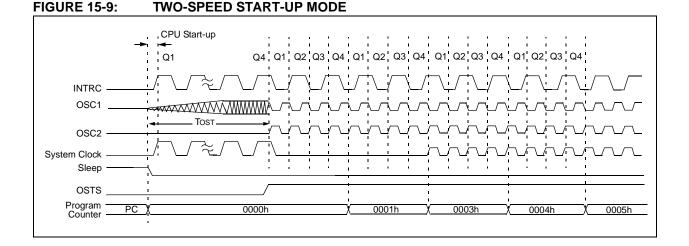

#### 15.12.3 TWO-SPEED CLOCK START-UP MODE

Two-Speed Start-up mode minimizes the latency between oscillator start-up and code execution that may be selected with the IESO (Internal/External Switchover) bit in Configuration Word 2. This mode is achieved by initially using the INTRC for code execution until the primary oscillator is stable.

If this mode is enabled and any of the following conditions exist, the system will begin execution with the INTRC oscillator. This results in almost immediate code execution with a minimum of delay.

- <u>POR and after the Power-up Timer has expired (if</u> <u>PWRTEN = 0);</u>

- or following a wake-up from Sleep;

- or a Reset when running from T1OSC or INTRC (after a Reset, SCS<1:0> are always set to '00').

| Note: | Following any Reset, the IRCF bits are    |

|-------|-------------------------------------------|

|       | zeroed and the frequency selection is     |

|       | forced to 31.25 kHz. The user can modify  |

|       | the IRCF bits to select a higher internal |

|       | oscillator frequency.                     |

If the primary oscillator is configured to be anything other than XT, LP or HS, then Two-Speed Start-up mode is disabled because the primary oscillator will not require any time to become stable after POR, or an exit from Sleep.

If the IRCF bits of the OSCCON register are configured to a non-zero value prior to entering Sleep mode, the system clock frequency will come from the output of the INTOSC. The IOFS bit in the OSCCON register will be clear until the INTOSC is stable. This will allow the user to determine when the internal oscillator can be used for time critical applications. Checking the state of the OSTS bit will confirm whether the primary clock configuration is engaged. If not, the OSTS bit will remain clear.

When the device is auto-configured in INTRC mode following a POR or wake-up from Sleep, the rules for entering other oscillator modes still apply, meaning the SCS<1:0> bits in OSCCON can be modified before the OST time-out has occurred. This would allow the application to wake-up from Sleep, perform a few instructions using the INTRC as the clock source and go back to Sleep without waiting for the primary oscillator to become stable.

**Note:** Executing a SLEEP instruction will abort the oscillator start-up time and will cause the OSTS bit to remain clear.

- 15.12.3.1 Two-Speed Start-up Mode Sequence

- 1. Wake-up from Sleep, Reset or POR.

- OSCCON bits configured to run from INTRC (31.25 kHz).

- Instructions begin execution by INTRC (31.25 kHz).

- 4. OST enabled to count 1024 clock cycles.

- 5. OST timed out, wait for falling edge of INTRC.

- 6. OSTS is set.

- 7. System clock held low for eight falling edges of new clock (LP, XT or HS).

- 8. System clock is switched to primary source (LP, XT or HS).

The software may read the OSTS bit to determine when the switchover takes place so that any software timing edges can be adjusted.

# PIC16F87/88

| SUBLW            | Subtract W from Literal                                                                                                        | XORLW            | Exclusive OR Literal with W                                                                                                |

|------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] SUBLW k                                                                                                       | Syntax:          | [label] XORLW k                                                                                                            |

| Operands:        | $0 \leq k \leq 255$                                                                                                            | Operands:        | $0 \leq k \leq 255$                                                                                                        |

| Operation:       | $k - (W) \rightarrow (W)$                                                                                                      | Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                              |

| Status Affected: | C, DC, Z                                                                                                                       | Status Affected: | Z                                                                                                                          |

| Description:     | The W register is subtracted (two's complement method) from the eight-bit literal 'k'. The result is placed in the W register. | Description:     | The contents of the W register<br>are XOR'ed with the eight-bit<br>literal 'k'. The result is placed in<br>the W register. |

| SUBWF            | Subtract W from f                                                                                                                                                                       | XORWF            | Exclusive OR W with f                                                                                                                                                     |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [label] SUBWF f,d                                                                                                                                                                       | Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                                                |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                             | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                         |  |  |

| Operation:       | (f) – (W) $\rightarrow$ (destination)                                                                                                                                                   | Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                 |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                                | Status Affected: | Z                                                                                                                                                                         |  |  |

| Description:     | Subtract (two's complement<br>method) W register from register 'f'.<br>If 'd' = 0, the result is stored in the<br>W register. If 'd' = 1, the result is<br>stored back in register 'f'. | Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' = 0, the result is stored in the W register. If 'd' = 1, the result is stored back in register 'f'. |  |  |

| SWAPF            | Swap Nibbles in f                                                                                                                                            |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] SWAPF f,d                                                                                                                                   |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                  |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                      |

| Status Affected: | None                                                                                                                                                         |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' = 0, the result is placed in W register. If 'd' = 1, the result is placed in register 'f'. |

DS30487D-page 156

### 17.7 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 17.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs PIC<sup>®</sup> Flash MCUs and dsPIC<sup>®</sup> Flash DSCs with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with incircuit debugger systems (RJ11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 17.9 MPLAB ICD 3 In-Circuit Debugger System

MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost effective high-speed hardware debugger/programmer for Microchip Flash Digital Signal Controller (DSC) and microcontroller (MCU) devices. It debugs and programs PIC<sup>®</sup> Flash microcontrollers and dsPIC<sup>®</sup> DSCs with the powerful, yet easyto-use graphical user interface of MPLAB Integrated Development Environment (IDE).

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

### 17.10 PICkit 3 In-Circuit Debugger/ Programmer and PICkit 3 Debug Express

The MPLAB PICkit 3 allows debugging and programming of PIC<sup>®</sup> and dsPIC<sup>®</sup> Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB Integrated Development Environment (IDE). The MPLAB PICkit 3 is connected to the design engineer's PC using a full speed USB interface and can be connected to the target via an Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup>.

The PICkit 3 Debug Express include the PICkit 3, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

### 18.2 DC Characteristics: Power-Down and Supply Current PIC16F87/88 (Industrial, Extended) PIC16LF87/88 (Industrial) (Continued)

| PIC16LF<br>(Indu |                                       | i <b>rd Oper</b><br>ing temp |                              |       | ss otherwise states $A \leq +85^{\circ}C$ for indust |                                                                                         |                                |  |  |  |

|------------------|---------------------------------------|------------------------------|------------------------------|-------|------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------|--|--|--|

| PIC16F8<br>(Indu | 7/88<br>strial, Extended)             |                              | i <b>rd Oper</b><br>ing temp |       | -40°C ≤ T                                            | As otherwise states<br>$A \le +85^{\circ}C$ for indus<br>$A \le +125^{\circ}C$ for exte | trial                          |  |  |  |

| Param<br>No.     | Device                                | Тур                          | Max                          | Units | Conditions                                           |                                                                                         |                                |  |  |  |

|                  | Supply Current (IDD) <sup>(2,3)</sup> |                              |                              |       |                                                      |                                                                                         |                                |  |  |  |

|                  | PIC16LF87/88                          | 72                           | 95                           | μΑ    | -40°C                                                |                                                                                         |                                |  |  |  |

|                  |                                       | 76                           | 90                           | μΑ    | +25°C                                                | VDD = 2.0V                                                                              |                                |  |  |  |

|                  |                                       | 76                           | 90                           | μΑ    | +85°C                                                |                                                                                         |                                |  |  |  |

|                  | PIC16LF87/88                          | 138                          | 175                          | μΑ    | -40°C                                                |                                                                                         |                                |  |  |  |

|                  |                                       | 136                          | 170                          | μA    | +25°C                                                | VDD = 3.0V                                                                              | Fosc = 1 MHz                   |  |  |  |

|                  |                                       | 136                          | 170                          | μΑ    | +85°C                                                |                                                                                         | (RC Oscillator) <sup>(3)</sup> |  |  |  |

|                  | All devices                           | 310                          | 380                          | μA    | -40°C                                                |                                                                                         |                                |  |  |  |

|                  |                                       | 290                          | 360                          | μΑ    | +25°C                                                | VDD = 5.0V                                                                              |                                |  |  |  |

|                  |                                       | 280                          | 360                          | μA    | +85°C                                                | VDD = 3.0V                                                                              |                                |  |  |  |

|                  | Extended devices                      | 330                          | 500                          | μA    | 125°C                                                |                                                                                         |                                |  |  |  |

|                  | PIC16LF87/88                          | 270                          | 335                          | μΑ    | -40°C                                                | _                                                                                       |                                |  |  |  |

|                  |                                       | 280                          | 330                          | μA    | +25°C                                                | VDD = 2.0V                                                                              |                                |  |  |  |

|                  |                                       | 285                          | 330                          | μA    | +85°C                                                |                                                                                         |                                |  |  |  |

|                  | PIC16LF87/88                          | 460                          | 610                          | μA    | -40°C                                                |                                                                                         |                                |  |  |  |

|                  |                                       | 450                          | 600                          | μΑ    | +25°C                                                | VDD = 3.0V                                                                              | Fosc = 4 MHz                   |  |  |  |

|                  |                                       | 450                          | 600                          | μΑ    | +85°C                                                |                                                                                         | (RC Oscillator) <sup>(3)</sup> |  |  |  |

|                  | All devices                           | 900                          | 1060                         | μΑ    | -40°C                                                | 4                                                                                       |                                |  |  |  |

|                  |                                       | 890                          | 1050                         | μΑ    | +25°C                                                | VDD = 5.0V                                                                              |                                |  |  |  |

|                  |                                       | 890                          | 1050                         | μΑ    | +85°C                                                |                                                                                         |                                |  |  |  |

|                  | Extended devices                      | .920                         | 1.5                          | mA    | +125°C                                               |                                                                                         |                                |  |  |  |

Legend: Shading of rows is to assist in readability of the table.

**Note 1:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or VSs and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;

- MCLR = VDD; WDT enabled/disabled as specified.

- 3: For RC oscillator configurations, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

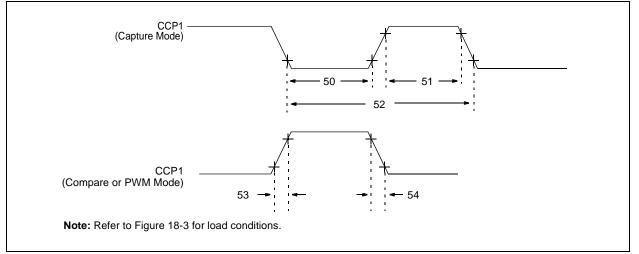

| Param<br>No. | Symbol | Characteristic        |                       |                        | Min          | Тур† | Max | Units                              | Conditions |

|--------------|--------|-----------------------|-----------------------|------------------------|--------------|------|-----|------------------------------------|------------|

| 50*          | TccL   | CCP1                  | CP1 No Prescaler      |                        | 0.5 Tcy + 20 | —    |     | ns                                 |            |

|              |        | Input Low Time        | With Prescaler        | PIC16 <b>F</b> 87/88   | 10           | —    | —   | ns                                 |            |

|              |        |                       |                       | PIC16 <b>LF</b> 87/88  | 20           | —    | _   | ns                                 |            |

| 51*          | TccH   | CCP1                  | CCP1 No Prescaler     |                        | 0.5 TCY + 20 |      | _   | ns                                 |            |

|              |        | Input High Time       | With Prescaler        | PIC16 <b>F</b> 87/88   | 10           |      | _   | ns                                 |            |

|              |        |                       |                       | PIC16 <b>LF</b> 87/88  | 20           |      | _   | ns                                 |            |

| 52*          | TccP   | CCP1 Input Period     |                       | <u>3 Tcy + 40</u><br>N | —            | _    |     | N = prescale<br>value (1, 4 or 16) |            |

| 53*          | TccR   | CCP1 Output Ris       | CCP1 Output Rise Time |                        | _            | 10   | 25  | ns                                 |            |

|              |        |                       |                       |                        | —            | 25   | 50  | ns                                 |            |

| 54*          | TccF   | CCP1 Output Fall Time |                       | PIC16 <b>F</b> 87/88   | —            | 10   | 25  | ns                                 |            |

|              |        |                       |                       | PIC16 <b>LF</b> 87/88  | —            | 25   | 45  | ns                                 |            |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

|              |         | Bee en arther   | of Brid Kego |      |     |     | -     |                                    |

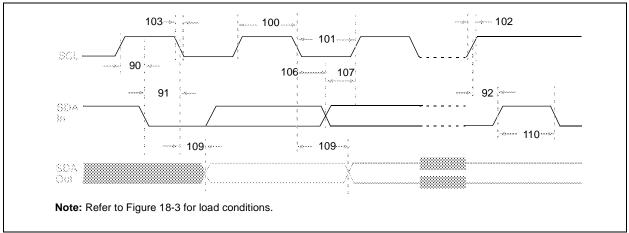

|--------------|---------|-----------------|--------------|------|-----|-----|-------|------------------------------------|

| Param<br>No. | Symbol  | Characteristic  |              | Min  | Тур | Max | Units | Conditions                         |

| 90*          | TSU:STA | Start Condition | 100 kHz mode | 4700 | _   | —   | ns    | Only relevant for Repeated         |

|              |         | Setup Time      | 400 kHz mode | 600  |     | —   |       | Start condition                    |

| 91*          | THD:STA | Start Condition | 100 kHz mode | 4000 |     | —   | ns    | After this period, the first clock |

|              |         | Hold Time       | 400 kHz mode | 600  |     | —   |       | pulse is generated                 |

| 92*          | Tsu:sto | Stop Condition  | 100 kHz mode | 4700 |     | —   | ns    |                                    |

|              |         | Setup Time      | 400 kHz mode | 600  | _   |     |       |                                    |

| 93           | THD:STO | Stop Condition  | 100 kHz mode | 4000 |     | —   | ns    |                                    |

|              |         | Hold Time       | 400 kHz mode | 600  |     | —   |       |                                    |

TABLE 18-9: I<sup>2</sup>C<sup>™</sup> BUS START/STOP BITS REQUIREMENTS

\* These parameters are characterized but not tested.

## FIGURE 18-15: I<sup>2</sup>C<sup>™</sup> BUS DATA TIMING

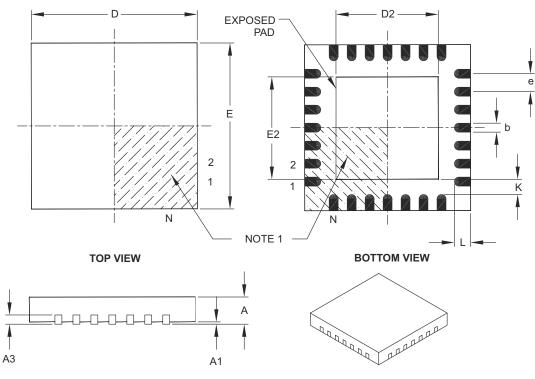

# 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units    | MILLIMETERS |          |      |  |

|------------------------|----------|-------------|----------|------|--|

| Dimensio               | n Limits | MIN         | NOM      | MAX  |  |

| Number of Pins         | Ν        | 28          |          |      |  |

| Pitch                  | е        |             | 0.65 BSC |      |  |

| Overall Height         | Α        | 0.80        | 0.90     | 1.00 |  |

| Standoff               | A1       | 0.00        | 0.02     | 0.05 |  |

| Contact Thickness      | A3       | 0.20 REF    |          |      |  |

| Overall Width          | Е        | 6.00 BSC    |          |      |  |

| Exposed Pad Width      | E2       | 3.65        | 3.70     | 4.20 |  |

| Overall Length         | D        |             | 6.00 BSC |      |  |

| Exposed Pad Length     | D2       | 3.65        | 3.70     | 4.20 |  |

| Contact Width          | b        | 0.23        | 0.30     | 0.35 |  |

| Contact Length         | L        | 0.50        | 0.55     | 0.70 |  |

| Contact-to-Exposed Pad | К        | 0.20        | -        | -    |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-105B

# PIC16F87/88

### Е

| EEADR Register18                                           | , 29 |

|------------------------------------------------------------|------|

| EEADRH Register18                                          | , 29 |

| EECON1 Register                                            | , 29 |

| EECON2 Register                                            | , 29 |

| EEDATA Register                                            | , 29 |

| EEDATH Register 18                                         | , 29 |

| Electrical Characteristics                                 | 163  |

| Errata                                                     | 6    |

| Exiting Sleep with an Interrupt                            | . 52 |

| External Clock Input                                       | . 38 |

| External Clock Input (RA4/T0CKI). See Timer0.              |      |

| External Interrupt Input (RB0/INT). See Interrupt Sources. |      |

#### F

| Flash Program Memory<br>Associated Registers<br>EEADR Register<br>EEADRH Register<br>EECON1 Register<br>EECON2 Register<br>EEDATA Register<br>EEDATH Register<br>Erasing<br>Reading<br>Writing | Fail-Safe Clock Monitor | . 131, 146 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------|

| EEADR Register<br>EEADRH Register<br>EECON1 Register<br>EECON2 Register<br>EEDATA Register<br>EEDATH Register<br>Erasing<br>Reading                                                            | Flash Program Memory    | 29         |

| EEADRH Register<br>EECON1 Register<br>EECON2 Register<br>EEDATA Register<br>EEDATH Register<br>Erasing<br>Reading                                                                              | Associated Registers    |            |

| EECON1 Register<br>EECON2 Register<br>EEDATA Register<br>EEDATH Register<br>Erasing<br>Reading                                                                                                 | EEADR Register          | 29         |

| EECON2 Register<br>EEDATA Register<br>EEDATH Register<br>Erasing<br>Reading                                                                                                                    | EEADRH Register         | 29         |

| EEDATA Register<br>EEDATH Register<br>Erasing<br>Reading                                                                                                                                       | EECON1 Register         | 29         |

| EEDATH Register<br>Erasing<br>Reading                                                                                                                                                          | EECON2 Register         | 29         |

| EEDATH Register<br>Erasing<br>Reading                                                                                                                                                          | EEDATA Register         | 29         |

| Erasing<br>Reading                                                                                                                                                                             | -                       |            |

| -                                                                                                                                                                                              | -                       |            |

| -                                                                                                                                                                                              | Reading                 | 32         |

|                                                                                                                                                                                                | -                       |            |

| FSR Register                                                                                                                                                                                   | -                       |            |

## G

| General Purpose Register File |  |

|-------------------------------|--|

|-------------------------------|--|

## I

| I/O Po           | orts                                     |            |

|------------------|------------------------------------------|------------|

| F                | PORTA                                    |            |

| F                | PORTB                                    |            |

| 7                | TRISB Register                           |            |

| I <sup>2</sup> C | J. J |            |

| 1                | Addressing                               |            |

|                  | Associated Registers                     |            |

| 1                | Master Mode                              |            |

| ſ                | Mode                                     | 94         |

| ſ                | Mode Selection                           |            |

| 1                | Multi-Master Mode                        |            |

| F                | Reception                                |            |

| 5                | SCL and SDA Pins                         |            |

| 5                | Slave Mode                               |            |

| ٦                | Transmission                             |            |

| ID Lo            | cations                                  | . 131, 149 |

| In-Cir           | cuit Debugger                            | 149        |