Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |  |  |  |  |

|----------------------------|---------------------------------------------------------------------------|--|--|--|--|

| Core Processor             | PIC                                                                       |  |  |  |  |

| Core Size                  | 8-Bit                                                                     |  |  |  |  |

| Speed                      | 10MHz                                                                     |  |  |  |  |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |  |  |  |  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |  |  |  |  |

| Number of I/O              | 16                                                                        |  |  |  |  |

| Program Memory Size        | 7KB (4K x 14)                                                             |  |  |  |  |

| Program Memory Type        | FLASH                                                                     |  |  |  |  |

| EEPROM Size                | 256 x 8                                                                   |  |  |  |  |

| RAM Size                   | 368 x 8                                                                   |  |  |  |  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |  |  |  |  |

| Data Converters            | A/D 7x10b                                                                 |  |  |  |  |

| Oscillator Type            | Internal                                                                  |  |  |  |  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |  |  |  |  |

| Mounting Type              | Surface Mount                                                             |  |  |  |  |

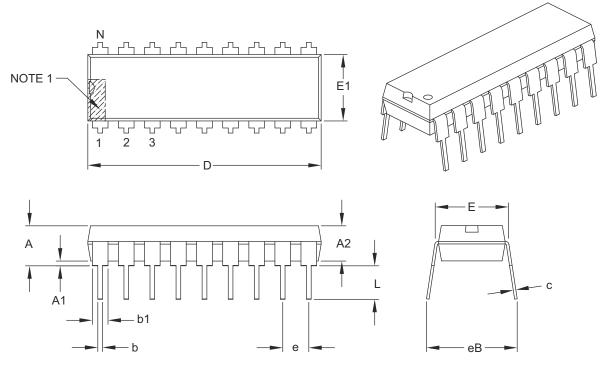

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                            |  |  |  |  |

| Supplier Device Package    | 18-SOIC                                                                   |  |  |  |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf88t-i-so |  |  |  |  |

|                            |                                                                           |  |  |  |  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 2-1. The Special Function Registers can be classified into two sets: core (CPU) and peripheral. Those registers associated with the core functions are described in detail in this section. Those related to the operation of the peripheral features are described in detail in the peripheral feature section.

| Address              | Name                  | Bit 7       | Bit 6                                                                                                                                                         | Bit 5         | Bit 4           | Bit 3                          | Bit 2           | Bit 1        | Bit 0    | Value on:<br>POR, BOR  | Details<br>on<br>page |

|----------------------|-----------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------|--------------------------------|-----------------|--------------|----------|------------------------|-----------------------|

| Bank 0               | •                     | •           |                                                                                                                                                               | •             | •               | •                              | •               | •            |          | •                      |                       |

| 00h <sup>(2)</sup>   | INDF                  | Addressing  | g this locatio                                                                                                                                                | n uses conte  | ents of FSR to  | address data                   | memory (not     | a physical r | egister) | 0000 0000              | 26, 135               |

| 01h                  | TMR0                  | Timer0 Mc   | dule Registe                                                                                                                                                  | ər            |                 |                                |                 |              |          | XXXX XXXX              | 69                    |

| 02h <sup>(2)</sup>   | PCL                   | Program C   | gram Counter (PC) Least Significant Byte                                                                                                                      |               |                 |                                |                 |              |          | 0000 0000              |                       |

| 03h <sup>(2)</sup>   | STATUS                | IRP         | RP1                                                                                                                                                           | RP0           | TO              | PD                             | Z               | DC           | С        | 0001 1xxx              | 17                    |

| 04h <sup>(2)</sup>   | FSR                   | Indirect Da | ata Memory                                                                                                                                                    | Address Poir  | nter            |                                |                 |              |          | xxxx xxxx              | 135                   |

| 05h                  | PORTA                 |             | DRTA Data Latch when written; PORTA pins when read (PIC16F87)     xxxx 0000       DRTA Data Latch when written; PORTA pins when read (PIC16F88)     xxx0 0000 |               |                 |                                |                 |              |          | 52                     |                       |

| 06h                  | PORTB                 |             |                                                                                                                                                               |               |                 | hen read (PIC<br>hen read (PIC |                 |              |          | xxxx xxxx<br>00xx xxxx | 58                    |

| 07h                  | —                     | Unimplem    | ented                                                                                                                                                         |               |                 |                                |                 |              |          | —                      | _                     |

| 08h                  | _                     | Unimplem    | ented                                                                                                                                                         |               |                 |                                |                 |              |          | _                      | _                     |

| 09h                  | _                     | Unimplem    | ented                                                                                                                                                         |               |                 |                                |                 |              |          | _                      | _                     |

| 0Ah <sup>(1,2)</sup> | PCLATH                | _           | _                                                                                                                                                             | _             | Write Buffer    | for the Upper                  | 5 bits of the F | Program Cou  | unter    | 0 0000                 | 135                   |

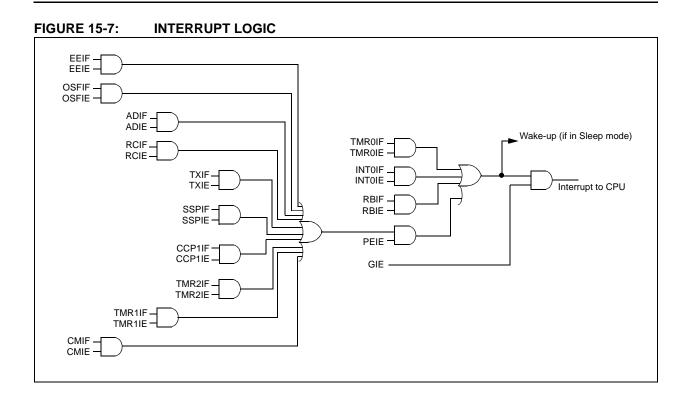

| 0Bh <sup>(2)</sup>   | INTCON                | GIE         | PEIE                                                                                                                                                          | TMR0IE        | INTOIE          | RBIE                           | TMR0IF          | INTOIF       | RBIF     | 0000 000x              | 19, 69,<br>77         |

| 0Ch                  | PIR1                  | _           | ADIF <sup>(4)</sup>                                                                                                                                           | RCIF          | TXIF            | SSPIF                          | CCP1IF          | TMR2IF       | TMR1IF   | -000 0000              | 21, 77                |

| 0Dh                  | PIR2                  | OSFIF       | CMIF                                                                                                                                                          | —             | EEIF            | —                              | _               | _            | _        | 00-0                   | 23, 34                |

| 0Eh                  | TMR1L                 | Holding Re  | egister for th                                                                                                                                                | e Least Sign  | ificant Byte of | the 16-bit TM                  | IR1 Register    | •            | •        | xxxx xxxx              | 77, 83                |

| 0Fh                  | TMR1H                 | Holding Re  | egister for th                                                                                                                                                | e Most Signi  | ficant Byte of  | the 16-bit TM                  | R1 Register     |              |          | xxxx xxxx              | 77, 83                |

| 10h                  | T1CON                 | _           | T1RUN                                                                                                                                                         | T1CKPS1       | T1CKPS0         | T1OSCEN                        | T1SYNC          | TMR1CS       | TMR10N   | -000 0000              | 72, 83                |

| 11h                  | TMR2                  | Timer2 Mc   | dule Registe                                                                                                                                                  | er            |                 |                                |                 | •            | •        | 0000 0000              | 80, 85                |

| 12h                  | T2CON                 | _           | TOUTPS3                                                                                                                                                       | TOUTPS2       | TOUTPS1         | TOUTPS0                        | TMR2ON          | T2CKPS1      | T2CKPS0  | -000 0000              | 80, 85                |

| 13h                  | SSPBUF                | Synchrono   | ous Serial Po                                                                                                                                                 | ort Receive B | uffer/Transmi   | t Register                     |                 |              |          | xxxx xxxx              | 90, 95                |

| 14h                  | SSPCON                | WCOL        | SSPOV                                                                                                                                                         | SSPEN         | CKP             | SSPM3                          | SSPM2           | SSPM1        | SSPM0    | 0000 0000              | 89, 95                |

| 15h                  | CCPR1L                | Capture/C   | ompare/PWI                                                                                                                                                    | M Register 1  | (LSB)           |                                |                 |              |          | xxxx xxxx              | 83, 85                |

| 16h                  | CCPR1H                | Capture/C   | ompare/PWI                                                                                                                                                    | M Register 1  | (MSB)           |                                |                 |              |          | XXXX XXXX              | 83, 85                |

| 17h                  | CCP1CON               | _           | _                                                                                                                                                             | CCP1X         | CCP1Y           | CCP1M3                         | CCP1M2          | CCP1M1       | CCP1M0   | 00 0000                | 81, 83                |

| 18h                  | RCSTA                 | SPEN        | RX9                                                                                                                                                           | SREN          | CREN            | ADDEN                          | FERR            | OERR         | RX9D     | 0000 000x              | 98, 99                |

| 19h                  | TXREG                 | AUSART 1    | Fransmit Dat                                                                                                                                                  | a Register    |                 |                                |                 |              |          | 0000 0000              | 103                   |

| 1Ah                  | RCREG                 | AUSART F    | AUSART Receive Data Register 000                                                                                                                              |               |                 |                                |                 | 0000 0000    | 105      |                        |                       |

| 1Bh                  | _                     | Unimplem    | ented                                                                                                                                                         |               |                 |                                |                 |              |          | _                      |                       |

| 1Ch                  | _                     | Unimplem    | ented                                                                                                                                                         |               |                 |                                |                 |              |          | _                      |                       |

| 1Dh                  | —                     | Unimplem    | ented                                                                                                                                                         |               |                 |                                |                 |              |          | —                      | _                     |

| 1Eh                  | ADRESH <sup>(4)</sup> | A/D Resul   | t Register Hi                                                                                                                                                 | gh Byte       |                 |                                |                 |              |          | xxxx xxxx              | 120                   |

| 1Fh                  | ADCON0 <sup>(4)</sup> | ADCS1       | ADCS0                                                                                                                                                         | CHS2          | CHS1            | CHS0                           | GO/DONE         | _            | ADON     | 0000 00-0              | 114, 120              |

TABLE 2-1:

SPECIAL FUNCTION REGISTER SUMMARY

**Legend:** x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for PC<12:8>, whose contents are transferred to the upper byte of the program counter.

2: These registers can be addressed from any bank.

3: RA5 is an input only; the state of the TRISA5 bit has no effect and will always read '1'.

4: PIC16F88 device only.

### 2.2.2.4 PIE1 Register

This register contains the individual enable bits for the peripheral interrupts.

| Note: | Bit PEIE (INTCON<6>) must be set to |  |  |  |  |  |

|-------|-------------------------------------|--|--|--|--|--|

|       | enable any peripheral interrupt.    |  |  |  |  |  |

### REGISTER 2-4: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1 (ADDRESS 8Ch)

| U-0   | R/W-0               | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  |  |

|-------|---------------------|-------|-------|-------|--------|--------|--------|--|

| _     | ADIE <sup>(1)</sup> | RCIE  | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE |  |

| bit 7 |                     |       |       |       |        |        | bit 0  |  |

- bit 7 Unimplemented: Read as '0'

- bit 6 ADIE: A/D Converter Interrupt Enable bit<sup>(1)</sup>

- 1 = Enabled

- 0 = Disabled

Note 1: This bit is only implemented on the PIC16F88. The bit will read '0' on the PIC16F87.

- bit 5 RCIE: AUSART Receive Interrupt Enable bit

- 1 = Enabled

- 0 = Disabled

- bit 4 TXIE: AUSART Transmit Interrupt Enable bit

- 1 = Enabled

- 0 = Disabled

- bit 3 SSPIE: Synchronous Serial Port (SSP) Interrupt Enable bit

- 1 = Enabled

- 0 = Disabled

- bit 2 CCP1IE: CCP1 Interrupt Enable bit

- 1 = Enabled

- 0 = Disabled

- bit 1 TMR2IE: TMR2 to PR2 Match Interrupt Enable bit

- 1 = Enabled

- 0 = Disabled

- bit 0 TMR1IE: TMR1 Overflow Interrupt Enable bit

- 1 = Enabled

- 0 = Disabled

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### 2.2.2.7 PIR2 Register

The PIR2 register contains the flag bit for the EEPROM write operation interrupt.

| Note: | Interrupt flag bits are set when an interrupt |  |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|--|

|       | condition occurs, regardless of the state of  |  |  |  |  |  |

|       | its corresponding enable bit, or the global   |  |  |  |  |  |

|       | enable bit, GIE (INTCON<7>). User             |  |  |  |  |  |

|       | software should ensure the appropriate        |  |  |  |  |  |

|       | interrupt flag bits are clear prior to        |  |  |  |  |  |

|       | enabling an interrupt.                        |  |  |  |  |  |

## REGISTER 2-7: PIR2: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 2 (ADDRESS 0Dh)

| R/W-0 | R/W-0 | U-0 | R/W-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|-----|-------|-----|-----|-----|-------|

| OSFIF | CMIF  | —   | EEIF  | —   | —   | —   | —     |

| bit 7 |       |     |       |     |     |     | bit 0 |

| bit 7   | <b>OSFIF:</b> Oscillator Fail Interrupt Flag bit<br>1 = System oscillator failed, clock input has changed to INTRC (must be cleared in software)<br>0 = System clock operating |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | CMIF: Comparator Interrupt Flag bit                                                                                                                                            |

|         | <ul><li>1 = Comparator input has changed (must be cleared in software)</li><li>0 = Comparator input has not changed</li></ul>                                                  |

| bit 5   | Unimplemented: Read as '0'                                                                                                                                                     |

| bit 4   | EEIF: EEPROM Write Operation Interrupt Flag bit                                                                                                                                |

|         | <ul><li>1 = The write operation completed (must be cleared in software)</li><li>0 = The write operation is not complete or has not been started</li></ul>                      |

| bit 3-0 | Unimplemented: Read as '0'                                                                                                                                                     |

|         |                                                                                                                                                                                |

|         | Legend:                                                                                                                                                                        |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### 2.2.2.8 PCON Register

| Note: | Interrupt flag bits get set when an interrupt<br>condition occurs, regardless of the state of<br>its corresponding enable bit, or the global<br>enable bit, GIE (INTCON<7>). User<br>software should ensure the appropriate |  |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|       | interrupt flag bits are clear prior to enabling an interrupt.                                                                                                                                                               |  |  |  |

The Power Control (PCON) register contains a flag bit to allow differentiation between a Power-on Reset (POR), a Brown-out Reset, an external MCLR Reset and WDT Reset.

Note: BOR is unknown on Power-on Reset. It must then be set by the user and checked on subsequent Resets to see if BOR is clear, indicating a brown-out has occurred. The BOR status bit is a 'don't care' and is not necessarily predictable if the brownout circuit is disabled (by clearing the BOREN bit in the Configuration Word register).

### REGISTER 2-8: PCON: POWER CONTROL REGISTER (ADDRESS 8Eh)

|         |                                |              |               |                |              | ,           |              |         |

|---------|--------------------------------|--------------|---------------|----------------|--------------|-------------|--------------|---------|

|         | U-0                            | U-0          | U-0           | U-0            | U-0          | U-0         | R/W-0        | R/W-x   |

|         | _                              | _            | _             | _              | _            | _           | POR          | BOR     |

|         | bit 7                          |              |               |                |              |             |              | bit 0   |

| bit 7-2 | Unimplem                       | nented: Rea  | d as '0'      |                |              |             |              |         |

|         | '                              |              |               |                |              |             |              |         |

| bit 1   | POR: Power-on Reset Status bit |              |               |                |              |             |              |         |

|         | 1 = No Por                     | wer-on Rese  | et occurred   |                |              |             |              |         |

|         | 0 = A Pow                      | er-on Reset  | occurred (m   | ust be set in  | software aft | er a Power- | on Reset o   | ccurs)  |

| L:1.0   |                                |              | ``            |                | contrat o an |             |              |         |

| bit 0   | BOK: Brov                      | wn-out Rese  | t Status bit  |                |              |             |              |         |

|         | 1 = No Bro                     | own-out Res  | et occurred   |                |              |             |              |         |

|         | 0 = A Brow                     | vn-out Reset | t occurred (m | nust be set in | software af  | ter a Brown | -out Reset   | occurs) |

|         |                                |              |               |                |              |             |              |         |

|         | Legend:                        |              |               |                |              |             |              |         |

|         | -                              |              |               |                |              |             |              |         |

|         | R = Reada                      | able bit     | W = W         | /ritable bit   | U = Unim     | plemented   | bit, read as | ʻ0'     |

|         | -n = Value                     | at POR       | '1' = B       | it is set      | '0' = Bit is | s cleared   | x = Bit is ι | unknown |

## 3.0 DATA EEPROM AND FLASH PROGRAM MEMORY

The data EEPROM and Flash program memory are readable and writable during normal operation (over the full VDD range). This memory is not directly mapped in the register file space. Instead, it is indirectly addressed through the Special Function Registers. There are six SFRs used to read and write this memory:

- EECON1

- EECON2

- EEDATA

- EEDATH

- EEADR

- EEADRH

This section focuses on reading and writing data EEPROM and Flash program memory during normal operation. Refer to the appropriate device programming specification document for serial programming information.

When interfacing the data memory block, EEDATA holds the 8-bit data for read/write and EEADR holds the address of the EEPROM location being accessed. The PIC16F87/88 devices have 256 bytes of data EEPROM with an address range from 00h to 0FFh. When writing to unimplemented locations, the charge pump will be turned off.

When interfacing the program memory block, the EED-ATA and EEDATH registers form a two-byte word that holds the 14-bit data for read/write and the EEADR and EEADRH registers form a two-byte word that holds the 13-bit address of the EEPROM location being accessed. The PIC16F87/88 devices have 4K words of program Flash with an address range from 0000h to 0FFFh. Addresses above the range of the respective device will wraparound to the beginning of program memory.

The EEPROM data memory allows single byte read and write. The Flash program memory allows singleword reads and four-word block writes. Program memory writes must first start with a 32-word block erase, then write in 4-word blocks. A byte write in data EEPROM memory automatically erases the location and writes the new data (erase before write).

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump, rated to operate over the voltage range of the device for byte or word operations.

When the device is code-protected, the CPU may continue to read and write the data EEPROM memory. Depending on the settings of the write-protect bits, the device may or may not be able to write certain blocks of the program memory; however, reads of the program memory are allowed. When code-protected, the device programmer can no longer access data or program memory; this does NOT inhibit internal reads or writes.

## 3.1 EEADR and EEADRH

The EEADRH:EEADR register pair can address up to a maximum of 256 bytes of data EEPROM, or up to a maximum of 8K words of program EEPROM. When selecting a data address value, only the LSB of the address is written to the EEADR register. When selecting a program address value, the MSB of the address is written to the EEADRH register and the LSB is written to the EEADR register.

If the device contains less memory than the full address reach of the address register pair, the Most Significant bits of the registers are not implemented. For example, if the device has 128 bytes of data EEPROM, the Most Significant bit of EEADR is not implemented on access to data EEPROM.

### 3.2 EECON1 and EECON2 Registers

EECON1 is the control register for memory accesses.

Control bit EEPGD determines if the access will be a program or data memory access. When clear, as it is when reset, any subsequent operations will operate on the data memory. When set, any subsequent operations will operate on the program memory.

Control bits, RD and WR, initiate read and write, respectively. These bits cannot be cleared, only set in software. They are cleared in hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write or erase operation. On power-up, the WREN bit is clear. The WRERR bit is set when a write (or erase) operation is interrupted by a MCLR, or a WDT Time-out Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and rewrite the location. The data and address will be unchanged in the EEDATA and EEADR registers.

Interrupt flag bit, EEIF in the PIR2 register, is set when the write is complete. It must be cleared in software.

EECON2 is not a physical register. Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the EEPROM write sequence.

### 3.3 Reading Data EEPROM Memory

To read a data memory location, the user must write the address to the EEADR register, clear the EEPGD control bit (EECON1<7>) and then set control bit RD (EECON1<0>). The data is available in the very next cycle in the EEDATA register; therefore, it can be read in the next instruction (see Example 3-1). EEDATA will hold this value until another read or until it is written to by the user (during a write operation).

The steps to reading the EEPROM data memory are:

- 1. Write the address to EEADR. Make sure that the address is not larger than the memory size of the device.

- 2. Clear the EEPGD bit to point to EEPROM data memory.

- 3. Set the RD bit to start the read operation.

- 4. Read the data from the EEDATA register.

|         |         | 0/(1)  |                       |

|---------|---------|--------|-----------------------|

| BANKSEL | EEADR   | ;      | Select Bank of EEADR  |

| MOVF    | ADDR, W | ;      |                       |

| MOVWF   | EEADR   | ;      | Data Memory Address   |

|         |         | ;      | to read               |

| BANKSEL | EECON1  | ;      | Select Bank of EECON1 |

| BCF     | EECON1, | EEPGD; | Point to Data memory  |

| BSF     | EECON1, | RD ;   | EE Read               |

| BANKSEL | EEDATA  | ;      | Select Bank of EEDATA |

| MOVF    | EEDATA, | W;     | W = EEDATA            |

|         |         |        |                       |

### EXAMPLE 3-1: DATA EEPROM READ

### 3.4 Writing to Data EEPROM Memory

To write an EEPROM data location, the user must first write the address to the EEADR register and the data to the EEDATA register. Then, the user must follow a specific write sequence to initiate the write for each byte.

The write will not initiate if the write sequence is not exactly followed (write 55h to EECON2, write AAh to EECON2, then set WR bit) for each byte. We strongly recommend that interrupts be disabled during this code segment (see Example 3-2).

Additionally, the WREN bit in EECON1 must be set to enable write. This mechanism prevents accidental writes to data EEPROM due to errant (unexpected) code execution (i.e., lost programs). The user should keep the WREN bit clear at all times except when updating EEPROM. The WREN bit is not cleared by hardware

After a write sequence has been initiated, clearing the WREN bit will not affect this write cycle. The WR bit will be inhibited from being set unless the WREN bit is set. At the completion of the write cycle, the WR bit is cleared in hardware and the EE Write Complete Interrupt Flag bit (EEIF) is set. The user can either enable this interrupt or poll this bit. EEIF must be cleared by software.

The steps to write to EEPROM data memory are:

- 1. If step 10 is not implemented, check the WR bit to see if a write is in progress.

- 2. Write the address to EEADR. Make sure that the address is not larger than the memory size of the device.

- 3. Write the 8-bit data value to be programmed in the EEDATA register.

- 4. Clear the EEPGD bit to point to EEPROM data memory.

- 5. Set the WREN bit to enable program operations.

- 6. Disable interrupts (if enabled).

- 7. Execute the special five instruction sequence:

Write 55h to EECON2 in two steps (first to W, then to EECON2).

Write AAh to EECON2 in two steps (first to W, then to EECON2).

Set the WR bit.

- 8. Enable interrupts (if using interrupts).

- 9. Clear the WREN bit to disable program operations.

- 10. At the completion of the write cycle, the WR bit is cleared and the EEIF interrupt flag bit is set (EEIF must be cleared by firmware). If step 1 is not implemented, then firmware should check for EEIF to be set, or WR to clear, to indicate the end of the program cycle.

#### EXAMPLE 3-2: DATA EEPROM WRITE

| -  |                      |                         |          |       |   |                   |

|----|----------------------|-------------------------|----------|-------|---|-------------------|

|    |                      | BANKSEL                 | EECON1   |       | ' | Select Bank of    |

|    |                      | DEEGO                   | DDCOM1   | MD    | ' | EECON1            |

|    |                      |                         |          |       |   | Wait for write    |

|    |                      | GOTO                    | •        |       |   | to complete       |

|    |                      | BANKSEL                 | EEADR    |       | ' | Select Bank of    |

|    |                      | MOLTE                   | 1000 11  |       | ' | EEADR             |

|    |                      |                         | ADDR, W  |       | ; |                   |

|    |                      | MOVWF                   | EEADR    |       |   | Data Memory       |

|    |                      |                         |          | _     | ; | Address to write  |

|    |                      |                         | VALUE, N |       | ; |                   |

|    |                      | MOVWF                   | EEDATA   |       |   | Data Memory Value |

|    |                      |                         |          |       | ' | to write          |

|    |                      | BANKSEL                 | EECON1   |       | ' | Select Bank of    |

|    |                      |                         |          |       | ' | EECON1            |

|    |                      | BCF                     | EECON1,  | EEPGD | ; | Point to DATA     |

|    |                      |                         |          |       |   | memory            |

|    |                      | BSF                     | EECON1,  | WREN  | ; | Enable writes     |

|    |                      |                         |          |       |   |                   |

| ١. | _                    | BCF                     | INTCON,  | GIE   | ; | Disable INTs.     |

| Ш  |                      | MOVLW                   |          |       | ; |                   |

| Ш  | g g                  | MOVWF                   | EECON2   |       | ; | Write 55h         |

| Ш  | Required<br>Sequence | MOVWF<br>MOVLW<br>MOVWF | AAh      |       | ; |                   |

| Ш  | sed %                | MOVWF                   | EECON2   |       | ; | Write AAh         |

| Ш  | E 0)                 |                         |          | WR    | ; | Set WR bit to     |

| l  |                      |                         |          |       | ; | begin write       |

|    |                      | BSF                     | INTCON,  | GIE   | ; | Enable INTs.      |

|    |                      | BCF                     | EECON1,  | WREN  | ; | Disable writes    |

| 1  |                      |                         |          |       |   |                   |

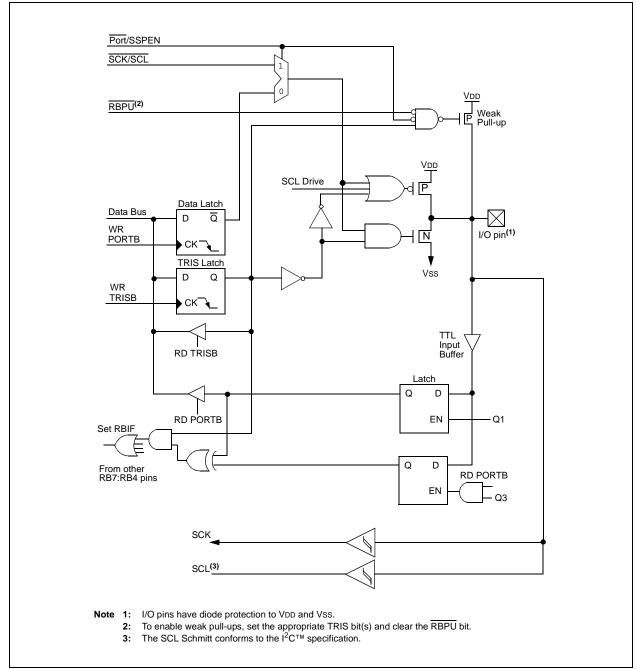

# FIGURE 5-13: BLOCK DIAGRAM OF RB5/SS/TX/CK PIN

| REGISTER 10-2: | SSPCON:                       | SYNCHR                | ONOUS SER                                      | IAL PORT                 | CONTROL         | REGISTE      | R (ADDRE      | SS 14h)      |

|----------------|-------------------------------|-----------------------|------------------------------------------------|--------------------------|-----------------|--------------|---------------|--------------|

|                | R/W-0                         | R/W-0                 | R/W-0                                          | R/W-0                    | R/W-0           | R/W-0        | R/W-0         | R/W-0        |

|                | WCOL                          | SSPOV                 | SSPEN <sup>(1)</sup>                           | CKP                      | SSPM3           | SSPM2        | SSPM1         | SSPM0        |

|                | bit 7                         |                       |                                                |                          |                 |              |               | bit 0        |

| bit 7          | WCOL: W                       | rite Collisior        | Detect bit                                     |                          |                 |              |               |              |

|                |                               |                       | e the SSPBUF                                   | -<br>register fai        | led because     | the SSP m    | odule is bu   | sy           |

|                | (must                         | be cleared            | in software)                                   | C C                      |                 |              |               |              |

|                | 0 = No col                    |                       | <b>a b b c</b>                                 |                          |                 |              |               |              |

| bit 6          | In SPI mod                    |                       | rflow Indicator                                | Dit                      |                 |              |               |              |

|                |                               |                       | eived while the                                | SSPBUF re                | aister is still | holdina the  | previous da   | ata. In case |

|                | of ove                        | rflow, the d          | ata in SSPSR                                   | is lost. Ove             | rflow can or    | ly occur in  | Slave mode    | e. The user  |

|                |                               |                       | PBUF, even if                                  |                          |                 |              |               |              |

|                |                               |                       | w bit is not se<br>SPBUF regist                |                          | i new recep     | uon (and tra | ansmission)   | is initiated |

|                | 0 = No over                   | erflow                | 0                                              |                          |                 |              |               |              |

|                | In I <sup>2</sup> C mod       |                       |                                                |                          |                 | r            |               | 00001/-      |

|                | •                             |                       | while the SSI                                  | •                        |                 | • .          | •             |              |

|                | 0 = No over                   |                       |                                                |                          |                 |              |               |              |

| bit 5          | SSPEN: S                      | ynchronous            | Serial Port Er                                 | nable bit <sup>(1)</sup> |                 |              |               |              |

|                | In SPI mod                    |                       |                                                |                          |                 |              |               |              |

|                |                               |                       | t and configure<br>rt and configur             |                          |                 |              | t pins        |              |

|                | In I <sup>2</sup> C mod       | -                     | it and coningui                                | es triese pir            | 13 a3 1/0 p01   | t pins       |               |              |

|                | 1 = Enable                    | es the serial         | port and confi                                 |                          |                 |              | rial port pin | 5            |

|                |                               | -                     | rt and configur                                |                          |                 | -            |               |              |

|                | Note 1:                       | In both mo<br>output. | odes, when en                                  | abled, these             | e pins must l   | be properly  | configured    | as input or  |

| bit 4          |                               | k Polarity S          | elect bit                                      |                          |                 |              |               |              |

|                | In SPI mod                    |                       | on falling edge                                | , receive or             | ricing odgo     | Idlo ototo f | or clock is c | high loval   |

|                |                               |                       | on rising edge                                 |                          |                 |              |               |              |

|                | <u>In I<sup>2</sup>C Slav</u> | <u>e mode:</u>        |                                                |                          |                 |              |               |              |

|                | SCK release                   |                       |                                                |                          |                 |              |               |              |

|                | 1 = Enable<br>0 = Holds (     |                       | lock stretch). (                               | Used to ens              | sure data set   | up time.)    |               |              |

| bit 3-0        | SSPM<3:0                      | >: Synchro            | nous Serial Po                                 | ort Mode Se              | lect bits       | . ,          |               |              |

|                |                               |                       | ode, clock = O                                 |                          |                 |              |               |              |

|                |                               |                       | ode, clock = O<br>ode, clock = O               |                          |                 |              |               |              |

|                |                               |                       | ode, clock = O<br>ode, clock = Tl              |                          | 2               |              |               |              |

|                | 0100 = SP                     | I Slave mo            | de, clock = SC                                 | K pin. SS pi             | in control en   |              |               |              |

|                |                               |                       | de, clock = SC<br>le, 7-bit addre              |                          | n control dis   | abled. SS c  | an be used    | as I/O pin.  |

|                |                               |                       | de, 7-bit addres                               |                          |                 |              |               |              |

|                | $1011 = I^2C$                 | Firmware              | Controlled Ma                                  | ster mode (              |                 |              |               |              |

|                |                               |                       | le, 7-bit addres                               |                          |                 |              |               |              |

|                |                               |                       | <b>le, 10-bit addr</b><br>L00, 1101 <b>=</b> R |                          | n anu stop i    |              |               |              |

|                |                               | ,, .                  | .,                                             |                          |                 |              |               |              |

|                | Legend:                       |                       |                                                |                          |                 |              |               |              |

|                | R = Reada                     | ble bit               | W = W                                          | ritable bit              | U = Unim        | plemented    | bit, read as  | '0'          |

| Legena.           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

NOTES:

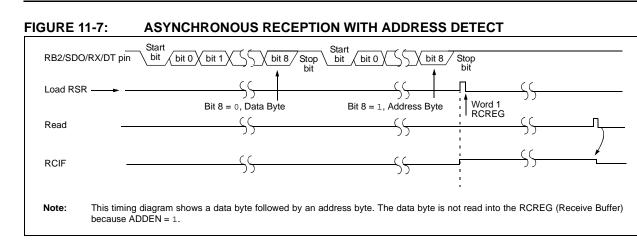

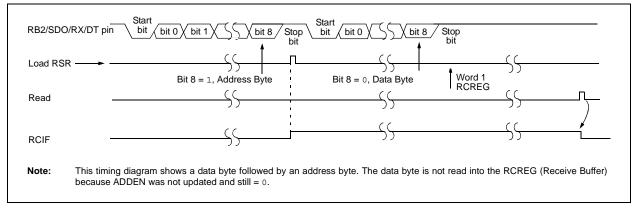

### FIGURE 11-8: ASYNCHRONOUS RECEPTION WITH ADDRESS BYTE FIRST

#### TABLE 11-9: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Address                | Name   | Bit 7                           | Bit 6               | Bit 5     | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0     | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|------------------------|--------|---------------------------------|---------------------|-----------|--------|-------|--------|--------|-----------|-----------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                             | PEIE                | TMR0IE    | INT0IE | RBIE  | TMR0IF | INTOIF | RBIF      | 0000 000x             | 0000 000u                       |

| 0Ch                    | PIR1   | —                               | ADIF <sup>(1)</sup> | RCIF      | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF    | -000 0000             | -000 0000                       |

| 18h                    | RCSTA  | SPEN                            | RX9                 | SREN      | CREN   | ADDEN | FERR   | OERR   | RX9D      | x000 000x             | 0000 000x                       |

| 1Ah                    | RCREG  | AUSART                          | Receive             | Data Regi | ster   |       |        |        |           | 0000 0000             | 0000 0000                       |

| 8Ch                    | PIE1   | —                               | ADIE <sup>(1)</sup> | RCIE      | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE    | -000 0000             | -000 0000                       |

| 98h                    | TXSTA  | CSRC                            | TX9                 | TXEN      | SYNC   | —     | BRGH   | TRMT   | TX9D      | 0000 -010             | 0000 -010                       |

| 99h                    | SPBRG  | RG Baud Rate Generator Register |                     |           |        |       |        |        | 0000 0000 | 0000 0000             |                                 |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception.

**Note 1:** This bit is only implemented on the PIC16F88. The bit will read '0' on the PIC16F87.

### 15.18 Low-Voltage ICSP Programming

The LVP bit of the Configuration Word enables Low-Voltage ICSP Programming. This mode allows the microcontroller to be programmed via ICSP using a VDD source in the operating voltage range. This only means that VPP does not have to be brought to VIHH, but can instead be left at the normal operating voltage. In this mode, the RB3/PGM pin is dedicated to the programming function and ceases to be a general purpose I/O pin.

If Low-Voltage Programming mode is not used, the LVP bit can be programmed to a '0' and RB3/PGM becomes a digital I/O pin. However, the LVP bit may only be programmed when Programming mode is entered with VIHH on MCLR. The LVP bit can only be changed when using high voltage on MCLR.

It should be noted that once the LVP bit is programmed to '0', only the High-Voltage Programming mode is available and only this mode can be used to program the device.

When using Low-Voltage ICSP, the part must be supplied at 4.5V to 5.5V if a bulk erase will be executed. This includes reprogramming of the code-protect bits from an ON state to an OFF state. For all other cases of Low-Voltage ICSP, the part may be programmed at the normal operating voltage. This means calibration values, unique user IDs or user code can be reprogrammed or added.

The following LVP steps assume the LVP bit is set in the Configuration register.

- 1. Apply VDD to the VDD pin.

- 2. Drive MCLR low.

- 3. Apply VDD to the RB3/PGM pin.

- 4. Apply VDD to the  $\overline{\text{MCLR}}$  pin.

- 5. Follow with the associated programming steps.

- Note 1: The High-Voltage Programming mode is always available, regardless of the state of the LVP bit, by applying VIHH to the MCLR pin.

- 2: While in Low-Voltage ICSP mode (LVP = 1), the RB3 pin can no longer be used as a general purpose I/O pin.

- 3: When using Low-Voltage ICSP Programming (LVP) and the pull-ups on PORTB are enabled, bit 3 in the TRISB register must be cleared to disable the pull-up on RB3 and ensure the proper operation of the device.

- 4: RB3 should not be allowed to float if LVP is enabled. An external pull-down device should be used to default the device to normal operating mode. If RB3 floats high, the PIC16F87/88 devices will enter Programming mode.

- LVP mode is enabled by default on all devices shipped from Microchip. It can be disabled by clearing the LVP bit in the CONFIG1 register.

- 6: Disabling LVP will provide maximum compatibility to other PIC16CXXX devices.

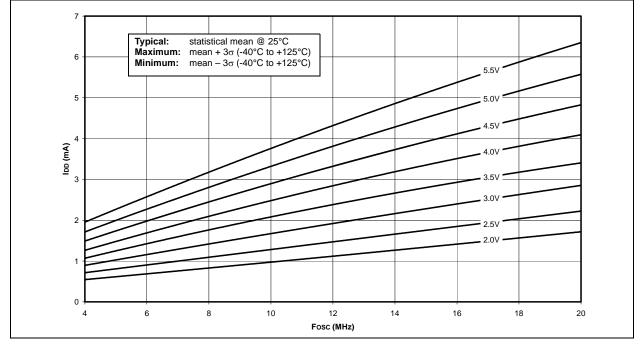

## 18.2 DC Characteristics: Power-Down and Supply Current PIC16F87/88 (Industrial, Extended) PIC16LF87/88 (Industrial) (Continued)

| PIC16LF87/88<br>(Industrial)<br>PIC16F87/88<br>(Industrial, Extended) |                                       | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |      |       |        |            |                                |  |

|-----------------------------------------------------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------|------------|--------------------------------|--|

|                                                                       |                                       | $ \begin{array}{llllllllllllllllllllllllllllllllllll$                                                                              |      |       |        |            |                                |  |

| Param<br>No.                                                          | Device                                | Тур                                                                                                                                | Max  | Units |        | Condi      | tions                          |  |

|                                                                       | Supply Current (IDD) <sup>(2,3)</sup> |                                                                                                                                    |      |       |        |            |                                |  |

|                                                                       | PIC16LF87/88                          | 72                                                                                                                                 | 95   | μΑ    | -40°C  |            |                                |  |

|                                                                       |                                       | 76                                                                                                                                 | 90   | μΑ    | +25°C  | VDD = 2.0V |                                |  |

|                                                                       |                                       | 76                                                                                                                                 | 90   | μΑ    | +85°C  |            |                                |  |

|                                                                       | PIC16LF87/88                          | 138                                                                                                                                | 175  | μΑ    | -40°C  |            |                                |  |

|                                                                       |                                       | 136                                                                                                                                | 170  | μA    | +25°C  | VDD = 3.0V | Fosc = 1 MHz                   |  |

|                                                                       |                                       | 136                                                                                                                                | 170  | μΑ    | +85°C  |            | (RC Oscillator) <sup>(3)</sup> |  |

|                                                                       | All devices                           | 310                                                                                                                                | 380  | μA    | -40°C  | Vdd = 5.0V |                                |  |

|                                                                       |                                       | 290                                                                                                                                | 360  | μΑ    | +25°C  |            |                                |  |

|                                                                       |                                       | 280                                                                                                                                | 360  | μA    | +85°C  | VDD = 3.0V |                                |  |

|                                                                       | Extended devices                      | 330                                                                                                                                | 500  | μA    | 125°C  |            |                                |  |

|                                                                       | PIC16LF87/88                          | 270                                                                                                                                | 335  | μΑ    | -40°C  | _          |                                |  |

|                                                                       |                                       | 280                                                                                                                                | 330  | μA    | +25°C  | VDD = 2.0V |                                |  |

|                                                                       |                                       | 285                                                                                                                                | 330  | μA    | +85°C  |            |                                |  |

|                                                                       | PIC16LF87/88                          | 460                                                                                                                                | 610  | μA    | -40°C  |            |                                |  |

|                                                                       |                                       | 450                                                                                                                                | 600  | μΑ    | +25°C  | VDD = 3.0V | Fosc = 4 MHz                   |  |

|                                                                       |                                       | 450                                                                                                                                | 600  | μΑ    | +85°C  |            | (RC Oscillator) <sup>(3)</sup> |  |

|                                                                       | All devices                           | 900                                                                                                                                | 1060 | μΑ    | -40°C  | 4          |                                |  |

|                                                                       |                                       | 890                                                                                                                                | 1050 | μΑ    | +25°C  | VDD = 5.0V |                                |  |

|                                                                       |                                       | 890<br>.920                                                                                                                        | 1050 | μΑ    | +85°C  |            |                                |  |

|                                                                       | Extended devices                      |                                                                                                                                    | 1.5  | mA    | +125°C |            |                                |  |

Legend: Shading of rows is to assist in readability of the table.

**Note 1:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or VSs and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

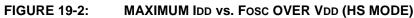

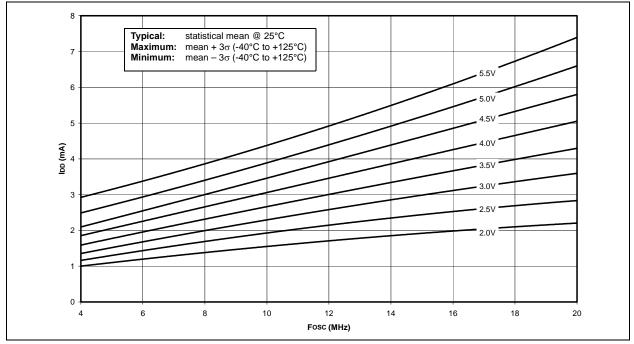

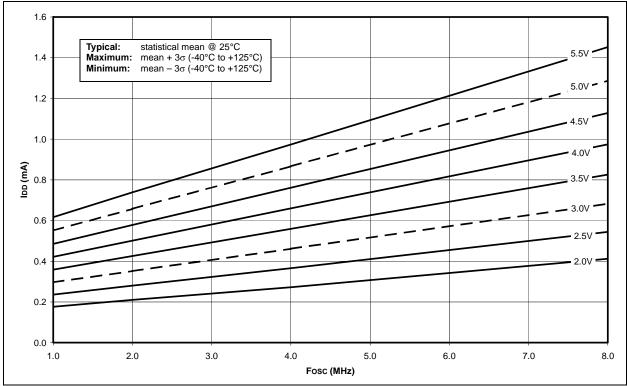

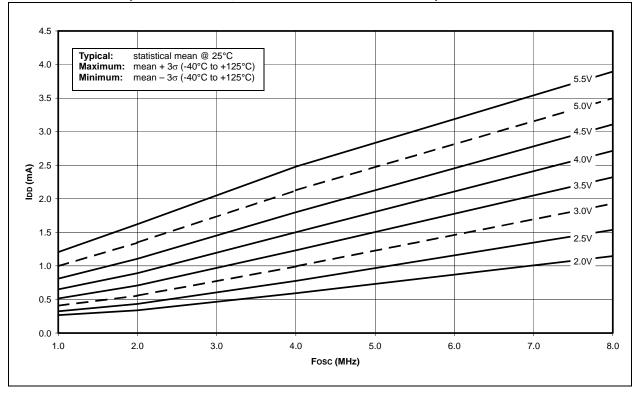

2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;

- MCLR = VDD; WDT enabled/disabled as specified.

- 3: For RC oscillator configurations, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

## 18.2 DC Characteristics: Power-Down and Supply Current PIC16F87/88 (Industrial, Extended) PIC16LF87/88 (Industrial) (Continued)

| PIC16LF87/88<br>(Industrial)<br>PIC16F87/88<br>(Industrial, Extended) |                                       | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial                                                      |     |       |        |            |                                           |  |

|-----------------------------------------------------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|--------|------------|-------------------------------------------|--|

|                                                                       |                                       | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |     |       |        |            |                                           |  |

| Param<br>No.                                                          | Device                                | Тур                                                                                                                                                                                     | Max | Units |        | Condi      | tions                                     |  |

|                                                                       | Supply Current (IDD) <sup>(2,3)</sup> |                                                                                                                                                                                         |     |       |        |            |                                           |  |

|                                                                       | PIC16LF87/88                          | 8                                                                                                                                                                                       | 20  | μA    | -40°C  |            |                                           |  |

|                                                                       |                                       | 7                                                                                                                                                                                       | 15  | μA    | +25°C  | VDD = 2.0V |                                           |  |

|                                                                       |                                       | 7                                                                                                                                                                                       | 15  | μΑ    | +85°C  |            |                                           |  |

|                                                                       | PIC16LF87/88                          | 16                                                                                                                                                                                      | 30  | μΑ    | -40°C  |            |                                           |  |

|                                                                       |                                       | 14                                                                                                                                                                                      | 25  | μΑ    | +25°C  | VDD = 3.0V | Fosc = 31.25 kHz<br>( <b>RC RUN</b> mode, |  |

|                                                                       |                                       | 14                                                                                                                                                                                      | 25  | μA    | +85°C  |            | Internal RC Oscillator)                   |  |

|                                                                       | All devices                           | 32                                                                                                                                                                                      | 40  | μΑ    | -40°C  | Vdd = 5.0V | ,                                         |  |

|                                                                       |                                       | 29                                                                                                                                                                                      | 35  | μΑ    | +25°C  |            |                                           |  |

|                                                                       |                                       | 29                                                                                                                                                                                      | 35  | μA    | +85°C  | VDD = 0.0V |                                           |  |

|                                                                       | Extended devices                      | 35                                                                                                                                                                                      | 45  | μΑ    | +125°C |            |                                           |  |

|                                                                       | PIC16LF87/88                          | 132                                                                                                                                                                                     | 160 | μΑ    | -40°C  | _          |                                           |  |

|                                                                       |                                       | 126                                                                                                                                                                                     | 155 | μΑ    | +25°C  | VDD = 2.0V |                                           |  |

|                                                                       |                                       | 126                                                                                                                                                                                     | 155 | μA    | +85°C  |            |                                           |  |

|                                                                       | PIC16LF87/88                          | 260                                                                                                                                                                                     | 310 | μA    | -40°C  |            |                                           |  |

|                                                                       |                                       | 230                                                                                                                                                                                     | 300 | μΑ    | +25°C  | VDD = 3.0V | Fosc = 1 MHz<br>( <b>RC RUN</b> mode,     |  |

|                                                                       |                                       | 230                                                                                                                                                                                     | 300 | μΑ    | +85°C  |            | Internal RC Oscillator)                   |  |

|                                                                       | All devices                           | 560                                                                                                                                                                                     | 690 | μΑ    | -40°C  |            |                                           |  |

|                                                                       |                                       | 500                                                                                                                                                                                     | 650 | μΑ    | +25°C  | VDD = 5.0V |                                           |  |

|                                                                       |                                       | 500                                                                                                                                                                                     | 650 | μΑ    | +85°C  |            |                                           |  |

|                                                                       | Extended devices                      | 570                                                                                                                                                                                     | 710 | μA    | +125°C |            |                                           |  |

Legend: Shading of rows is to assist in readability of the table.

**Note 1:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or VSs and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;

- MCLR = VDD; WDT enabled/disabled as specified.

- 3: For RC oscillator configurations, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

| Param.<br>No. | Symbol                    | Characte                      | Characteristic |             |      | Units | Conditions                             |

|---------------|---------------------------|-------------------------------|----------------|-------------|------|-------|----------------------------------------|

| 100*          | Тнідн                     | Clock High Time               | 100 kHz mode   | 4.0         |      | μS    |                                        |

|               |                           |                               | 400 kHz mode   | 0.6         |      | μS    |                                        |

|               |                           |                               | SSP Module     | 1.5 TCY     |      |       |                                        |

| 101*          | TLOW                      | Clock Low Time                | 100 kHz mode   | 4.7         | _    | μs    |                                        |

|               |                           |                               | 400 kHz mode   | 1.3         | _    | μS    |                                        |

|               |                           |                               | SSP Module     | 1.5 TCY     |      |       |                                        |

| 102*          | TR                        | SDA and SCL Rise              | 100 kHz mode   | —           | 1000 | ns    |                                        |

| Ti            |                           | Time                          | 400 kHz mode   | 20 + 0.1 Св | 300  | ns    | CB is specified to be from 10-400 pF   |

| 103*          | TF                        | SDA and SCL Fall              | 100 kHz mode   | —           | 300  | ns    |                                        |

|               | Time                      |                               | 400 kHz mode   | 20 + 0.1 Св | 300  | ns    | CB is specified to be from 10-400 pF   |

| 90*           | TSU:STA                   | Start Condition<br>Setup Time | 100 kHz mode   | 4.7         | -    | μS    | Only relevant for                      |

|               |                           |                               | 400 kHz mode   | 0.6         |      | μS    | Repeated Start<br>condition            |

| 91*           | THD:STA                   | Start Condition Hold<br>Time  | 100 kHz mode   | 4.0         |      | μS    | After this period, the first           |

|               |                           |                               | 400 kHz mode   | 0.6         | _    | μS    | clock pulse is generated               |

| 106*          | THD:DAT                   | Data Input Hold               | 100 kHz mode   | 0           | _    | ns    |                                        |

|               |                           | Time                          | 400 kHz mode   | 0           | 0.9  | μS    |                                        |

| 107*          | TSU:DAT                   | Data Input Setup              | 100 kHz mode   | 250         |      | ns    | (Note 2)                               |

|               |                           | Time                          | 400 kHz mode   | 100         | _    | ns    |                                        |

| 92*           | TSU:STO                   | Stop Condition                | 100 kHz mode   | 4.7         | _    | μs    |                                        |

|               |                           | Setup Time                    | 400 kHz mode   | 0.6         | _    | μS    |                                        |

| 109*          | ΤΑΑ                       | Output Valid from             | 100 kHz mode   | —           | 3500 | ns    | (Note 1)                               |

|               |                           | Clock                         | 400 kHz mode   | —           |      | ns    |                                        |

| 110*          | TBUF                      | Bus Free Time                 | 100 kHz mode   | 4.7         |      | μS    | Time the bus must be free              |

|               |                           |                               | 400 kHz mode   | 1.3         | _    | μS    | before a new transmission<br>can start |

|               | CB Bus Capacitive Loading |                               |                | _           | 400  | pF    |                                        |

## TABLE 18-10: I<sup>2</sup>C<sup>™</sup> BUS DATA REQUIREMENTS

\* These parameters are characterized but not tested.

**Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of Start or Stop conditions.