Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Obsolete                                                      |

| Number of LABs/CLBs            | -                                                             |

| Number of Logic Elements/Cells | -                                                             |

| Total RAM Bits                 | -                                                             |

| Number of I/O                  | 49                                                            |

| Number of Gates                | 15000                                                         |

| Voltage - Supply               | 1.425V ~ 1.575V                                               |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                            |

| Package / Case                 | 68-VFQFN Exposed Pad                                          |

| Supplier Device Package        | 68-QFN (8x8)                                                  |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/a3p015-1qng68i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# I/Os Per Package <sup>1</sup>

| ProASIC3<br>Devices  | A3P015 <sup>2</sup> | A3P030           | A3P060           | A3P125           | A3P                           | 250 <sup>3</sup>       | A3P                           | 400 <sup>3</sup>       | A3F                           | P600                   | A3P                           | 1000                   |

|----------------------|---------------------|------------------|------------------|------------------|-------------------------------|------------------------|-------------------------------|------------------------|-------------------------------|------------------------|-------------------------------|------------------------|

| Cortex-M1<br>Devices |                     |                  |                  |                  | M1A3F                         | 250 <sup>3,5</sup>     | M1A3                          | P400 <sup>3</sup>      | M1A3                          | 3P600                  | M1A3                          | P1000                  |

|                      |                     |                  |                  |                  | I/C                           | ) Type                 |                               |                        |                               |                        |                               |                        |

| Package              | Single-Ended I/O    | Single-Ended I/O | Single-Ended I/O | Single-Ended I/O | Single-Ended I/O <sup>4</sup> | Differential I/O Pairs |

| QN48                 | _                   | 34               | _                | _                | -                             | _                      |                               | _                      | _                             | _                      | _                             | _                      |

| QN68                 | 49                  | 49               | _                | _                | _                             | _                      | _                             | _                      |                               | _                      | _                             | _                      |

| QN132 <sup>7</sup>   | _                   | 81               | 80               | 84               | 87                            | 19                     | _                             | -                      |                               | _                      | _                             | _                      |

| CS121                | _                   | _                | 96               | _                | -                             | _                      | _                             | _                      | _                             | _                      | _                             | _                      |

| VQ100                | _                   | 77               | 71               | 71               | 68                            | 13                     | _                             | _                      |                               | _                      | _                             | _                      |

| TQ144                | _                   | _                | 91               | 100              | -                             | _                      | _                             | _                      | _                             | _                      | _                             | _                      |

| PQ208                | _                   | -                | -                | 133              | 151                           | 34                     | 151                           | 34                     | 154                           | 35                     | 154                           | 35                     |

| FG144                | _                   | _                | 96               | 97               | 97                            | 24                     | 97                            | 25                     | 97                            | 25                     | 97                            | 25                     |

| FG256 <sup>5,6</sup> | _                   | -                | -                | -                | 157                           | 38                     | 178                           | 38                     | 177                           | 43                     | 177                           | 44                     |

| FG484 <sup>6</sup>   | _                   | _                | _                | _                | -                             | _                      | 194                           | 38                     | 235                           | 60                     | 300                           | 74                     |

#### Notes

- 1. When considering migrating your design to a lower- or higher-density device, refer to the ProASIC3 FPGA Fabric User Guide to ensure complying with design and board migration requirements.

- 2. A3P015 is not recommended for new designs.

- 3. For A3P250 and A3P400 devices, the maximum number of LVPECL pairs in east and west banks cannot exceed 15. Refer to the ProASIC3 FPGA Fabric Users Guide for position assignments of the 15 LVPECL pairs.

- 4. Each used differential I/O pair reduces the number of single-ended I/Os available by two.

- 5. The M1A3P250 device does not support FG256 package.

- 6. FG256 and FG484 are footprint-compatible packages.

- 7. Package not available.

Table 1 • ProASIC3 FPGAs Package Sizes Dimensions

| Package                            | CS121 | QN48  | QN68  | QN132 * | VQ100   | TQ144   | PQ208   | FG144   | FG256   | FG484   |

|------------------------------------|-------|-------|-------|---------|---------|---------|---------|---------|---------|---------|

| Length × Width (mm × mm)           | 6 × 6 | 6 × 6 | 8 × 8 | 8 × 8   | 14 × 14 | 20 × 20 | 28 × 28 | 13 × 13 | 17 × 17 | 23 × 23 |

| Nominal Area<br>(mm <sup>2</sup> ) | 36    | 36    | 64    | 64      | 196     | 400     | 784     | 169     | 289     | 529     |

| Pitch (mm)                         | 0.5   | 0.4   | 0.4   | 0.5     | 0.5     | 0.5     | 0.5     | 1.0     | 1.0     | 1.0     |

| Height (mm)                        | 0.99  | 0.90  | 0.90  | 0.75    | 1.00    | 1.40    | 3.40    | 1.45    | 1.60    | 2.23    |

Note: \* Package not available

Revision 18 III

Your valuable IP is protected with industry-standard security, making remote ISP possible. A ProASIC3 device provides the best available security for programmable logic designs.

#### Single Chip

Flash-based FPGAs store their configuration information in on-chip flash cells. Once programmed, the configuration data is an inherent part of the FPGA structure, and no external configuration data needs to be loaded at system power-up (unlike SRAM-based FPGAs). Therefore, flash-based ProASIC3 FPGAs do not require system configuration components such as EEPROMs or microcontrollers to load device configuration data. This reduces bill-of-materials costs and PCB area, and increases security and system reliability.

#### Instant On

Flash-based ProASIC3 devices support Level 0 of the Instant On classification standard. This feature helps in system component initialization, execution of critical tasks before the processor wakes up, setup and configuration of memory blocks, clock generation, and bus activity management. The Instant On feature of flash-based ProASIC3 devices greatly simplifies total system design and reduces total system cost, often eliminating the need for CPLDs and clock generation PLLs that are used for these purposes in a system. In addition, glitches and brownouts in system power will not corrupt the ProASIC3 device's flash configuration, and unlike SRAM-based FPGAs, the device will not have to be reloaded when system power is restored. This enables the reduction or complete removal of the configuration PROM, expensive voltage monitor, brownout detection, and clock generator devices from the PCB design. Flash-based ProASIC3 devices simplify total system design and reduce cost and design risk while increasing system reliability and improving system initialization time.

#### Firm Errors

Firm errors occur most commonly when high-energy neutrons, generated in the upper atmosphere, strike a configuration cell of an SRAM FPGA. The energy of the collision can change the state of the configuration cell and thus change the logic, routing, or I/O behavior in an unpredictable way. These errors are impossible to prevent in SRAM FPGAs. The consequence of this type of error can be a complete system failure. Firm errors do not exist in the configuration memory of ProASIC3 flash-based FPGAs. Once it is programmed, the flash cell configuration element of ProASIC3 FPGAs cannot be altered by high-energy neutrons and is therefore immune to them. Recoverable (or soft) errors occur in the user data SRAM of all FPGA devices. These can easily be mitigated by using error detection and correction (EDAC) circuitry built into the FPGA fabric.

#### Low Power

Flash-based ProASIC3 devices exhibit power characteristics similar to an ASIC, making them an ideal choice for power-sensitive applications. ProASIC3 devices have only a very limited power-on current surge and no high-current transition period, both of which occur on many FPGAs.

ProASIC3 devices also have low dynamic power consumption to further maximize power savings.

Table 2-2 • Recommended Operating Conditions <sup>1</sup>

| Symbol                    | Parame                                          | eters <sup>1</sup>     | Commercial           | Industrial              | Units |

|---------------------------|-------------------------------------------------|------------------------|----------------------|-------------------------|-------|

| $T_J$                     | Junction temperature                            |                        | 0 to 85 <sup>2</sup> | -40 to 100 <sup>2</sup> | °C    |

| VCC <sup>3</sup>          | 1.5 V DC core supply voltage                    | ge                     | 1.425 to 1.575       | 1.425 to 1.575          | V     |

| VJTAG                     | JTAG DC voltage                                 |                        | 1.4 to 3.6           | 1.4 to 3.6              | V     |

| VPUMP                     | Programming voltage                             | Programming Mode       | 3.15 to 3.45         | 3.15 to 3.45            | V     |

|                           |                                                 | Operation <sup>4</sup> | 0 to 3.6             | 0 to 3.6                | V     |

| VCCPLL                    | Analog power supply (PLL)                       |                        | 1.425 to 1.575       | 1.425 to 1.575          | V     |

| VCCI and VMV <sup>5</sup> | 1.5 V DC supply voltage                         |                        | 1.425 to 1.575       | 1.425 to 1.575          | V     |

|                           | 1.8 V DC supply voltage                         |                        | 1.7 to 1.9           | 1.7 to 1.9              | V     |

|                           | 2.5 V DC supply voltage                         |                        | 2.3 to 2.7           | 2.3 to 2.7              | V     |

|                           | 3.3 V DC supply voltage                         |                        | 3.0 to 3. <u>6</u>   | 3.0 to 3. <u>6</u>      | V     |

|                           | 3.3 V wide range DC supply voltage <sup>6</sup> |                        | 2.7 to 3.6           | 2.7 to 3.6              | V     |

|                           | LVDS/B-LVDS/M-LVDS diff                         | erential I/O           | 2.375 to 2.625       | 2.375 to 2.625          | V     |

|                           | LVPECL differential I/O                         |                        | 3.0 to 3.6           | 3.0 to 3.6              | V     |

#### Notes:

- 1. All parameters representing voltages are measured with respect to GND unless otherwise specified.

- Software Default Junction Temperature Range in the Libero<sup>®</sup> System-on-Chip (SoC) software is set to 0°C to +70°C for commercial, and -40°C to +85°C for industrial. To ensure targeted reliability standards are met across the full range of junction temperatures, Microsemi recommends using custom settings for temperature range before running timing and power analysis tools. For more information regarding custom settings, refer to the New Project Dialog Box in the Libero SoC Online Help.

- 3. The ranges given here are for power supplies only. The recommended input voltage ranges specific to each I/O standard are given in Table 2-18 on page 2-19.

- 4. VPUMP can be left floating during operation (not programming mode).

- 5. VMV and VCCI should be at the same voltage within a given I/O bank. VMV pins must be connected to the corresponding VCCI pins. See the "VMVx I/O Supply Voltage (quiet)" section on page 3-1 for further information.

- 6. 3.3 V wide range is compliant to the JESD8-B specification and supports 3.0 V VCCI operation.

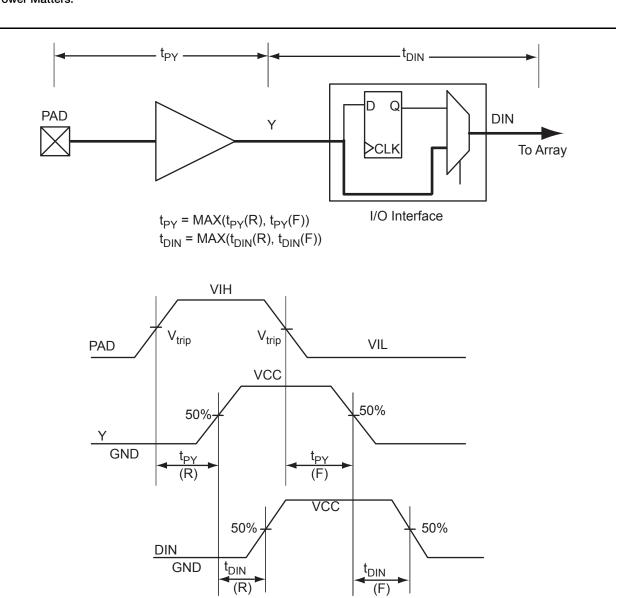

Figure 2-4 • Input Buffer Timing Model and Delays (Example)

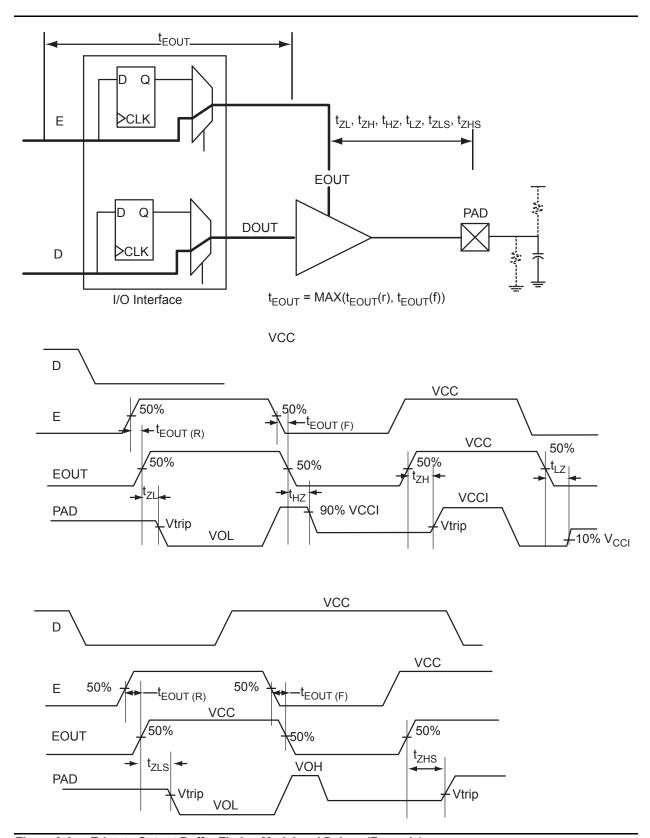

Figure 2-6 • Tristate Output Buffer Timing Model and Delays (Example)

#### **Timing Characteristics**

Table 2-41 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V

Applicable to Advanced I/O Banks

|                   | 1 -            | ī                 | T               |                  | T               | I                 | T               | T               | T               |                 | I                |                  | I 1   |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

| 2 mA              | Std.           | 0.66              | 7.66            | 0.04             | 1.02            | 0.43              | 7.80            | 6.59            | 2.65            | 2.61            | 10.03            | 8.82             | ns    |

|                   | -1             | 0.56              | 6.51            | 0.04             | 0.86            | 0.36              | 6.63            | 5.60            | 2.25            | 2.22            | 8.54             | 7.51             | ns    |

|                   | -2             | 0.49              | 5.72            | 0.03             | 0.76            | 0.32              | 5.82            | 4.92            | 1.98            | 1.95            | 7.49             | 6.59             | ns    |

| 4 mA              | Std.           | 0.66              | 7.66            | 0.04             | 1.02            | 0.43              | 7.80            | 6.59            | 2.65            | 2.61            | 10.03            | 8.82             | ns    |

|                   | -1             | 0.56              | 6.51            | 0.04             | 0.86            | 0.36              | 6.63            | 5.60            | 2.25            | 2.22            | 8.54             | 7.51             | ns    |

|                   | -2             | 0.49              | 5.72            | 0.03             | 0.76            | 0.32              | 5.82            | 4.92            | 1.98            | 1.95            | 7.49             | 6.59             | ns    |

| 6 mA              | Std.           | 0.66              | 4.91            | 0.04             | 1.02            | 0.43              | 5.00            | 4.07            | 2.99            | 3.20            | 7.23             | 6.31             | ns    |

|                   | -1             | 0.56              | 4.17            | 0.04             | 0.86            | 0.36              | 4.25            | 3.46            | 2.54            | 2.73            | 6.15             | 5.36             | ns    |

|                   | -2             | 0.49              | 3.66            | 0.03             | 0.76            | 0.32              | 3.73            | 3.04            | 2.23            | 2.39            | 5.40             | 4.71             | ns    |

| 8 mA              | Std.           | 0.66              | 4.91            | 0.04             | 1.02            | 0.43              | 5.00            | 4.07            | 2.99            | 3.20            | 7.23             | 6.31             | ns    |

|                   | -1             | 0.56              | 4.17            | 0.04             | 0.86            | 0.36              | 4.25            | 3.46            | 2.54            | 2.73            | 6.15             | 5.36             | ns    |

|                   | -2             | 0.49              | 3.66            | 0.03             | 0.76            | 0.32              | 3.73            | 3.04            | 2.23            | 2.39            | 5.40             | 4.71             | ns    |

| 12 mA             | Std.           | 0.66              | 3.53            | 0.04             | 1.02            | 0.43              | 3.60            | 2.82            | 3.21            | 3.58            | 5.83             | 5.06             | ns    |

|                   | <b>–</b> 1     | 0.56              | 3.00            | 0.04             | 0.86            | 0.36              | 3.06            | 2.40            | 2.73            | 3.05            | 4.96             | 4.30             | ns    |

|                   | -2             | 0.49              | 2.64            | 0.03             | 0.76            | 0.32              | 2.69            | 2.11            | 2.40            | 2.68            | 4.36             | 3.78             | ns    |

| 16 mA             | Std.           | 0.66              | 3.33            | 0.04             | 1.02            | 0.43              | 3.39            | 2.56            | 3.26            | 3.68            | 5.63             | 4.80             | ns    |

|                   | -1             | 0.56              | 2.83            | 0.04             | 0.86            | 0.36              | 2.89            | 2.18            | 2.77            | 3.13            | 4.79             | 4.08             | ns    |

|                   | -2             | 0.49              | 2.49            | 0.03             | 0.76            | 0.32              | 2.53            | 1.91            | 2.44            | 2.75            | 4.20             | 3.58             | ns    |

| 24 mA             | Std.           | 0.66              | 3.08            | 0.04             | 1.02            | 0.43              | 3.13            | 2.12            | 3.32            | 4.06            | 5.37             | 4.35             | ns    |

|                   | <b>–</b> 1     | 0.56              | 2.62            | 0.04             | 0.86            | 0.36              | 2.66            | 1.80            | 2.83            | 3.45            | 4.57             | 3.70             | ns    |

|                   | -2             | 0.49              | 2.30            | 0.03             | 0.76            | 0.32              | 2.34            | 1.58            | 2.48            | 3.03            | 4.01             | 3.25             | ns    |

#### Notes:

- 1. Software default selection highlighted in gray.

- 2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### **B-LVDS/M-LVDS**

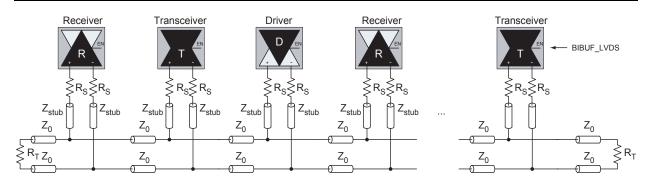

Bus LVDS (B-LVDS) and Multipoint LVDS (M-LVDS) specifications extend the existing LVDS standard to high-performance multipoint bus applications. Multidrop and multipoint bus configurations may contain any combination of drivers, receivers, and transceivers. Microsemi LVDS drivers provide the higher drive current required by B-LVDS and M-LVDS to accommodate the loading. The drivers require series terminations for better signal quality and to control voltage swing. Termination is also required at both ends of the bus since the driver can be located anywhere on the bus. These configurations can be implemented using the TRIBUF\_LVDS and BIBUF\_LVDS macros along with appropriate terminations. Multipoint designs using Microsemi LVDS macros can achieve up to 200 MHz with a maximum of 20 loads. A sample application is given in Figure 2-13. The input and output buffer delays are available in the LVDS section in Table 2-92.

Example: For a bus consisting of 20 equidistant loads, the following terminations provide the required differential voltage, in worst-case Industrial operating conditions, at the farthest receiver:  $R_S$  = 60  $\Omega$  and  $R_T$  = 70  $\Omega$ , given  $Z_0$  = 50  $\Omega$  (2") and  $Z_{stub}$  = 50  $\Omega$  (~1.5").

Figure 2-13 • B-LVDS/M-LVDS Multipoint Application Using LVDS I/O Buffers

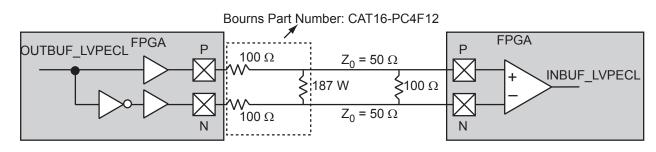

#### **LVPECL**

Low-Voltage Positive Emitter-Coupled Logic (LVPECL) is another differential I/O standard. It requires that one data bit be carried through two signal lines. Like LVDS, two pins are needed. It also requires external resistor termination.

The full implementation of the LVDS transmitter and receiver is shown in an example in Figure 2-14. The building blocks of the LVPECL transmitter-receiver are one transmitter macro, one receiver macro, three board resistors at the transmitter end, and one resistor at the receiver end. The values for the three driver resistors are different from those used in the LVDS implementation because the output standard specifications are different.

Figure 2-14 • LVPECL Circuit Diagram and Board-Level Implementation

2-67 Revision 18

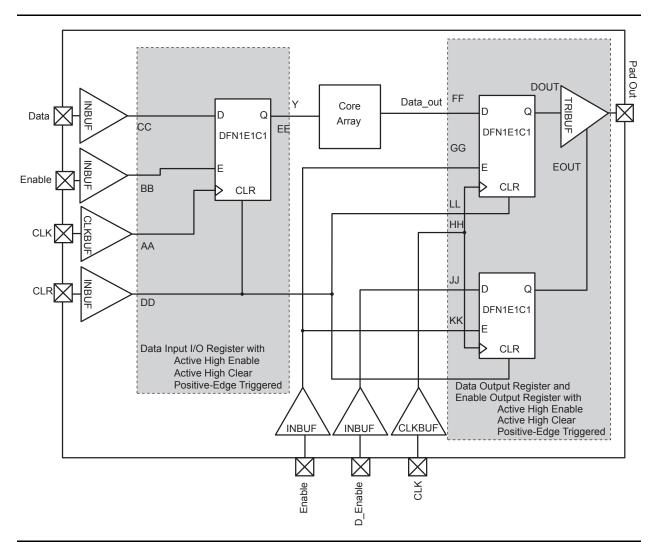

# Fully Registered I/O Buffers with Synchronous Enable and Asynchronous Clear

Figure 2-16 • Timing Model of the Registered I/O Buffers with Synchronous Enable and Asynchronous Clear

2-71 Revision 18

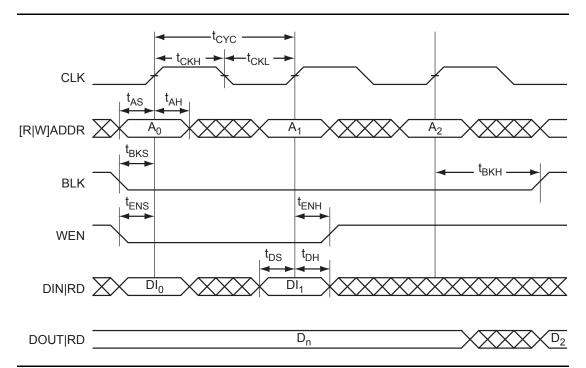

Figure 2-33 • RAM Write, Output Retained. Applicable to Both RAM4K9 and RAM512x18.

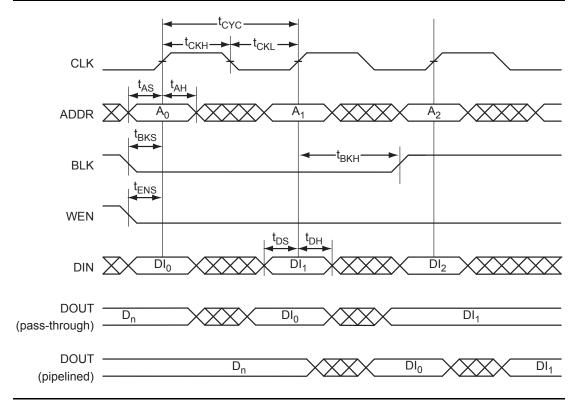

Figure 2-34 • RAM Write, Output as Write Data (WMODE = 1). Applicable to RAM4K9 Only.

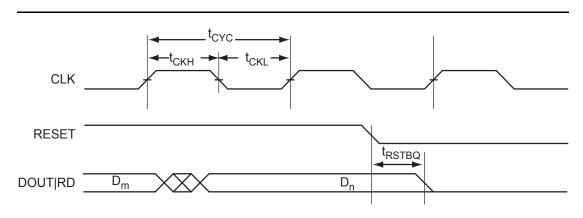

Figure 2-35 • RAM Reset. Applicable to Both RAM4K9 and RAM512x18.

2-95 Revision 18

Table 2-117 • RAM512X18 Commercial-Case Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V

| Parameter             | Description                                                                                                        | -2   | -1   | Std. | Units |

|-----------------------|--------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| t <sub>AS</sub>       | Address setup time                                                                                                 | 0.25 | 0.28 | 0.33 | ns    |

| t <sub>AH</sub>       | Address hold time                                                                                                  | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>ENS</sub>      | REN, WEN setup time                                                                                                | 0.13 | 0.15 | 0.17 | ns    |

| t <sub>ENH</sub>      | REN, WEN hold time                                                                                                 | 0.10 | 0.11 | 0.13 | ns    |

| t <sub>DS</sub>       | Input data (WD) setup time                                                                                         | 0.18 | 0.21 | 0.25 | ns    |

| t <sub>DH</sub>       | Input data (WD) hold time                                                                                          | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>CKQ1</sub>     | Clock High to new data valid on RD (output retained)                                                               | 2.16 | 2.46 | 2.89 | ns    |

| t <sub>CKQ2</sub>     | Clock High to new data valid on RD (pipelined)                                                                     | 0.90 | 1.02 | 1.20 | ns    |

| t <sub>C2CRWH</sub> 1 | Address collision clk-to-clk delay for reliable read access after write on same address—Applicable to Opening Edge | 0.50 | 0.43 | 0.38 | ns    |

| t <sub>C2CWRH</sub> 1 | Address collision clk-to-clk delay for reliable write access after read on same address—Applicable to Opening Edge | 0.59 | 0.50 | 0.44 | ns    |

| t <sub>RSTBQ</sub>    | RESET Low to data out Low on RD (flow-through)                                                                     | 0.92 | 1.05 | 1.23 | ns    |

|                       | RESET Low to data out Low on RD (pipelined)                                                                        | 0.92 | 1.05 | 1.23 | ns    |

| t <sub>REMRSTB</sub>  | RESET removal                                                                                                      | 0.29 | 0.33 | 0.38 | ns    |

| t <sub>RECRSTB</sub>  | RESET recovery                                                                                                     | 1.50 | 1.71 | 2.01 | ns    |

| t <sub>MPWRSTB</sub>  | RESET minimum pulse width                                                                                          | 0.21 | 0.24 | 0.29 | ns    |

| t <sub>CYC</sub>      | Clock cycle time                                                                                                   | 3.23 | 3.68 | 4.32 | ns    |

| F <sub>MAX</sub>      | Maximum frequency                                                                                                  | 310  | 272  | 231  | MHz   |

#### Notes:

2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

2-97 Revision 18

<sup>1.</sup> For more information, refer to the application note Simultaneous Read-Write Operations in Dual-Port SRAM for Flash-Based cSoCs and FPGAs.

In critical applications, an upset in the JTAG circuit could allow entrance to an undesired JTAG state. In such cases, Microsemi recommends tying off TRST to GND through a resistor placed close to the FPGA pin.

Note that to operate at all VJTAG voltages, 500  $\Omega$  to 1 k $\Omega$  will satisfy the requirements.

# **Special Function Pins**

NC No Connect

This pin is not connected to circuitry within the device. These pins can be driven to any voltage or can be left floating with no effect on the operation of the device.

DC Do Not Connect

This pin should not be connected to any signals on the PCB. These pins should be left unconnected.

### **Related Documents**

#### **User's Guides**

ProASIC FPGA Fabric User's Guide

http://www.microsemi.com/soc/documents/PA3\_UG.pdf

## **Packaging**

The following documents provide packaging information and device selection for low power flash devices.

#### **Product Catalog**

http://www.microsemi.com/soc/documents/ProdCat PIB.pdf

Lists devices currently recommended for new designs and the packages available for each member of the family. Use this document or the datasheet tables to determine the best package for your design, and which package drawing to use.

#### Package Mechanical Drawings

http://www.microsemi.com/soc/documents/PckgMechDrwngs.pdf

This document contains the package mechanical drawings for all packages currently or previously supplied by Actel. Use the bookmarks to navigate to the package mechanical drawings.

Additional packaging materials are at http://www.microsemi.com/products/solutions/package/docs.aspx.

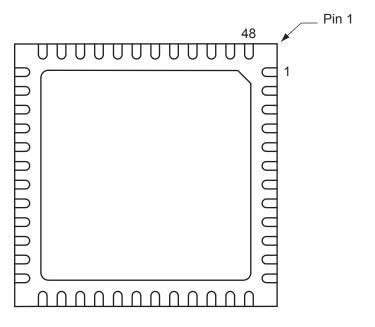

# 4 – Package Pin Assignments

# **QN48 – Bottom View**

Note: The die attach paddle center of the package is tied to ground (GND).

#### Note

For more information on package drawings, see PD3068: Package Mechanical Drawings.

## Package Pin Assignments

| 01140      |                 |  |  |  |  |  |

|------------|-----------------|--|--|--|--|--|

|            | N48             |  |  |  |  |  |

| Pin Number | A3P030 Function |  |  |  |  |  |

| 1          | IO82RSB1        |  |  |  |  |  |

| 2          | GEC0/IO73RSB1   |  |  |  |  |  |

| 3          | GEA0/IO72RSB1   |  |  |  |  |  |

| 4          | GEB0/IO71RSB1   |  |  |  |  |  |

| 5          | GND             |  |  |  |  |  |

| 6          | VCCIB1          |  |  |  |  |  |

| 7          | IO68RSB1        |  |  |  |  |  |

| 8          | IO67RSB1        |  |  |  |  |  |

| 9          | IO66RSB1        |  |  |  |  |  |

| 10         | IO65RSB1        |  |  |  |  |  |

| 11         | IO64RSB1        |  |  |  |  |  |

| 12         | IO62RSB1        |  |  |  |  |  |

| 13         | IO61RSB1        |  |  |  |  |  |

| 14         | IO60RSB1        |  |  |  |  |  |

| 15         | IO57RSB1        |  |  |  |  |  |

| 16         | IO55RSB1        |  |  |  |  |  |

| 17         | IO53RSB1        |  |  |  |  |  |

| 18         | VCC             |  |  |  |  |  |

| 19         | VCCIB1          |  |  |  |  |  |

| 20         | IO46RSB1        |  |  |  |  |  |

| 21         | IO42RSB1        |  |  |  |  |  |

| 22         | TCK             |  |  |  |  |  |

| 23         | TDI             |  |  |  |  |  |

| 24         | TMS             |  |  |  |  |  |

| 25         | VPUMP           |  |  |  |  |  |

| 26         | TDO             |  |  |  |  |  |

| 27         | TRST            |  |  |  |  |  |

| 28         | VJTAG           |  |  |  |  |  |

| 29         | IO38RSB0        |  |  |  |  |  |

| 30         | GDB0/IO34RSB0   |  |  |  |  |  |

| 31         | GDA0/IO33RSB0   |  |  |  |  |  |

| 32         | GDC0/IO32RSB0   |  |  |  |  |  |

| 33         | VCCIB0          |  |  |  |  |  |

| 34         | GND             |  |  |  |  |  |

| 35         | VCC             |  |  |  |  |  |

| 36         | IO25RSB0        |  |  |  |  |  |

| QN48       |                 |  |  |  |  |  |

|------------|-----------------|--|--|--|--|--|

| Pin Number | A3P030 Function |  |  |  |  |  |

| 37         | IO24RSB0        |  |  |  |  |  |

| 38         | IO22RSB0        |  |  |  |  |  |

| 39         | IO20RSB0        |  |  |  |  |  |

| 40         | IO18RSB0        |  |  |  |  |  |

| 41         | IO16RSB0        |  |  |  |  |  |

| 42         | IO14RSB0        |  |  |  |  |  |

| 43         | IO10RSB0        |  |  |  |  |  |

| 44         | IO08RSB0        |  |  |  |  |  |

| 45         | IO06RSB0        |  |  |  |  |  |

| 46         | IO04RSB0        |  |  |  |  |  |

| 47         | IO02RSB0        |  |  |  |  |  |

| 48         | IO00RSB0        |  |  |  |  |  |

4-2 Revision 18

## Package Pin Assignments

|            | CS121           |            | CS121           |            | CS121           |  |  |  |

|------------|-----------------|------------|-----------------|------------|-----------------|--|--|--|

| Pin Number | A3P060 Function | Pin Number | A3P060 Function | Pin Number | A3P060 Function |  |  |  |

| A1         | GNDQ            | D4         | IO10RSB0        | G7         | VCC             |  |  |  |

| A2         | IO01RSB0        | D5         | IO11RSB0        | G8         | GDC0/IO46RSB0   |  |  |  |

| A3         | GAA1/IO03RSB0   | D6         | IO18RSB0        | G9         | GDA1/IO49RSB0   |  |  |  |

| A4         | GAC1/IO07RSB0   | D7         | IO32RSB0        | G10        | GDB0/IO48RSB0   |  |  |  |

| A5         | IO15RSB0        | D8         | IO31RSB0        | G11        | GCA0/IO40RSB0   |  |  |  |

| A6         | IO13RSB0        | D9         | GCA2/IO41RSB0   | H1         | IO75RSB1        |  |  |  |

| A7         | IO17RSB0        | D10        | IO30RSB0        | H2         | IO76RSB1        |  |  |  |

| A8         | GBB1/IO22RSB0   | D11        | IO33RSB0        | H3         | GFC2/IO78RSB1   |  |  |  |

| A9         | GBA1/IO24RSB0   | E1         | IO87RSB1        | H4         | GFA2/IO80RSB1   |  |  |  |

| A10        | GNDQ            | E2         | GFC0/IO85RSB1   | H5         | IO77RSB1        |  |  |  |

| A11        | VMV0            | E3         | IO92RSB1        | H6         | GEC2/IO66RSB1   |  |  |  |

| B1         | GAA2/IO95RSB1   | E4         | IO94RSB1        | H7         | IO54RSB1        |  |  |  |

| B2         | IO00RSB0        | E5         | VCC             | H8         | GDC2/IO53RSB1   |  |  |  |

| В3         | GAA0/IO02RSB0   | E6         | VCCIB0          | H9         | VJTAG           |  |  |  |

| B4         | GAC0/IO06RSB0   | E7         | GND             | H10        | TRST            |  |  |  |

| B5         | IO08RSB0        | E8         | GCC0/IO36RSB0   | H11        | IO44RSB0        |  |  |  |

| B6         | IO12RSB0        | E9         | IO34RSB0        | J1         | GEC1/IO74RSB1   |  |  |  |

| B7         | IO16RSB0        | E10        | GCB1/IO37RSB0   | J2         | GEC0/IO73RSB1   |  |  |  |

| B8         | GBC1/IO20RSB0   | E11        | GCC1/IO35RSB0   | J3         | GEB1/IO72RSB1   |  |  |  |

| В9         | GBB0/IO21RSB0   | F1         | VCOMPLF         | J4         | GEA0/IO69RSB1   |  |  |  |

| B10        | GBB2/IO27RSB0   | F2         | GFB0/IO83RSB1   | J5         | GEB2/IO67RSB1   |  |  |  |

| B11        | GBA2/IO25RSB0   | F3         | GFA0/IO82RSB1   | J6         | IO62RSB1        |  |  |  |

| C1         | IO89RSB1        | F4         | GFC1/IO86RSB1   | J7         | GDA2/IO51RSB1   |  |  |  |

| C2         | GAC2/IO91RSB1   | F5         | VCCIB1          | J8         | GDB2/IO52RSB1   |  |  |  |

| C3         | GAB1/IO05RSB0   | F6         | VCC             | J9         | TDI             |  |  |  |

| C4         | GAB0/IO04RSB0   | F7         | VCCIB0          | J10        | TDO             |  |  |  |

| C5         | IO09RSB0        | F8         | GCB2/IO42RSB0   | J11        | GDC1/IO45RSB0   |  |  |  |

| C6         | IO14RSB0        | F9         | GCC2/IO43RSB0   | K1         | GEB0/IO71RSB1   |  |  |  |

| C7         | GBA0/IO23RSB0   | F10        | GCB0/IO38RSB0   | K2         | GEA1/IO70RSB1   |  |  |  |

| C8         | GBC0/IO19RSB0   | F11        | GCA1/IO39RSB0   | K3         | GEA2/IO68RSB1   |  |  |  |

| C9         | IO26RSB0        | G1         | VCCPLF          | K4         | IO64RSB1        |  |  |  |

| C10        | IO28RSB0        | G2         | GFB2/IO79RSB1   | K5         | IO60RSB1        |  |  |  |

| C11        | GBC2/IO29RSB0   | G3         | GFA1/IO81RSB1   | K6         | IO59RSB1        |  |  |  |

| D1         | IO88RSB1        | G4         | GFB1/IO84RSB1   | K7         | IO56RSB1        |  |  |  |

| D2         | IO90RSB1        | G5         | GND             | K8         | TCK             |  |  |  |

| D3         | GAB2/IO93RSB1   | G6         | VCCIB1          | K9         | TMS             |  |  |  |

4-16 Revision 18

| F          | G144            |

|------------|-----------------|

| Pin Number | A3P250 Function |

| K1         | GEB0/IO99NDB3   |

| K2         | GEA1/IO98PDB3   |

| K3         | GEA0/IO98NDB3   |

| K4         | GEA2/IO97RSB2   |

| K5         | IO90RSB2        |

| K6         | IO84RSB2        |

| K7         | GND             |

| K8         | IO66RSB2        |

| K9         | GDC2/IO63RSB2   |

| K10        | GND             |

| K11        | GDA0/IO60VDB1   |

| K12        | GDB0/IO59VDB1   |

| L1         | GND             |

| L2         | VMV3            |

| L3         | GEB2/IO96RSB2   |

| L4         | IO91RSB2        |

| L5         | VCCIB2          |

| L6         | IO82RSB2        |

| L7         | IO80RSB2        |

| L8         | IO72RSB2        |

| L9         | TMS             |

| L10        | VJTAG           |

| L11        | VMV2            |

| L12        | TRST            |

| M1         | GNDQ            |

| M2         | GEC2/IO95RSB2   |

| M3         | IO92RSB2        |

| M4         | IO89RSB2        |

| M5         | IO87RSB2        |

| M6         | IO85RSB2        |

| M7         | IO78RSB2        |

| M8         | IO76RSB2        |

| M9         | TDI             |

| M10        | VCCIB2          |

| M11        | VPUMP           |

| M12        | GNDQ            |

| FG484      |                 |  |  |  |  |

|------------|-----------------|--|--|--|--|

| Pin Number | A3P400 Function |  |  |  |  |

| E21        | NC              |  |  |  |  |

| E22        | NC              |  |  |  |  |

| F1         | NC              |  |  |  |  |

| F2         | NC              |  |  |  |  |

| F3         | NC              |  |  |  |  |

| F4         | IO154VDB3       |  |  |  |  |

| F5         | IO155VDB3       |  |  |  |  |

| F6         | IO11RSB0        |  |  |  |  |

| F7         | IO07RSB0        |  |  |  |  |

| F8         | GAC0/IO04RSB0   |  |  |  |  |

| F9         | GAC1/IO05RSB0   |  |  |  |  |

| F10        | IO20RSB0        |  |  |  |  |

| F11        | IO24RSB0        |  |  |  |  |

| F12        | IO33RSB0        |  |  |  |  |

| F13        | IO39RSB0        |  |  |  |  |

| F14        | IO45RSB0        |  |  |  |  |

| F15        | GBC0/IO54RSB0   |  |  |  |  |

| F16        | IO48RSB0        |  |  |  |  |

| F17        | VMV0            |  |  |  |  |

| F18        | IO61NPB1        |  |  |  |  |

| F19        | IO63PDB1        |  |  |  |  |

| F20        | NC              |  |  |  |  |

| F21        | NC              |  |  |  |  |

| F22        | NC              |  |  |  |  |

| G1         | NC              |  |  |  |  |

| G2         | NC              |  |  |  |  |

| G3         | NC              |  |  |  |  |

| G4         | IO151VDB3       |  |  |  |  |

| G5         | IO151UDB3       |  |  |  |  |

| G6         | GAC2/IO153UDB3  |  |  |  |  |

| G7         | IO06RSB0        |  |  |  |  |

| G8         | GNDQ            |  |  |  |  |

| G9         | IO10RSB0        |  |  |  |  |

| G10        | IO19RSB0        |  |  |  |  |

| G11        | IO26RSB0        |  |  |  |  |

| G12        | IO30RSB0        |  |  |  |  |

|            | FG484           |

|------------|-----------------|

| Pin Number | A3P400 Function |

| G13        | IO40RSB0        |

| G14        | IO46RSB0        |

| G15        | GNDQ            |

| G16        | IO47RSB0        |

| G17        | GBB2/IO61PPB1   |

| G18        | IO53RSB0        |

| G19        | IO63NDB1        |

| G20        | NC              |

| G21        | NC              |

| G22        | NC              |

| H1         | NC              |

| H2         | NC              |

| H3         | VCC             |

| H4         | IO150PDB3       |

| H5         | IO08RSB0        |

| H6         | IO153VDB3       |

| H7         | IO152VDB3       |

| H8         | VMV0            |

| H9         | VCCIB0          |

| H10        | VCCIB0          |

| H11        | IO25RSB0        |

| H12        | IO31RSB0        |

| H13        | VCCIB0          |

| H14        | VCCIB0          |

| H15        | VMV1            |

| H16        | GBC2/IO62PDB1   |

| H17        | IO65RSB1        |

| H18        | IO52RSB0        |

| H19        | IO66PDB1        |

| H20        | VCC             |

| H21        | NC              |

| H22        | NC              |

| J1         | NC              |

| J2         | NC              |

| J3         | NC              |

| J4         | IO150NDB3       |

| FG484      |                 |  |

|------------|-----------------|--|

| Pin Number | A3P400 Function |  |

| J5         | IO149NPB3       |  |

| J6         | IO09RSB0        |  |

| J7         | IO152UDB3       |  |

| J8         | VCCIB3          |  |

| J9         | GND             |  |

| J10        | VCC             |  |

| J11        | VCC             |  |

| J12        | VCC             |  |

| J13        | VCC             |  |

| J14        | GND             |  |

| J15        | VCCIB1          |  |

| J16        | IO62NDB1        |  |

| J17        | IO49RSB0        |  |

| J18        | IO64PPB1        |  |

| J19        | IO66NDB1        |  |

| J20        | NC              |  |

| J21        | NC              |  |

| J22        | NC              |  |

| K1         | NC              |  |

| K2         | NC              |  |

| K3         | NC              |  |

| K4         | IO148NDB3       |  |

| K5         | IO148PDB3       |  |

| K6         | IO149PPB3       |  |

| K7         | GFC1/IO147PPB3  |  |

| K8         | VCCIB3          |  |

| K9         | VCC             |  |

| K10        | GND             |  |

| K11        | GND             |  |

| K12        | GND             |  |

| K13        | GND             |  |

| K14        | VCC             |  |

| K15        | VCCIB1          |  |

| K16        | GCC1/IO67PPB1   |  |

| K17        | IO64NPB1        |  |

| K18        | IO73PDB1        |  |

| FG484      |                 |  |

|------------|-----------------|--|

| Pin Number | A3P600 Function |  |

| K19        | IO75NDB1        |  |

| K20        | NC              |  |

| K21        | IO76NDB1        |  |

| K22        | IO76PDB1        |  |

| L1         | NC              |  |

| L2         | IO155PDB3       |  |

| L3         | NC              |  |

| L4         | GFB0/IO163NPB3  |  |

| L5         | GFA0/IO162NDB3  |  |

| L6         | GFB1/IO163PPB3  |  |

| L7         | VCOMPLF         |  |

| L8         | GFC0/IO164NPB3  |  |

| L9         | VCC             |  |

| L10        | GND             |  |

| L11        | GND             |  |

| L12        | GND             |  |

| L13        | GND             |  |

| L14        | VCC             |  |

| L15        | GCC0/IO69NPB1   |  |

| L16        | GCB1/IO70PPB1   |  |

| L17        | GCA0/IO71NPB1   |  |

| L18        | IO67NPB1        |  |

| L19        | GCB0/IO70NPB1   |  |

| L20        | IO77PDB1        |  |

| L21        | IO77NDB1        |  |

| L22        | IO78NPB1        |  |

| M1         | NC              |  |

| M2         | IO155NDB3       |  |

| M3         | IO158NPB3       |  |

| M4         | GFA2/IO161PPB3  |  |

| M5         | GFA1/IO162PDB3  |  |

| M6         | VCCPLF          |  |

| M7         | IO160NDB3       |  |

| M8         | GFB2/IO160PDB3  |  |

| M9         | VCC             |  |

| M10        | GND             |  |

| FG484      |                 |  |

|------------|-----------------|--|

| Pin Number | A3P600 Function |  |

| M11        | GND             |  |

| M12        | GND             |  |

| M13        | GND             |  |

| M14        | VCC             |  |

| M15        | GCB2/IO73PPB1   |  |

| M16        | GCA1/IO71PPB1   |  |

| M17        | GCC2/IO74PPB1   |  |

| M18        | IO80PPB1        |  |

| M19        | GCA2/IO72PDB1   |  |

| M20        | IO79PPB1        |  |

| M21        | IO78PPB1        |  |

| M22        | NC              |  |

| N1         | IO154NDB3       |  |

| N2         | IO154PDB3       |  |

| N3         | NC              |  |

| N4         | GFC2/IO159PDB3  |  |

| N5         | IO161NPB3       |  |

| N6         | IO156PPB3       |  |

| N7         | IO129RSB2       |  |

| N8         | VCCIB3          |  |

| N9         | VCC             |  |

| N10        | GND             |  |

| N11        | GND             |  |

| N12        | GND             |  |

| N13        | GND             |  |

| N14        | VCC             |  |

| N15        | VCCIB1          |  |

| N16        | IO73NPB1        |  |

| N17        | IO80NPB1        |  |

| N18        | IO74NPB1        |  |

| N19        | IO72NDB1        |  |

| N20        | NC              |  |

| N21        | IO79NPB1        |  |

| N22        | NC              |  |

| P1         | NC              |  |

| P2         | IO153PDB3       |  |

|            | FG484           |  |  |

|------------|-----------------|--|--|

| Pin Number | A3P600 Function |  |  |

| P3         | IO153NDB3       |  |  |

| P4         | IO159NDB3       |  |  |

| P5         | IO156NPB3       |  |  |

| P6         | IO151PPB3       |  |  |

| P7         | IO158PPB3       |  |  |

| P8         | VCCIB3          |  |  |

| P9         | GND             |  |  |

| P10        | VCC             |  |  |

| P11        | VCC             |  |  |

| P12        | VCC             |  |  |

| P13        | VCC             |  |  |

| P14        | GND             |  |  |

| P15        | VCCIB1          |  |  |

| P16        | GDB0/IO87NPB1   |  |  |

| P17        | IO85NDB1        |  |  |

| P18        | IO85PDB1        |  |  |

| P19        | IO84PDB1        |  |  |

| P20        | NC              |  |  |

| P21        | IO81PDB1        |  |  |

| P22        | NC              |  |  |

| R1         | NC              |  |  |

| R2         | NC              |  |  |

| R3         | VCC             |  |  |

| R4         | IO150PDB3       |  |  |

| R5         | IO151NPB3       |  |  |

| R6         | IO147NPB3       |  |  |

| R7         | GEC0/IO146NPB3  |  |  |

| R8         | VMV3            |  |  |

| R9         | VCCIB2          |  |  |

| R10        | VCCIB2          |  |  |

| R11        | IO117RSB2       |  |  |

| R12        | IO110RSB2       |  |  |

| R13        | VCCIB2          |  |  |

| R14        | VCCIB2          |  |  |

| R15        | VMV2            |  |  |

| R16        | IO94RSB2        |  |  |

#### Datasheet Information

| Revision                                                    | Changes                                                                                                                                                                                                                                                                                                  | Page       |

|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Revision 5 (Aug 2008) DC and Switching Characteristics v1.3 | TJ, Maximum Junction Temperature, was changed to 100° from 110° in the "Thermal Characteristics" section and EQ 1. The calculated result of Maximum Power Allowed has thus changed to 1.463 W from 1.951 W.                                                                                              | 2-6        |

|                                                             | Values for the A3P015 device were added to Table 2-7 • Quiescent Supply Current Characteristics.                                                                                                                                                                                                         | 2-7        |

|                                                             | Values for the A3P015 device were added to Table 2-14 • Different Components Contributing to Dynamic Power Consumption in ProASIC3 Devices. P <sub>AC14</sub> was removed. Table 2-15 • Different Components Contributing to the Static Power Consumption in ProASIC3 Devices is new.                    | 2-11, 2-12 |

|                                                             | The "PLL Contribution—PPLL" section was updated to change the $P_{PLL}$ formula from $P_{AC13} + P_{AC14} * F_{CLKOUT}$ to $P_{DC4} + P_{AC13} * F_{CLKOUT}$ .                                                                                                                                           | 2-14       |

|                                                             | Both fall and rise values were included for $t_{\text{DDRISUD}}$ and $t_{\text{DDRIHD}}$ in Table 2-102 • Input DDR Propagation Delays.                                                                                                                                                                  | 2-78       |

|                                                             | Table 2-107 • A3P015 Global Resource is new.                                                                                                                                                                                                                                                             | 2-86       |

|                                                             | The typical value for Delay Increments in Programmable Delay Blocks was changed from 160 to 200 in Table 2-115 • ProASIC3 CCC/PLL Specification.                                                                                                                                                         | 2-90       |

| Revision 4 (Jun 2008) DC and Switching Characteristics v1.2 | Table note references were added to Table 2-2 • Recommended Operating Conditions 1, and the order of the table notes was changed.                                                                                                                                                                        | 2-2        |

|                                                             | The title for Table 2-4 • Overshoot and Undershoot Limits 1 was modified to remove "as measured on quiet I/Os." Table note 1 was revised to remove "estimated SSO density over cycles." Table note 2 was revised to remove "refers only to overshoot/undershoot limits for simultaneous switching I/Os." | 2-3        |

|                                                             | The "Power per I/O Pin" section was updated to include 3 additional tables pertaining to input buffer power and output buffer power.                                                                                                                                                                     | 2-7        |

|                                                             | Table 2-29 • I/O Output Buffer Maximum Resistances 1 was revised to include values for 3.3 V PCI/PCI-X.                                                                                                                                                                                                  | 2-27       |

|                                                             | Table 2-90 • LVDS Minimum and Maximum DC Input and Output Levels was updated.                                                                                                                                                                                                                            | 2-66       |

| Revision 3 (Jun 2008) Packaging v1.3                        | Pin numbers were added to the "QN68 – Bottom View" package diagram. Note 2 was added below the diagram.                                                                                                                                                                                                  | 4-3        |

|                                                             | The "QN132 – Bottom View" package diagram was updated to include D1 to D4. In addition, note 1 was changed from top view to bottom view, and note 2 is new.                                                                                                                                              | 4-6        |

| Revision 2 (Feb 2008)<br>Product Brief v1.0                 | This document was divided into two sections and given a version number, starting at v1.0. The first section of the document includes features, benefits, ordering information, and temperature and speed grade offerings. The second section is a device family overview.                                | N/A        |

|                                                             | This document was updated to include A3P015 device information. QN68 is a new package that was added because it is offered in the A3P015. The following sections were updated:  "Features and Benefits"                                                                                                  | N/A        |

|                                                             | "ProASIC3 Ordering Information"                                                                                                                                                                                                                                                                          |            |

|                                                             | "Temperature Grade Offerings"                                                                                                                                                                                                                                                                            |            |

|                                                             | "ProASIC3 Flash Family FPGAs"                                                                                                                                                                                                                                                                            |            |

|                                                             | "A3P015 and A3P030" note                                                                                                                                                                                                                                                                                 |            |

|                                                             | Introduction and Overview (NA)                                                                                                                                                                                                                                                                           |            |

5-7 Revision 18

# **Datasheet Categories**

#### **Categories**

In order to provide the latest information to designers, some datasheet parameters are published before data has been fully characterized from silicon devices. The data provided for a given device, as highlighted in the "ProASIC3 Device Status" table on page IV, is designated as either "Product Brief," "Advance," "Preliminary," or "Production." The definitions of these categories are as follows:

#### **Product Brief**

The product brief is a summarized version of a datasheet (advance or production) and contains general product information. This document gives an overview of specific device and family information.

#### Advance

This version contains initial estimated information based on simulation, other products, devices, or speed grades. This information can be used as estimates, but not for production. This label only applies to the DC and Switching Characteristics chapter of the datasheet and will only be used when the data has not been fully characterized.

#### **Preliminary**

The datasheet contains information based on simulation and/or initial characterization. The information is believed to be correct, but changes are possible.

#### Unmarked (production)

This version contains information that is considered to be final.

#### **Export Administration Regulations (EAR)**

The products described in this document are subject to the Export Administration Regulations (EAR). They could require an approved export license prior to export from the United States. An export includes release of product or disclosure of technology to a foreign national inside or outside the United States.

# Safety Critical, Life Support, and High-Reliability Applications Policy

The products described in this advance status document may not have completed the Microsemi qualification process. Products may be amended or enhanced during the product introduction and qualification process, resulting in changes in device functionality or performance. It is the responsibility of each customer to ensure the fitness of any product (but especially a new product) for a particular purpose, including appropriateness for safety-critical, life-support, and other high-reliability applications. Consult the Microsemi SoC Products Group Terms and Conditions for specific liability exclusions relating to life-support applications. A reliability report covering all of the SoC Products Group's products is available at http://www.microsemi.com/soc/documents/ORT\_Report.pdf. Microsemi also offers a variety of enhanced qualification and lot acceptance screening procedures. Contact your local sales office for additional reliability information.

5-15 Revision 18