Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT           |

| Number of I/O              | 17                                                        |

| Program Memory Size        | 1KB (1K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | 16 x 8                                                    |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f011ahh020eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

viii

| ADC Data High Byte Register                                                                                          |                                                     |

|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| Low Power Operational Amplifier                                                                                      |                                                     |

| Comparator                                                                                                           | . 140                                               |

| Temperature Sensor                                                                                                   |                                                     |

| Flash Memory Architecture Flash Information Area Operation  Flash Operation Timing Hains the Flash Fragman Pagisters | <ul><li>. 146</li><li>. 147</li><li>. 147</li></ul> |

| Flash Operation Timing Using the Flash Frequency Registers  Flash Code Protection Against External Access            | . 149                                               |

| Flash Code Protection Against Accidental Program and Erasure  Byte Programming  Page Erase  Mass Erase               | . 151<br>. 152                                      |

| Flash Controller Bypass                                                                                              | . 152                                               |

| Flash Control Register Definitions                                                                                   | . 153                                               |

| Flash Status Register                                                                                                | . 156                                               |

| Flash Sector Protect Register                                                                                        | . 157                                               |

| Flash Option Bits                                                                                                    | . 159                                               |

| Option Bit Configuration By Reset                                                                                    | . 160                                               |

| Reading the Flash Information Page                                                                                   | . 161                                               |

| Trim Bit Address Register  Trim Bit Data Register                                                                    |                                                     |

| Flash Option Bit Address Space                                                                                       |                                                     |

| Flash Program Memory Address 0001H                                                                                   |                                                     |

# Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

xii

| Figure 25. | Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface; #2 of 2                                    |

|------------|-----------------------------------------------------------------------------------------------------------------|

| Figure 26. | OCD Data Format                                                                                                 |

| Figure 27. | Recommended 20MHz Crystal Oscillator Configuration 199                                                          |

| Figure 28. | Connecting the On-Chip Oscillator to an External RC Network 201                                                 |

| Figure 29. | Typical RC Oscillator Frequency as a Function of the External Capacitance with a $45 \mathrm{k}\Omega$ Resistor |

| Figure 30. | Opcode Map Cell Description                                                                                     |

| Figure 31. | First Opcode Map                                                                                                |

| Figure 32. | Second Opcode Map after 1FH                                                                                     |

| Figure 33. | Typical Active Mode IDD Versus System Clock Frequency                                                           |

| Figure 34. | Port Input Sample Timing                                                                                        |

| Figure 35. | GPIO Port Output Timing                                                                                         |

| Figure 36. | On-Chip Debugger Timing                                                                                         |

| Figure 37. | UART Timing With CTS                                                                                            |

| Figure 38. | UART Timing Without CTS                                                                                         |

| Table 59. | Watchdog Timer Control Register (WDTCTL)               |

|-----------|--------------------------------------------------------|

| Table 60. | Watchdog Timer Reload Upper Byte Register (WDTU) 9     |

| Table 61. | Watchdog Timer Reload High Byte Register (WDTH) 9      |

| Table 62. | Watchdog Timer Reload Low Byte Register (WDTL) 9       |

| Table 63. | UART Control 0 Register (U0CTL0)                       |

| Table 64. | UART Control 1 Register (U0CTL1)                       |

| Table 65. | UART Status 0 Register (U0STAT0)                       |

| Table 66. | UART Status 1 Register (U0STAT1)                       |

| Table 67. | UART Transmit Data Register (U0TXD)                    |

| Table 68. | UART Receive Data Register (U0RXD)                     |

| Table 69. | UART Address Compare Register (U0ADDR)                 |

| Table 70. | UART Baud Rate High Byte Register (U0BRH)11            |

| Table 71. | UART Baud Rate Low Byte Register (U0BRL)               |

| Table 72. | UART Baud Rates                                        |

| Table 73. | ADC Control Register 0 (ADCCTL0)                       |

| Table 74. | ADC Control/Status Register 1 (ADCCTL1)                |

| Table 75. | ADC Data High Byte Register (ADCD_H)                   |

| Table 76. | ADC Data Low Byte Register (ADCD_L)                    |

| Table 77. | Comparator Control Register (CMP0)                     |

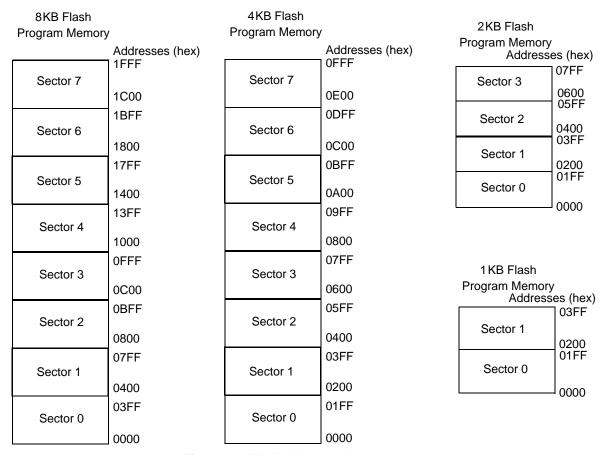

| Table 78. | Z8 Encore! XP F082A Series Flash Memory Configurations |

| Table 79. | Flash Code Protection Using the Flash Option Bits      |

| Table 80. | Flash Status Register (FSTAT)                          |

| Table 81. | Flash Control Register (FCTL)                          |

| Table 82. | Flash Page Select Register (FPS)                       |

| Table 83. | Flash Sector Protect Register (FPROT)                  |

| Table 84. | Flash Frequency High Byte Register (FFREQH)            |

| Table 85. | Flash Frequency Low Byte Register (FFREQL)             |

| Table 86. | Trim Bit Address Register (TRMADR)                     |

| Table 87. | Trim Bit Data Register (TRMDR)                         |

| Table 88. | Flash Option Bits at Program Memory Address 0000H 16   |

- Up to 8 ports capable of direct LED drive with no current limit resistor required

- On-Chip Debugger (OCD)

- Voltage Brown-Out (VBO) protection

- Programmable low battery detection (LVD) (8-pin devices only)

- Bandgap generated precision voltage references available for the ADC, comparator, VBO and LVD

- Power-On Reset (POR)

- 2.7 V to 3.6 V operating voltage

- 8-, 20- and 28-pin packages

- $0^{\circ}$ C to  $+70^{\circ}$ C and  $-40^{\circ}$ C to  $+105^{\circ}$ C for operating temperature ranges

# **Part Selection Guide**

Table 1 identifies the basic features and package styles available for each device within the Z8 Encore! XP F082A Series product line.

Table 1. Z8 Encore! XP F082A Series Family Part Selection Guide

| Part<br>Number | Flash<br>(KB) | RAM<br>(B) | NVDS <sup>1</sup><br>(B) | I/O  | Comparator | Advanced<br>Analog <sup>2</sup> | ADC<br>Inputs | Packages           |

|----------------|---------------|------------|--------------------------|------|------------|---------------------------------|---------------|--------------------|

| Z8F082A        | 8             | 1024       | 0                        | 6–23 | Yes        | Yes                             | 4–8           | 8-, 20- and 28-pin |

| Z8F081A        | 8             | 1024       | 0                        | 6–25 | Yes        | No                              | 0             | 8-, 20- and 28-pin |

| Z8F042A        | 4             | 1024       | 128                      | 6–23 | Yes        | Yes                             | 4–8           | 8-, 20- and 28-pin |

| Z8F041A        | 4             | 1024       | 128                      | 6–25 | Yes        | No                              | 0             | 8-, 20- and 28-pin |

| Z8F022A        | 2             | 512        | 64                       | 6–23 | Yes        | Yes                             | 4–8           | 8-, 20- and 28-pin |

| Z8F021A        | 2             | 512        | 64                       | 6–25 | Yes        | No                              | 0             | 8-, 20- and 28-pin |

| Z8F012A        | 1             | 256        | 16                       | 6–23 | Yes        | Yes                             | 4–8           | 8-, 20- and 28-pin |

| Z8F011A        | 1             | 256        | 16                       | 6–25 | Yes        | No                              | 0             | 8-, 20- and 28-pin |

#### Notes:

- 1. Non-volatile data storage.

- 2. Advanced Analog includes ADC, temperature sensor and low-power operational amplifier.

# Register Map

Table 7 provides the address map for the Register File of the Z8 Encore! XP F082A Series devices. Not all devices and package styles in the Z8 Encore! XP F082A Series support the ADC, or all of the GPIO Ports. Consider registers for unimplemented peripherals as Reserved.

Table 7. Register File Address Map

| Address (Hex)  | Register Description              | Mnemonic | Reset (Hex) | Page      |

|----------------|-----------------------------------|----------|-------------|-----------|

| General-Purpos | e RAM                             |          |             |           |

| Z8F082A/Z8F08  | 1A Devices                        |          |             |           |

| 000-3FF        | General-Purpose Register File RAM | _        | XX          |           |

| 400-EFF        | Reserved                          | _        | XX          |           |

| Z8F042A/Z8F04  | 1A Devices                        |          |             |           |

| 000–3FF        | General-Purpose Register File RAM | _        | XX          |           |

| 400-EFF        | Reserved                          | _        | XX          |           |

| Z8F022A/Z8F02  | 1A Devices                        |          |             |           |

| 000–1FF        | General-Purpose Register File RAM | _        | XX          |           |

| 200-EFF        | Reserved                          | _        | XX          |           |

| Z8F012A/Z8F01  | 1A Devices                        |          |             |           |

| 000-0FF        | General-Purpose Register File RAM | _        | XX          |           |

| 100-EFF        | Reserved                          | _        | XX          |           |

| Timer 0        |                                   |          |             |           |

| F00            | Timer 0 High Byte                 | T0H      | 00          | <u>90</u> |

| F01            | Timer 0 Low Byte                  | T0L      | 01          | 90        |

| F02            | Timer 0 Reload High Byte          | T0RH     | FF          | <u>91</u> |

| F03            | Timer 0 Reload Low Byte           | T0RL     | FF          | <u>91</u> |

| F04            | Timer 0 PWM High Byte             | T0PWMH   | 00          | <u>92</u> |

| F05            | Timer 0 PWM Low Byte              | T0PWML   | 00          | <u>92</u> |

| F06            | Timer 0 Control 0                 | T0CTL0   | 00          | <u>85</u> |

| F07            | Timer 0 Control 1                 | T0CTL1   | 00          | <u>86</u> |

#### Notes:

- 1. XX = Undefined.

- 2. Refer to the <u>eZ8 CPU Core User Manual (UM0128)</u>.

# **Shared Debug Pin**

On the 8-pin version of this device only, the Debug pin shares function with the PA0 GPIO pin. This pin performs as a general purpose input pin on power-up, but the debug logic monitors this pin during the reset sequence to determine if the unlock sequence occurs. If the unlock sequence is present, the debug function is unlocked and the pin no longer functions as a GPIO pin. If it is not present, the debug feature is disabled until/unless another reset event occurs. For more details, see the On-Chip Debugger chapter on page 180.

# **Crystal Oscillator Override**

For systems using a crystal oscillator, PA0 and PA1 are used to connect the crystal. When the crystal oscillator is enabled, the GPIO settings are overridden and PA0 and PA1 are disabled. See the Oscillator Control Register Definitions section on page 196 for details.

### **5V Tolerance**

All six I/O pins on the 8-pin devices are 5V-tolerant, unless the programmable pull-ups are enabled. If the pull-ups are enabled and inputs higher than  $V_{DD}$  are applied to these parts, excessive current flows through those pull-up devices and can damage the chip.

Note:

In the 20- and 28-pin versions of this device, any pin which shares functionality with an ADC, crystal or comparator port is not 5 V-tolerant, including PA[1:0], PB[5:0] and PC[2:0]. All other signal pins are 5 V-tolerant and can safely handle inputs higher than  $V_{DD}$  except when the programmable pull-ups are enabled.

# **External Clock Setup**

For systems using an external TTL drive, PB3 is the clock source for 20- and 28-pin devices. In this case, configure PB3 for alternate function CLKIN. Write the Oscillator Control (OSCCTL) Register such that the external oscillator is selected as the system clock. See the Oscillator Control Register Definitions section on page 196 for details. For 8-pin devices, use PA1 instead of PB3.

Table 15. Port Alternate Function Mapping (Non 8-Pin Parts) (Continued)

| Port                | Pin | Mnemonic                           | Alternate Function Description            | Alternate Function<br>Set Register AFS1 |

|---------------------|-----|------------------------------------|-------------------------------------------|-----------------------------------------|

| Port C <sup>5</sup> | PC0 | Reserved                           |                                           | AFS1[0]: 0                              |

|                     |     | ANA4/CINP                          | ADC or Comparator Input                   | AFS1[0]: 1                              |

|                     | PC1 | Reserved                           |                                           | AFS1[1]: 0                              |

|                     |     | ANA5/CINN                          | ADC or Comparator Input                   | AFS1[1]: 1                              |

|                     | PC2 | Reserved                           |                                           | AFS1[2]: 0                              |

|                     |     | ANA6/V <sub>REF</sub> <sup>4</sup> | ADC Analog Input or ADC Voltage Reference | AFS1[2]: 1                              |

|                     | PC3 | COUT                               | Comparator Output                         | AFS1[3]: 0                              |

|                     |     | Reserved                           |                                           | AFS1[3]: 1                              |

|                     | PC4 | Reserved                           |                                           | AFS1[4]: 0                              |

|                     |     |                                    |                                           | AFS1[4]: 1                              |

|                     | PC5 | Reserved                           |                                           | AFS1[5]: 0                              |

|                     |     |                                    |                                           | AFS1[5]: 1                              |

|                     | PC6 | Reserved                           |                                           | AFS1[6]: 0                              |

|                     |     |                                    |                                           | AFS1[6]: 1                              |

|                     | PC7 | Reserved                           |                                           | AFS1[7]: 0                              |

|                     |     |                                    |                                           | AFS1[7]: 1                              |

| Port D <sup>6</sup> | PD0 | RESET                              | External Reset                            | N/A                                     |

| Natae.              |     |                                    |                                           |                                         |

#### Notes:

- 1. Because there is only a single alternate function for each Port A pin, the Alternate Function Set registers are not implemented for Port A. Enabling alternate function selections automatically enables the associated alternate function. See the <a href="Port A-D Alternate Function Subregisters">Port A-D Alternate Function Subregisters</a> (PxAF) section on page 47 for details.

- 2. Whether PA0/PA6 takes on the timer input or timer output complement function depends on the timer configuration. See the <u>Timer Pin Signal Operation</u> section on page 84 for details.

- 3. Because there are at most two choices of alternate function for any pin of Port B, the Alternate Function Set Register AFS2 is not used to select the function. Alternate function selection must also be enabled. See the <a href="Port-A-D Alternate Function Subregisters">Port-A-D Alternate Function Subregisters</a> (PxAF) section on page 47 for details.

- 4. V<sub>REF</sub> is available on PB5 in 28-pin products and on PC2 in 20-pin parts.

- 5. Because there are at most two choices of alternate function for any pin of Port C, the Alternate Function Set Register AFS2 is not used to select the function. Alternate function selection must also be enabled. See the <a href="Port-A-D Alternate Function Subregisters">Port-A-D Alternate Function Subregisters</a> (PxAF) section on page 47 for details.

- 6. Because there is only a single alternate function for the Port PD0 pin, the Alternate Function Set registers are not implemented for Port D. Enabling alternate function selections automatically enables the associated alternate function. See the Port A–D Alternate Function Subregisters (PxAF) section on page 47 for details.

Table 23. Port A-D Output Control Subregisters (PxOC)

| Bit     | 7                             | 6                           | 5           | 4             | 3             | 2            | 1            | 0        |

|---------|-------------------------------|-----------------------------|-------------|---------------|---------------|--------------|--------------|----------|

| Field   | POC7                          | POC6                        | POC5        | POC4          | POC3          | POC2         | POC1         | POC0     |

| RESET   | 00H (Ports A-C); 01H (Port D) |                             |             |               |               |              |              |          |

| R/W     | R/W                           | R/W R/W R/W R/W R/W R/W R/W |             |               |               |              |              |          |

| Address | If 03H ir                     | n Port A–D A                | Address Reg | jister, acces | sible througl | h the Port A | –D Control F | Register |

| Bit   | Description                                                                                                           |

|-------|-----------------------------------------------------------------------------------------------------------------------|

| [7:0] | Port Output Control                                                                                                   |

| POCx  | These bits function independently of the alternate function bit and always disable the drains if set to 1.            |

|       | 0 = The source current is enabled for any output mode unless overridden by the alternate function (push-pull output). |

|       | 1 = The source current for the associated pin is disabled (open-drain mode).                                          |

Note: x indicates the specific GPIO port pin number (7–0).

### Port A-D High Drive Enable Subregisters

The Port A–D High Drive Enable Subregister, shown in Table 24, is accessed through the port A–D Control Register by writing 04H to the Port A–D Address Register. Setting the bits in the Port A–D High Drive Enable subregisters to 1 configures the specified port pins for high current output drive operation. The Port A–D High Drive Enable subregister affects the pins directly and, as a result, alternate functions are also affected.

Table 24. Port A-D High Drive Enable Subregisters (PxHDE)

| Bit     | 7         | 6            | 5           | 4             | 3             | 2            | 1            | 0        |

|---------|-----------|--------------|-------------|---------------|---------------|--------------|--------------|----------|

| Field   | PHDE7     | PHDE6        | PHDE5       | PHDE4         | PHDE3         | PHDE2        | PHDE1        | PHDE0    |

| RESET   | 0         | 0            | 0           | 0             | 0             | 0            | 0            | 0        |

| R/W     | R/W       | R/W          | R/W         | R/W           | R/W           | R/W          | R/W          | R/W      |

| Address | If 04H ir | n Port A–D A | Address Reg | jister, acces | sible througl | h the Port A | –D Control F | Register |

| Bit        | Description                                                       |

|------------|-------------------------------------------------------------------|

| [7:0]      | Port High Drive Enabled                                           |

| PHDEx      | 0 = The port pin is configured for standard output current drive. |

|            | 1 = The port pin is configured for high output current drive.     |

| Note: v ir | ndicates the specific GPIO port pin number (7–0)                  |

# GPIO Mode Interrupt Controller

The interrupt controller on the Z8 Encore! XP F082A Series products prioritizes the interrupt requests from the on-chip peripherals and the GPIO port pins. The features of interrupt controller include:

- 20 possible interrupt sources with 18 unique interrupt vectors:

- Twelve GPIO port pin interrupt sources (two interrupt vectors are shared)

- Eight on-chip peripheral interrupt sources (two interrupt vectors are shared)

- Flexible GPIO interrupts:

- Eight selectable rising and falling edge GPIO interrupts

- Four dual-edge interrupts

- Three levels of individually programmable interrupt priority

- Watchdog Timer and LVD can be configured to generate an interrupt

- Supports vectored and polled interrupts

Interrupt requests (IRQs) allow peripheral devices to suspend CPU operation in an orderly manner and force the CPU to start an interrupt service routine (ISR). Usually this interrupt service routine is involved with the exchange of data, status information, or control information between the CPU and the interrupting peripheral. When the service routine is completed, the CPU returns to the operation from which it was interrupted.

The eZ8 CPU supports both vectored and polled interrupt handling. For polled interrupts, the interrupt controller has no effect on operation. For more information about interrupt servicing by the eZ8 CPU, refer to the eZ8 CPU Core User Manual (UM0128), which is available for download on <a href="https://www.zilog.com">www.zilog.com</a>.

# **Interrupt Vector Listing**

Table 34 lists all of the interrupts available in order of priority. The interrupt vector is stored with the most-significant byte (MSB) at the even Program Memory address and the least-significant byte (LSB) at the following odd Program Memory address.

Note:

Some port interrupts are not available on the 8- and 20-pin packages. The ADC interrupt is unavailable on devices not containing an ADC.

Table 34. Trap and Interrupt Vectors in Order of Priority

| Priority | Program<br>Memory<br>Vector Address | Interrupt or Trap Source                                                                                               |

|----------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Highest  | 0002H                               | Reset (not an interrupt)                                                                                               |

|          | 0004H                               | Watchdog Timer (see Watchdog Timer)                                                                                    |

|          | 003AH                               | Primary Oscillator Fail Trap (not an interrupt)                                                                        |

|          | 003CH                               | Watchdog Oscillator Fail Trap (not an interrupt)                                                                       |

|          | 0006H                               | Illegal Instruction Trap (not an interrupt)                                                                            |

|          | H8000                               | Reserved                                                                                                               |

|          | 000AH                               | Timer 1                                                                                                                |

|          | 000CH                               | Timer 0                                                                                                                |

|          | 000EH                               | UART 0 receiver                                                                                                        |

|          | 0010H                               | UART 0 transmitter                                                                                                     |

|          | 0012H                               | Reserved                                                                                                               |

|          | 0014H                               | Reserved                                                                                                               |

|          | 0016H                               | ADC                                                                                                                    |

|          | 0018H                               | Port A Pin 7, selectable rising or falling input edge or LVD (see Reset, Stop Mode Recovery and Low Voltage Detection) |

|          | 001AH                               | Port A Pin 6, selectable rising or falling input edge or Comparator Output                                             |

|          | 001CH                               | Port A Pin 5, selectable rising or falling input edge                                                                  |

|          | 001EH                               | Port A Pin 4, selectable rising or falling input edge                                                                  |

|          | 0020H                               | Port A Pin 3, selectable rising or falling input edge                                                                  |

|          | 0022H                               | Port A Pin 2, selectable rising or falling input edge                                                                  |

|          | 0024H                               | Port A Pin 1, selectable rising or falling input edge                                                                  |

|          | 0026H                               | Port A Pin 0, selectable rising or falling input edge                                                                  |

|          | 0028H                               | Reserved                                                                                                               |

|          | 002AH                               | Reserved                                                                                                               |

|          | 002CH                               | Reserved                                                                                                               |

|          | 002EH                               | Reserved                                                                                                               |

|          | 0030H                               | Port C Pin 3, both input edges                                                                                         |

|          | 0032H                               | Port C Pin 2, both input edges                                                                                         |

|          | 0034H                               | Port C Pin 1, both input edges                                                                                         |

| owest    | 0036H                               | Port C Pin 0, both input edges                                                                                         |

|          | 0038H                               | Reserved                                                                                                               |

#### **PWM SINGLE OUTPUT Mode**

In PWM SINGLE OUTPUT Mode, the timer outputs a Pulse-Width Modulator (PWM) output signal through a GPIO port pin. The timer input is the system clock. The timer first counts up to the 16-bit PWM match value stored in the Timer PWM High and Low Byte registers. When the timer count value matches the PWM value, the Timer Output toggles. The timer continues counting until it reaches the reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

If the TPOL bit in the Timer Control Register is set to 1, the Timer Output signal begins as a High (1) and transitions to a Low (0) when the timer value matches the PWM value. The Timer Output signal returns to a High (1) after the timer reaches the reload value and is reset to 0001H.

If the TPOL bit in the Timer Control Register is set to 0, the Timer Output signal begins as a Low (0) and transitions to a High (1) when the timer value matches the PWM value. The Timer Output signal returns to a Low (0) after the timer reaches the reload value and is reset to 0001H.

Observe the following steps for configuring a timer for PWM SINGLE OUTPUT Mode and initiating the PWM operation:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for PWM SINGLE OUTPUT Mode

- Set the prescale value

- Set the initial logic level (High or Low) and PWM High/Low transition for the Timer Output alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H). This only affects the first pass in PWM mode. After the first timer reset in PWM mode, counting always begins at the reset value of 0001H.

- 3. Write to the PWM High and Low Byte registers to set the PWM value.

- 4. Write to the Timer Reload High and Low Byte registers to set the reload value (PWM period). The reload value must be greater than the PWM value.

- 5. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 6. Configure the associated GPIO port pin for the Timer Output alternate function.

- 7. Write to the Timer Control Register to enable the timer and initiate counting.

- Set or clear the CTSE bit to enable or disable control from the remote receiver using the CTS pin

- 6. Check the TDRE bit in the UART Status 0 Register to determine if the Transmit Data Register is empty (indicated by a 1). If empty, continue to <u>Step 7</u>. If the Transmit Data Register is full (indicated by a 0), continue to monitor the TDRE bit until the Transmit Data Register becomes available to receive new data.

- 7. Write the UART Control 1 Register to select the outgoing address bit.

- 8. Set the Multiprocessor Bit Transmitter (MPBT) if sending an address byte, clear it if sending a data byte.

- 9. Write the data byte to the UART Transmit Data Register. The transmitter automatically transfers the data to the Transmit Shift Register and transmits the data.

- 10. Make any changes to the Multiprocessor Bit Transmitter (MPBT) value, if appropriate and MULTIPROCESSOR Mode is enabled.

- 11. To transmit additional bytes, return to <u>Step 5</u>.

## Transmitting Data using the Interrupt-Driven Method

The UART Transmitter interrupt indicates the availability of the Transmit Data Register to accept new data for transmission. Observe the following steps to configure the UART for interrupt-driven data transmission:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the appropriate baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Execute a DI instruction to disable interrupts.

- 4. Write to the Interrupt control registers to enable the UART Transmitter interrupt and set the acceptable priority.

- 5. Write to the UART Control 1 Register to enable MULTIPROCESSOR (9-bit) Mode functions, if MULTIPROCESSOR Mode is appropriate.

- 6. Set the MULTIPROCESSOR Mode Select (MPEN) to Enable MULTIPROCESSOR Mode.

- 7. Write to the UART Control 0 Register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission

- Enable parity, if appropriate and if MULTIPROCESSOR Mode is not enabled and select either even or odd parity

| Bit         | Description (Continued)                                                                                                                                                                                                                                                                                                                             |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [2]<br>TDRE | TDRE—Transmitter Data Register Empty This bit indicates that the UART Transmit Data Register is empty and ready for additional data. Writing to the UART Transmit Data Register resets this bit. 0 = Do not write to the UART Transmit Data Register. 1 = The UART Transmit Data Register is ready to receive an additional byte to be transmitted. |

| [1]<br>TXE  | Transmitter Empty This bit indicates that the Transmit Shift Register is empty and character transmission is finished.  0 = Data is currently transmitting.  1 = Transmission is complete.                                                                                                                                                          |

| [0]<br>CTS  | CTS Signal When this bit is read it returns the level of the CTS signal. This signal is active Low.                                                                                                                                                                                                                                                 |

# **UART Status 1 Register**

This register contains multiprocessor control and status bits.

Table 66. UART Status 1 Register (U0STAT1)

| Bit     | 7                   | 6 | 5 | 4 | 3   | 2   | 1 | 0 |  |

|---------|---------------------|---|---|---|-----|-----|---|---|--|

| Field   | Reserved NEWFRM MPF |   |   |   |     |     |   |   |  |

| RESET   | 0                   | 0 | 0 | 0 | 0   | 0   | 0 | 0 |  |

| R/W     | R                   | R | R | R | R/W | R/W | R | R |  |

| Address | F44H                |   |   |   |     |     |   |   |  |

| Bit           | Description                                                                                                                                                                                                                                          |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:2]         | Reserved These bits are reserved and must be programmed to 000000.                                                                                                                                                                                   |

| [1]<br>NEWFRM | New Frame A status bit denoting the start of a new frame. Reading the UART Receive Data Register resets this bit to 0.  0 = The current byte is not the first data byte of a new frame.  1 = The current byte is the first data byte of a new frame. |

| [0]<br>MPRX   | Multiprocessor Receive Returns the value of the most recent multiprocessor bit received. Reading from the UART Receive Data Register resets this bit to 0.                                                                                           |

# **UART Transmit Data Register**

Data bytes written to the UART Transmit Data (UxTXD) Register, shown in Table 67, are shifted out on the TXDx pin. The Write-only UART Transmit Data Register shares a Register File address with the read-only UART Receive Data Register.

Figure 21. Flash Memory Arrangement

### **Flash Information Area**

The Flash information area is separate from Program Memory and is mapped to the address range FE00H to FFFFH. This area is readable but cannot be erased or overwritten. Factory trim values for the analog peripherals are stored here. Factory calibration data for the ADC is also stored here.

# **Operation**

The Flash Controller programs and erases Flash memory. The Flash Controller provides the proper Flash controls and timing for Byte Programming, Page Erase and Mass Erase of Flash memory.

The Flash Controller contains several protection mechanisms to prevent accidental programming or erasure. These mechanism operate on the page, sector and full-memory levels.

### **Trim Bit Address 0002H**

Table 92. Trim Option Bits at 0002H (TIPO)

| Bit                                             | 7                             | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------------------------------------------------|-------------------------------|---|---|---|---|---|---|---|--|--|

| Field                                           | IPO_TRIM                      |   |   |   |   |   |   |   |  |  |

| RESET                                           | U                             |   |   |   |   |   |   |   |  |  |

| R/W                                             | R/W                           |   |   |   |   |   |   |   |  |  |

| Address                                         | Information Page Memory 0022H |   |   |   |   |   |   |   |  |  |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                               |   |   |   |   |   |   |   |  |  |

### **Trim Bit Address 0003H**

**Note:** The LVD is available on 8-pin devices only.

#### Table 93. Trim Option Bits at Address 0003H (TLVD)

| Bit                                             | 7                             | 6        | 5   | 4        | 3   | 2   | 1   | 0   |  |

|-------------------------------------------------|-------------------------------|----------|-----|----------|-----|-----|-----|-----|--|

| Field                                           |                               | Reserved |     | LVD_TRIM |     |     |     |     |  |

| RESET                                           | U                             | U        | U   | U        | U U |     | U   | U   |  |

| R/W                                             | R/W                           | R/W      | R/W | R/W      | R/W | R/W | R/W | R/W |  |

| Address                                         | Information Page Memory 0023H |          |     |          |     |     |     |     |  |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                               |          |     |          |     |     |     |     |  |

| Bit               | Description                                                                                                                                                                                                                                                   |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:5]             | Reserved These bits are reserved and must be programmed to 111.                                                                                                                                                                                               |

| [4:0]<br>LVD_TRIM | Low Voltage Detect Trimm  This trimming affects the low voltage detection threshold. Each LSB represents a 50mV change in the threshold level. Alternatively, the low voltage threshold may be computed from the options bit value by the following equation: |

|                   | $LVD_LVL = 3.6 V - LVD_TRIM \times 0.05 V$                                                                                                                                                                                                                    |

|                   | These values are tabulated in Table 94.                                                                                                                                                                                                                       |

Table 107, NVDS Read Time

| Operation              | Minimum<br>Latency | Maximum<br>Latency |

|------------------------|--------------------|--------------------|

| Read (16 byte array)   | 875                | 9961               |

| Read (64 byte array)   | 876                | 8952               |

| Read (128 byte array)  | 883                | 7609               |

| Write (16 byte array)  | 4973               | 5009               |

| Write (64 byte array)  | 4971               | 5013               |

| Write (128 byte array) | 4984               | 5023               |

| Illegal Read           | 43                 | 43                 |

| Illegal Write          | 31                 | 31                 |

|                        |                    |                    |

If NVDS read performance is critical to your software architecture, you can optimize your code for speed. Try the first suggestion below before attempting the second.

- 1. Periodically refresh all addresses that are used. The optimal use of NVDS in terms of speed is to rotate the writes evenly among all addresses planned to use, bringing all reads closer to the minimum read time. Because the minimum read time is much less than the write time, however, actual speed benefits are not always realized.

- 2. Use as few unique addresses as possible to optimize the impact of refreshing, plus minimize the requirement for it.

Serial Break leaves the device in DEBUG Mode if that is the current mode. The OCD is held in Reset until the end of the Serial Break when the DBG pin returns High. Because of the open-drain nature of the DBG pin, the host can send a Serial Break to the OCD even if the OCD is transmitting a character.

# OCD Unlock Sequence (8-Pin Devices Only)

Because of pin-sharing on the 8-pin device, an unlock sequence must be performed to access the DBG pin. If this sequence is not completed during a system reset, then the PAO/DBG pin functions only as a GPIO pin.

The following sequence unlocks the DBG pin:

- 1. Hold PA2/RESET Low.

- 2. Wait 5ms for the internal reset sequence to complete.

- 3. Send the following bytes serially to the debug pin:

```

DBG ← 80H (autobaud)

DBG ← EBH

DBG ← 5AH

DBG ← 70H

DBG ← CDH (32-bit unlock key)

```

- 4. Release PA2/RESET. The PA0/DBG pin is now identical in function to that of the DBG pin on the 20-/28-pin device. To enter DEBUG Mode, reautobaud and write 80H to the OCD Control Register (see the On-Chip Debugger Commands section on page 186).

- Caution: Between <u>Steps 3</u> and <u>4</u>, there is an interval during which the 8-pin device is neither in RE-SET nor DEBUG Mode. If a device has been erased or has not yet been programmed, all program memory bytes contain FFH. The CPU interprets this value as an illegal instruction; therefore some irregular behavior can occur before entering DEBUG Mode, and the register values after entering DEBUG Mode will differ from their specified reset values. However, none of these irregularities prevent the programming of Flash memory. Before beginning system debug, Zilog recommends that some legal code be programmed into the 8-pin device and that a RESET occurs.

# **Breakpoints**

Execution Breakpoints are generated using the BRK instruction (opcode 00H). When the eZ8 CPU decodes a BRK instruction, it signals the On-Chip Debugger. If Breakpoints are enabled, the OCD enters DEBUG Mode and idles the eZ8 CPU. If Breakpoints are not

# **Ordering Information**

Order your F082A Series products from Zilog using the part numbers shown in Table 148. For more information about ordering, please consult your local Zilog sales office. The <u>Sales Location page</u> on the Zilog website lists all regional offices.

Table 148. Z8 Encore! XP F082A Series Ordering Matrix

| Table 140. 20 Elloore. At 1 002A certed ordering matrix |          |          |         |           |            |                     |                     |                |            |                    |                     |

|---------------------------------------------------------|----------|----------|---------|-----------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|

| Part Number                                             | Flash    | RAM      | NVDS    | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |

| Z8 Encore! XP F082A                                     | A Series | with 8 k | (B Flas | h, 10     | -Bit A     | Analo               | g-to-               | -Digit         | al Co      | nve                | erter               |

| Standard Temperature: 0°C to 70°C                       |          |          |         |           |            |                     |                     |                |            |                    |                     |

| Z8F082APB020SG                                          | 8KB      | 1KB      | 0       | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F082AQB020SG                                          | 8KB      | 1KB      | 0       | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F082ASB020SG                                          | 8KB      | 1KB      | 0       | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F082ASH020SG                                          | 8KB      | 1KB      | 0       | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F082AHH020SG                                          | 8KB      | 1KB      | 0       | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F082APH020SG                                          | 8KB      | 1KB      | 0       | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |

| Z8F082ASJ020SG                                          | 8KB      | 1KB      | 0       | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F082AHJ020SG                                          | 8KB      | 1KB      | 0       | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F082APJ020SG                                          | 8KB      | 1KB      | 0       | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |

| Extended Temperatu                                      | re: –40° | C to 10  | 5°C     |           |            |                     |                     |                |            |                    |                     |

| Z8F082APB020EG                                          | 8KB      | 1KB      | 0       | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F082AQB020EG                                          | 8KB      | 1KB      | 0       | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F082ASB020EG                                          | 8KB      | 1KB      | 0       | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F082ASH020EG                                          | 8KB      | 1KB      | 0       | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F082AHH020EG                                          | 8KB      | 1KB      | 0       | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F082APH020EG                                          | 8KB      | 1KB      | 0       | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |

| Z8F082ASJ020EG                                          | 8KB      | 1KB      | 0       | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F082AHJ020EG                                          | 8KB      | 1KB      | 0       | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F082APJ020EG                                          | 8KB      | 1KB      | 0       | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |

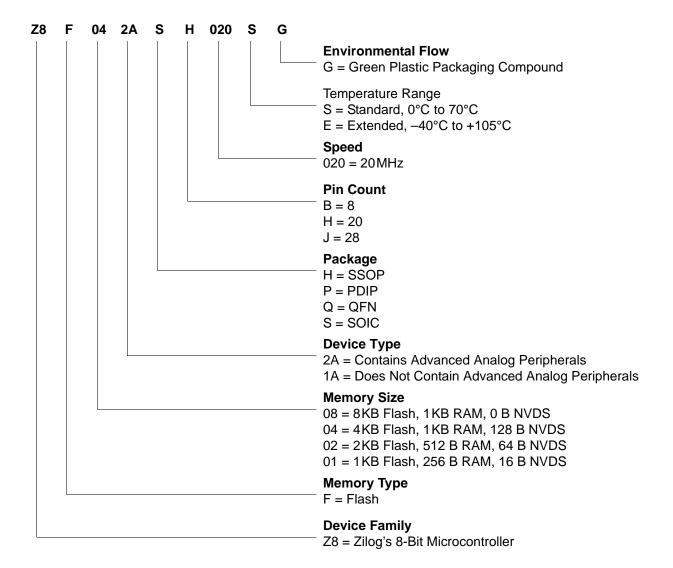

## **Part Number Suffix Designations**

Zilog part numbers consist of a number of components, as indicated in the following example.

**Example.** Part number Z8F042ASH020SG is an 8-bit Flash MCU with 4KB of Program Memory, equipped with advanced analog peripherals in a 20-pin SOIC package, operating within a 0°C to +70°C temperature range and built using lead-free solder.

| LD 210                           | architecture 55                                       |

|----------------------------------|-------------------------------------------------------|

| LDC 210                          | interrupt assertion types 58                          |

| LDCI 209, 210                    | interrupt vectors and priority 58                     |

| LDE 210                          | operation 57                                          |

| LDEI 209                         | register definitions 60                               |

| LDX 210                          | software interrupt assertion 59                       |

| LEA 210                          | interrupt edge select register 67                     |

| logical 210                      | interrupt request 0 register 60                       |

| MULT 208                         | interrupt request 1 register 61                       |

| NOP 209                          | interrupt request 2 register 62                       |

| OR 210                           | interrupt return 211                                  |

| ORX 210                          | interrupt vector listing 55                           |

| POP 210                          | interrupts                                            |

| POPX 210                         | UART 108                                              |

| program control 211              | IR 206                                                |

| PUSH 210                         | Ir 206                                                |

| PUSHX 210                        | IrDA                                                  |

| RCF 209, 210                     | architecture 120                                      |

| RET 211                          | block diagram 120                                     |

| RL 211                           | control register definitions 123                      |

| RLC 211                          | operation 120                                         |

| rotate and shift 211             | receiving data 122                                    |

| RR 211                           | transmitting data 121                                 |

| RRC 211                          | IRET 211                                              |

| SBC 208                          | IRQ0 enable high and low bit registers 62             |

| SCF 209, 210                     | IRQ1 enable high and low bit registers 64             |

| SRA 211                          | IRQ2 enable high and low bit registers 65             |

| SRL 211                          | IRR 206                                               |

| SRP 210                          | Irr 206                                               |

| STOP 210                         |                                                       |

| SUB 208                          |                                                       |

| SUBX 208                         | J                                                     |

| SWAP 211                         | JP 211                                                |

| TCM 209                          | jump, conditional, relative, and relative conditional |

| TCMX 209                         | 211                                                   |

| TM 209                           |                                                       |

| TMX 209                          |                                                       |

| TRAP 211                         | L                                                     |

| Watchdog Timer refresh 210       | LD 210                                                |

| XOR 210                          | LDC 210                                               |

| XORX 210                         | LDCI 209, 210                                         |

| instructions, eZ8 classes of 207 | LDE 210                                               |

| interrupt control register 69    | LDEI 209, 210                                         |

| interrupt controller 55          | LDX 210                                               |