Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Active                                                    |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT           |

| Number of I/O              | 6                                                         |

| Program Memory Size        | 1KB (1K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | 16 x 8                                                    |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                    |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f011apb020eg |

| Table 59. | Watchdog Timer Control Register (WDTCTL)               |

|-----------|--------------------------------------------------------|

| Table 60. | Watchdog Timer Reload Upper Byte Register (WDTU) 9     |

| Table 61. | Watchdog Timer Reload High Byte Register (WDTH) 9      |

| Table 62. | Watchdog Timer Reload Low Byte Register (WDTL) 9       |

| Table 63. | UART Control 0 Register (U0CTL0)                       |

| Table 64. | UART Control 1 Register (U0CTL1)                       |

| Table 65. | UART Status 0 Register (U0STAT0)                       |

| Table 66. | UART Status 1 Register (U0STAT1)                       |

| Table 67. | UART Transmit Data Register (U0TXD)                    |

| Table 68. | UART Receive Data Register (U0RXD)                     |

| Table 69. | UART Address Compare Register (U0ADDR)                 |

| Table 70. | UART Baud Rate High Byte Register (U0BRH)11            |

| Table 71. | UART Baud Rate Low Byte Register (U0BRL)               |

| Table 72. | UART Baud Rates                                        |

| Table 73. | ADC Control Register 0 (ADCCTL0)                       |

| Table 74. | ADC Control/Status Register 1 (ADCCTL1)                |

| Table 75. | ADC Data High Byte Register (ADCD_H)                   |

| Table 76. | ADC Data Low Byte Register (ADCD_L)                    |

| Table 77. | Comparator Control Register (CMP0)                     |

| Table 78. | Z8 Encore! XP F082A Series Flash Memory Configurations |

| Table 79. | Flash Code Protection Using the Flash Option Bits      |

| Table 80. | Flash Status Register (FSTAT)                          |

| Table 81. | Flash Control Register (FCTL)                          |

| Table 82. | Flash Page Select Register (FPS)                       |

| Table 83. | Flash Sector Protect Register (FPROT)                  |

| Table 84. | Flash Frequency High Byte Register (FFREQH)            |

| Table 85. | Flash Frequency Low Byte Register (FFREQL)             |

| Table 86. | Trim Bit Address Register (TRMADR)                     |

| Table 87. | Trim Bit Data Register (TRMDR)                         |

| Table 88. | Flash Option Bits at Program Memory Address 0000H 16   |

# Z8 Encore! XP<sup>®</sup> F082A Series | Product Specification

7

warning signal. The  $\overline{RESET}$  pin is bidirectional, that is, it functions as reset source and as a reset indicator.

Table 27. Port A-D Alternate Function Set 1 Subregisters (PxAFS1)

| Bit     | 7         | 6                                                                                     | 5      | 4      | 3      | 2      | 1      | 0      |

|---------|-----------|---------------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|

| Field   | PAFS17    | PAFS16                                                                                | PAFS15 | PAFS14 | PAFS13 | PAFS12 | PAFS11 | PAFS10 |

| RESET   | 0         | 0                                                                                     | 0      | 0      | 0      | 0      | 0      | 0      |

| R/W     | R/W       | R/W                                                                                   | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

| Address | If 07H ir | If 07H in Port A–D Address Register, accessible through the Port A–D Control Register |        |        |        |        |        |        |

| Bit      | Description                                                                      |

|----------|----------------------------------------------------------------------------------|

| [7:0]    | Port Alternate Function Set 1                                                    |

| PAFSx    | 0 = Port Alternate Function selected, as defined in Tables 15 and 16 on page 43. |

|          | 1 = Port Alternate Function selected, as defined in Tables 15 and 16 on page 43. |

| Note: vi | indicates the specific GPIO port pin number (7–0)                                |

#### Port A-D Alternate Function Set 2 Subregisters

The Port A–D Alternate Function Set 2 Subregister, shown in Table 28, is accessed through the Port A–D Control Register by writing 08H to the Port A–D Address Register. The Alternate Function Set 2 subregisters selects the alternate function available at a port pin. Alternate Functions selected by setting or clearing bits of this register is defined in Table 16 on page 43.

Note: Alternate function selection on the port pins must also be enabled. See the <u>Port A–D Alternate Function Subregisters</u> section on page 47 for details.

Table 28. Port A–D Alternate Function Set 2 Subregisters (PxAFS2)

| Bit     | 7         | 6                                                                  | 5           | 4             | 3            | 2            | 1            | 0        |

|---------|-----------|--------------------------------------------------------------------|-------------|---------------|--------------|--------------|--------------|----------|

| Field   | PAFS27    | PAFS26                                                             | PAFS25      | PAFS24        | PAFS23       | PAFS22       | PAFS21       | PAFS20   |

| RESET   |           | 00H (all ports of 20/28 pin devices); 04H (Port A of 8-pin device) |             |               |              |              |              |          |

| R/W     | R/W       | R/W                                                                | R/W         | R/W           | R/W          | R/W          | R/W          | R/W      |

| Address | If 08H ir | Port A–D A                                                         | Address Reg | jister, acces | sible throug | h the Port A | –D Control F | Register |

| Bit        | Description                                                   |

|------------|---------------------------------------------------------------|

| [7]        | Port Alternate Function Set 2                                 |

| PAFS2x     | 0 = Port Alternate Function selected, as defined in Table 16. |

|            | 1 = Port Alternate Function selected, as defined in Table 16. |

| Note: x in | ndicates the specific GPIO port pin number (7–0).             |

The PWM period is represented by the following equation:

PWM Period (s) =

$$\frac{\text{Reload Value} \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, use the ONE-SHOT Mode equation to determine the first PWM time-out period.

If TPOL is set to 0, the ratio of the PWM output High time to the total period is represented by:

PWM Output High Time Ratio (%) =

$$\frac{\text{Reload Value} - \text{PWM Value}}{\text{Reload Value}} \times 100$$

If TPOL is set to 1, the ratio of the PWM output High time to the total period is represented by:

PWM Output High Time Ratio (%) =

$$\frac{PWM \text{ Value}}{\text{Reload Value}} \times 100$$

#### **PWM DUAL OUTPUT Mode**

In PWM DUAL OUTPUT Mode, the timer outputs a Pulse-Width Modulated (PWM) output signal pair (basic PWM signal and its complement) through two GPIO port pins. The timer input is the system clock. The timer first counts up to the 16-bit PWM match value stored in the Timer PWM High and Low Byte registers. When the timer count value matches the PWM value, the Timer Output toggles. The timer continues counting until it reaches the reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

If the TPOL bit in the Timer Control Register is set to 1, the Timer Output signal begins as a High (1) and transitions to a Low (0) when the timer value matches the PWM value. The Timer Output signal returns to a High (1) after the timer reaches the reload value and is reset to 0001H.

If the TPOL bit in the Timer Control Register is set to 0, the Timer Output signal begins as a Low (0) and transitions to a High (1) when the timer value matches the PWM value. The Timer Output signal returns to a Low (0) after the timer reaches the reload value and is reset to 0001H.

The timer also generates a second PWM output signal Timer Output Complement. The Timer Output Complement is the complement of the Timer Output PWM signal. A programmable deadband delay can be configured to time delay (0 to 128 system clock cycles) PWM output transitions on these two pins from a low to a high (inactive to active). This

Rate Generator to function as an additional counter if the UART functionality is not employed.

#### **UART Baud Rate Generator**

The UART Baud Rate Generator creates a lower frequency baud rate clock for data transmission. The input to the Baud Rate Generator is the system clock. The UART Baud Rate High and Low Byte registers combine to create a 16-bit baud rate divisor value (BRG[15:0]) that sets the data transmission rate (baud rate) of the UART. The UART data rate is calculated using the following equation:

UART Data Rate (bits/s) =

$$\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$$

When the UART is disabled, the Baud Rate Generator functions as a basic 16-bit timer with an interrupt upon time-out. Observe the following steps to configure the Baud Rate Generator as a timer with an interrupt upon time-out:

- 1. Disable the UART by clearing the REN and TEN bits in the UART Control 0 Register to 0

- 2. Load the acceptable 16-bit count value into the UART Baud Rate High and Low Byte registers.

- 3. Enable the Baud Rate Generator timer function and associated interrupt by setting the BRGCTL bit in the UART Control 1 Register to 1.

When configured as a general purpose timer, the interrupt interval is calculated using the following equation:

Interrupt Interval(s) = System Clock Period (s) × BRG[15:0]

### **UART Control Register Definitions**

The UART Control registers support the UART and the associated Infrared Encoder/Decoders. For more information about infrared operation, see the <u>Infrared Encoder/Decoder</u> chapter on page 120.

## **UART Control 0 and Control 1 Registers**

The UART Control 0 (UxCTL0) and Control 1 (UxCTL1) registers, shown in Tables 63 and 64, configure the properties of the UART's transmit and receive operations. The UART Control registers must not be written while the UART is enabled.

Table 64. UART Control 1 Register (U0CTL1)

| Bit     | 7       | 6    | 5       | 4    | 3     | 2      | 1      | 0    |

|---------|---------|------|---------|------|-------|--------|--------|------|

| Field   | MPMD[1] | MPEN | MPMD[0] | MPBT | DEPOL | BRGCTL | RDAIRQ | IREN |

| RESET   | 0       | 0    | 0       | 0    | 0     | 0      | 0      | 0    |

| R/W     | R/W     | R/W  | R/W     | R/W  | R/W   | R/W    | R/W    | R/W  |

| Address | F43H    |      |         |      |       |        |        |      |

| Bit                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7,5]<br>MPMD[1,0] | If MULTIPROCESSOR Mode  If MULTIPROCESSOR (9-bit) Mode is enabled:  00 = The UART generates an interrupt request on all received bytes (data and address).  01 = The UART generates an interrupt request only on received address bytes.  10 = The UART generates an interrupt request when a received address byte matches the value stored in the Address Compare Register and on all successive data bytes until an address mismatch occurs.  11 = The UART generates an interrupt request on all received data bytes for which the most recent address byte matched the value in the Address Compare Register. |

| [6]<br>MPEN        | MULTIPROCESSOR (9-bit) Enable This bit is used to enable MULTIPROCESSOR (9-bit) Mode. 0 = Disable MULTIPROCESSOR (9-bit) Mode. 1 = Enable MULTIPROCESSOR (9-bit) Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| [4]<br>MPBT        | Multiprocessor Bit Transmit  This bit is applicable only when MULTIPROCESSOR (9-bit) Mode is enabled. The 9th bit is used by the receiving device to determine if the data byte contains address or data information.  0 = Send a 0 in the multiprocessor bit location of the data stream (data byte).  1 = Send a 1 in the multiprocessor bit location of the data stream (address byte).                                                                                                                                                                                                                         |

| [3]<br>DEPOL       | Driver Enable Polarity 0 = DE signal is Active High. 1 = DE signal is Active Low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

Table 67. UART Transmit Data Register (U0TXD)

| Bit         | 7          | 6 | 5 | 4  | 3  | 2 | 1 | 0 |

|-------------|------------|---|---|----|----|---|---|---|

| Field       |            |   |   | T  | (D |   |   |   |

| RESET       | Χ          | Х | Χ | Х  | Х  | Х | Х | Х |

| R/W         | W          | W | W | W  | W  | W | W | W |

| Address     |            |   |   | F4 | 0H |   |   |   |

| Note: X = U | Jndefined. |   |   |    |    |   |   |   |

| Bit   | Description                                                        |

|-------|--------------------------------------------------------------------|

| [7:0] | Transmit Data                                                      |

| TXD   | UART transmitter data byte to be shifted out through the TXDx pin. |

### **UART Receive Data Register**

Data bytes received through the RXDx pin are stored in the UART Receive Data (UxRXD) Register, shown in Table 68. The read-only UART Receive Data Register shares a Register File address with the Write-only UART Transmit Data Register.

Table 68. UART Receive Data Register (U0RXD)

| Bit                  | 7    | 6 | 5 | 4  | 3  | 2 | 1 | 0 |

|----------------------|------|---|---|----|----|---|---|---|

| Field                |      |   |   | R) | (D |   |   |   |

| RESET                | Χ    | Χ | Х | Χ  | Χ  | Х | Х | Х |

| R/W                  | R    | R | R | R  | R  | R | R | R |

| Address              | F40H |   |   |    |    |   |   |   |

| Note: X = Undefined. |      |   |   |    |    |   |   |   |

| Bit   | Description                                |

|-------|--------------------------------------------|

| [7:0] | Receive Data                               |

| RXD   | UART receiver data byte from the RXDx pin. |

### **UART Address Compare Register**

The UART Address Compare (UxADDR) Register stores the multi-node network address of the UART (see Table 69). When the MPMD[1] bit of UART Control Register 0 is set, all incoming address bytes are compared to the value stored in the Address Compare Register. Receive interrupts and RDA assertions only occur in the event of a match.

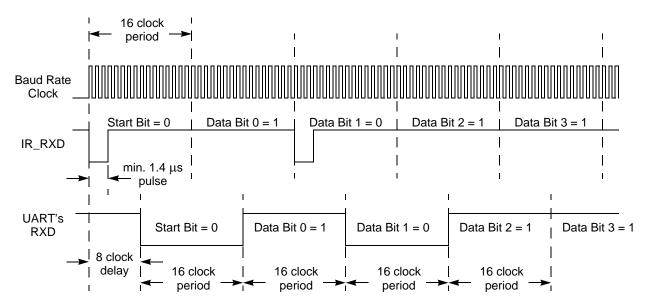

#### **Receiving IrDA Data**

Data received from the infrared transceiver using the IR\_RXD signal through the RXD pin is decoded by the infrared endec and passed to the UART. The UART's baud rate clock is used by the infrared endec to generate the demodulated signal (RXD) that drives the UART. Each UART/Infrared data bit is 16-clocks wide. Figure 18 displays data reception. When the infrared endec is enabled, the UART's RXD signal is internal to the Z8 Encore! XP F082A Series products while the IR\_RXD signal is received through the RXD pin.

Figure 18. IrDA Data Reception

#### **Infrared Data Reception**

**Caution:** The system clock frequency must be at least 1.0MHz to ensure proper reception of the 1.4µs minimum width pulses allowed by the IrDA standard.

#### **Endec Receiver Synchronization**

The IrDA receiver uses a local baud rate clock counter (0 to 15 clock periods) to generate an input stream for the UART and to create a sampling window for detection of incoming pulses. The generated UART input (UART RXD) is delayed by 8 baud rate clock periods with respect to the incoming IrDA data stream. When a falling edge in the input data stream is detected, the Endec counter is reset. When the count reaches a value of 8, the UART RXD value is updated to reflect the value of the decoded data. When the count reaches 12 baud clock periods, the sampling window for the next incoming pulse opens.

These serial numbers are stored in the Flash information page and are unaffected by mass erasure of the device's Flash memory. See the Reading the Flash Information Page section below and the Serialization Data section on page 173 for more details.

#### Randomized Lot Identification Bits

As an optional feature, Zilog is able to provide a factory-programmed random lot identifier. With this feature, all devices in a given production lot are programmed with the same random number. This random number is uniquely regenerated for each successive production lot and is not likely to be repeated.

The randomized lot identifier is a 32 byte binary value, stored in the Flash information page and is unaffected by mass erasure of the device's Flash memory. See Reading the Flash Information Page, below, and the <u>Randomized Lot Identifier section on page 174</u> for more details.

#### Reading the Flash Information Page

The following code example shows how to read data from the Flash information area.

```

; get value at info address 60 (FE60h)

ldx FPS, #%80 ; enable access to flash info page

ld R0, #%FE

ld R1, #%60

ldc R2, @RR0 ; R2 now contains the calibration value

```

## **Flash Option Bit Control Register Definitions**

This section briefly describes the features of the Trim Bit Address and Data registers.

## **Trim Bit Address Register**

The Trim Bit Address (TRMADR) Register contains the target address for an access to the trim option bits (Table 86).

Table 86. Trim Bit Address Register (TRMADR)

| Bit     | 7                                     | 6    | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

|---------|---------------------------------------|------|-----|-----|-----|-----|-----|-----|--|--|--|

| Field   | TRMADR: Trim Bit Address (00H to 1FH) |      |     |     |     |     |     |     |  |  |  |

| RESET   | 0                                     | 0    | 0   | 0   | 0   | 0   | 0   | 0   |  |  |  |

| R/W     | R/W                                   | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |

| Address |                                       | FF6H |     |     |     |     |     |     |  |  |  |

**Table 97. ADC Calibration Data Location (Continued)**

| Info Page | Memory  |                         |                          |                |

|-----------|---------|-------------------------|--------------------------|----------------|

| Address   | Address | Compensation Usage      | ADC Mode                 | Reference Type |

| 12        | FE12    | Positive Gain High Byte | Differential Unbuffered  | Internal 2.0 V |

| 13        | FE13    | Positive Gain Low Byte  | Differential Unbuffered  | Internal 2.0 V |

| 30        | FE30    | Negative Gain High Byte | Differential Unbuffered  | Internal 2.0 V |

| 31        | FE31    | Negative Gain Low Byte  | Differential Unbuffered  | Internal 2.0 V |

| 72        | FE72    | Offset                  | Differential Unbuffered  | Internal 1.0 V |

| 14        | FE14    | Positive Gain High Byte | Differential Unbuffered  | Internal 1.0 V |

| 15        | FE15    | Positive Gain Low Byte  | Differential Unbuffered  | Internal 1.0 V |

| 32        | FE32    | Negative Gain High Byte | Differential Unbuffered  | Internal 1.0 V |

| 33        | FE33    | Negative Gain Low Byte  | Differential Unbuffered  | Internal 1.0 V |

| 75        | FE75    | Offset                  | Differential Unbuffered  | External 2.0 V |

| 16        | FE16    | Positive Gain High Byte | Differential Unbuffered  | External 2.0 V |

| 17        | FE17    | Positive Gain Low Byte  | Differential Unbuffered  | External 2.0 V |

| 34        | FE34    | Negative Gain High Byte | Differential Unbuffered  | External 2.0 V |

| 35        | FE35    | Negative Gain Low Byte  | Differential Unbuffered  | External 2.0 V |

| 78        | FE78    | Offset                  | Differential 1x Buffered | Internal 2.0 V |

| 18        | FE18    | Positive Gain High Byte | Differential 1x Buffered | Internal 2.0 V |

| 19        | FE19    | Positive Gain Low Byte  | Differential 1x Buffered | Internal 2.0 V |

| 36        | FE36    | Negative Gain High Byte | Differential 1x Buffered | Internal 2.0 V |

| 37        | FE37    | Negative Gain Low Byte  | Differential 1x Buffered | Internal 2.0 V |

| 7B        | FE7B    | Offset                  | Differential 1x Buffered | External 2.0 V |

| 1A        | FE1A    | Positive Gain High Byte | Differential 1x Buffered | External 2.0 V |

| 1B        | FE1B    | Positive Gain Low Byte  | Differential 1x Buffered | External 2.0 V |

| 38        | FE38    | Negative Gain High Byte | Differential 1x Buffered | External 2.0 V |

| 39        | FE39    | Negative Gain Low Byte  | Differential 1x Buffered | External 2.0 V |

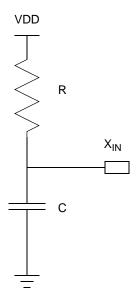

## Oscillator Operation with an External RC Network

Figure 28 displays a recommended configuration for connection with an external resistor-capacitor (RC) network.

Figure 28. Connecting the On-Chip Oscillator to an External RC Network

An external resistance value of  $45\,\mathrm{k}\Omega$  is recommended for oscillator operation with an external RC network. The minimum resistance value to ensure operation is  $40\,\mathrm{k}\Omega$ . The typical oscillator frequency can be estimated from the values of the resistor (R in  $\mathrm{k}\Omega$ ) and capacitor (C in pF) elements using the following equation:

Oscillator Frequency (kHz) =

$$\frac{1 \times 10^6}{(0.4 \times R \times C) + (4 \times C)}$$

Figure 29 displays the typical (3.3 V and 25°C) oscillator frequency as a function of the capacitor (C, in pF) employed in the RC network assuming a 45 K $\Omega$  external resistor. For very small values of C, the parasitic capacitance of the oscillator  $X_{IN}$  pin and the printed circuit board must be included in the estimation of the oscillator frequency.

It is possible to operate the RC oscillator using only the parasitic capacitance of the package and printed circuit board. To minimize sensitivity to external parasitics, external capacitance values in excess of 20pF are recommended.

#### **Assembly Language Source Program Example**

JP START ; Everything after the semicolon is a comment.

START: ; A label called 'START'. The first instruction (JP START) in this

; example causes program execution to jump to the point within the

; program where the START label occurs.

LD R4, R7; A Load (LD) instruction with two operands. The first operand,

; Working Register R4, is the destination. The second operand, ; Working Register R7, is the source. The contents of R7 is

; written into R4.

LD 234H, #%01; Another Load (LD) instruction with two operands.

; The first operand, Extended Mode Register Address  $234 \mathrm{H}$ , ; identifies the destination. The second operand, Immediate Data ; value  $01 \mathrm{H}$ , is the source. The value  $01 \mathrm{H}$  is written into the

; Register at address 234H.

## **Assembly Language Syntax**

For proper instruction execution, eZ8 CPU assembly language syntax requires that the operands be written as 'destination, source'. After assembly, the object code usually has the operands in the order 'source, destination', but ordering is opcode-dependent. The following instruction examples illustrate the format of some basic assembly instructions and the resulting object code produced by the assembler. This binary format must be followed if manual program coding is preferred or if you intend to implement your own assembler.

**Example 1.** If the contents of registers 43H and 08H are added and the result is stored in 43H, the assembly syntax and resulting object code is:

Table 116. Assembly Language Syntax Example 1

| Assembly Language Code | ADD | 43H, | H80 | (ADD dst, src) |

|------------------------|-----|------|-----|----------------|

| Object Code            | 04  | 08   | 43  | (OPC src, dst) |

**Example 2.** In general, when an instruction format requires an 8-bit register address, that address can specify any register location in the range 0–255 or, using Escaped Mode Addressing, a Working Register R0–R15. If the contents of Register 43H and Working Register R8 are added and the result is stored in 43H, the assembly syntax and resulting object code is:

Table 117. Assembly Language Syntax Example 2

| Assembly Language Code | ADD | 43H, | R8 | (ADD dst, src) |

|------------------------|-----|------|----|----------------|

| Object Code            | 04  | E8   | 43 | (OPC src, dst) |

**Table 118. Notational Shorthand (Continued)**

| Notation | Description    | Operand | Range                                                                                                                     |

|----------|----------------|---------|---------------------------------------------------------------------------------------------------------------------------|

| Vector   | Vector address | Vector  | Vector represents a number in the range of 00H to FFH.                                                                    |

| X        | Indexed        | #Index  | The register or register pair to be indexed is off-<br>set by the signed Index value (#Index) in a +127<br>to -128 range. |

Table 119 lists additional symbols that are used throughout the Instruction Summary and Instruction Set Description sections.

**Table 119. Additional Symbols**

| Definition                |

|---------------------------|

| Destination Operand       |

| Source Operand            |

| Indirect Address Prefix   |

| Stack Pointer             |

| Program Counter           |

| Flags Register            |

| Register Pointer          |

| Immediate Operand Prefix  |

| Binary Number Suffix      |

| Hexadecimal Number Prefix |

| Hexadecimal Number Suffix |

|                           |

Assignment of a value is indicated by an arrow, as shown in the following example.

$$dst \leftarrow dst + src$$

This example indicates that the source data is added to the destination data; the result is stored in the destination location.

## **eZ8 CPU Instruction Classes**

eZ8 CPU instructions can be divided functionally into the following groups:

- Arithmetic

- Bit Manipulation

## **eZ8 CPU Instruction Summary**

Table 128 summarizes the eZ8 CPU instructions. The table identifies the addressing modes employed by the instruction, the effect upon the Flags Register, the number of CPU clock cycles required for the instruction fetch and the number of CPU clock cycles required for the instruction execution.

Table 128. eZ8 CPU Instruction Summary

| Assembly      |                                | Address<br>Mode |     | _ Opcode(s) |   |   | Fla     | ags | Fetch<br>Cycle | Instr.<br>Cycle |   |   |

|---------------|--------------------------------|-----------------|-----|-------------|---|---|---------|-----|----------------|-----------------|---|---|

| Mnemonic      | Symbolic Operation             | dst             | src |             |   | Z | S V D H |     |                | Н               | S | S |

| ADC dst, src  | dst ← dst + src + C            | r               | r   | 12          | * | * | *       | *   | 0              | *               | 2 | 3 |

|               |                                | r               | lr  | 13          |   |   |         |     |                |                 | 2 | 4 |

|               |                                | R               | R   | 14          |   |   |         |     |                |                 | 3 | 3 |

|               |                                | R               | IR  | 15          |   |   |         |     |                |                 | 3 | 4 |

|               |                                | R               | IM  | 16          |   |   |         |     |                |                 | 3 | 3 |

|               |                                | IR              | IM  | 17          |   |   |         |     |                |                 | 3 | 4 |

| ADCX dst, src | $dst \leftarrow dst + src + C$ | ER              | ER  | 18          | * | * | *       | *   | 0              | *               | 4 | 3 |

|               |                                | ER              | IM  | 19          |   |   |         |     |                |                 | 4 | 3 |

| ADD dst, src  | dst ← dst + src                | r               | r   | 02          | * | * | *       | *   | 0              | *               | 2 | 3 |

|               |                                | r               | lr  | 03          |   |   |         |     |                |                 | 2 | 4 |

|               |                                | R               | R   | 04          |   |   |         |     |                |                 | 3 | 3 |

|               |                                | R               | IR  | 05          |   |   |         |     |                |                 | 3 | 4 |

|               |                                | R               | IM  | 06          |   |   |         |     |                |                 | 3 | 3 |

|               |                                | IR              | IM  | 07          |   |   |         |     |                |                 | 3 | 4 |

| ADDX dst, src | dst ← dst + src                | ER              | ER  | 08          | * | * | *       | *   | 0              | *               | 4 | 3 |

|               |                                | ER              | IM  | 09          |   |   |         |     |                |                 | 4 | 3 |

Note: Flags Notation:

<sup>\* =</sup> Value is a function of the result of the operation.

<sup>-</sup> = Unaffected.

X = Undefined.

<sup>0 =</sup> Reset to 0.

<sup>1 =</sup> Set to 1.

Table 148. Z8 Encore! XP F082A Series Ordering Matrix

| Part Number         | Flash     | RAM     | NVDS    | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | <b>Temperature Sensor</b> | Description         |

|---------------------|-----------|---------|---------|-----------|------------|---------------------|---------------------|----------------|------------|---------------------------|---------------------|

| Z8 Encore! XP F082A | Series    | with 4  | KB Flas | h, 10     | -Bit /     | Analo               | og-to               | -Digi          | tal Co     | onve                      | erter               |

| Standard Temperatur | re: 0°C t | :o 70°C | ;       |           |            |                     |                     |                |            |                           |                     |

| Z8F042APB020SG      | 4 KB      | 1KB     | 128 B   | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                         | PDIP 8-pin package  |

| Z8F042AQB020SG      | 4 KB      | 1KB     | 128 B   | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                         | QFN 8-pin package   |

| Z8F042ASB020SG      | 4 KB      | 1KB     | 128 B   | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                         | SOIC 8-pin package  |

| Z8F042ASH020SG      | 4 KB      | 1KB     | 128 B   | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                         | SOIC 20-pin package |

| Z8F042AHH020SG      | 4 KB      | 1KB     | 128 B   | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                         | SSOP 20-pin package |

| Z8F042APH020SG      | 4 KB      | 1KB     | 128 B   | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                         | PDIP 20-pin package |

| Z8F042ASJ020SG      | 4 KB      | 1KB     | 128 B   | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                         | SOIC 28-pin package |

| Z8F042AHJ020SG      | 4 KB      | 1KB     | 128 B   | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                         | SSOP 28-pin package |

| Z8F042APJ020SG      | 4 KB      | 1KB     | 128 B   | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                         | PDIP 28-pin package |

| Extended Temperatu  | re: –40°  | C to 10 | )5°C    |           |            |                     |                     |                |            |                           |                     |

| Z8F042APB020EG      | 4 KB      | 1KB     | 128 B   | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                         | PDIP 8-pin package  |

| Z8F042AQB020EG      | 4 KB      | 1KB     | 128 B   | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                         | QFN 8-pin package   |

| Z8F042ASB020EG      | 4 KB      | 1KB     | 128 B   | 6         | 14         | 2                   | 4                   | 1              | 1          | 1                         | SOIC 8-pin package  |

| Z8F042ASH020EG      | 4 KB      | 1KB     | 128 B   | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                         | SOIC 20-pin package |

| Z8F042AHH020EG      | 4 KB      | 1KB     | 128 B   | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                         | SSOP 20-pin package |

| Z8F042APH020EG      | 4 KB      | 1KB     | 128 B   | 17        | 20         | 2                   | 7                   | 1              | 1          | 1                         | PDIP 20-pin package |

| Z8F042ASJ020EG      | 4 KB      | 1KB     | 128 B   | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                         | SOIC 28-pin package |

| Z8F042AHJ020EG      | 4 KB      | 1KB     | 128 B   | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                         | SSOP 28-pin package |

| Z8F042APJ020EG      | 4 KB      | 1KB     | 128 B   | 23        | 20         | 2                   | 8                   | 1              | 1          | 1                         | PDIP 28-pin package |

Table 148. Z8 Encore! XP F082A Series Ordering Matrix

| Part Number         | Flash    | RAM      | NVDS    | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | <b>Temperature Sensor</b> | Description         |

|---------------------|----------|----------|---------|-----------|------------|---------------------|---------------------|----------------|------------|---------------------------|---------------------|

| Z8 Encore! XP F082A | A Series | with 2   | KB Flas | sh        |            |                     |                     |                |            |                           |                     |

| Standard Temperatu  | re: 0°C  | to 70°C  |         |           |            |                     |                     |                |            |                           |                     |

| Z8F021APB020SG      | 2 KB     | 512 B    | 64 B    | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                         | PDIP 8-pin package  |

| Z8F021AQB020SG      | 2 KB     | 512 B    | 64 B    | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                         | QFN 8-pin package   |

| Z8F021ASB020SG      | 2 KB     | 512 B    | 64 B    | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                         | SOIC 8-pin package  |

| Z8F021ASH020SG      | 2 KB     | 512 B    | 64 B    | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                         | SOIC 20-pin package |

| Z8F021AHH020SG      | 2 KB     | 512 B    | 64 B    | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                         | SSOP 20-pin package |

| Z8F021APH020SG      | 2 KB     | 512 B    | 64 B    | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                         | PDIP 20-pin package |

| Z8F021ASJ020SG      | 2 KB     | 512 B    | 64 B    | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                         | SOIC 28-pin package |

| Z8F021AHJ020SG      | 2 KB     | 512 B    | 64 B    | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                         | SSOP 28-pin package |

| Z8F021APJ020SG      | 2 KB     | 512 B    | 64 B    | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                         | PDIP 28-pin package |

| Extended Temperatu  | re: –40° | °C to 10 | 5°C     |           |            |                     |                     |                |            |                           |                     |

| Z8F021APB020EG      | 2 KB     | 512 B    | 64 B    | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                         | PDIP 8-pin package  |

| Z8F021AQB020EG      | 2 KB     | 512 B    | 64 B    | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                         | QFN 8-pin package   |

| Z8F021ASB020EG      | 2 KB     | 512 B    | 64 B    | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                         | SOIC 8-pin package  |

| Z8F021ASH020EG      | 2 KB     | 512 B    | 64 B    | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                         | SOIC 20-pin package |

| Z8F021AHH020EG      | 2 KB     | 512 B    | 64 B    | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                         | SSOP 20-pin package |

| Z8F021APH020EG      | 2 KB     | 512 B    | 64 B    | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                         | PDIP 20-pin package |

| Z8F021ASJ020EG      | 2 KB     | 512 B    | 64 B    | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                         | SOIC 28-pin package |

| Z8F021AHJ020EG      | 2 KB     | 512 B    | 64 B    | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                         | SSOP 28-pin package |

| Z8F021APJ020EG      | 2 KB     | 512 B    | 64 B    | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                         | PDIP 28-pin package |

## Index

| Numerics                                                                                                                                                                                                                                                      | b 206<br>baud rate generator, UART 110                                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10-bit ADC 6                                                                                                                                                                                                                                                  | BCLR 209                                                                                                                                                                                             |

| A absolute maximum ratings 226 AC characteristics 232 ADC 208 architecture 124 block diagram 125 continuous conversion 127 control register 134, 135 control register definitions 133 data high byte register 136                                             | binary number suffix 207 BIT 209 bit 206 clear 209 manipulation instructions 209 set 209 set or clear 209 swap 209 test and jump 211 test and jump if non-zero 211 bit jump and test if non-zero 211 |

| data low bits register 137 electrical characteristics and timing 236 operation 125 single-shot conversion 126 ADCCTL register 134, 135 ADCDH register 136 ADCDL register 137 ADCX 208 ADD 208 add - extended addressing 208 add with carry 208                | bit jump and test if hon-zero 211 bit swap 211 block diagram 3 block transfer instructions 209 BRK 211 BSET 209 BSWAP 209, 211 BTJ 211 BTJNZ 211 BTJZ 211                                            |

| add with carry - extended addressing 208 additional symbols 207 address space 15 ADDX 208 analog signals 11 analog-to-digital converter (ADC) 124 AND 210 ANDX 210 arithmetic instructions 208 assembly language programming 204 assembly language syntax 205 | CALL procedure 211 CAPTURE mode 87, 88 CAPTURE/COMPARE mode 88 cc 206 CCF 209 characteristics, electrical 226 clear 210 CLR 210 COM 210 compare 87 compare - extended addressing 208                 |

| <b>B</b> B 207                                                                                                                                                                                                                                                | COMPARE mode 87 compare with carry 208                                                                                                                                                               |

| LEA 210                                           | b 206                               |

|---------------------------------------------------|-------------------------------------|

| load 210                                          | cc 206                              |

| load constant 209                                 | DA 206                              |

| load constant to/from program memory 210          | ER 206                              |

| load constant with auto-increment addresses 210   | IM 206                              |

| load effective address 210                        | IR 206                              |

| load external data 210                            | Ir 206                              |

| load external data to/from data memory and auto-  | IRR 206                             |

| increment addresses 209                           | Irr 206                             |

| load external to/from data memory and auto-incre- | p 206                               |

| ment addresses 210                                | R 206                               |

| load using extended addressing 210                | r 206                               |

| logical AND 210                                   | RA 206                              |

| logical AND/extended addressing 210               | RR 206                              |

| logical exclusive OR 210                          | rr 206                              |

| logical exclusive OR/extended addressing 210      | vector 207                          |

| logical instructions 210                          | X 207                               |

| logical OR 210                                    | notational shorthand 206            |

|                                                   | notational shorthand 200            |

| logical OR/extended addressing 210                |                                     |

| low power modes 32                                | 0                                   |

|                                                   | _                                   |

| M                                                 | OCD                                 |

| •••                                               | architecture 180                    |

| master interrupt enable 57                        | auto-baud detector/generator 183    |

| memory                                            | baud rate limits 184                |

| data 17                                           | block diagram 180                   |

| program 15                                        | breakpoints 185                     |

| mode                                              | commands 186                        |

| CAPTURE 87, 88                                    | control register 191                |

| CAPTURE/COMPARE 88                                | data format 183                     |

| CONTINUOUS 87                                     | DBG pin to RS-232 Interface 181     |

| COUNTER 87                                        | debug mode 182                      |

| GATED 88                                          | debugger break 211                  |

| ONE-SHOT 87                                       | interface 181                       |

| PWM 87, 88                                        | serial errors 184                   |

| modes 87                                          | status register 192                 |

| MULT 208                                          | timing 242                          |

| multiply 208                                      | OCD commands                        |

| multiprocessor mode, UART 105                     | execute instruction (12H) 190       |

|                                                   | read data memory (0DH) 190          |

| NI.                                               | read OCD control register (05H) 188 |

| N                                                 | read OCD revision (00H) 187         |

| NOP (no operation) 209                            | read OCD status register (02H) 187  |

| notation                                          | read program counter (07H) 188      |

|                                                   |                                     |

#### Ζ

Z8 Encore! block diagram 3 features 1 part selection guide 2

## **Customer Support**

To share comments, get your technical questions answered, or report issues you may be experiencing with our products, please visit Zilog's Technical Support page at <a href="http://support.zilog.com">http://support.zilog.com</a>.

To learn more about this product, find additional documentation, or to discover other facets about Zilog product offerings, please visit the Zilog Knowledge Base at <a href="http://zilog.com/forum">http://zilog.com/forum</a>. <a href="mailto:zilog.com/forum">zilog.com/forum</a>.

This publication is subject to replacement by a later edition. To determine whether a later edition exists, please visit the Zilog website at <a href="http://www.zilog.com">http://www.zilog.com</a>.

PS022827-1212 PRELIMINARY Customer Support