Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT           |

| Number of I/O              | 25                                                        |

| Program Memory Size        | 1KB (1K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | 16 × 8                                                    |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 28-DIP (0.600", 15.24mm)                                  |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f011apj020eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### xi

# List of Figures

| Figure 1.  | Z8 Encore! XP F082A Series Block Diagram 3                                      |

|------------|---------------------------------------------------------------------------------|

| Figure 2.  | Z8F08xA, Z8F04xA, Z8F02xA and Z8F01xA in 8-Pin SOIC, QFN/MLF-S, or PDIP Package |

| Figure 3.  | Z8F08xA, Z8F04xA, Z8F02xA and Z8F01xA in 20-Pin SOIC, SSOP or PDIP Package      |

| Figure 4.  | Z8F08xA, Z8F04xA, Z8F02xA and Z8F01xA in 28-Pin SOIC, SSOP or PDIP Package      |

| Figure 5.  | Power-On Reset Operation                                                        |

| Figure 6.  | Voltage Brown-Out Reset Operation                                               |

| Figure 7.  | GPIO Port Pin Block Diagram                                                     |

| Figure 8.  | Interrupt Controller Block Diagram                                              |

| Figure 9.  | Timer Block Diagram                                                             |

| Figure 10. | UART Block Diagram 100                                                          |

| Figure 11. | UART Asynchronous Data Format without Parity                                    |

| Figure 12. | UART Asynchronous Data Format with Parity 101                                   |

| Figure 13. | UART Asynchronous MULTIPROCESSOR Mode Data Format 105                           |

| Figure 14. | UART Driver Enable Signal Timing (shown with 1 Stop Bit and Parity) 107         |

| Figure 15. | UART Receiver Interrupt Service Routine Flow                                    |

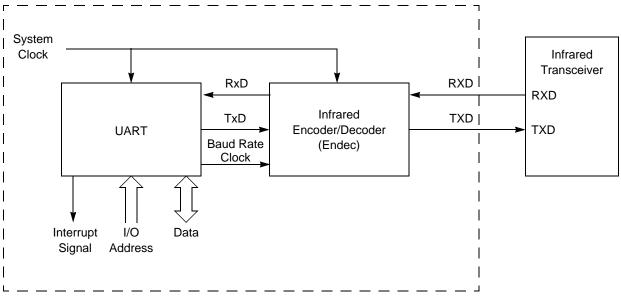

| Figure 16. | Infrared Data Communication System Block Diagram                                |

| Figure 17. | Infrared Data Transmission                                                      |

| Figure 18. | IrDA Data Reception 122                                                         |

| Figure 19. | Analog-to-Digital Converter Block Diagram                                       |

| Figure 20. | Comparator Block Diagram 140                                                    |

| Figure 21. | Flash Memory Arrangement 147                                                    |

| Figure 22. | Flash Controller Operation Flow Chart 148                                       |

| Figure 23. | On-Chip Debugger Block Diagram 180                                              |

| Figure 24. | Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface;<br>#1 of 2 |

# Reset, Stop Mode Recovery and Low Voltage Detection

The Reset Controller within the Z8 Encore! XP F082A Series controls Reset and Stop Mode Recovery operation and provides indication of low supply voltage conditions. In typical operation, the following events cause a Reset:

- Power-On Reset (POR)

- Voltage Brown-Out (VBO)

- Watchdog Timer time-out (when configured by the WDT\_RES Flash option bit to initiate a reset)

- External **RESET** pin assertion (when the alternate **RESET** function is enabled by the GPIO Register)

- On-chip debugger initiated Reset (OCDCTL[0] set to 1)

When the device is in STOP Mode, a Stop Mode Recovery is initiated by either of the following occurrences:

- Watchdog Timer time-out

- GPIO Port input pin transition on an enabled Stop Mode Recovery source

The low voltage detection circuitry on the device (available on the 8-pin product versions only) performs the following functions:

- Generates the VBO reset when the supply voltage drops below a minimum safe level.

- Generates an interrupt when the supply voltage drops below a user-defined level (8-pin devices only).

# **Reset Types**

The Z8 Encore! XP F082A Series provides several different types of Reset operation. Stop Mode Recovery is considered as a form of Reset. Table 8 lists the types of Reset and their operating characteristics. The System Reset is longer if the external crystal oscillator is enabled by the Flash option bits, allowing additional time for oscillator start-up.

tor address. Following Stop Mode Recovery, the STOP bit in the Reset Status (RSTSTAT) Register is set to 1. Table 10 lists the Stop Mode Recovery sources and resulting actions. The text following provides more detailed information about each of the Stop Mode Recovery sources.

| Operating Mode | Stop Mode Recovery Source                                                   | Action                                                               |

|----------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------|

| STOP Mode      | Watchdog Timer time-out when configured for Reset                           | Stop Mode Recovery                                                   |

|                | Watchdog Timer time-out when configured for interrupt                       | Stop Mode Recovery followed by interrupt (if interrupts are enabled) |

|                | Data transition on any GPIO port pin enabled as a Stop Mode Recovery source | Stop Mode Recovery                                                   |

|                | Assertion of external RESET Pin                                             | System Reset                                                         |

|                | Debug Pin driven Low                                                        | System Reset                                                         |

#### Table 10. Stop Mode Recovery Sources and Resulting Action

## Stop Mode Recovery Using Watchdog Timer Time-Out

If the Watchdog Timer times out during STOP Mode, the device undergoes a Stop Mode Recovery sequence. In the Reset Status (RSTSTAT) Register, the WDT and STOP bits are set to 1. If the Watchdog Timer is configured to generate an interrupt upon time-out and the Z8 Encore! XP F082A Series device is configured to respond to interrupts, the eZ8 CPU services the Watchdog Timer interrupt request following the normal Stop Mode Recovery sequence.

## Stop Mode Recovery Using a GPIO Port Pin Transition

Each of the GPIO port pins may be configured as a Stop Mode Recovery input source. On any GPIO pin enabled as a Stop Mode Recovery source, a change in the input pin value (from High to Low or from Low to High) initiates Stop Mode Recovery.

• Note: SMR pulses shorter than specified do not trigger a recovery (see <u>Table 135</u> on page 233). In this instance, the STOP bit in the Reset Status (RSTSTAT) Register is set to 1.

**Caution:** In STOP Mode, the GPIO Port Input Data registers (PxIN) are disabled. The Port Input Data registers record the Port transition only if the signal stays on the Port pin through the end of the Stop Mode Recovery delay. As a result, short pulses on the Port pin can initiate Stop Mode Recovery without being written to the Port Input Data Register or

| Bit           | Description (Continued)                                                  |

|---------------|--------------------------------------------------------------------------|

| [4]<br>U0RENL | UART 0 Receive Interrupt Request Enable Low Bit                          |

| [3]<br>U0TENL | UART 0 Transmit Interrupt Request Enable Low Bit                         |

| [2:1]         | <b>Reserved</b><br>These bits are reserved and must be programmed to 00. |

| [0]<br>ADCENL | ADC Interrupt Request Enable Low Bit                                     |

## **IRQ1 Enable High and Low Bit Registers**

Table 41 describes the priority control for IRQ1. The IRQ1 Enable High and Low Bit registers, shown in Tables 41 and 42, form a priority-encoded enabling for interrupts in the Interrupt Request 1 Register.

| IRQ1ENH[x]                           | IRQ1ENL[x] | Priority | Description |  |  |  |

|--------------------------------------|------------|----------|-------------|--|--|--|

| 0                                    | 0          | Disabled | Disabled    |  |  |  |

| 0                                    | 1          | Level 1  | Low         |  |  |  |

| 1                                    | 0          | Level 2  | Medium      |  |  |  |

| 1                                    | 1          | Level 3  | High        |  |  |  |

| Note: x indicates register bits 0–7. |            |          |             |  |  |  |

#### Table 41. IRQ1 Enable and Priority Encoding

| Bit     | 7       | 6       | 5      | 4      | 3             | 2      | 1      | 0      |  |

|---------|---------|---------|--------|--------|---------------|--------|--------|--------|--|

| Field   | PA7VENH | PA6CENH | PA5ENH | PA4ENH | <b>PA3ENH</b> | PA2ENH | PA1ENH | PA0ENH |  |

| RESET   | 0       | 0       | 0      | 0      | 0             | 0      | 0      | 0      |  |

| R/W     | R/W     | R/W     | R/W    | R/W    | R/W           | R/W    | R/W    | R/W    |  |

| Address |         | FC4H    |        |        |               |        |        |        |  |

| Bit             | Description                                                   |

|-----------------|---------------------------------------------------------------|

| [7]<br>PA7VENH  | Port A Bit[7] or LVD Interrupt Request Enable High Bit        |

| [6]<br>PA6CENH  | Port A Bit[7] or Comparator Interrupt Request Enable High Bit |

| [5:0]<br>PAxENH | Port A Bit[ <i>x</i> ] Interrupt Request Enable High Bit      |

See the <u>Shared Interrupt Select Register (IRQSS) Register</u> on page 68 for selection of either the LVD or the comparator as the interrupt source.

| Bit     | 7       | 6       | 5      | 4      | 3             | 2      | 1      | 0      |

|---------|---------|---------|--------|--------|---------------|--------|--------|--------|

| Field   | PA7VENL | PA6CENL | PA5ENL | PA4ENL | <b>PA3ENL</b> | PA2ENL | PA1ENL | PA0ENL |

| RESET   | 0       | 0       | 0      | 0      | 0             | 0      | 0      | 0      |

| R/W     | R/W     | R/W     | R/W    | R/W    | R/W           | R/W    | R/W    | R/W    |

| Address | FC5H    |         |        |        |               |        |        |        |

| Bit             | Description                                                  |

|-----------------|--------------------------------------------------------------|

| [7]<br>PA7VENL  | Port A Bit[7] or LVD Interrupt Request Enable Low Bit        |

| [6]<br>PA6CENL  | Port A Bit[6] or Comparator Interrupt Request Enable Low Bit |

| [5:0]<br>PAxENL | Port A Bit[x] Interrupt Request Enable Low Bit               |

## **IRQ2 Enable High and Low Bit Registers**

Table 44 describes the priority control for IRQ2. The IRQ2 Enable High and Low Bit registers, shown in Tables 44 and 45, form a priority-encoded enabling for interrupts in the Interrupt Request 2 Register.

# **Interrupt Control Register**

The Interrupt Control (IRQCTL) Register, shown in Table 49, contains the master enable bit for all interrupts.

| Bit     | 7                                                                                                   | 6                        | 5        | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|-----------------------------------------------------------------------------------------------------|--------------------------|----------|---|---|---|---|---|--|--|

| Field   | IRQE                                                                                                |                          | Reserved |   |   |   |   |   |  |  |

| RESET   | 0                                                                                                   | 0                        | 0        | 0 | 0 | 0 | 0 | 0 |  |  |

| R/W     | R/W                                                                                                 | R                        | R        | R | R | R | R | R |  |  |

| Address |                                                                                                     | FCFH                     |          |   |   |   |   |   |  |  |

| Bit     | Description                                                                                         |                          |          |   |   |   |   |   |  |  |

| [7]     | Interrupt R                                                                                         | Interrupt Request Enable |          |   |   |   |   |   |  |  |

| IRQE    | This bit is set to 1 by executing an EI (Enable Interrupts) or IRET (Interrupt Return) instruction, |                          |          |   |   |   |   |   |  |  |

#### Table 49. Interrupt Control Register (IRQCTL)

| ЫІ    | Description                                                                                                                                                                                                                                                                                                                                    |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]   | Interrupt Request Enable                                                                                                                                                                                                                                                                                                                       |

| IRQE  | This bit is set to 1 by executing an EI (Enable Interrupts) or IRET (Interrupt Return) instruction, or by a direct register write of a 1 to this bit. It is reset to 0 by executing a DI instruction, eZ8 CPU acknowledgement of an interrupt request, Reset or by a direct register write of a 0 to this bit.<br>0 = Interrupts are disabled. |

|       | 1 = Interrupts are enabled.                                                                                                                                                                                                                                                                                                                    |

| [6:0] | <b>Reserved</b><br>These bits are reserved and must be programmed to 0000000.                                                                                                                                                                                                                                                                  |

|       |                                                                                                                                                                                                                                                                                                                                                |

it is appropriate to have the Timer Output make a state change at a One-Shot time-out (rather than a single cycle pulse), first set the TPOL bit in the Timer Control Register to the start value before enabling ONE-SHOT Mode. After starting the timer, set TPOL to the opposite bit value.

Observe the following steps for configuring a timer for ONE-SHOT Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for ONE-SHOT Mode.

- Set the prescale value.

- Set the initial output level (High or Low) if using the Timer Output alternate function.

- 2. Write to the Timer High and Low Byte registers to set the starting count value.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 6. Write to the Timer Control Register to enable the timer and initiate counting.

In ONE-SHOT Mode, the system clock always provides the timer input. The timer period is computed via the following equation:

$ONE-SHOT \text{ Mode Time-Out Period } (s) = \frac{\text{Reload Value} - \text{Start Value} \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$

#### **CONTINUOUS Mode**

In CONTINUOUS Mode, the timer counts up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer Reload.

Observe the following steps for configuring a timer for CONTINUOUS Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CONTINUOUS Mode

enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer Reload.

Observe the following steps for configuring a timer for COUNTER Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer.

- Configure the timer for COUNTER Mode.

- Select either the rising edge or falling edge of the Timer Input signal for the count. This selection also sets the initial logic level (High or Low) for the Timer Output alternate function. However, the Timer Output function is not required to be enabled.

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This only affects the first pass in COUNTER Mode. After the first timer Reload in COUNTER Mode, counting always begins at the reset value of 0001H. In COUNTER Mode the Timer High and Low Byte registers must be written with the value 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 7. Write to the Timer Control Register to enable the timer.

In COUNTER Mode, the number of Timer Input transitions since the timer start is computed via the following equation:

COUNTER Mode Timer Input Transitions = Current Count Value-Start Value

#### **COMPARATOR COUNTER Mode**

In COMPARATOR COUNTER Mode, the timer counts input transitions from the analog comparator output. The TPOL bit in the Timer Control Register selects whether the count occurs on the rising edge or the falling edge of the comparator output signal. In COMPAR-ATOR COUNTER Mode, the prescaler is disabled.

# Timer 0–1 PWM High and Low Byte Registers

The Timer 0–1 PWM High and Low Byte (TxPWMH and TxPWML) registers, shown in Tables 56 and 57, control Pulse-Width Modulator (PWM) operations. These registers also store the Capture values for the CAPTURE and CAPTURE/COMPARE modes.

| Bit     | 7   | 6   | 5   | 4     | 3    | 2   | 1   | 0   |

|---------|-----|-----|-----|-------|------|-----|-----|-----|

| Field   |     |     |     | PW    | MH   |     |     |     |

| RESET   | 0   | 0   | 0   | 0     | 0    | 0   | 0   | 0   |

| R/W     | R/W | R/W | R/W | R/W   | R/W  | R/W | R/W | R/W |

| Address |     |     |     | F04H, | F0CH |     |     |     |

#### Table 56. Timer 0–1 PWM High Byte Register (TxPWMH)

#### Table 57. Timer 0–1 PWM Low Byte Register (TxPWML)

| Bit     | 7   | 6          | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----|------------|-----|-----|-----|-----|-----|-----|

| Field   |     |            |     | PW  | ′ML |     |     |     |

| RESET   | 0   | 0          | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W | R/W        | R/W | R/W | R/W | R/W | R/W | R/W |

| Address |     | F05H, F0DH |     |     |     |     |     |     |

#### Bit Description

| [7:0] | Pulse-Width Modulator High and Low Bytes                                                     |

|-------|----------------------------------------------------------------------------------------------|

| PWMH, | These two bytes, {PWMH[7:0], PWML[7:0]}, form a 16-bit value that is compared to the current |

| PWML  | 16-bit timer count. When a match occurs, the PWM output changes state. The PWM output        |

|       | value is set by the TPOL bit in the Timer Control Register (TxCTL1) Register.                |

The TxPWMH and TxPWML registers also store the 16-bit captured timer value when operating in CAPTURE or CAPTURE/COMPARE modes.

- Set or clear the CTSE bit to enable or disable control from the remote receiver using the  $\overline{\text{CTS}}$  pin

- 6. Check the TDRE bit in the UART Status 0 Register to determine if the Transmit Data Register is empty (indicated by a 1). If empty, continue to <u>Step 7</u>. If the Transmit Data Register is full (indicated by a 0), continue to monitor the TDRE bit until the Transmit Data Register becomes available to receive new data.

- 7. Write the UART Control 1 Register to select the outgoing address bit.

- 8. Set the Multiprocessor Bit Transmitter (MPBT) if sending an address byte, clear it if sending a data byte.

- 9. Write the data byte to the UART Transmit Data Register. The transmitter automatically transfers the data to the Transmit Shift Register and transmits the data.

- 10. Make any changes to the Multiprocessor Bit Transmitter (MPBT) value, if appropriate and MULTIPROCESSOR Mode is enabled.

- 11. To transmit additional bytes, return to <u>Step 5</u>.

# Transmitting Data using the Interrupt-Driven Method

The UART Transmitter interrupt indicates the availability of the Transmit Data Register to accept new data for transmission. Observe the following steps to configure the UART for interrupt-driven data transmission:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the appropriate baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Execute a DI instruction to disable interrupts.

- 4. Write to the Interrupt control registers to enable the UART Transmitter interrupt and set the acceptable priority.

- 5. Write to the UART Control 1 Register to enable MULTIPROCESSOR (9-bit) Mode functions, if MULTIPROCESSOR Mode is appropriate.

- 6. Set the MULTIPROCESSOR Mode Select (MPEN) to Enable MULTIPROCESSOR Mode.

- 7. Write to the UART Control 0 Register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission

- Enable parity, if appropriate and if MULTIPROCESSOR Mode is not enabled and select either even or odd parity

# **UART Interrupts**

The UART features separate interrupts for the transmitter and the receiver. In addition, when the UART primary functionality is disabled, the Baud Rate Generator can also function as a basic timer with interrupt capability.

#### **Transmitter Interrupts**

The transmitter generates a single interrupt when the Transmit Data Register Empty bit (TDRE) is set to 1. This indicates that the transmitter is ready to accept new data for transmission. The TDRE interrupt occurs after the Transmit Shift Register has shifted the first bit of data out. The Transmit Data Register can now be written with the next character to send. This action provides 7 bit periods of latency to load the Transmit Data Register before the Transmit Shift Register completes shifting the current character. Writing to the UART Transmit Data Register clears the TDRE bit to 0.

#### **Receiver Interrupts**

The receiver generates an interrupt when any of the following actions occur:

• A data byte is received and is available in the UART Receive Data Register. This interrupt can be disabled independently of the other receiver interrupt sources. The received data interrupt occurs after the receive character has been received and placed in the Receive Data Register. To avoid an overrun error, software must respond to this received data available condition before the next character is completely received.

**Note:** In MULTIPROCESSOR Mode (MPEN=1), the receive data interrupts are dependent on the multiprocessor configuration and the most recent address byte.

- A break is received.

- An overrun is detected.

- A data framing error is detected.

#### **UART Overrun Errors**

When an overrun error condition occurs the UART prevents overwriting of the valid data currently in the Receive Data Register. The Break Detect and Overrun status bits are not displayed until after the valid data has been read.

After the valid data has been read, the UART Status 0 Register is updated to indicate the overrun condition (and Break Detect, if applicable). The RDA bit is set to 1 to indicate that the Receive Data Register contains a data byte. However, because the overrun error occurred, this byte may not contain valid data and must be ignored. The BRKD bit indicates if the overrun was caused by a break condition on the line. After reading the status

The UART data rate is calculated using the following equation:

UART Baud Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

For a given UART data rate, calculate the integer baud rate divisor value using the following equation:

UART Baud Rate Divisor Value (BRG) = Round  $\left(\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Data Rate (bits/s)}}\right)$

The baud rate error relative to the acceptable baud rate is calculated using the following equation:

UART Baud Rate Error (%) =  $100 \times \left(\frac{\text{Actual Data Rate} - \text{Desired Data Rate}}{\text{Desired Data Rate}}\right)$

For reliable communication, the UART baud rate error must never exceed 5 percent. Table 72 provides information about the data rate errors for popular baud rates and commonly used crystal oscillator frequencies.

|                          | 10.0MHz Syste            | em Clock             |              | 5.                       | 5296MHz Sys              | tem Clock            |              |

|--------------------------|--------------------------|----------------------|--------------|--------------------------|--------------------------|----------------------|--------------|

| Acceptable<br>Rate (kHz) | BRG Divisor<br>(Decimal) | Actual Rate<br>(kHz) | Error<br>(%) | Acceptable<br>Rate (kHz) | BRG Divisor<br>(Decimal) | Actual Rate<br>(kHz) | Error<br>(%) |

| 1250.0                   | N/A                      | N/A                  | N/A          | 1250.0                   | N/A                      | N/A                  | N/A          |

| 625.0                    | 1                        | 625.0                | 0.00         | 625.0                    | N/A                      | N/A                  | N/A          |

| 250.0                    | 3                        | 208.33               | -16.67       | 250.0                    | 1                        | 345.6                | 38.24        |

| 115.2                    | 5                        | 125.0                | 8.51         | 115.2                    | 3                        | 115.2                | 0.00         |

| 57.6                     | 11                       | 56.8                 | -1.36        | 57.6                     | 6                        | 57.6                 | 0.00         |

| 38.4                     | 16                       | 39.1                 | 1.73         | 38.4                     | 9                        | 38.4                 | 0.00         |

| 19.2                     | 33                       | 18.9                 | 0.16         | 19.2                     | 18                       | 19.2                 | 0.00         |

| 9.60                     | 65                       | 9.62                 | 0.16         | 9.60                     | 36                       | 9.60                 | 0.00         |

| 4.80                     | 130                      | 4.81                 | 0.16         | 4.80                     | 72                       | 4.80                 | 0.00         |

| 2.40                     | 260                      | 2.40                 | -0.03        | 2.40                     | 144                      | 2.40                 | 0.00         |

| 1.20                     | 521                      | 1.20                 | -0.03        | 1.20                     | 288                      | 1.20                 | 0.00         |

| 0.60                     | 1042                     | 0.60                 | -0.03        | 0.60                     | 576                      | 0.60                 | 0.00         |

| 0.30                     | 2083                     | 0.30                 | 0.2          | 0.30                     | 1152                     | 0.30                 | 0.00         |

| 3 5                      | 705/5MH7 Sv              | stom Clock           | <u> </u>     | 1                        | 8/32MHz Sve              | tom Clock            |              |

#### Table 72. UART Baud Rates

3.579545 MHz System Clock

1.8432MHz System Clock

# Infrared Encoder/Decoder

Z8 Encore! XP F082A Series products contain a fully-functional, high-performance UART to Infrared Encoder/Decoder (endec). The infrared endec is integrated with an onchip UART to allow easy communication between the Z8 Encore! XP MCU and IrDA Physical Layer Specification, Version 1.3-compliant infrared transceivers. Infrared communication provides secure, reliable, low-cost, point-to-point communication between PCs, PDAs, cell phones, printers and other infrared enabled devices.

# Architecture

Figure 16 displays the architecture of the infrared endec.

Figure 16. Infrared Data Communication System Block Diagram

# Operation

When the infrared endec is enabled, the transmit data from the associated on-chip UART is encoded as digital signals in accordance with the IrDA standard and output to the infrared transceiver through the TXD pin. Likewise, data received from the infrared transceiver is passed to the infrared endec through the RXD pin, decoded by the infrared endec and passed to the UART. Communication is half-duplex, which means simultaneous data transmission and reception is not allowed. For the reserved values, all input switches are disabled to avoid leakage or other undesirable operation. ADC samples taken with reserved bit settings are undefined.

SINGLE-ENDED Mode:

0000 = ANA0 (transimpedance amp output when enabled) 0001 = ANA1 (transimpedance amp inverting input) 0010 = ANA2 (transimpedance amp noninverting input) 0011 = ANA3 0100 = ANA4 0101 = ANA5 0110 = ANA6 0111 = ANA7 1000 = Reserved 1001 = Reserved 1010 = Reserved 1011 = Reserved 1100 = Hold transimpedance input nodes (ANA1 and ANA2) to ground. 1101 = Reserved 1110 = Temperature Sensor.

1110 = Reserved.

DIFFERENTIAL Mode (noninverting input and inverting input respectively):

- 0000 = ANA0 and ANA1 0001 = ANA2 and ANA3 0010 = ANA4 and ANA5 0011 = ANA4 and ANA5 0011 = ANA1 and ANA0 0100 = ANA3 and ANA2 0101 = ANA5 and ANA4 0110 = ANA6 and ANA5 0111 = ANA0 and ANA5 1001 = ANA0 and ANA3 1001 = ANA0 and ANA4 1010 = ANA0 and ANA4 1010 = ANA0 and ANA5 1011 = Reserved 1100 = Reserved 1101 = Reserved 1101 = Reserved1110 = Reserved

- 1111 = Manual Offset Calibration Mode

## **ADC Control/Status Register 1**

The ADC Control/Status Register 1 (ADCCTL1) configures the input buffer stage, enables the threshold interrupts and contains the status of both threshold triggers. It is also used to select the voltage reference configuration.

# Flash Memory

The products in the Z8 Encore! XP F082A Series feature a nonvolatile Flash memory of 8KB (8192), 4 KB (4096), 2 KB (2048 bytes), or 1 KB (1024) with read/write/erase capability. The Flash Memory can be programmed and erased in-circuit by user code or through the On-Chip Debugger. The features include:

- User controlled read and write protect capability

- Sector-based write protection scheme

- Additional protection schemes against accidental program and erasure

#### Architecture

The Flash memory array is arranged in pages with 512 bytes per page. The 512-byte page is the minimum Flash block size that can be erased. Each page is divided into 8 rows of 64 bytes.

For program or data protection, the Flash memory is also divided into sectors. In the Z8 Encore! XP F082A Series, these sectors are either 1024 bytes (in the 8KB devices) or 512 bytes (all other memory sizes) in size. Page and sector sizes are not generally equal.

The first 2 bytes of Flash Program memory are used as Flash option bits. For more information about their operation, see the <u>Flash Option Bits</u> chapter on page 159.

Table 78 describes the Flash memory configuration for each device in the Z8 Encore! XP F082A Series. Figure 21 displays the Flash memory arrangement.

| Part Number | Flash Size<br>KB (Bytes) | Flash<br>Pages | Program Memory<br>Addresses | Flash Sector<br>Size (Bytes) |

|-------------|--------------------------|----------------|-----------------------------|------------------------------|

| Z8F08xA     | 8 (8192)                 | 16             | 0000H-1FFFH                 | 1024                         |

| Z8F04xA     | 4 (4096)                 | 8              | 0000H-0FFFH                 | 512                          |

| Z8F02xA     | 2 (2048)                 | 4              | 0000H-07FFH                 | 512                          |

| Z8F01xA     | 1 (1024)                 | 2              | 0000H-03FFH                 | 512                          |

Table 78. Z8 Encore! XP F082A Series Flash Memory Configurations

Debugger. Writing an invalid value or an invalid sequence returns the Flash Controller to its locked state. The Write-only Flash Control Register shares its Register File address with the read-only Flash Status Register.

# **Crystal Oscillator**

The products in the Z8 Encore! XP F082A Series contain an on-chip crystal oscillator for use with external crystals with 32kHz to 20MHz frequencies. In addition, the oscillator supports external RC networks with oscillation frequencies up to 4MHz or ceramic resonators with frequencies up to 8MHz. The on-chip crystal oscillator can be used to generate the primary system clock for the internal eZ8 CPU and the majority of the on-chip peripherals. Alternatively, the  $X_{IN}$  input pin can also accept a CMOS-level clock input signal (32kHz–20MHz). If an external clock generator is used, the  $X_{OUT}$  pin must be left unconnected. The Z8 Encore! XP F082A Series products do not contain an internal clock divider. The frequency of the signal on the  $X_{IN}$  input pin determines the frequency of the system clock.

**Note:** Although the X<sub>IN</sub> pin can be used as an input for an external clock generator, the CLKIN pin is better suited for such use (see the <u>System Clock Selection</u> section on page 193).

# **Operating Modes**

The Z8 Encore! XP F082A Series products support four oscillator modes:

- Minimum power for use with very low frequency crystals (32kHz-1MHz)

- Medium power for use with medium frequency crystals or ceramic resonators (0.5 MHz to 8MHz)

- Maximum power for use with high frequency crystals (8MHz to 20MHz)

- On-chip oscillator configured for use with external RC networks (<4MHz)

The oscillator mode is selected via user-programmable Flash option bits. See **the** <u>Flash</u> <u>Option Bits</u> chapter on page 159 for information.

# **Crystal Oscillator Operation**

The XTLDIS Flash option bit controls whether the crystal oscillator is enabled during reset. The crystal may later be disabled after reset if a new oscillator has been selected as the system clock. If the crystal is manually enabled after reset through the OSCCTL Register, the user code must wait at least 1000 crystal oscillator cycles for the crystal to stabilize. After this, the crystal oscillator may be selected as the system clock.

#### Table 123. CPU Control Instructions (Continued)

| Mnemonic | Operands | Instruction            |

|----------|----------|------------------------|

| RCF      | —        | Reset Carry Flag       |

| SCF      | —        | Set Carry Flag         |

| SRP      | SIC      | Set Register Pointer   |

| STOP     | —        | STOP Mode              |

| WDT      | —        | Watchdog Timer Refresh |

#### Table 124. Load Instructions

| Mnemonic | Operands    | Instruction                                                             |

|----------|-------------|-------------------------------------------------------------------------|

| CLR      | dst         | Clear                                                                   |

| LD       | dst, src    | Load                                                                    |

| LDC      | dst, src    | Load Constant to/from Program Memory                                    |

| LDCI     | dst, src    | Load Constant to/from Program Memory and Auto-<br>Increment Addresses   |

| LDE      | dst, src    | Load External Data to/from Data Memory                                  |

| LDEI     | dst, src    | Load External Data to/from Data Memory and Auto-<br>Increment Addresses |

| LDWX     | dst, src    | Load Word using Extended Addressing                                     |

| LDX      | dst, src    | Load using Extended Addressing                                          |

| LEA      | dst, X(src) | Load Effective Address                                                  |

| POP      | dst         | Рор                                                                     |

| POPX     | dst         | Pop using Extended Addressing                                           |

| PUSH     | src         | Push                                                                    |

| PUSHX    | SIC         | Push using Extended Addressing                                          |

#### Table 125. Logical Instructions

| Mnemonic | Operands | Instruction                                    |

|----------|----------|------------------------------------------------|

| AND      | dst, src | Logical AND                                    |

| ANDX     | dst, src | Logical AND using Extended Addressing          |

| СОМ      | dst      | Complement                                     |

| OR       | dst, src | Logical OR                                     |

| ORX      | dst, src | Logical OR using Extended Addressing           |

| XOR      | dst, src | Logical Exclusive OR                           |

| XORX     | dst, src | Logical Exclusive OR using Extended Addressing |

#### 232

# **AC Characteristics**

The section provides information about the AC characteristics and timing. All AC timing information assumes a standard load of 50pF on all outputs.

|                     |                              | T <sub>A</sub> = -40°C<br>(unless c | ℃ to 3.6V<br>c to +105°C<br>otherwise<br>ted) |       |                                                                                                           |

|---------------------|------------------------------|-------------------------------------|-----------------------------------------------|-------|-----------------------------------------------------------------------------------------------------------|

| Symbol              | Parameter                    | Minimum                             | Maximum                                       | Units | Conditions                                                                                                |

| F <sub>SYSCLK</sub> | System Clock Frequency       | -                                   | 20.0                                          | MHz   | Read-only from Flash mem-<br>ory                                                                          |

|                     |                              | 0.032768                            | 20.0                                          | MHz   | Program or erasure of the<br>Flash memory                                                                 |

| F <sub>XTAL</sub>   | Crystal Oscillator Frequency | -                                   | 20.0                                          | MHz   | System clock frequencies<br>below the crystal oscillator<br>minimum require an exter-<br>nal clock driver |

| T <sub>XIN</sub>    | System Clock Period          | 50                                  | -                                             | ns    | T <sub>CLK</sub> = 1/F <sub>sysclk</sub>                                                                  |

| T <sub>XINH</sub>   | System Clock High Time       | 20                                  | 30                                            | ns    | T <sub>CLK</sub> = 50 ns                                                                                  |

| T <sub>XINL</sub>   | System Clock Low Time        | 20                                  | 30                                            | ns    | T <sub>CLK</sub> = 50 ns                                                                                  |

| T <sub>XINR</sub>   | System Clock Rise Time       | -                                   | 3                                             | ns    | T <sub>CLK</sub> = 50 ns                                                                                  |

| T <sub>XINF</sub>   | System Clock Fall Time       | _                                   | 3                                             | ns    | T <sub>CLK</sub> = 50 ns                                                                                  |

#### Table 134. Internal Precision Oscillator Electrical Characteristics

|                    |                                                           | T <sub>A</sub> = - | = 2.7V to<br>-40°C to +<br>otherwise |            |       |                                         |

|--------------------|-----------------------------------------------------------|--------------------|--------------------------------------|------------|-------|-----------------------------------------|

| Symbol             | Parameter                                                 | Minimum            | Typical                              | Maximum    | Units | Conditions                              |

| F <sub>IPO</sub>   | Internal Precision Oscillator Fre-<br>quency (High Speed) |                    | 5.53                                 |            | MHz   | $V_{DD} = 3.3 V$<br>$T_A = 30^{\circ}C$ |

| F <sub>IPO</sub>   | Internal Precision Oscillator Fre-<br>quency (Low Speed)  |                    | 32.7                                 |            | kHz   | $V_{DD} = 3.3 V$<br>$T_A = 30^{\circ}C$ |

| F <sub>IPO</sub>   | Internal Precision Oscillator Error                       |                    | <u>+</u> 1                           | <u>+</u> 4 | %     |                                         |

| T <sub>IPOST</sub> | Internal Precision Oscillator<br>Startup Time             |                    | 3                                    |            | μs    |                                         |

#### 240

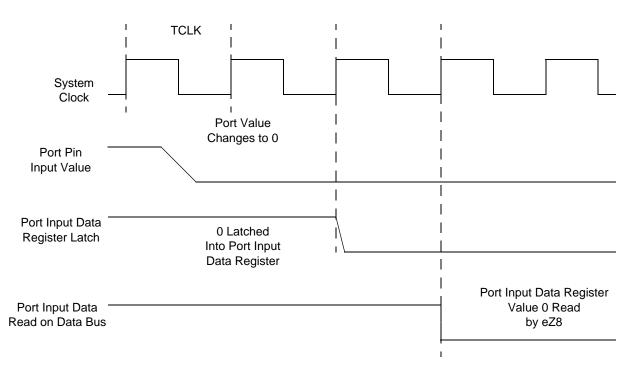

#### General Purpose I/O Port Input Data Sample Timing

Figure 34 displays timing of the GPIO Port input sampling. The input value on a GPIO port pin is sampled on the rising edge of the system clock. The Port value is available to the eZ8 CPU on the second rising clock edge following the change of the Port value.

#### Figure 34. Port Input Sample Timing

#### Table 143. GPIO Port Input Timing

|                     |                                                                                                    | Delay (ns) |         |

|---------------------|----------------------------------------------------------------------------------------------------|------------|---------|

| Parameter           | Abbreviation                                                                                       | Minimum    | Maximum |

| T <sub>S_PORT</sub> | Port Input Transition to X <sub>IN</sub> Rise Setup Time (not pictured)                            | 5          | -       |

| T <sub>H_PORT</sub> | X <sub>IN</sub> Rise to Port Input Transition Hold Time (not pictured)                             | 0          | -       |

| T <sub>SMR</sub>    | GPIO Port Pin Pulse Width to ensure Stop Mode Recovery (for GPIO port pins enabled as SMR sources) | 1 μs       |         |