Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betans                     |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT           |

| Number of I/O              | 25                                                        |

| Program Memory Size        | 1KB (1K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | 16 x 8                                                    |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 28-DIP (0.600", 15.24mm)                                  |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f011apj020sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

| Table 29. | Port A–C Input Data Registers (PxIN)            |

|-----------|-------------------------------------------------|

| Table 30. | Port A–D Output Data Register (PxOUT)           |

| Table 31. | LED Drive Enable (LEDEN)                        |

| Table 32. | LED Drive Level High Register (LEDLVLH)         |

| Table 33. | LED Drive Level Low Register (LEDLVLL)          |

| Table 34. | Trap and Interrupt Vectors in Order of Priority |

| Table 35. | Interrupt Request 0 Register (IRQ0) 60          |

| Table 36. | Interrupt Request 1 Register (IRQ1) 61          |

| Table 37. | Interrupt Request 2 Register (IRQ2) 62          |

| Table 38. | IRQ0 Enable and Priority Encoding               |

| Table 39. | IRQ0 Enable High Bit Register (IRQ0ENH)         |

| Table 40. | IRQ0 Enable Low Bit Register (IRQ0ENL)          |

| Table 41. | IRQ1 Enable and Priority Encoding               |

| Table 42. | IRQ1 Enable Low Bit Register (IRQ1ENL)          |

| Table 43. | IRQ1 Enable High Bit Register (IRQ1ENH)         |

| Table 44. | IRQ2 Enable and Priority Encoding               |

| Table 45. | IRQ2 Enable High Bit Register (IRQ2ENH)         |

| Table 46. | Interrupt Edge Select Register (IRQES) 67       |

| Table 47. | IRQ2 Enable Low Bit Register (IRQ2ENL)          |

| Table 48. | Shared Interrupt Select Register (IRQSS) 68     |

| Table 49. | Interrupt Control Register (IRQCTL)             |

| Table 50. | Timer 0–1 Control Register 0 (TxCTL0)           |

| Table 51. | Timer 0–1 Control Register 1 (TxCTL1)           |

| Table 52. | Timer 0–1 High Byte Register (TxH)              |

| Table 53. | Timer 0–1 Low Byte Register (TxL)               |

| Table 54. | Timer 0–1 Reload High Byte Register (TxRH)      |

| Table 55. | Timer 0–1 Reload Low Byte Register (TxRL)       |

| Table 56. | Timer 0–1 PWM High Byte Register (TxPWMH)       |

| Table 57. | Timer 0–1 PWM Low Byte Register (TxPWML)        |

| Table 58. | Watchdog Timer Approximate Time-Out Delays      |

|           |                                                 |

# Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

| Table 89.  | Flash Options Bits at Program Memory Address 0001H 164                   |

|------------|--------------------------------------------------------------------------|

| Table 90.  | Trim Options Bits at Address 0000H 165                                   |

| Table 91.  | Trim Option Bits at 0001H 165                                            |

| Table 92.  | Trim Option Bits at 0002H (TIPO) 166                                     |

| Table 93.  | Trim Option Bits at Address 0003H (TLVD) 166                             |

| Table 94.  | LVD Trim Values                                                          |

| Table 95.  | Trim Option Bits at 0004H 168                                            |

| Table 96.  | ADC Calibration Bits                                                     |

| Table 97.  | ADC Calibration Data Location                                            |

| Table 98.  | Temperature Sensor Calibration High Byte at 003A (TSCALH) 171            |

| Table 99.  | Temperature Sensor Calibration Low Byte at 003B (TSCALL) 171             |

| Table 100. | Watchdog Calibration High Byte at 007EH (WDTCALH) 172                    |

| Table 101. | Serial Number at 001C - 001F (S_NUM) 173                                 |

| Table 102. | Serialization Data Locations                                             |

| Table 103. | Watchdog Calibration Low Byte at 007FH (WDTCALL) 173                     |

| Table 104. | Lot Identification Number (RAND_LOT)                                     |

| Table 105. | Randomized Lot ID Locations                                              |

| Table 106. | Write Status Byte 177                                                    |

| Table 107. | NVDS Read Time                                                           |

| Table 108. | OCD Baud-Rate Limits                                                     |

| Table 109. | Debug Command Enable/Disable 186                                         |

| Table 110. | OCD Control Register (OCDCTL) 191                                        |

| Table 111. | OCD Status Register (OCDSTAT) 192                                        |

| Table 112. | Oscillator Configuration and Selection                                   |

| Table 113. | Oscillator Control Register (OSCCTL)                                     |

| Table 114. | Recommended Crystal Oscillator Specifications                            |

| Table 115. | Transconductance Values for Low, Medium and High Gain Operating<br>Modes |

| Table 116. | Assembly Language Syntax Example 1                                       |

| Table 117. | Assembly Language Syntax Example 2                                       |

| Table 118. | Notational Shorthand                                                     |

## HALT Mode

Executing the eZ8 CPU's HALT instruction places the device into HALT Mode, which powers down the CPU but leaves all other peripherals active. In HALT Mode, the operating characteristics are:

- Primary oscillator is enabled and continues to operate

- System clock is enabled and continues to operate

- eZ8 CPU is stopped

- Program counter (PC) stops incrementing

- Watchdog Timer's internal RC oscillator continues to operate

- If enabled, the Watchdog Timer continues to operate

- All other on-chip peripherals continue to operate, if enabled

The eZ8 CPU can be brought out of HALT Mode by any of the following operations:

- Interrupt

- Watchdog Timer time-out (interrupt or reset)

- Power-On Reset

- Voltage Brown-Out reset

- External **RESET** pin assertion

To minimize current in HALT Mode, all GPIO pins that are configured as inputs must be driven to one of the supply rails ( $V_{CC}$  or GND).

# **Peripheral-Level Power Control**

In addition to the STOP and HALT modes, it is possible to disable each peripheral on each of the Z8 Encore! XP F082A Series devices. Disabling a given peripheral minimizes its power consumption.

# **Power Control Register Definitions**

The following sections define the Power Control registers.

### **Power Control Register 0**

Each bit of the following registers disables a peripheral block, either by gating its system clock input or by removing power from the block. The default state of the low-power

| Port                | Pin | Mnemonic                      | Alternate Function Description | Alternate Function<br>Set Register AFS1 |

|---------------------|-----|-------------------------------|--------------------------------|-----------------------------------------|

| Port B <sup>3</sup> | PB0 | Reserved                      |                                | AFS1[0]: 0                              |

|                     |     | ANA0/AMPOUT                   | ADC Analog Input/LPO Output    | AFS1[0]: 1                              |

|                     | PB1 | Reserved                      |                                | AFS1[1]: 0                              |

|                     |     | ANA1/AMPINN                   | ADC Analog Input/LPO Input (N) | AFS1[1]: 1                              |

|                     | PB2 | Reserved                      |                                | AFS1[2]: 0                              |

|                     |     | ANA2/AMPINP                   | ADC Analog Input/LPO Input (P) | AFS1[2]: 1                              |

|                     | PB3 | CLKIN                         | External Clock Input           | AFS1[3]: 0                              |

|                     |     | ANA3                          | ADC Analog Input               | AFS1[3]: 1                              |

|                     | PB4 | Reserved                      |                                | AFS1[4]: 0                              |

|                     |     | ANA7                          | ADC Analog Input               | AFS1[4]: 1                              |

|                     | PB5 | Reserved                      |                                | AFS1[5]: 0                              |

|                     |     | V <sub>REF</sub> <sup>4</sup> | ADC Voltage Reference          | AFS1[5]: 1                              |

|                     | PB6 | Reserved                      |                                | AFS1[6]: 0                              |

|                     |     | Reserved                      |                                | AFS1[6]: 1                              |

|                     | PB7 | Reserved                      |                                | AFS1[7]: 0                              |

|                     |     | Reserved                      |                                | AFS1[7]: 1                              |

#### Table 15. Port Alternate Function Mapping (Non 8-Pin Parts) (Continued)

Notes:

- Because there is only a single alternate function for each Port A pin, the Alternate Function Set registers are not implemented for Port A. Enabling alternate function selections automatically enables the associated alternate function. See the <u>Port A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

- 2. Whether PA0/PA6 takes on the timer input or timer output complement function depends on the timer configuration. See the <u>Timer Pin Signal Operation</u> section on page 84 for details.

- Because there are at most two choices of alternate function for any pin of Port B, the Alternate Function Set Register AFS2 is not used to select the function. Alternate function selection must also be enabled. See the <u>Port</u> <u>A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

- 4. V<sub>RFF</sub> is available on PB5 in 28-pin products and on PC2 in 20-pin parts.

- Because there are at most two choices of alternate function for any pin of Port C, the Alternate Function Set Register AFS2 is not used to select the function. Alternate function selection must also be enabled. See the <u>Port</u> <u>A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

- 6. Because there is only a single alternate function for the Port PD0 pin, the Alternate Function Set registers are not implemented for Port D. Enabling alternate function selections automatically enables the associated alternate function. See the Port A–D Alternate Function Subregisters (PxAF) section on page 47 for details.

**Caution:** To avoid retriggerings of the Watchdog Timer interrupt after exiting the associated interrupt service routine, Zilog recommends that the service routine continues to read from the RSTSTAT Register until the WDT bit is cleared as shown in the following example.

```

CLEARWDT:

LDX r0, RSTSTAT ; read reset status register to clear wdt bit

BTJNZ 5, r0, CLEARWDT ; loop until bit is cleared

```

## **Interrupt Control Register Definitions**

For all interrupts other than the Watchdog Timer interrupt, the Primary Oscillator Fail Trap and the Watchdog Oscillator Fail Trap, the interrupt control registers enable individual interrupts, set interrupt priorities and indicate interrupt requests.

### **Interrupt Request 0 Register**

The Interrupt Request 0 (IRQ0) Register, shown in Table 35, stores the interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ0 Register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 0 Register to determine if any interrupt requests are pending.

| Bit     | 7        | 6   | 5   | 4     | 3     | 2        | 1        | 0    |

|---------|----------|-----|-----|-------|-------|----------|----------|------|

| Field   | Reserved | T1I | TOI | U0RXI | U0TXI | Reserved | Reserved | ADCI |

| RESET   | 0        | 0   | 0   | 0     | 0     | 0        | 0        | 0    |

| R/W     | R/W      | R/W | R/W | R/W   | R/W   | R/W      | R/W      | R/W  |

| Address |          |     |     | FC    | 0H    |          |          |      |

| Bit        | Description                                                                                                                                        |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]        | <b>Reserved</b><br>This bit is reserved and must be programmed to 0.                                                                               |

| [6]<br>T1I | <b>Timer 1 Interrupt Request</b><br>0 = No interrupt request is pending for Timer 1.<br>1 = An interrupt request from Timer 1 is awaiting service. |

| [5]<br>T0I | <b>Timer 0 Interrupt Request</b><br>0 = No interrupt request is pending for Timer 0.<br>1 = An interrupt request from Timer 0 is awaiting service. |

| Bit           | Description (Continued)                                                  |

|---------------|--------------------------------------------------------------------------|

| [4]<br>U0RENL | UART 0 Receive Interrupt Request Enable Low Bit                          |

| [3]<br>U0TENL | UART 0 Transmit Interrupt Request Enable Low Bit                         |

| [2:1]         | <b>Reserved</b><br>These bits are reserved and must be programmed to 00. |

| [0]<br>ADCENL | ADC Interrupt Request Enable Low Bit                                     |

### **IRQ1 Enable High and Low Bit Registers**

Table 41 describes the priority control for IRQ1. The IRQ1 Enable High and Low Bit registers, shown in Tables 41 and 42, form a priority-encoded enabling for interrupts in the Interrupt Request 1 Register.

| IRQ1ENH[x]        | IRQ1ENL[x]        | Priority | Description |

|-------------------|-------------------|----------|-------------|

| 0                 | 0                 | Disabled | Disabled    |

| 0                 | 1                 | Level 1  | Low         |

| 1                 | 0                 | Level 2  | Medium      |

| 1                 | 1                 | Level 3  | High        |

| Note: x indicates | register bits 0-7 |          |             |

### Table 41. IRQ1 Enable and Priority Encoding

| Table 46. IRQ2 Enable Low Bit Register (IRQ2ENL |

|-------------------------------------------------|

|-------------------------------------------------|

| Bit     | 7   | 6    | 5     | 4   | 3     | 2     | 1     | 0     |

|---------|-----|------|-------|-----|-------|-------|-------|-------|

| Field   |     | Rese | erved |     | C3ENL | C2ENL | C1ENL | C0ENL |

| RESET   | 0   | 0    | 0     | 0   | 0     | 0     | 0     | 0     |

| R/W     | R/W | R/W  | R/W   | R/W | R/W   | R/W   | R/W   | R/W   |

| Address |     |      |       | FC  | 8H    |       |       |       |

| Bit          | Description                                                         |

|--------------|---------------------------------------------------------------------|

| [7:4]        | Reserved<br>These bits are reserved and must be programmed to 0000. |

| [3]<br>C3ENL | Port C3 Interrupt Request Enable Low Bit                            |

| [2]<br>C2ENL | Port C2 Interrupt Request Enable Low Bit                            |

| [1]<br>C1ENL | Port C1 Interrupt Request Enable Low Bit                            |

| [0]<br>COENL | Port C0 Interrupt Request Enable Low Bit                            |

# Interrupt Edge Select Register

The Interrupt Edge Select (IRQES) Register, shown in Table 47, determines whether an interrupt is generated for the rising edge or falling edge on the selected GPIO Port A input pin.

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |

|---------|------|------|------|------|------|------|------|------|--|

| Field   | IES7 | IES6 | IES5 | IES4 | IES3 | IES2 | IES1 | IES0 |  |

| RESET   | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |  |

| R/W     | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |  |

| Address |      | FCDH |      |      |      |      |      |      |  |

| Table 47. | Interrupt | Edge | Select | Register | (IRQES) |

|-----------|-----------|------|--------|----------|---------|

|           |           |      |        |          | (       |

| Bit   | Description                                                                 |

|-------|-----------------------------------------------------------------------------|

| [7:0] | Interrupt Edge Select x                                                     |

| IESx  | 0 = An interrupt request is generated on the falling edge of the PAx input. |

|       | 1 = An interrupt request is generated on the rising edge of the PAx input.  |

| Note: | x indicates the specific GPIO port pin number (0–7).                        |

If TPOL is set to 0, the ratio of the PWM output High time to the total period is represented by:

PWM Output High Time Ratio (%) =  $\frac{\text{Reload Value} - \text{PWM Value}}{\text{Reload Value}} \times 100$

If TPOL is set to 1, the ratio of the PWM output High time to the total period is represented by:

PWM Output High Time Ratio (%) =  $\frac{PWM \text{ Value}}{\text{Reload Value}} \times 100$

### **CAPTURE Mode**

In CAPTURE Mode, the current timer count value is recorded when the appropriate external Timer Input transition occurs. The Capture count value is written to the Timer PWM High and Low Byte registers. The timer input is the system clock. The TPOL bit in the Timer Control Register determines if the Capture occurs on a rising edge or a falling edge of the Timer Input signal. When the Capture event occurs, an interrupt is generated and the timer continues counting. The INPCAP bit in TxCTL0 Register is set to indicate the timer interrupt is because of an input capture event.

The timer continues counting up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt and continues counting. The INPCAP bit in TxCTL0 Register clears indicating the timer interrupt is not because of an input capture event.

Observe the following steps for configuring a timer for CAPTURE Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE Mode

- Set the prescale value

- Set the Capture edge (rising or falling) for the Timer Input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. Clear the Timer PWM High and Low Byte registers to 0000H. Clearing these registers allows the software to determine if interrupts were generated by either a capture event or a reload. If the PWM High and Low Byte registers still contain 0000H after the interrupt, the interrupt was generated by a Reload.

- Set the initial logic level (High or Low) for the Timer Output alternate function, if appropriate

- 2. Write to the Timer High and Low Byte registers to set the starting count value.

- 3. Write to the Timer Reload High and Low Byte registers to set the Compare value.

- 4. Enable the timer interrupt, if appropriate and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 6. Write to the Timer Control Register to enable the timer and initiate counting.

In COMPARE Mode, the system clock always provides the timer input. The Compare time can be calculated by the following equation:

COMPARE Mode Time (s) = (Compare Value – Start Value) × Prescale System Clock Frequency (Hz)

### GATED Mode

In GATED Mode, the timer counts only when the Timer Input signal is in its active state (asserted), as determined by the TPOL bit in the Timer Control Register. When the Timer Input signal is asserted, counting begins. A timer interrupt is generated when the Timer Input signal is deasserted or a timer reload occurs. To determine if a Timer Input signal deassertion generated the interrupt, read the associated GPIO input value and compare to the value stored in the TPOL bit.

The timer counts up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. When reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes (assuming the Timer Input signal remains asserted). Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer reset.

Observe the following steps for configuring a timer for GATED Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

The UART is now configured for interrupt-driven data reception. When the UART Receiver interrupt is detected, the associated interrupt service routine (ISR) performs the following:

- 1. Checks the UART Status 0 Register to determine the source of the interrupt error, break, or received data.

- 2. Reads the data from the UART Receive Data Register if the interrupt was because of data available. If operating in MULTIPROCESSOR (9-bit) Mode, further actions may be required depending on the MULTIPROCESSOR Mode bits MPMD[1:0].

- 3. Clears the UART Receiver interrupt in the applicable Interrupt Request Register.

- 4. Executes the IRET instruction to return from the interrupt-service routine and await more data.

# Clear To Send (CTS) Operation

The CTS pin, if enabled by the CTSE bit of the UART Control 0 Register, performs flow control on the outgoing transmit datastream. The Clear To Send ( $\overline{\text{CTS}}$ ) input pin is sampled one system clock before beginning any new character transmission. To delay transmission of the next data character, an external receiver must deassert  $\overline{\text{CTS}}$  at least one system clock cycle before a new data transmission begins. For multiple character transmissions, this action is typically performed during Stop Bit transmission. If  $\overline{\text{CTS}}$  deasserts in the middle of a character transmission, the current character is sent completely.

## MULTIPROCESSOR (9-bit) Mode

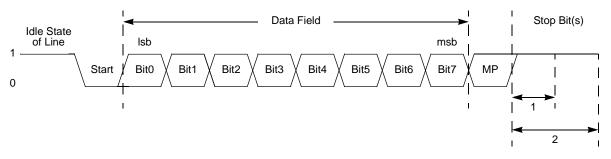

The UART features a MULTIPROCESSOR (9-bit) Mode that uses an extra (9th) bit for selective communication when a number of processors share a common UART bus. In MULTIPROCESSOR Mode (also referred to as *9-bit Mode*), the multiprocessor bit (MP) is transmitted immediately following the 8-bits of data and immediately preceding the Stop bit(s) as displayed in Figure 13. The character format is:

Figure 13. UART Asynchronous MULTIPROCESSOR Mode Data Format

## **UART Interrupts**

The UART features separate interrupts for the transmitter and the receiver. In addition, when the UART primary functionality is disabled, the Baud Rate Generator can also function as a basic timer with interrupt capability.

### **Transmitter Interrupts**

The transmitter generates a single interrupt when the Transmit Data Register Empty bit (TDRE) is set to 1. This indicates that the transmitter is ready to accept new data for transmission. The TDRE interrupt occurs after the Transmit Shift Register has shifted the first bit of data out. The Transmit Data Register can now be written with the next character to send. This action provides 7 bit periods of latency to load the Transmit Data Register before the Transmit Shift Register completes shifting the current character. Writing to the UART Transmit Data Register clears the TDRE bit to 0.

### **Receiver Interrupts**

The receiver generates an interrupt when any of the following actions occur:

• A data byte is received and is available in the UART Receive Data Register. This interrupt can be disabled independently of the other receiver interrupt sources. The received data interrupt occurs after the receive character has been received and placed in the Receive Data Register. To avoid an overrun error, software must respond to this received data available condition before the next character is completely received.

**Note:** In MULTIPROCESSOR Mode (MPEN=1), the receive data interrupts are dependent on the multiprocessor configuration and the most recent address byte.

- A break is received.

- An overrun is detected.

- A data framing error is detected.

### **UART Overrun Errors**

When an overrun error condition occurs the UART prevents overwriting of the valid data currently in the Receive Data Register. The Break Detect and Overrun status bits are not displayed until after the valid data has been read.

After the valid data has been read, the UART Status 0 Register is updated to indicate the overrun condition (and Break Detect, if applicable). The RDA bit is set to 1 to indicate that the Receive Data Register contains a data byte. However, because the overrun error occurred, this byte may not contain valid data and must be ignored. The BRKD bit indicates if the overrun was caused by a break condition on the line. After reading the status

| Bit           | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [2]<br>BRGCTL | <ul> <li>Baud Rate Control</li> <li>This bit causes an alternate UART behavior depending on the value of the REN bit in the UART Control 0 Register. When the UART receiver is not enabled (REN=0), this bit determines whether the Baud Rate Generator issues interrupts.</li> <li>0 = Reads from the Baud Rate High and Low Byte registers return the BRG reload value.</li> <li>1 = The Baud Rate Generator generates a receive interrupt when it counts down to 0. Reads from the Baud Rate High and Low Byte registers return the current BRG count value.</li> <li>When the UART receiver is enabled (REN=1), this bit allows reads from the Baud Rate registers to return the BRG count value instead of the reload value.</li> <li>0 = Reads from the Baud Rate High and Low Byte registers return the BRG reload value.</li> <li>1 = Reads from the Baud Rate High and Low Byte registers return the BRG reload value.</li> <li>1 = Reads from the Baud Rate High and Low Byte registers return the BRG reload value.</li> </ul> |

| [1]<br>RDAIRQ | <ul> <li>Receive Data Interrupt Enable</li> <li>0 = Received data and receiver errors generates an interrupt request to the Interrupt Controller.</li> <li>1 = Received data does not generate an interrupt request to the Interrupt Controller. Only receiver errors generate an interrupt request.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| [0]<br>IREN   | <ul> <li>Infrared Encoder/Decoder Enable</li> <li>0 = Infrared Encoder/Decoder is disabled. UART operates normally.</li> <li>1 = Infrared Encoder/Decoder is enabled. The UART transmits and receives data through the Infrared Encoder/Decoder.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

113

**Note:** The offset compensation is performed first, followed by the gain compensation. One bit of resolution is lost because of rounding on both the offset and gain computations. As a result the ADC registers read back 13 bits: 1 sign bit, two calibration bits lost to rounding and 10 data bits.

Also note that in the second term, the multiplication must be performed before the division by  $2^{16}$ . Otherwise, the second term incorrectly evaluates to zero.

**Caution:** Although the ADC can be used without the gain and offset compensation, it does exhibit nonunity gain. Designing the ADC with sub-unity gain reduces noise across the ADC range but requires the ADC results to be scaled by a factor of 8/7.

### **ADC Compensation Details**

High-efficiency assembly code that performs ADC compensation is available for download on <u>www.zilog.com</u>. This section offers a bit-specific description of the ADC compensation process used by this code.

The following data bit definitions are used:

0-9, a-f = bit indices in hexadecimal

s = sign bit

v = overflow bit

-= unused

### Input Data

| MSB             | LSB                      |                                                |

|-----------------|--------------------------|------------------------------------------------|

| s b a 9 8 7 6 5 | 4 3 2 1 0 v (ADC)        | ADC Output Word; if v = 1, the data is invalid |

|                 | s 6 5 4 3 2 1 0          | Offset Correction Byte                         |

| ssss 7 6 5      | 4 3 2 1 0 0 0 0 (Offset) | Offset Byte shifted to align with ADC data     |

|                 |                          |                                                |

| sedcba98        | 76543210 (Gain)          | Gain Correction Word                           |

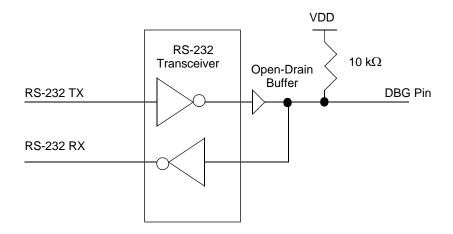

Figure 25. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface; #2 of 2

### **DEBUG Mode**

The operating characteristics of the devices in DEBUG Mode are:

- The eZ8 CPU fetch unit stops, idling the eZ8 CPU, unless directed by the OCD to execute specific instructions

- The system clock operates unless in STOP Mode

- All enabled on-chip peripherals operate unless in STOP Mode

- Automatically exits HALT Mode

- Constantly refreshes the Watchdog Timer, if enabled

### **Entering DEBUG Mode**

The operating characteristics of the devices entering DEBUG Mode are:

- The device enters DEBUG Mode after the eZ8 CPU executes a BRK (Breakpoint) instruction

- If the DBG pin is held Low during the final clock cycle of system reset, the part enters DEBUG Mode immediately (20-/28-pin products only)

**Note:** Holding the DBG pin Low for an additional 5000 (minimum) clock cycles after reset (making sure to account for any specified frequency error if using an internal oscillator) prevents a false interpretation of an Autobaud sequence (see the <u>OCD Auto-Baud Detector/Generator</u> section on page 183).

|                                                        | V <sub>DE</sub>                                                                                                                                                                                          | ) = 2.7 V to 3                                                                                                                                                                                                      | 3.6 V                                                                                                                                                                                                                                                   |                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                              |                                                                                                                                                                                                          |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                         | Units                                                                                                                                                                                            | Conditions                                                                                                                                                                                                                                                                                                                      |

| ADC Internal Ref-<br>erence Supply Cur-<br>rent        | 0                                                                                                                                                                                                        |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                         | μA                                                                                                                                                                                               | See Note 4.                                                                                                                                                                                                                                                                                                                     |

| Comparator sup-<br>ply Current                         | 150                                                                                                                                                                                                      | 180                                                                                                                                                                                                                 | 190                                                                                                                                                                                                                                                     | μA                                                                                                                                                                                               | See Note 4.                                                                                                                                                                                                                                                                                                                     |

| Low-Power Opera-<br>tional Amplifier<br>Supply Current | 3                                                                                                                                                                                                        | 5                                                                                                                                                                                                                   | 5                                                                                                                                                                                                                                                       | μA                                                                                                                                                                                               | Driving a high-impedance load                                                                                                                                                                                                                                                                                                   |

| Temperature Sen-<br>sor Supply Current                 | 60                                                                                                                                                                                                       |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                         | μA                                                                                                                                                                                               | See Note 4.                                                                                                                                                                                                                                                                                                                     |

| Band Gap Supply                                        | 320                                                                                                                                                                                                      | 480                                                                                                                                                                                                                 | 500                                                                                                                                                                                                                                                     | μA                                                                                                                                                                                               | For 20-/28-pin devices.                                                                                                                                                                                                                                                                                                         |

| Current                                                |                                                                                                                                                                                                          |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                         |                                                                                                                                                                                                  | For 8-pin devices.                                                                                                                                                                                                                                                                                                              |

|                                                        | ADC Internal Ref-<br>erence Supply Cur-<br>rent<br>Comparator sup-<br>ply Current<br>Low-Power Opera-<br>tional Amplifier<br>Supply Current<br>Temperature Sen-<br>sor Supply Current<br>Band Gap Supply | ParameterTypical1ADC Internal Ref-<br>erence Supply Cur-<br>rent0Comparator sup-<br>ply Current150Low-Power Opera-<br>tional Amplifier<br>Supply Current3Temperature Sen-<br>sor Supply Current60Band Gap Supply320 | ParameterTypical1Maximum<br>Std Temp2ADC Internal Ref-<br>erence Supply Cur-<br>rent0150180Comparator sup-<br>ply Current150180Low-Power Opera-<br>tional Amplifier<br>Supply Current35Temperature Sen-<br>sor Supply Current60180Band Gap Supply320480 | ADC Internal Ref-<br>erence Supply Cur-<br>rent<br>Comparator sup-<br>ply Current<br>Low-Power Opera-<br>Supply Current<br>Temperature Sen-<br>sor Supply Current<br>Band Gap Supply 320 480 500 | ParameterTypical <sup>1</sup> Maximum<br>Std Temp <sup>2</sup> Maximum<br>Ext Temp <sup>3</sup> UnitsADC Internal Ref-<br>erence Supply Cur-<br>rent0μAComparator sup-<br>ply Current150180190μALow-Power Opera-<br>tional Amplifier<br>Supply Current355μATemperature Sen-<br>sor Supply Current60μABand Gap Supply320480500μA |

#### Table 132. Power Consumption (Continued)

Notes:

1. Typical conditions are defined as  $V_{DD} = 3.3 V$  and  $+30^{\circ}C$ .

2. Standard temperature is defined as  $T_A = 0^{\circ}C$  to +70°C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

3. Extended temperature is defined as  $T_A = -40^{\circ}$ C to +105°C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

4. For this block to operate, the bandgap circuit is automatically turned on and must be added to the total supply current. This bandgap current is only added once, regardless of how many peripherals are using it.

|                     |                          | T <sub>A</sub> = - | = 2.7 V to<br>-40°C to +<br>otherwise | -105°C      |       |                                                                                            |

|---------------------|--------------------------|--------------------|---------------------------------------|-------------|-------|--------------------------------------------------------------------------------------------|

| Symbol              | Parameter                | Minimum            | Typical                               | Maximum     | Units | Conditions                                                                                 |

| F <sub>WDT</sub>    | WDT Oscillator Frequency |                    | 10                                    |             | kHz   |                                                                                            |

| F <sub>WDT</sub>    | WDT Oscillator Error     |                    |                                       | <u>+</u> 50 | %     |                                                                                            |

| T <sub>WDTCAL</sub> | WDT Calibrated Time-out  | 0.98               | 1                                     | 1.02        | S     | V <sub>DD</sub> = 3.3V;<br>T <sub>A</sub> = 30°C                                           |

|                     |                          | 0.70               | 1                                     | 1.30        | S     | $V_{DD} = 2.7 V \text{ to } 3.6 V$<br>$T_A = 0^{\circ}C \text{ to } 70^{\circ}C$           |

|                     |                          | 0.50               | 1                                     | 1.50        | S     | $V_{DD} = 2.7 V \text{ to } 3.6 V$<br>$T_A = -40^{\circ}\text{C to } +105^{\circ}\text{C}$ |

### Table 137. Watchdog Timer Electrical Characteristics and Timing

#### Table 138. Non-Volatile Data Storage

|                        |         | = 2.7 V to<br>-40°C to + |         |        |                                           |  |

|------------------------|---------|--------------------------|---------|--------|-------------------------------------------|--|

| Parameter              | Minimum | Typical                  | Maximum | Units  | Notes                                     |  |

| NVDS Byte Read Time    | 34      | _                        | 519     | μs     | With system clock at 20MHz                |  |

| NVDS Byte Program Time | 0.171   | _                        | 39.7    | ms     | With system clock at 20MHz                |  |

| Data Retention         | 100     | _                        | -       | years  | 25°C                                      |  |

| Endurance              | 160,000 | _                        | _       | cycles | Cumulative write cycles for entire memory |  |

|                          |                                                                | T <sub>A</sub> :        | = 3.0 V to<br>= 0°C to +7<br>otherwise | ′0°C       |                                |                                                                                                |  |

|--------------------------|----------------------------------------------------------------|-------------------------|----------------------------------------|------------|--------------------------------|------------------------------------------------------------------------------------------------|--|

| Symbol                   | Parameter                                                      | Minimum Typical Maximum |                                        | Units      | Conditions                     |                                                                                                |  |

|                          | Resolution                                                     | 10                      |                                        | _          | bits                           |                                                                                                |  |

|                          | Differential Nonlinearity (DNL)                                | -1.0                    | -                                      | 1.0        | LSB <sup>3</sup>               | External V <sub>REF</sub> = 2.0 V;<br>R <sub>S</sub> $\leftarrow$ 3.0 k $\Omega$               |  |

|                          | Integral Nonlinearity (INL)                                    | -3.0                    | -                                      | 3.0        | LSB <sup>3</sup>               | External V <sub>REF</sub> = 2.0 V;<br>R <sub>S</sub> $\leftarrow$ 3.0 k $\Omega$               |  |

|                          | Offset Error with Calibra-<br>tion                             |                         | <u>+</u> 1                             |            | LSB <sup>3</sup>               |                                                                                                |  |

|                          | Absolute Accuracy with Calibration                             |                         | <u>+</u> 3                             |            | LSB <sup>3</sup>               |                                                                                                |  |

| V <sub>REF</sub>         | Internal Reference Volt-<br>age                                | 1.0<br>2.0              | 1.1<br>2.2                             | 1.2<br>2.4 | V                              | REFSEL=01<br>REFSEL=10                                                                         |  |

| V <sub>REF</sub>         | Internal Reference Varia-<br>tion with Temperature             |                         | <u>+</u> 1.0                           |            | %                              | Temperature variation with $V_{DD} = 3.0$                                                      |  |

| V <sub>REF</sub>         | Internal Reference Volt-<br>age Variation with V <sub>DD</sub> |                         | <u>+</u> 0.5                           |            | %                              | Supply voltage varia-<br>tion with $T_A = 30^{\circ}C$                                         |  |

| R <sub>RE-</sub><br>FOUT | Reference Buffer Output<br>Impedance                           |                         | 850                                    |            | W                              | When the internal ref-<br>erence is buffered and<br>driven out to the VREF<br>pin (REFOUT = 1) |  |

|                          | Single-Shot Conversion<br>Time                                 | -                       | 5129                                   | _          | Sys-<br>tem<br>clock<br>cycles | All measurements but temperature sensor                                                        |  |

|                          |                                                                |                         | 10258                                  |            |                                | Temperature sensor measurement                                                                 |  |

### Table 139. Analog-to-Digital Converter Electrical Characteristics and Timing

Notes:

1. Analog source impedance affects the ADC offset voltage (because of pin leakage) and input settling time.

2. Devices are factory calibrated at  $V_{DD}$  = 3.3V and  $T_A$  = +30°C, so the ADC is maximally accurate under these conditions.

3. LSBs are defined assuming 10-bit resolution.

4. This is the maximum recommended resistance seen by the ADC input pin.

5. The input impedance is inversely proportional to the system clock frequency.

|                   |                   | V <sub>DD</sub> | = 2.7 V to   |            |       |                                                                             |  |

|-------------------|-------------------|-----------------|--------------|------------|-------|-----------------------------------------------------------------------------|--|

| Symbol            | Parameter         | Minimum         | Typical      | Maximum    | Units | Conditions                                                                  |  |

| T <sub>AERR</sub> | Temperature Error |                 | <u>+</u> 0.5 | <u>+</u> 2 | °C    | Over the range +20°C to +30°C (as mea-<br>sured by ADC). <sup>1</sup>       |  |

|                   |                   |                 | <u>+</u> 1   | <u>+</u> 5 | °C    | Over the range +0°C<br>to +70°C (as mea-<br>sured by ADC).                  |  |

|                   |                   |                 | <u>+</u> 2   | <u>+</u> 7 | °C    | Over the range +0°C<br>to +105°C (as mea-<br>sured by ADC).                 |  |

|                   |                   |                 | <u>+</u> 7   |            | °C    | Over the range –40°C<br>to +105°C (as mea-<br>sured by ADC).                |  |

| t <sub>WAKE</sub> | Wakeup Time       |                 | 80           | 100        | μs    | Time required for Tem<br>perature Sensor to<br>stabilize after<br>enabling. |  |

#### Table 142. Temperature Sensor Electrical Characteristics

Note: Devices are factory calibrated at for maximal accuracy between +20°C and +30°C, so the sensor is maximally accurate in that range. User recalibration for a different temperature range is possible and increases accuracy near the new calibration point.

compare with carry - extended addressing 208 complement 210 complement carry flag 209 condition code 206 continuous conversion (ADC) 127 **CONTINUOUS** mode 87 control register definition, UART 110 Control Registers 15, 18 **COUNTER modes 87** CP 208 **CPC 208 CPCX 208** CPU and peripheral overview 4 CPU control instructions 209 **CPX 208** Customer Feedback Form 265

# D

DA 206, 208 data memory 17 DC characteristics 227 debugger, on-chip 180 **DEC 208** decimal adjust 208 decrement 208 decrement and jump non-zero 211 decrement word 208 **DECW 208** destination operand 207 device, port availability 36 DI 209 direct address 206 disable interrupts 209 DJNZ 211 dst 207

# Ε

EI 209 electrical characteristics 226 ADC 236 flash memory and timing 234 GPIO input data sample timing 240 Watchdog Timer 235, 238 enable interrupt 209 ER 206 extended addressing register 206 external pin reset 26 eZ8 CPU features 4 eZ8 CPU instruction classes 207 eZ8 CPU instruction notation 206 eZ8 CPU instruction set 204 eZ8 CPU instruction summary 212

## F

FCTL register 155, 161, 162 features, Z8 Encore! 1 first opcode map 224 FLAGS 207 flags register 207 flash controller 6 option bit address space 162 option bit configuration - reset 159 program memory address 0000H 162 program memory address 0001H 164 flash memory 146 arrangement 147 byte programming 151 code protection 149 configurations 146 control register definitions 153, 161 controller bypass 152 electrical characteristics and timing 234 flash control register 155, 161, 162 flash option bits 150 flash status register 155 flow chart 148 frequency high and low byte registers 157 mass erase 152 operation 147 operation timing 149 page erase 152 page select register 156, 157 FPS register 156, 157 FSTAT register 155

CONTINUOUS mode 72, 87 COUNTER mode 73, 74 **COUNTER** modes 87 GATED mode 82, 88 ONE-SHOT mode 71, 87 operating mode 71 PWM mode 76, 77, 87, 88 reading the timer count values 84 reload high and low byte registers 91 timer control register definitions 85 timer output signal operation 84 timers 0-3 control registers 85, 86 high and low byte registers 89, 92 TM 209 TMX 209 transmit IrDA data 121 transmitting UART data-polled method 101 transmitting UART dat-interrupt-driven method 102 **TRAP 211**

# U

UART 6 architecture 99 baud rate generator 110 baud rates table 118 control register definitions 110 controller signals 10 interrupts 108 multiprocessor mode 105 receiving data using interrupt-driven method 104 receiving data using the polled method 103 transmitting data usin the interrupt-driven method 102 transmitting data using the polled method 101 x baud rate high and low registers 117 x control 0 and control 1 registers 110 x status 0 and status 1 registers 114, 115 UxBRH register 117 UxBRL register 117

UxCTL0 register 111, 117 UxCTL1 register 112 UxRXD register 116 UxSTAT0 register 114 UxSTAT1 register 115 UxTXD register 116

## V

vector 207 Voltage Brownout reset (VBR) 25

## W

Watchdog Timer approximate time-out delay 93 approximate time-out delays 140 CNTL 25 control register 96 electrical characteristics and timing 235, 238 interrupt in normal operation 94 interrupt in STOP mode 94 operation 140 refresh 94, 210 reload unlock sequence 95 reload upper, high and low registers 97 reset 26 reset in normal operation 95 reset in STOP mode 95 time-out response 94 WDTCTL register 30, 96, 141, 196 WDTH register 97 WDTL register 98 working register 206 working register pair 206 WTDU register 97

## Χ

X 207 XOR 210 XORX 210 263