Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Active                                                    |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT           |

| Number of I/O              | 6                                                         |

| Program Memory Size        | 1KB (1K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | 16 x 8                                                    |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | ·                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                             |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f011asb020sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

| Table 119. | Additional Symbols 207                                                |

|------------|-----------------------------------------------------------------------|

| Table 120. | Arithmetic Instructions                                               |

| Table 121. | Bit Manipulation Instructions                                         |

| Table 122. | Block Transfer Instructions                                           |

| Table 123. | CPU Control Instructions                                              |

| Table 124. | Load Instructions                                                     |

| Table 125. | Logical Instructions                                                  |

| Table 126. | Program Control Instructions 211                                      |

| Table 127. | Rotate and Shift Instructions 211                                     |

| Table 128. | eZ8 CPU Instruction Summary 212                                       |

| Table 129. | Opcode Map Abbreviations 223                                          |

| Table 130. | Absolute Maximum Ratings 226                                          |

| Table 131. | DC Characteristics                                                    |

| Table 132. | Power Consumption                                                     |

| Table 133. | AC Characteristics                                                    |

| Table 134. | Internal Precision Oscillator Electrical Characteristics              |

| Table 135. | Power-On Reset and Voltage Brown-Out Electrical Characteristics       |

|            | and Timing 233                                                        |

| Table 136. | Flash Memory Electrical Characteristics and Timing 234                |

| Table 137. | Watchdog Timer Electrical Characteristics and Timing 235              |

| Table 138. | Non-Volatile Data Storage                                             |

| Table 139. | Analog-to-Digital Converter Electrical Characteristics and Timing 236 |

| Table 140. | Low Power Operational Amplifier Electrical Characteristics 238        |

| Table 141. | Comparator Electrical Characteristics                                 |

| Table 142. | Temperature Sensor Electrical Characteristics                         |

| Table 143. | GPIO Port Input Timing                                                |

| Table 144. | GPIO Port Output Timing                                               |

| Table 145. | On-Chip Debugger Timing                                               |

| Table 146. | UART Timing With CTS                                                  |

| Table 147. | UART Timing Without CTS 244                                           |

| Table 148. | Z8 Encore! XP F082A Series Ordering Matrix                            |

### **Internal Precision Oscillator**

The internal precision oscillator (IPO) is a trimmable clock source that requires no external components.

### **Temperature Sensor**

The optional temperature sensor produces an analog output proportional to the device temperature. This signal can be sent to either the ADC or the analog comparator.

### **Analog Comparator**

The analog comparator compares the signal at an input pin with either an internal programmable voltage reference or a second input pin. The comparator output can be used to drive either an output pin or to generate an interrupt.

### **External Crystal Oscillator**

The crystal oscillator circuit provides highly accurate clock frequencies with the use of an external crystal, ceramic resonator or RC network.

### Low Voltage Detector

The low voltage detector (LVD) is able to generate an interrupt when the supply voltage drops below a user-programmable level. The LVD is available on 8-pin devices only.

### **On-Chip Debugger**

The Z8 Encore! XP F082A Series products feature an integrated on-chip debugger (OCD) accessed via a single-pin interface. The OCD provides a rich-set of debugging capabilities, such as reading and writing registers, programming Flash memory, setting breakpoints and executing code.

### **Universal Asynchronous Receiver/Transmitter**

The full-duplex universal asynchronous receiver/transmitter (UART) is included in all Z8 Encore! XP package types. The UART supports 8- and 9-bit data modes and selectable parity. The UART also supports multi-drop address processing in hardware. The UART baud rate generator (BRG) can be configured and used as a basic 16-bit timer.

### Timers

Two enhanced 16-bit reloadable timers can be used for timing/counting events or for motor control operations. These timers provide a 16-bit programmable reload counter and

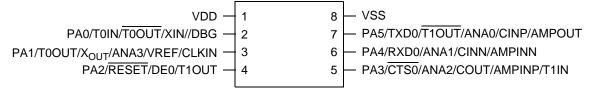

Figure 2. Z8F08xA, Z8F04xA, Z8F02xA and Z8F01xA in 8-Pin SOIC, QFN/MLF-S, or PDIP Package

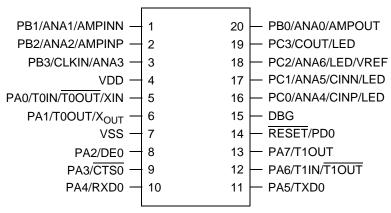

Figure 3. Z8F08xA, Z8F04xA, Z8F02xA and Z8F01xA in 20-Pin SOIC, SSOP or PDIP Package

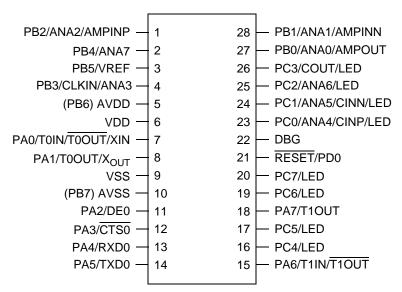

Figure 4. Z8F08xA, Z8F04xA, Z8F02xA and Z8F01xA in 28-Pin SOIC, SSOP or PDIP Package

| Table 4. Pin Characteristics (8-Pin Devices) |           |                                                                         |                                       |                    |                                                      |                              |                                                      |                                       |

|----------------------------------------------|-----------|-------------------------------------------------------------------------|---------------------------------------|--------------------|------------------------------------------------------|------------------------------|------------------------------------------------------|---------------------------------------|

| Symbol<br>Mnemonic                           | Direction | Reset<br>Direction                                                      | Active<br>Low<br>or<br>Active<br>High | Tristate<br>Output | Internal<br>Pull-up or<br>Pull-down                  | Schmitt-<br>Trigger<br>Input | Open Drain<br>Output                                 | 5V<br>Tolerance                       |

| PA0/DBG                                      | I/O       | I (but can<br>change<br>during<br>reset if key<br>sequence<br>detected) | N/A                                   | Yes                | Programma-<br>ble<br>Pull-up                         | Yes                          | Yes,<br>Programma-<br>ble                            | Yes,<br>unless<br>pull-ups<br>enabled |

| PA1                                          | I/O       | I                                                                       | N/A                                   | Yes                | Programma-<br>ble<br>Pull-up                         | Yes                          | Yes,<br>Programma-<br>ble                            | Yes,<br>unless<br>pull-ups<br>enabled |

| RESET/<br>PA2                                | I/O       | I/O<br>(defaults<br>to RESET)                                           | Low (in<br>Reset<br>mode)             | Yes                | Programma-<br>ble for PA2;<br>always on for<br>RESET | Yes                          | Programma-<br>ble for PA2;<br>always on for<br>RESET | Yes,<br>unless<br>pull-ups<br>enabled |

| PA[5:3]                                      | I/O       | I                                                                       | N/A                                   | Yes                | Programma-<br>ble<br>Pull-up                         | Yes                          | Yes,<br>Programma-<br>ble                            | Yes,<br>unless<br>pull-ups<br>enabled |

| $V_{DD}$                                     | N/A       | N/A                                                                     | N/A                                   | N/A                | N/A                                                  | N/A                          | N/A                                                  | N/A                                   |

| V <sub>SS</sub>                              | N/A       | N/A                                                                     | N/A                                   | N/A                | N/A                                                  | N/A                          | N/A                                                  | N/A                                   |

| Program Memory Address (Hex)              | Function                     |

|-------------------------------------------|------------------------------|

| 0002–0003                                 | Reset Vector                 |

| 0004–0005                                 | WDT Interrupt Vector         |

| 0006–0007                                 | Illegal Instruction Trap     |

| 0008–0037                                 | Interrupt Vectors*           |

| 0038–0039                                 | Reserved                     |

| 003A-003D                                 | Oscillator Fail Trap Vectors |

| 003E-03FF                                 | Program Memory               |

| Note: *See Table 32 on page 56 for a list | t of the interrupt vectors.  |

| Table 5. Z8 Encore! XP F082A Series P | Program Memory Maps (Continued) |

|---------------------------------------|---------------------------------|

|---------------------------------------|---------------------------------|

### **Data Memory**

The Z8 Encore! XP F082A Series does not use the eZ8 CPU's 64 KB Data Memory address space.

### **Flash Information Area**

Table 6 describes the Z8 Encore! XP F082A Series Flash Information Area. This 128B Information Area is accessed by setting bit 7 of the Flash Page Select Register to 1. When access is enabled, the Flash Information Area is mapped into the Program Memory and overlays the 128 bytes at addresses FE00H to FF7FH. When the Information Area access is enabled, all reads from these Program Memory addresses return the Information Area data rather than the Program Memory data. Access to the Flash Information Area is read-only.

Table 6. Z8 Encore! XP F082A Series Flash Memory Information Area Map

| Program Memory |                                                                                           |

|----------------|-------------------------------------------------------------------------------------------|

| Address (Hex)  | Function                                                                                  |

| FE00–FE3F      | Zilog Option Bits/Calibration Data                                                        |

| FE40-FE53      | Part Number<br>20-character ASCII alphanumeric code<br>Left-justified and filled with FFH |

| FE54–FE5F      | Reserved                                                                                  |

| FE60–FE7F      | Zilog Calibration Data                                                                    |

| FE80–FFFF      | Reserved                                                                                  |

**Note:** Asserting any power control bit disables the targeted block regardless of any enable bits contained in the target block's control registers.

>

| Port                | Pin | Mnemonic                           | Alternate Function Description            | Alternate Function<br>Set Register AFS1 |

|---------------------|-----|------------------------------------|-------------------------------------------|-----------------------------------------|

| Port C <sup>5</sup> | PC0 | Reserved                           |                                           | AFS1[0]: 0                              |

|                     |     | ANA4/CINP                          | ADC or Comparator Input                   | AFS1[0]: 1                              |

|                     | PC1 | Reserved                           |                                           | AFS1[1]: 0                              |

|                     |     | ANA5/CINN                          | ADC or Comparator Input                   | AFS1[1]: 1                              |

|                     | PC2 | Reserved                           |                                           | AFS1[2]: 0                              |

|                     |     | ANA6/V <sub>REF</sub> <sup>4</sup> | ADC Analog Input or ADC Voltage Reference | AFS1[2]: 1                              |

|                     | PC3 | COUT                               | Comparator Output                         | AFS1[3]: 0                              |

|                     |     | Reserved                           |                                           | AFS1[3]: 1                              |

|                     | PC4 | Reserved                           |                                           | AFS1[4]: 0                              |

|                     |     |                                    |                                           | AFS1[4]: 1                              |

|                     | PC5 | Reserved                           |                                           | AFS1[5]: 0                              |

|                     |     |                                    |                                           | AFS1[5]: 1                              |

|                     | PC6 | Reserved                           |                                           | AFS1[6]: 0                              |

|                     |     |                                    |                                           | AFS1[6]: 1                              |

|                     | PC7 | Reserved                           |                                           | AFS1[7]: 0                              |

|                     |     |                                    |                                           | AFS1[7]: 1                              |

| Port D <sup>6</sup> | PD0 | RESET                              | External Reset                            | N/A                                     |

#### Table 15. Port Alternate Function Mapping (Non 8-Pin Parts) (Continued)

Notes:

2. Whether PA0/PA6 takes on the timer input or timer output complement function depends on the timer configuration. See the <u>Timer Pin Signal Operation</u> section on page 84 for details.

Because there are at most two choices of alternate function for any pin of Port B, the Alternate Function Set Register AFS2 is not used to select the function. Alternate function selection must also be enabled. See the <u>Port</u> <u>A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

4. V<sub>REF</sub> is available on PB5 in 28-pin products and on PC2 in 20-pin parts.

Because there are at most two choices of alternate function for any pin of Port C, the Alternate Function Set Register AFS2 is not used to select the function. Alternate function selection must also be enabled. See the <u>Port</u> <u>A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

6. Because there is only a single alternate function for the Port PD0 pin, the Alternate Function Set registers are not implemented for Port D. Enabling alternate function selections automatically enables the associated alternate function. See the Port A–D Alternate Function Subregisters (PxAF) section on page 47 for details.

Because there is only a single alternate function for each Port A pin, the Alternate Function Set registers are not implemented for Port A. Enabling alternate function selections automatically enables the associated alternate function. See the <u>Port A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

## Architecture

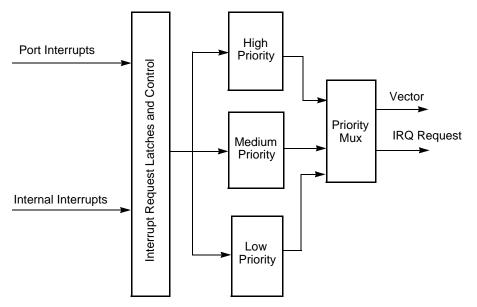

Figure 8 displays the interrupt controller block diagram.

Figure 8. Interrupt Controller Block Diagram

## Operation

This section describes the operational aspects of the following functions.

Master Interrupt Enable: see page 57

Interrupt Vectors and Priority: see page 58

Interrupt Assertion: see page 58

Software Interrupt Assertion: see page 59

Watchdog Timer Interrupt Assertion: see page 59

### Master Interrupt Enable

The master interrupt enable bit (IRQE) in the Interrupt Control Register globally enables and disables interrupts. Interrupts are globally enabled by any of the following actions:

- Execution of an EI (Enable Interrupt) instruction

- Execution of an IRET (Return from Interrupt) instruction

| Bit           | Description (Continued)                                                  |

|---------------|--------------------------------------------------------------------------|

| [4]<br>U0RENL | UART 0 Receive Interrupt Request Enable Low Bit                          |

| [3]<br>U0TENL | UART 0 Transmit Interrupt Request Enable Low Bit                         |

| [2:1]         | <b>Reserved</b><br>These bits are reserved and must be programmed to 00. |

| [0]<br>ADCENL | ADC Interrupt Request Enable Low Bit                                     |

#### **IRQ1 Enable High and Low Bit Registers**

Table 41 describes the priority control for IRQ1. The IRQ1 Enable High and Low Bit registers, shown in Tables 41 and 42, form a priority-encoded enabling for interrupts in the Interrupt Request 1 Register.

| IRQ1ENH[x]                           | IRQ1ENL[x] | Priority | Description |  |  |  |

|--------------------------------------|------------|----------|-------------|--|--|--|

| 0                                    | 0          | Disabled | Disabled    |  |  |  |

| 0                                    | 1          | Level 1  | Low         |  |  |  |

| 1                                    | 0          | Level 2  | Medium      |  |  |  |

| 1                                    | 1          | Level 3  | High        |  |  |  |

| Note: x indicates register bits 0–7. |            |          |             |  |  |  |

#### Table 41. IRQ1 Enable and Priority Encoding

- Set the Capture edge (rising or falling) for the Timer Input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the Compare value.

- 4. Enable the timer interrupt, if appropriate and set the timer interrupt priority by writing to the relevant interrupt registers.By default, the timer interrupt are generated for both input capture and reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the reload event by setting TICONFIG field of the TxCTL0 Register.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control Register to enable the timer.

- 7. Counting begins on the first appropriate transition of the Timer Input signal. No interrupt is generated by this first edge.

In CAPTURE/COMPARE Mode, the elapsed time from timer start to Capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

#### **Reading the Timer Count Values**

The current count value in the timers can be read while counting (enabled). This capability has no effect on timer operation. When the timer is enabled and the Timer High Byte Register is read, the contents of the Timer Low Byte Register are placed in a holding register. A subsequent read from the Timer Low Byte Register returns the value in the holding register. This operation allows accurate reads of the full 16-bit timer count value while enabled. When the timers are not enabled, a read from the Timer Low Byte Register returns the actual value in the counter.

#### **Timer Pin Signal Operation**

The timer output function is a GPIO port pin alternate function. The Timer Output is toggled every time the counter is reloaded. The timer input can be used as a selectable counting source. It shares the same pin as the complementary timer output. When selected by the GPIO Alternate Function registers, this pin functions as a timer input in all modes except for the DUAL PWM OUTPUT mode. For this mode, there is no timer input available.

### **Timer Control Register Definitions**

This section defines the features of the following Timer Control registers.

<u>Timer 0–1 Control Registers</u>: see page 85

<u>Timer 0–1 High and Low Byte Registers</u>: see page 89

Timer Reload High and Low Byte Registers: see page 91

Timer 0-1 PWM High and Low Byte Registers: see page 92

### Timer 0–1 Control Registers

The Timer Control registers are 8-bit read/write registers that control the operation of their associated counter/timers.

#### Time 0–1 Control Register 0

The Timer Control Register 0 (TxCTL0) and Timer Control Register 1 (TxCTL1), shown in Table 50, determine the timer operating mode. These registers each include a programmable PWM deadband delay, two bits to configure timer interrupt definition and a status bit to identify if the most recent timer interrupt is caused by an input capture event.

| Bit            | 7                                                                                                                                                                                                                                                                                                                                      | 6           | 5    | 4        | 3   | 2    | 1   | 0      |  |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------|----------|-----|------|-----|--------|--|

| Field          | TMODEHI                                                                                                                                                                                                                                                                                                                                | TICO        | NFIG | Reserved |     | PWMD |     | INPCAP |  |

| RESET          | 0                                                                                                                                                                                                                                                                                                                                      | 0           | 0    | 0        | 0   | 0    | 0   | 0      |  |

| R/W            | R/W                                                                                                                                                                                                                                                                                                                                    | R/W         | R/W  | R/W      | R/W | R/W  | R/W | R      |  |

| Address        | F06H, F0EH                                                                                                                                                                                                                                                                                                                             |             |      |          |     |      |     |        |  |

| Bit            | Descript                                                                                                                                                                                                                                                                                                                               | Description |      |          |     |      |     |        |  |

| [7]<br>TMODEHI | <b>Timer Mode High Bit</b><br>This bit, along with the TMODE field in the TxCTL1 Register, determines the operating mode of the timer. This bit is the most significant bit of the Timer mode selection value. See the description of the <u>Timer 0–1 Control Register 1 (TxCTL1)</u> for details about the full timer mode decoding. |             |      |          |     |      |     |        |  |

Table 50. Timer 0–1 Control Register 0 (TxCTL0)

The UART data rate is calculated using the following equation:

UART Baud Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

For a given UART data rate, calculate the integer baud rate divisor value using the following equation:

UART Baud Rate Divisor Value (BRG) = Round  $\left(\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Data Rate (bits/s)}}\right)$

The baud rate error relative to the acceptable baud rate is calculated using the following equation:

UART Baud Rate Error (%) =  $100 \times \left(\frac{\text{Actual Data Rate} - \text{Desired Data Rate}}{\text{Desired Data Rate}}\right)$

For reliable communication, the UART baud rate error must never exceed 5 percent. Table 72 provides information about the data rate errors for popular baud rates and commonly used crystal oscillator frequencies.

|                          | 10.0MHz Syste            | em Clock             |              | 5.                       | 5296MHz Sys              | tem Clock            |              |

|--------------------------|--------------------------|----------------------|--------------|--------------------------|--------------------------|----------------------|--------------|

| Acceptable<br>Rate (kHz) | BRG Divisor<br>(Decimal) | Actual Rate<br>(kHz) | Error<br>(%) | Acceptable<br>Rate (kHz) | BRG Divisor<br>(Decimal) | Actual Rate<br>(kHz) | Error<br>(%) |

| 1250.0                   | N/A                      | N/A                  | N/A          | 1250.0                   | N/A                      | N/A                  | N/A          |

| 625.0                    | 1                        | 625.0                | 0.00         | 625.0                    | N/A                      | N/A                  | N/A          |

| 250.0                    | 3                        | 208.33               | -16.67       | 250.0                    | 1                        | 345.6                | 38.24        |

| 115.2                    | 5                        | 125.0                | 8.51         | 115.2                    | 3                        | 115.2                | 0.00         |

| 57.6                     | 11                       | 56.8                 | -1.36        | 57.6                     | 6                        | 57.6                 | 0.00         |

| 38.4                     | 16                       | 39.1                 | 1.73         | 38.4                     | 9                        | 38.4                 | 0.00         |

| 19.2                     | 33                       | 18.9                 | 0.16         | 19.2                     | 18                       | 19.2                 | 0.00         |

| 9.60                     | 65                       | 9.62                 | 0.16         | 9.60                     | 36                       | 9.60                 | 0.00         |

| 4.80                     | 130                      | 4.81                 | 0.16         | 4.80                     | 72                       | 4.80                 | 0.00         |

| 2.40                     | 260                      | 2.40                 | -0.03        | 2.40                     | 144                      | 2.40                 | 0.00         |

| 1.20                     | 521                      | 1.20                 | -0.03        | 1.20                     | 288                      | 1.20                 | 0.00         |

| 0.60                     | 1042                     | 0.60                 | -0.03        | 0.60                     | 576                      | 0.60                 | 0.00         |

| 0.30                     | 2083                     | 0.30                 | 0.2          | 0.30                     | 1152                     | 0.30                 | 0.00         |

| 3 5                      | 705/5MH7 Sv              | stom Clock           | <u> </u>     | 1                        | 8/32MHz Sve              | tom Clock            |              |

#### Table 72. UART Baud Rates

3.579545 MHz System Clock

1.8432MHz System Clock

| #3 | #3 | #3 | #3 |

|----|----|----|----|

4. Round the result and discard the least significant two bytes (equivalent to dividing by  $2^{16}$ ).

| #3     | #3     | #3   | #3   |

|--------|--------|------|------|

| _      |        |      |      |

| 0x00   | 0x00   | 0x80 | 0x00 |

| _      |        |      |      |

|        |        |      |      |

| #4 MSB | #4 LSB |      |      |

5. Determine the sign of the gain correction factor using the sign bits from <u>Step 2</u>. If the offset-corrected ADC value *and* the gain correction word both have the same sign, then the factor is positive and remains unchanged. If they have differing signs, then the factor is negative and must be multiplied by -1.

| #5 MSB | #5 LSB |

|--------|--------|

|--------|--------|

6. Add the gain correction factor to the original offset corrected value.

| #5 MSB | #5 LSB |

|--------|--------|

|        |        |

| +      |        |

| #1 MSB | #1 LSB |

|        |        |

| =      |        |

| #6 MSB | #6 LSB |

| L      |        |

7. Shift the result to the right, using the sign bit determined in <u>Step 1</u>, to allow for the detection of computational overflow.

| $S \rightarrow \#6 MSB \#6 LSB$ |

|---------------------------------|

|---------------------------------|

132

| Bit   | Description (Continued)                                                                                         |

|-------|-----------------------------------------------------------------------------------------------------------------|

| [2:1] | Reserved                                                                                                        |

|       | These bits are reserved and must be undefined.                                                                  |

| [0]   | Overflow Status                                                                                                 |

| OVF   | 0 = A hardware overflow did not occur in the ADC for the current sample.                                        |

|       | 1= A hardware overflow did occur in the ADC for the current sample, therefore the current<br>sample is invalid. |

## **Temperature Sensor**

The on-chip Temperature Sensor allows you to measure temperature on the die with either the on-board ADC or on-board comparator. This block is factory calibrated for in-circuit software correction. Uncalibrated accuracy is significantly worse, therefore the temperature sensor is not recommended for uncalibrated use.

### **Temperature Sensor Operation**

The on-chip temperature sensor is a Proportional to Absolute Temperature (PTAT) topology. A pair of Flash option bytes contain the calibration data. The temperature sensor can be disabled by a bit in the <u>Power Control Register 0</u> section on page 33 to reduce power consumption.

The temperature sensor can be directly read by the ADC to determine the absolute value of its output. The temperature sensor output is also available as an input to the comparator for threshold type measurement determination. The accuracy of the sensor when used with the comparator is substantially less than when measured by the ADC.

If the temperature sensor is routed to the ADC, the ADC must be configured in unity-gain buffered mode (for details, see the <u>Input Buffer Stage</u> section on page 133). The value read back from the ADC is a signed number, although it is always positive.

The sensor is factory-trimmed through the ADC using the external 2.0 V reference. Unless the sensor is retrimmed for use with a different reference, it is most accurate when used with the external 2.0 V reference.

Because this sensor is an on-chip sensor, Zilog recommends that the user account for the difference between ambient and die temperature when inferring ambient temperature conditions.

During normal operation, the die undergoes heating that causes a mismatch between the ambient temperature and that measured by the sensor. For best results, the Z8 Encore! XP device must be placed into STOP Mode for sufficient time such that the die and ambient temperatures converge (this time is dependent on the thermal design of the system). The temperature sensor measurement must then be made immediately after recovery from STOP Mode.

The following equation defines the transfer function between the temperature sensor output voltage and the die temperature. This is needed for comparator threshold measurements.

$V = 0.01 \times T + 0.65$

148

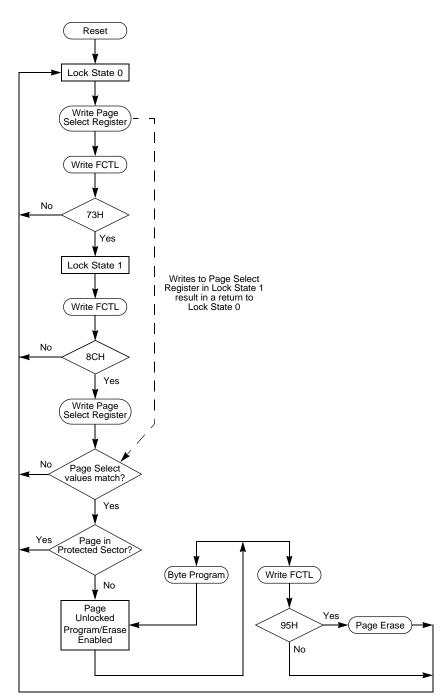

Figure 22 displays a basic Flash Controller flow. The following subsections provide details about the various operations displayed in Figure 22.

Figure 22. Flash Controller Operation Flow Chart

#### 150

#### Table 79. Flash Code Protection Using the Flash Option Bits

| FWP | Flash Code Protection Description                                                                                                                                                                     |  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0   | Programming and erasing disabled for all of Flash Program Mem-<br>ory. In user code programming, Page Erase and Mass Erase are all<br>disabled. Mass Erase is available through the On-Chip Debugger. |  |

| 1   | Programming, Page Erase and Mass Erase are enabled for all of Flash Program Memory.                                                                                                                   |  |

#### Flash Code Protection Using the Flash Controller

At Reset, the Flash Controller locks to prevent accidental program or erasure of the Flash memory. To program or erase the Flash memory, first write the Page Select Register with the target page. Unlock the Flash Controller by making two consecutive writes to the Flash Control Register with the values 73H and 8CH, sequentially. The Page Select Register must be rewritten with the target page. If the two Page Select writes do not match, the controller reverts to a locked state. If the two writes match, the selected page becomes active. See Figure 22 on page 148 for details.

After unlocking a specific page, you can enable either Page Program or Erase. Writing the value 95H causes a Page Erase only if the active page resides in a sector that is not protected. Any other value written to the Flash Control Register locks the Flash Controller. Mass Erase is not allowed in the user code but only in through the Debug Port.

After unlocking a specific page, you can also write to any byte on that page. After a byte is written, the page remains unlocked, allowing for subsequent writes to other bytes on the same page. Further writes to the Flash Control Register cause the active page to revert to a locked state.

#### **Sector-Based Flash Protection**

The final protection mechanism is implemented on a per-sector basis. The Flash memories of Z8 Encore! XP devices are divided into maximum number of 8 sectors. A sector is 1/8 of the total Flash memory size unless this value is smaller than the page size – in which case, the sector and page sizes are equal. On Z8 Encore! F082A Series devices, the sector size is varied according to the Flash memory configuration shown in <u>Table 78</u> on page 146.

The Flash Sector Protect Register can be configured to prevent sectors from being programmed or erased. After a sector is protected, it cannot be unprotected by user code. The Flash Sector Protect Register is cleared after reset, and any previously-written protection values are lost. User code must write this register in their initialization routine if they prefer to enable sector protection.

The Flash Sector Protect Register shares its Register File address with the Page Select Register. The Flash Sector Protect Register is accessed by writing the Flash Control Regis-

# Flash Option Bits

Programmable Flash option bits allow user configuration of certain aspects of Z8 Encore! XP F082A Series operation. The feature configuration data is stored in Flash program memory and loaded into holding registers during Reset. The features available for control through the Flash option bits include:

- Watchdog Timer time-out response selection-interrupt or system reset

- Watchdog Timer always on (enabled at Reset)

- The ability to prevent unwanted read access to user code in Program Memory

- The ability to prevent accidental programming and erasure of all or a portion of the user code in Program Memory

- Voltage Brown-Out configuration-always enabled or disabled during STOP Mode to reduce STOP Mode power consumption

- Oscillator mode selection-for high, medium and low power crystal oscillators, or external RC oscillator

- Factory trimming information for the internal precision oscillator and low voltage detection

- Factory calibration values for ADC, temperature sensor and Watchdog Timer compensation

- Factory serialization and randomized lot identifier (optional)

### Operation

This section describes the type and configuration of the programmable Flash option bits.

#### **Option Bit Configuration By Reset**

Each time the Flash option bits are programmed or erased, the device must be Reset for the change to take effect. During any reset operation (System Reset, Power-On Reset, or Stop Mode Recovery), the Flash option bits are automatically read from Flash program memory and written to the Option Configuration registers. The Option Configuration registers control the operation of the devices within the Z8 Encore! XP F082A Series. Option bit control is established before the device exits Reset and the eZ8 CPU begins code execution. The Option Configuration registers are not part of the Register File and are not accessible for read or write access.

| LVD Threshold (V)<br>Typical | Description                                                                                                                                  |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

|                              | Maximum LVD threshold                                                                                                                        |

|                              |                                                                                                                                              |

|                              |                                                                                                                                              |

|                              |                                                                                                                                              |

|                              |                                                                                                                                              |

|                              |                                                                                                                                              |

|                              |                                                                                                                                              |

|                              |                                                                                                                                              |

|                              |                                                                                                                                              |

|                              |                                                                                                                                              |

|                              | Default on Reset                                                                                                                             |

|                              | Delault off Reset                                                                                                                            |

|                              |                                                                                                                                              |

|                              |                                                                                                                                              |

|                              |                                                                                                                                              |

|                              |                                                                                                                                              |

|                              |                                                                                                                                              |

| 2.80                         |                                                                                                                                              |

| 2.75                         |                                                                                                                                              |

| 2.70                         |                                                                                                                                              |

| 2.70                         |                                                                                                                                              |

|                              | Minimum LVD threshold                                                                                                                        |

|                              | Typical   3.60   3.55   3.50   3.45   3.40   3.35   3.30   3.25   3.20   3.15   3.10   3.05   3.00   2.95   2.90   2.85   2.80   2.75   2.70 |

#### Table 94. LVD Trim Values

When selecting a new clock source, the system clock oscillator failure detection circuitry and the Watchdog Timer oscillator failure circuitry must be disabled. If SOFEN and WOFEN are not disabled prior to a clock switch-over, it is possible to generate an interrupt for a failure of either oscillator. The Failure detection circuitry can be enabled anytime after a successful write of OSCSEL in the OSCCTL Register.

The internal precision oscillator is enabled by default. If the user code changes to a different oscillator, it may be appropriate to disable the IPO for power savings. Disabling the IPO does not occur automatically.

#### **Clock Failure Detection and Recovery**

Should an oscillator or timer fail, there are methods of recovery, as this section describes.

#### System Clock Oscillator Failure

The Z8F04xA family devices can generate nonmaskable interrupt-like events when the primary oscillator fails. To maintain system function in this situation, the clock failure recovery circuitry automatically forces the Watchdog Timer oscillator to drive the system clock. The Watchdog Timer oscillator must be enabled to allow the recovery. Although this oscillator runs at a much slower speed than the original system clock, the CPU continues to operate, allowing execution of a clock failure vector and software routines that either remedy the oscillator failure or issue a failure alert. This automatic switch-over is not available if the Watchdog Timer oscillator is disabled, though it is not necessary to enable the Watchdog Timer reset function (see the <u>Watchdog Timer</u> chapter on page 93).

The primary oscillator failure detection circuitry asserts if the system clock frequency drops below  $1 \text{ kHz} \pm 50\%$ . If an external signal is selected as the system oscillator, it is possible that a very slow but nonfailing clock can generate a failure condition. Under these conditions, do not enable the clock failure circuitry (SOFEN must be deasserted in the OSCCTL Register).

#### Watchdog Timer Failure

In the event of a Watchdog Timer oscillator failure, a similar nonmaskable interrupt-like event is issued. This event does not trigger an attendant clock switch-over, but alerts the CPU of the failure. After a Watchdog Timer failure, it is no longer possible to detect a primary oscillator failure. The failure detection circuitry does not function if the Watchdog Timer is used as the system clock oscillator or if the Watchdog Timer oscillator has been disabled. For either of these cases, it is necessary to disable the detection circuitry by deasserting the WDFEN bit of the OSCCTL Register.

The Watchdog Timer oscillator failure detection circuit counts system clocks while looking for a Watchdog Timer clock. The logic counts 8004 system clock cycles before determining that a failure has occurred. The system clock rate determines the speed at which