# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT           |

| Number of I/O              | 17                                                        |

| Program Memory Size        | 1KB (1K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | 16 x 8                                                    |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f011ash020sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Reset Sources**

Table 9 lists the possible sources of a system reset.

| Table 9. Reset Sources and Resulting Reset Type |  |

|-------------------------------------------------|--|

| Operating Mode       | Reset Source                                          | Special Conditions                                                                            |

|----------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| NORMAL or HALT modes | Power-On Reset/Voltage Brown-<br>Out                  | Reset delay begins after supply voltage exceeds POR level.                                    |

|                      | Watchdog Timer time-out when configured for Reset     | None.                                                                                         |

|                      | RESET pin assertion                                   | All reset pulses less than three system clocks in width are ignored.                          |

|                      | On-Chip Debugger initiated Reset (OCDCTL[0] set to 1) | System Reset, except the On-Chip Debugger is unaffected by the reset.                         |

| STOP Mode            | Power-On Reset/Voltage Brown-<br>Out                  | Reset delay begins after supply voltage exceeds POR level.                                    |

|                      | RESET pin assertion                                   | All reset pulses less than the specified analog delay are ignored. See Table 131 on page 229. |

|                      | DBG pin driven Low                                    | None.                                                                                         |

## **Power-On Reset**

Z8 Encore! XP F082A Series devices contain an internal Power-On Reset circuit. The POR circuit monitors the supply voltage and holds the device in the Reset state until the supply voltage reaches a safe operating level. After the supply voltage exceeds the POR voltage threshold (VPOR), the device is held in the Reset state until the POR Counter has timed out. If the crystal oscillator is enabled by the option bits, this time-out is longer.

After the Z8 Encore! XP F082A Series device exits the Power-On Reset state, the eZ8 CPU fetches the Reset vector. Following Power-On Reset, the POR status bit in the Reset Status (RSTSTAT) Register is set to 1.

Figure 5 displays Power-On Reset operation. See Electrical Characteristics on page 221 for the POR threshold voltage (V<sub>POR</sub>).

| Port              | Pin | Mnemonic                      | Alternate Function<br>Description         | Alternate<br>Function Select<br>Register AFS1 | Alternate<br>Function<br>Select<br>Register<br>AFS2 |

|-------------------|-----|-------------------------------|-------------------------------------------|-----------------------------------------------|-----------------------------------------------------|

| Port A            | PA0 | TOIN                          | Timer 0 Input                             | AFS1[0]: 0                                    | AFS2[0]: 0                                          |

| <b>Port A</b> PAU |     | Reserved                      |                                           | AFS1[0]: 0                                    | AFS2[0]: 1                                          |

|                   |     | Reserved                      |                                           | AFS1[0]: 1                                    | AFS2[0]: 0                                          |

|                   |     | TOOUT                         | Timer 0 Output Complement                 | AFS1[0]: 1                                    | AFS2[0]: 1                                          |

|                   | PA1 | TOOUT                         | Timer 0 Output                            | AFS1[1]: 0                                    | AFS2[1]: 0                                          |

|                   |     | Reserved                      |                                           | AFS1[1]: 0                                    | AFS2[1]: 1                                          |

|                   |     | CLKIN                         | External Clock Input                      | AFS1[1]: 1                                    | AFS2[1]: 0                                          |

|                   |     | Analog Functions <sup>1</sup> | ADC Analog Input/V <sub>REF</sub>         | AFS1[1]: 1                                    | AFS2[1]: 1                                          |

|                   | PA2 | DE0                           | UART 0 Driver Enable                      | AFS1[2]: 0                                    | AFS2[2]: 0                                          |

|                   |     | RESET                         | External Reset                            | AFS1[2]: 0                                    | AFS2[2]: 1                                          |

|                   |     | T1OUT                         | Timer 1 Output                            | AFS1[2]: 1                                    | AFS2[2]: 0                                          |

|                   |     | Reserved                      |                                           | AFS1[2]: 1                                    | AFS2[2]: 1                                          |

|                   | PA3 | CTS0                          | UART 0 Clear to Send                      | AFS1[3]: 0                                    | AFS2[3]: 0                                          |

|                   |     | COUT                          | Comparator Output                         | AFS1[3]: 0                                    | AFS2[3]: 1                                          |

|                   |     | T1IN                          | Timer 1 Input                             | AFS1[3]: 1                                    | AFS2[3]: 0                                          |

|                   |     | Analog Functions <sup>2</sup> | ADC Analog Input/LPO Input (P)            | AFS1[3]: 1                                    | AFS2[3]: 1                                          |

|                   | PA4 | RXD0                          | UART 0 Receive Data                       | AFS1[4]: 0                                    | AFS2[4]: 0                                          |

|                   |     | Reserved                      |                                           | AFS1[4]: 0                                    | AFS2[4]: 1                                          |

|                   |     | Reserved                      |                                           | AFS1[4]: 1                                    | AFS2[4]: 0                                          |

|                   |     | Analog Functions <sup>2</sup> | ADC/Comparator Input (N)/LPO<br>Input (N) | AFS1[4]: 1                                    | AFS2[4]: 1                                          |

|                   | PA5 | TXD0                          | UART 0 Transmit Data                      | AFS1[5]: 0                                    | AFS2[5]: 0                                          |

|                   |     | T1OUT                         | Timer 1 Output Complement                 | AFS1[5]: 0                                    | AFS2[5]: 1                                          |

|                   |     | Reserved                      |                                           | AFS1[5]: 1                                    | AFS2[5]: 0                                          |

|                   |     | Analog Functions <sup>2</sup> | ADC/Comparator Input (P) LPO<br>Output    | AFS1[5]: 1                                    | AFS2[5]: 1                                          |

#### Table 16. Port Alternate Function Mapping (8-Pin Parts)

Notes:

1. Analog functions include ADC inputs, ADC reference, comparator inputs and LPO ports.

2. The alternate function selection must be enabled; see the Port A–D Alternate Function Subregisters (PxAF) section on page 47 for details.

# **GPIO Interrupts**

Many of the GPIO port pins can be used as interrupt sources. Some port pins can be configured to generate an interrupt request on either the rising edge or falling edge of the pin input signal. Other port pin interrupt sources generate an interrupt when any edge occurs (both rising and falling). See the <u>GPIO Mode Interrupt Controller</u> chapter on page 55 for more information about interrupts using the GPIO pins.

# **GPIO Control Register Definitions**

Four registers for each port provide access to GPIO control, input data and output data. Table 17 lists these port registers. Use the Port A–D Address and Control registers together to provide access to subregisters for port configuration and control.

| Port Register Mnemonic    | Port Register Name                                          |

|---------------------------|-------------------------------------------------------------|

| P <i>x</i> ADDR           | Port A–D Address Register; selects subregisters.            |

| P <i>x</i> CTL            | Port A–D Control Register; provides access to subregisters. |

| PxIN                      | Port A–D Input Data Register.                               |

| P <i>x</i> OUT            | Port A–D Output Data Register.                              |

| Port Subregister Mnemonic | Port Register Name                                          |

| P <i>x</i> DD             | Data Direction.                                             |

| P <i>x</i> AF             | Alternate Function.                                         |

| P <i>x</i> OC             | Output Control (Open-Drain).                                |

| P <i>x</i> HDE            | High Drive Enable.                                          |

| P <i>x</i> SMRE           | Stop Mode Recovery Source Enable.                           |

| P <i>x</i> PUE            | Pull-up Enable.                                             |

| PxAFS1                    | Alternate Function Set 1.                                   |

| PxAFS2                    | Alternate Function Set 2.                                   |

Table 17. GPIO Port Registers and Subregisters

#### Port A–D Pull-up Enable Subregisters

The Port A–D Pull-up Enable Subregister, shown in Table 26, is accessed through the Port A–D Control Register by writing 06H to the Port A–D Address Register. Setting the bits in the Port A–D Pull-up Enable subregisters enables a weak internal resistive pull-up on the specified port pins.

| Bit     | 7                                                                                     | 6                                                           | 5     | 4     | 3     | 2     | 1     | 0     |  |

|---------|---------------------------------------------------------------------------------------|-------------------------------------------------------------|-------|-------|-------|-------|-------|-------|--|

| Field   | PPUE7                                                                                 | PPUE6                                                       | PPUE5 | PPUE4 | PPUE3 | PPUE2 | PPUE1 | PPUE0 |  |

| RESET   |                                                                                       | 00H (Ports A-C); 01H (Port D); 04H (Port A of 8-pin device) |       |       |       |       |       |       |  |

| R/W     | R/W                                                                                   | R/W                                                         | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |  |

| Address | If 06H in Port A–D Address Register, accessible through the Port A–D Control Register |                                                             |       |       |       |       |       |       |  |

| Bit     | Description                                                                           | n                                                           |       |       |       |       |       |       |  |

| Table 26 | Dort    | וויים ח_א | IIn Enab |           | istors ( |        |

|----------|---------|-----------|----------|-----------|----------|--------|

| Table 20 | ). FUIL | A-D Fuii  | -∪p ⊏nau | le Subreg | isters ( | FXFUE) |

| Bit        | Description                                       |

|------------|---------------------------------------------------|

| [7:0]      | Port Pull-up Enabled                              |

| PPUEx      | 0 = The weak pull-up on the port pin is disabled. |

|            | 1 = The weak pull-up on the port pin is enabled.  |

| Note: x ii | ndicates the specific GPIO port pin number (7–0). |

#### Port A–D Alternate Function Set 1 Subregisters

The Port A–D Alternate Function Set1 Subregister, shown in Table 27, is accessed through the Port A–D Control Register by writing 07H to the Port A–D Address Register. The Alternate Function Set 1 subregisters selects the alternate function available at a port pin. Alternate Functions selected by setting or clearing bits of this register are defined in the <u>GPIO Alternate Functions</u> section on page 37.

**Note:** Alternate function selection on port pins must also be enabled as described in the <u>Port A</u>– <u>D Alternate Function Subregisters</u> section on page 47. • Writing a 1 to the IRQE bit in the Interrupt Control Register

Interrupts are globally disabled by any of the following actions:

- Execution of a Disable Interrupt (DI) instruction

- eZ8 CPU acknowledgement of an interrupt service request from the interrupt controller

- Writing a 0 to the IRQE bit in the Interrupt Control Register

- Reset

- Execution of a Trap instruction

- Illegal Instruction Trap

- Primary Oscillator Fail Trap

- Watchdog Oscillator Fail Trap

### **Interrupt Vectors and Priority**

The interrupt controller supports three levels of interrupt priority. Level 3 is the highest priority, Level 2 is the second highest priority and Level 1 is the lowest priority. If all of the interrupts are enabled with identical interrupt priority (all as Level 2 interrupts, for example), the interrupt priority is assigned from highest to lowest as specified in <u>Table 34</u> on page 56. Level 3 interrupts are always assigned higher priority than Level 2 interrupts which, in turn, always are assigned higher priority than Level 1 interrupts. Within each interrupt priority level (Level 1, Level 2, or Level 3), priority is assigned as specified in Table 34, above. Reset, Watchdog Timer interrupt (if enabled), Primary Oscillator Fail Trap, Watchdog Oscillator Fail Trap and Illegal Instruction Trap always have highest (level 3) priority.

#### **Interrupt Assertion**

Interrupt sources assert their interrupt requests for only a single system clock period (single pulse). When the interrupt request is acknowledged by the eZ8 CPU, the corresponding bit in the Interrupt Register is cleared until the next interrupt occurs. Writing a 0 to the corresponding bit in the Interrupt Request Register likewise clears the interrupt request.

**Caution:** Zilog recommends not using a coding style that clears bits in the Interrupt Request registers. All incoming interrupts received between execution of the first LDX command and the final LDX command are lost. See Example 1, which follows.

66

| IRQ2ENH[ <i>x</i> ] | IRQ2ENL[x] | Priority | Description |

|---------------------|------------|----------|-------------|

| 0                   | 0          | Disabled | Disabled    |

| 0                   | 1          | Level 1  | Low         |

| 1                   | 0          | Level 2  | Medium      |

| 1                   | 1          | Level 3  | High        |

#### Table 44. IRQ2 Enable and Priority Encoding

#### Table 45. IRQ2 Enable High Bit Register (IRQ2ENH)

| Bit     | 7   | 6    | 5     | 4   | 3     | 2     | 1     | 0     |

|---------|-----|------|-------|-----|-------|-------|-------|-------|

| Field   |     | Rese | erved |     | C3ENH | C2ENH | C1ENH | C0ENH |

| RESET   | 0   | 0    | 0     | 0   | 0     | 0     | 0     | 0     |

| R/W     | R/W | R/W  | R/W   | R/W | R/W   | R/W   | R/W   | R/W   |

| Address |     | FC7H |       |     |       |       |       |       |

| Bit          | Description                                                                |

|--------------|----------------------------------------------------------------------------|

| [7:4]        | <b>Reserved</b><br>These bits are reserved and must be programmed to 0000. |

| [3]<br>C3ENH | Port C3 Interrupt Request Enable High Bit                                  |

| [2]<br>C2ENH | Port C2 Interrupt Request Enable High Bit                                  |

| [1]<br>C1ENH | Port C1 Interrupt Request Enable High Bit                                  |

| [0]<br>C0ENH | Port C0 Interrupt Request Enable High Bit                                  |

## **Interrupt Control Register**

The Interrupt Control (IRQCTL) Register, shown in Table 49, contains the master enable bit for all interrupts.

| Bit     | 7             | 6                        | 5            | 4             | 3             | 2            | 1           | 0            |  |

|---------|---------------|--------------------------|--------------|---------------|---------------|--------------|-------------|--------------|--|

| Field   | IRQE          |                          |              |               | Reserved      |              |             |              |  |

| RESET   | 0             | 0                        | 0            | 0             | 0             | 0            | 0           | 0            |  |

| R/W     | R/W           | R                        | R            | R             | R             | R            | R           | R            |  |

| Address |               | FCFH                     |              |               |               |              |             |              |  |

| Bit     | Descriptio    | Description              |              |               |               |              |             |              |  |

| [7]     | Interrupt R   | Interrupt Request Enable |              |               |               |              |             |              |  |

| IRQE    | This bit is s | et to 1 by ex            | ecuting an E | El (Enable Ir | nterrupts) or | IRET (Interr | upt Return) | instruction, |  |

#### Table 49. Interrupt Control Register (IRQCTL)

| ЫІ    | Description                                                                                                                                                                                                                                                                                                                                    |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]   | Interrupt Request Enable                                                                                                                                                                                                                                                                                                                       |

| IRQE  | This bit is set to 1 by executing an EI (Enable Interrupts) or IRET (Interrupt Return) instruction, or by a direct register write of a 1 to this bit. It is reset to 0 by executing a DI instruction, eZ8 CPU acknowledgement of an interrupt request, Reset or by a direct register write of a 0 to this bit.<br>0 = Interrupts are disabled. |

|       | 1 = Interrupts are enabled.                                                                                                                                                                                                                                                                                                                    |

| [6:0] | <b>Reserved</b><br>These bits are reserved and must be programmed to 0000000.                                                                                                                                                                                                                                                                  |

|       |                                                                                                                                                                                                                                                                                                                                                |

into the Watchdog Timer Reload registers results in a one-second time-out at room temperature and 3.3V supply voltage. Time-outs other than one second may be obtained by scaling the calibration values up or down as required.

**Note:** The Watchdog Timer accuracy still degrades as temperature and supply voltage vary. See <u>Table 137</u> on page 235 for details.

# Watchdog Timer Control Register Definitions

This section defines the features of the following Watchdog Timer Control registers.

Watchdog Timer Control Register (WDTCTL): see page 96

Watchdog Timer Reload Upper Byte Register (WDTU): see page 97

Watchdog Timer Reload High Byte Register (WDTH): see page 97

Watchdog Timer Reload Low Byte Register (WDTL): see page 98

## Watchdog Timer Control Register

The Watchdog Timer Control (WDTCTL) Register is a write-only control register. Writing the 55H, AAH unlock sequence to the WDTCTL Register address unlocks the three Watchdog Timer Reload Byte registers (WDTU, WDTH and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL Register address produce no effect on the bits in the WDTCTL Register. The locking mechanism prevents spurious writes to the reload registers. This register address is shared with the read-only Reset Status Register.

| Bit       | 7                    | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-----------|----------------------|---|---|---|---|---|---|---|--|--|

| Field     | WDTUNLK              |   |   |   |   |   |   |   |  |  |

| RESET     | Х                    | Х | Х | Х | Х | Х | Х | Х |  |  |

| R/W       | W                    | W | W | W | W | W | W | W |  |  |

| Address   | FF0H                 |   |   |   |   |   |   |   |  |  |

| Note: X = | Note: X = Undefined. |   |   |   |   |   |   |   |  |  |

| DIL     | Description                                                                                  |

|---------|----------------------------------------------------------------------------------------------|

| [7:0]   | Watchdog Timer Unlock                                                                        |

| WDTUNLK | The software must write the correct unlocking sequence to this register before it is allowed |

|         | to modify the contents of the Watchdog Timer reload registers.                               |

Description

Dit

# Universal Asynchronous Receiver/ Transmitter

The universal asynchronous receiver/transmitter (UART) is a full-duplex communication channel capable of handling asynchronous data transfers. The UART uses a single 8-bit data mode with selectable parity. Features of the UART include:

- 8-bit asynchronous data transfer

- Selectable even- and odd-parity generation and checking

- Option of one or two STOP bits

- Separate transmit and receive interrupts

- Framing, parity, overrun and break detection

- Separate transmit and receive enables

- 16-bit baud rate generator (BRG)

- Selectable MULTIPROCESSOR (9-bit) Mode with three configurable interrupt schemes

- Baud rate generator (BRG) can be configured and used as a basic 16-bit timer

- Driver enable (DE) output for external bus transceivers

# Architecture

The UART consists of three primary functional blocks: transmitter, receiver and baud rate generator. The UART's transmitter and receiver function independently, but employ the same baud rate and data format. Figure 10 displays the UART architecture.

Rate Generator to function as an additional counter if the UART functionality is not employed.

## **UART Baud Rate Generator**

The UART Baud Rate Generator creates a lower frequency baud rate clock for data transmission. The input to the Baud Rate Generator is the system clock. The UART Baud Rate High and Low Byte registers combine to create a 16-bit baud rate divisor value (BRG[15:0]) that sets the data transmission rate (baud rate) of the UART. The UART data rate is calculated using the following equation:

UART Data Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

When the UART is disabled, the Baud Rate Generator functions as a basic 16-bit timer with an interrupt upon time-out. Observe the following steps to configure the Baud Rate Generator as a timer with an interrupt upon time-out:

- 1. Disable the UART by clearing the REN and TEN bits in the UART Control 0 Register to 0.

- 2. Load the acceptable 16-bit count value into the UART Baud Rate High and Low Byte registers.

- 3. Enable the Baud Rate Generator timer function and associated interrupt by setting the BRGCTL bit in the UART Control 1 Register to 1.

When configured as a general purpose timer, the interrupt interval is calculated using the following equation:

Interrupt Interval(s) = System Clock Period (s)  $\times$  BRG[15:0]

# **UART Control Register Definitions**

The UART Control registers support the UART and the associated Infrared Encoder/ Decoders. For more information about infrared operation, see the <u>Infrared Encoder/</u><u>Decoder</u> chapter on page 120.

## **UART Control 0 and Control 1 Registers**

The UART Control 0 (UxCTL0) and Control 1 (UxCTL1) registers, shown in Tables 63 and 64, configure the properties of the UART's transmit and receive operations. The UART Control registers must not be written while the UART is enabled.

| Bit           | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [2]<br>BRGCTL | <ul> <li>Baud Rate Control</li> <li>This bit causes an alternate UART behavior depending on the value of the REN bit in the UART Control 0 Register. When the UART receiver is not enabled (REN=0), this bit determines whether the Baud Rate Generator issues interrupts.</li> <li>0 = Reads from the Baud Rate High and Low Byte registers return the BRG reload value.</li> <li>1 = The Baud Rate Generator generates a receive interrupt when it counts down to 0. Reads from the Baud Rate High and Low Byte registers return the current BRG count value.</li> <li>When the UART receiver is enabled (REN=1), this bit allows reads from the Baud Rate registers to return the BRG count value instead of the reload value.</li> <li>0 = Reads from the Baud Rate High and Low Byte registers return the BRG reload value.</li> <li>1 = Reads from the Baud Rate High and Low Byte registers return the BRG reload value.</li> <li>1 = Reads from the Baud Rate High and Low Byte registers return the BRG reload value.</li> </ul> |

| [1]<br>RDAIRQ | <ul> <li>Receive Data Interrupt Enable</li> <li>0 = Received data and receiver errors generates an interrupt request to the Interrupt Controller.</li> <li>1 = Received data does not generate an interrupt request to the Interrupt Controller. Only receiver errors generate an interrupt request.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| [0]<br>IREN   | <ul> <li>Infrared Encoder/Decoder Enable</li> <li>0 = Infrared Encoder/Decoder is disabled. UART operates normally.</li> <li>1 = Infrared Encoder/Decoder is enabled. The UART transmits and receives data through the Infrared Encoder/Decoder.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

113

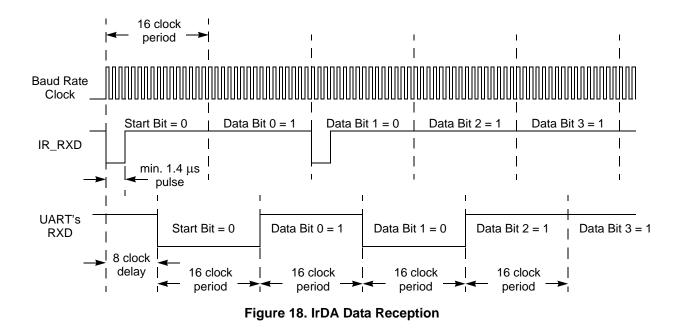

## **Receiving IrDA Data**

Data received from the infrared transceiver using the IR\_RXD signal through the RXD pin is decoded by the infrared endec and passed to the UART. The UART's baud rate clock is used by the infrared endec to generate the demodulated signal (RXD) that drives the UART. Each UART/Infrared data bit is 16-clocks wide. Figure 18 displays data reception. When the infrared endec is enabled, the UART's RXD signal is internal to the Z8 Encore! XP F082A Series products while the IR\_RXD signal is received through the RXD pin.

#### **Infrared Data Reception**

**Caution:** The system clock frequency must be at least 1.0MHz to ensure proper reception of the 1.4µs minimum width pulses allowed by the IrDA standard.

#### **Endec Receiver Synchronization**

The IrDA receiver uses a local baud rate clock counter (0 to 15 clock periods) to generate an input stream for the UART and to create a sampling window for detection of incoming pulses. The generated UART input (UART RXD) is delayed by 8 baud rate clock periods with respect to the incoming IrDA data stream. When a falling edge in the input data stream is detected, the Endec counter is reset. When the count reaches a value of 8, the UART RXD value is updated to reflect the value of the decoded data. When the count reaches 12 baud clock periods, the sampling window for the next incoming pulse opens.

The ADC registers actually return 13 bits of data, but the two LSBs are intended for compensation use only. When the software compensation routine is performed on the 13 bit raw ADC value, two bits of resolution are lost because of a rounding error. As a result, the final value is an 11-bit number.

### Hardware Overflow

When the hardware overflow bit (OVF) is set in ADC Data Low Byte (ADCD\_L) Register, all other data bits are invalid. The hardware overflow bit is set for values greater than  $V_{REF}$  and less than  $-V_{REF}$  (DIFFERENTIAL Mode).

## Automatic Powerdown

If the ADC is idle (no conversions in progress) for 160 consecutive system clock cycles, portions of the ADC are automatically powered down. From this powerdown state, the ADC requires 40 system clock cycles to power up. The ADC powers up when a conversion is requested by the ADC Control Register.

## Single-Shot Conversion

When configured for single-shot conversion, the ADC performs a single analog-to-digital conversion on the selected analog input channel. After completion of the conversion, the ADC shuts down. Observe the following steps for setting up the ADC and initiating a single-shot conversion:

- 1. Enable the appropriate analog inputs by configuring the general-purpose I/O pins for alternate analog function. This configuration disables the digital input and output drivers.

- 2. Write the ADC Control/Status Register 1 to configure the ADC.

- Write to BUFMODE[2:0] to select SINGLE-ENDED or DIFFERENTIAL mode, plus unbuffered or buffered mode.

- Write the REFSELH bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELL bit is. contained in the ADC Control Register 0.

- 3. Write to the ADC Control Register 0 to configure the ADC and begin the conversion. The bit fields in the ADC Control Register can be written simultaneously (the ADC can be configured and enabled with the same write instruction):

- Write to the ANAIN[3:0] field to select from the available analog input sources (different input pins available depending on the device).

- Clear CONT to 0 to select a single-shot conversion.

## 173

#### Table 101. Watchdog Calibration Low Byte at 007FH (WDTCALL)

| Bit       | 7                                               | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|-----------|-------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|--|--|

| Field     | WDTCALL                                         |     |     |     |     |     |     |     |  |  |

| RESET     | U                                               | U   | U   | U   | U   | U   | U   | U   |  |  |

| R/W       | R/W                                             | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Address   | Information Page Memory 007FH                   |     |     |     |     |     |     |     |  |  |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |     |     |     |     |     |     |     |  |  |

| Bit     | Description                                                                              |

|---------|------------------------------------------------------------------------------------------|

| [7:0]   | Watchdog Timer Calibration Low Byte                                                      |

| WDTCALL | The WDTCALH and WDTCALL bytes, when loaded into the Watchdog Timer reload regis-         |

|         | ters result in a one second time-out at room temperature and 3.3V supply voltage. To use |

|         | the Watchdog Timer calibration, user code must load WDTU with 0x00, WDTH with WDT-       |

|         | CALH and WDTL with WDTCALL.                                                              |

# **Serialization Data**

#### Table 102. Serial Number at 001C - 001F (S\_NUM)

| Bit                                             | 7                                 | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|-------------------------------------------------|-----------------------------------|-----|-----|-----|-----|-----|-----|-----|--|

| Field                                           | S_NUM                             |     |     |     |     |     |     |     |  |

| RESET                                           | U                                 | U   | U   | U   | U   | U   | U   | U   |  |

| R/W                                             | R/W                               | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address                                         | Information Page Memory 001C-001F |     |     |     |     |     |     |     |  |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                                   |     |     |     |     |     |     |     |  |

| Bit   | Description                                                          |

|-------|----------------------------------------------------------------------|

| [7:0] | Serial Number Byte                                                   |

| S_NUM | The serial number is a unique four-byte binary value. See Table 103. |

#### Table 103. Serialization Data Locations

| Info Page<br>Address | Memory<br>Address | Usage                                     |

|----------------------|-------------------|-------------------------------------------|

| 1C                   | FE1C              | Serial Number Byte 3 (most significant).  |

| 1D                   | FE1D              | Serial Number Byte 2.                     |

| 1E                   | FE1E              | Serial Number Byte 1.                     |

| 1F                   | FE1F              | Serial Number Byte 0 (least significant). |

## **Byte Read**

To read a byte from the NVDS array, user code must first push the address onto the stack. User code issues a CALL instruction to the address of the byte-read routine  $(0 \times 1000)$ . At the return from the sub-routine, the read byte resides in working register R0 and the read status byte resides in working register R1. The contents of the status byte are undefined for read operations to illegal addresses. Also, the user code must pop the address byte off the stack.

The read routine uses 9 bytes of stack space in addition to the one byte of address pushed by the user. Sufficient memory must be available for this stack usage.

Because of the Flash memory architecture, NVDS reads exhibit a nonuniform execution time. A read operation takes between 44  $\mu$ s and 489  $\mu$ s (assuming a 20MHz system clock). Slower system clock speeds result in proportionally higher execution times.

NVDS byte reads from invalid addresses (those exceeding the NVDS array size) return 0xff. Illegal read operations have a 2  $\mu$ s execution time.

The status byte returned by the NVDS read routine is zero for successful read, as determined by a CRC check. If the status byte is nonzero, there was a corrupted value in the NVDS array at the location being read. In this case, the value returned in R0 is the byte most recently written to the array that does not have a CRC error.

## **Power Failure Protection**

The NVDS routines employ error checking mechanisms to ensure a power failure endangers only the most recently written byte. Bytes previously written to the array are not perturbed.

A system reset (such as a pin reset or Watchdog Timer reset) that occurs during a write operation also perturbs the byte currently being written. All other bytes in the array are unperturbed.

## **Optimizing NVDS Memory Usage for Execution Speed**

NVDS read time can vary drastically. This discrepancy is a trade-off for minimizing the frequency of writes that require post-write page erases, as indicated in Table 107. The NVDS read time of address N is a function of the number of writes to addresses other than N since the most recent write to address N, plus the number of writes since the most recent page erase. Neglecting effects caused by page erases and results caused by the initial condition in which the NVDS is blank, a rule of thumb is that every write since the most recent page erase causes read times of unwritten addresses to increase by 1 µs up to a maximum of (511-NVDS\_SIZE)µs.

| Assembly      |                                         | Address<br>Mode<br>Opcode(s) _ |     |       |   | Fla | Fetch<br>Cycle | Instr.<br>Cycle |   |   |   |   |

|---------------|-----------------------------------------|--------------------------------|-----|-------|---|-----|----------------|-----------------|---|---|---|---|

| Mnemonic      | Symbolic Operation                      | dst                            | src | (Hex) | С | Ζ   | S              | ۷               | D | Н | S | S |

| RRC dst       |                                         | R                              |     | C0    | * | *   | *              | *               | _ | _ | 2 | 2 |

|               | ► <u>D7D6D5D4D3D2D1D0</u> ►_C<br>dst    | IR                             |     | C1    |   |     |                |                 |   |   | 2 | 3 |

| SBC dst, src  | $dst \gets dst - src - C$               | r                              | r   | 32    | * | *   | *              | *               | 1 | * | 2 | 3 |

|               | =                                       | r                              | lr  | 33    |   |     |                |                 |   |   | 2 | 4 |

|               | -                                       | R                              | R   | 34    |   |     |                |                 |   |   | 3 | 3 |

|               | -                                       | R                              | IR  | 35    |   |     |                |                 |   |   | 3 | 4 |

|               | -                                       | R                              | IM  | 36    |   |     |                |                 |   |   | 3 | 3 |

|               | -                                       | IR                             | IM  | 37    |   |     |                |                 |   |   | 3 | 4 |

| SBCX dst, src | $dst \gets dst - src - C$               | ER                             | ER  | 38    | * | *   | *              | *               | 1 | * | 4 | 3 |

|               | -                                       | ER                             | IM  | 39    |   |     |                |                 |   |   | 4 | 3 |

| SCF           | C ← 1                                   |                                |     | DF    | 1 | -   | _              | _               | _ | - | 1 | 2 |

| SRA dst       |                                         | R                              |     | D0    | * | *   | *              | 0               | - | - | 2 | 2 |

|               | $- D7 D6 D5 D4 D3 D2 D1 D0 - C^{-}$ dst | IR                             |     | D1    |   |     |                |                 |   |   | 2 | 3 |

| SRL dst       | 0 - D7D6D5D4D3D2D1D0 - C                | R                              |     | 1F C0 | * | *   | 0              | *               | _ | _ | 3 | 2 |

|               | dst                                     | IR                             |     | 1F C1 |   |     |                |                 |   |   | 3 | 3 |

| SRP src       | RP ← src                                |                                | IM  | 01    | _ | _   | _              | _               | _ | _ | 2 | 2 |

| STOP          | STOP Mode                               |                                |     | 6F    | _ | _   | _              | _               | _ | _ | 1 | 2 |

#### Table 128. eZ8 CPU Instruction Summary (Continued)

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

219

| ົງງ | n |

|-----|---|

|     | U |

| Assembly      | Symbolic Operation                  | Address<br>Mode |     | _ Opcode(s) | Flags |   |   |   |   | Fetch<br>₋ Cycle | Instr.<br>Cycle |   |

|---------------|-------------------------------------|-----------------|-----|-------------|-------|---|---|---|---|------------------|-----------------|---|

| Mnemonic      |                                     | dst             | src | (Hex)       | С     | Ζ | S | V | D | Н                | S               | S |

| SUB dst, src  | $dst \leftarrow dst - src$          | r               | r   | 22          | *     | * | * | * | 1 | *                | 2               | 3 |

|               |                                     | r               | lr  | 23          | -     |   |   |   |   |                  | 2               | 4 |

|               |                                     | R               | R   | 24          | -     |   |   |   |   |                  | 3               | 3 |

|               |                                     | R               | IR  | 25          |       |   |   |   |   |                  | 3               | 4 |

|               |                                     | R               | IM  | 26          | -     |   |   |   |   |                  | 3               | 3 |

|               |                                     | IR              | IM  | 27          | -     |   |   |   |   |                  | 3               | 4 |

| SUBX dst, src | $dst \leftarrow dst - src$          | ER              | ER  | 28          | *     | * | * | * | 1 | *                | 4               | 3 |

|               |                                     | ER              | IM  | 29          | -     |   |   |   |   |                  | 4               | 3 |

| SWAP dst      | $dst[7:4] \leftrightarrow dst[3:0]$ | R               |     | F0          | Х     | * | * | Х | - | -                | 2               | 2 |

|               |                                     | IR              |     | F1          | -     |   |   |   |   |                  | 2               | 3 |

| TCM dst, src  | (NOT dst) AND src                   | r               | r   | 62          | -     | * | * | 0 | - | -                | 2               | 3 |

|               |                                     | r               | lr  | 63          | -     |   |   |   |   |                  | 2               | 4 |

|               |                                     | R               | R   | 64          | -     |   |   |   |   |                  | 3               | 3 |

|               |                                     | R               | IR  | 65          | -     |   |   |   |   |                  | 3               | 4 |

|               |                                     | R               | IM  | 66          | -     |   |   |   |   |                  | 3               | 3 |

|               |                                     | IR              | IM  | 67          | -     |   |   |   |   |                  | 3               | 4 |

| TCMX dst, src | (NOT dst) AND src                   | ER              | ER  | 68          | -     | * | * | 0 | - | -                | 4               | 3 |

|               |                                     | ER              | IM  | 69          | -     |   |   |   |   |                  | 4               | 3 |

| TM dst, src   | dst AND src                         | r               | r   | 72          | -     | * | * | 0 | - | -                | 2               | 3 |

|               |                                     | r               | lr  | 73          |       |   |   |   |   |                  | 2               | 4 |

|               |                                     | R               | R   | 74          |       |   |   |   |   |                  | 3               | 3 |

|               |                                     | R               | IR  | 75          | -     |   |   |   |   |                  | 3               | 4 |

|               |                                     | R               | IM  | 76          | -     |   |   |   |   |                  | 3               | 3 |

|               |                                     | IR              | IM  | 77          | -     |   |   |   |   |                  | 3               | 4 |

#### Table 128. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 =Set to 1.

|                   |                   | V <sub>DD</sub> | = 2.7 V to   |                 | Conditions |                                                                             |

|-------------------|-------------------|-----------------|--------------|-----------------|------------|-----------------------------------------------------------------------------|

| Symbol            | Parameter         | Minimum         | Typical      | Typical Maximum |            |                                                                             |

| T <sub>AERR</sub> | Temperature Error |                 | <u>+</u> 0.5 | <u>+</u> 2      | °C         | Over the range +20°C<br>to +30°C (as mea-<br>sured by ADC). <sup>1</sup>    |

|                   |                   |                 | <u>+</u> 1   | <u>+</u> 5      | °C         | Over the range +0°C<br>to +70°C (as mea-<br>sured by ADC).                  |

|                   |                   |                 | <u>+</u> 2   | <u>+</u> 7      | °C         | Over the range +0°C<br>to +105°C (as mea-<br>sured by ADC).                 |

|                   |                   |                 | <u>+</u> 7   |                 | °C         | Over the range –40°C<br>to +105°C (as mea-<br>sured by ADC).                |

| t <sub>WAKE</sub> | Wakeup Time       |                 | 80           | 100             | μs         | Time required for Tem<br>perature Sensor to<br>stabilize after<br>enabling. |

#### Table 142. Temperature Sensor Electrical Characteristics

Note: Devices are factory calibrated at for maximal accuracy between +20°C and +30°C, so the sensor is maximally accurate in that range. User recalibration for a different temperature range is possible and increases accuracy near the new calibration point.

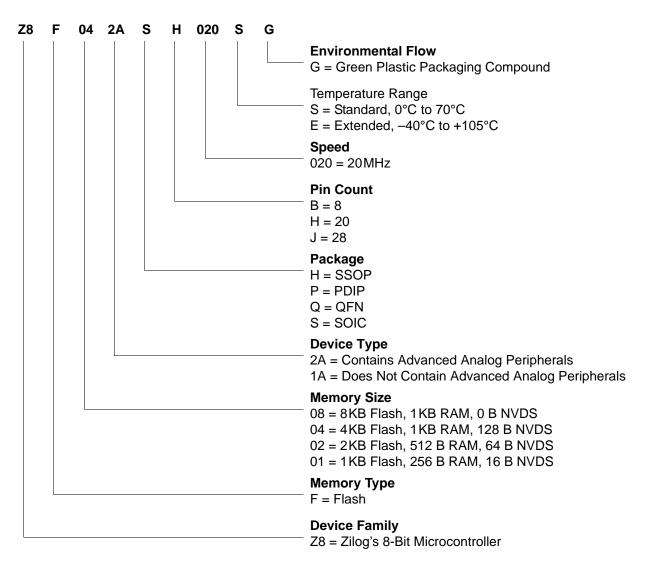

# Part Number Suffix Designations

Zilog part numbers consist of a number of components, as indicated in the following example.

**Example.** Part number Z8F042ASH020SG is an 8-bit Flash MCU with 4KB of Program Memory, equipped with advanced analog peripherals in a 20-pin SOIC package, operating within a 0°C to +70°C temperature range and built using lead-free solder.

Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

UARTx control 1 (UxCTL1) 112 UARTx receive data (UxRXD) 116 UARTx status 0 (UxSTAT0) 114 UARTx status 1 (UxSTAT1) 115 UARTx transmit data (UxTXD) 116 Watchdog Timer control (WDTCTL) 30, 96, 141, 196 Watchdog Timer reload high byte (WDTH) 97 Watchdog Timer reload low byte (WDTL) 98 Watchdog Timer reload upper byte (WDTU) 97 register file 15 register pair 206 register pointer 207 reset and stop mode characteristics 23 and Stop Mode Recovery 22 carry flag 209 sources 24 **RET 211** return 211 RL 211 **RLC 211** rotate and shift instuctions 211 rotate left 211 rotate left through carry 211 rotate right 211 rotate right through carry 211 **RP 207** RR 206, 211

rr 206 RRC 211

# S

SBC 208 SCF 209, 210 second opcode map after 1FH 225 set carry flag 209, 210 set register pointer 210 shift right arithmatic 211 shift right logical 211 signal descriptions 10 single-shot conversion (ADC) 126 software trap 211 source operand 207 SP 207 SRA 211 src 207 SRL 211 **SRP 210** stack pointer 207 **STOP 210** STOP mode 32 stop mode 210 Stop Mode Recovery sources 27 using a GPIO port pin transition 28 using Watchdog Timer time-out 28 stop mode recovery sources 29 using a GPIO port pin transition 29 **SUB 208** subtract 208 subtract - extended addressing 208 subtract with carry 208 subtract with carry - extended addressing 208 **SUBX 208 SWAP 211** swap nibbles 211 symbols, additional 207

# Т

PRELIMINARY

TCM 209 TCMX 209 test complement under mask 209 test complement under mask - extended addressing 209 test under mask 209 test under mask - extended addressing 209 timer signals 10 timers 70 architecture 70 block diagram 71 CAPTURE mode 79, 80, 87, 88 CAPTURE/COMPARE mode 83, 88 COMPARE mode 81, 87