Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT           |

| Number of I/O              | 25                                                        |

| Program Memory Size        | 1KB (1K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | 16 x 8                                                    |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f011asj020sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Internal Precision Oscillator**

The internal precision oscillator (IPO) is a trimmable clock source that requires no external components.

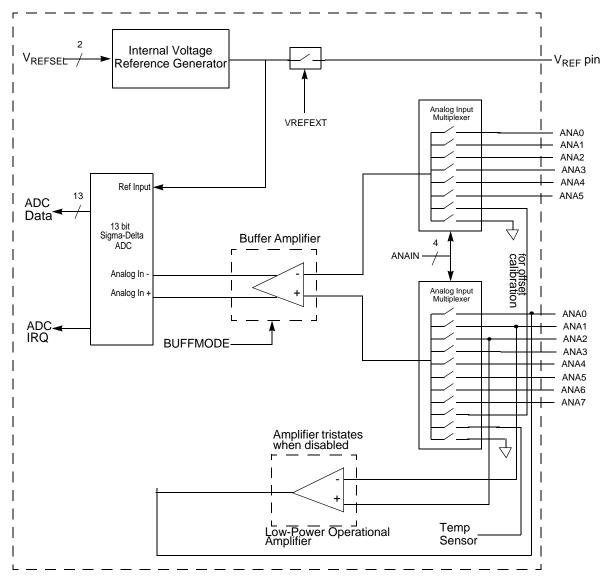

### **Temperature Sensor**

The optional temperature sensor produces an analog output proportional to the device temperature. This signal can be sent to either the ADC or the analog comparator.

### **Analog Comparator**

The analog comparator compares the signal at an input pin with either an internal programmable voltage reference or a second input pin. The comparator output can be used to drive either an output pin or to generate an interrupt.

# **External Crystal Oscillator**

The crystal oscillator circuit provides highly accurate clock frequencies with the use of an external crystal, ceramic resonator or RC network.

# Low Voltage Detector

The low voltage detector (LVD) is able to generate an interrupt when the supply voltage drops below a user-programmable level. The LVD is available on 8-pin devices only.

# **On-Chip Debugger**

The Z8 Encore! XP F082A Series products feature an integrated on-chip debugger (OCD) accessed via a single-pin interface. The OCD provides a rich-set of debugging capabilities, such as reading and writing registers, programming Flash memory, setting breakpoints and executing code.

# **Universal Asynchronous Receiver/Transmitter**

The full-duplex universal asynchronous receiver/transmitter (UART) is included in all Z8 Encore! XP package types. The UART supports 8- and 9-bit data modes and selectable parity. The UART also supports multi-drop address processing in hardware. The UART baud rate generator (BRG) can be configured and used as a basic 16-bit timer.

### Timers

Two enhanced 16-bit reloadable timers can be used for timing/counting events or for motor control operations. These timers provide a 16-bit programmable reload counter and

addresses outside the available Flash memory addresses returns FFH. Writing to these unimplemented Program Memory addresses produces no effect. Table 5 describes the Program Memory Maps for the Z8 Encore! XP F082A Series products.

| Program Memory Address (Hex) | Function                     |  |  |  |  |

|------------------------------|------------------------------|--|--|--|--|

| Z8F082A and Z8F081A Products |                              |  |  |  |  |

| 0000–0001                    | Flash Option Bits            |  |  |  |  |

| 0002–0003                    | Reset Vector                 |  |  |  |  |

| 0004–0005                    | WDT Interrupt Vector         |  |  |  |  |

| 0006–0007                    | Illegal Instruction Trap     |  |  |  |  |

| 0008–0037                    | Interrupt Vectors*           |  |  |  |  |

| 0038–0039                    | Reserved                     |  |  |  |  |

| 003A-003D                    | Oscillator Fail Trap Vectors |  |  |  |  |

| 003E-1FFF                    | Program Memory               |  |  |  |  |

| Z8F042A and Z8F041A Products |                              |  |  |  |  |

| 0000–0001                    | Flash Option Bits            |  |  |  |  |

| 0002–0003                    | Reset Vector                 |  |  |  |  |

| 0004–0005                    | WDT Interrupt Vector         |  |  |  |  |

| 0006–0007                    | Illegal Instruction Trap     |  |  |  |  |

| 0008–0037                    | Interrupt Vectors*           |  |  |  |  |

| 0038–0039                    | Reserved                     |  |  |  |  |

| 003A-003D                    | Oscillator Fail Trap Vectors |  |  |  |  |

| 003E-0FFF                    | Program Memory               |  |  |  |  |

| Z8F022A and Z8F021A Products |                              |  |  |  |  |

| 0000–0001                    | Flash Option Bits            |  |  |  |  |

| 0002–0003                    | Reset Vector                 |  |  |  |  |

| 0004–0005                    | WDT Interrupt Vector         |  |  |  |  |

| 0006–0007                    | Illegal Instruction Trap     |  |  |  |  |

| 0008–0037                    | Interrupt Vectors*           |  |  |  |  |

| 0038–0039                    | Reserved                     |  |  |  |  |

| 003A-003D                    | Oscillator Fail Trap Vectors |  |  |  |  |

| 003E-07FF                    | Program Memory               |  |  |  |  |

| Z8F012A and Z8F011A Products |                              |  |  |  |  |

| 0000–0001                    | Flash Option Bits            |  |  |  |  |

|                              |                              |  |  |  |  |

#### Table 5. Z8 Encore! XP F082A Series Program Memory Maps

Note: \*See Table 32 on page 56 for a list of the interrupt vectors.

| Program Memory Address (Hex)                                        | Function                     |  |  |  |  |

|---------------------------------------------------------------------|------------------------------|--|--|--|--|

| 0002–0003                                                           | Reset Vector                 |  |  |  |  |

| 0004–0005                                                           | WDT Interrupt Vector         |  |  |  |  |

| 0006–0007                                                           | Illegal Instruction Trap     |  |  |  |  |

| 0008–0037                                                           | Interrupt Vectors*           |  |  |  |  |

| 0038–0039                                                           | Reserved                     |  |  |  |  |

| 003A-003D                                                           | Oscillator Fail Trap Vectors |  |  |  |  |

| 003E-03FF                                                           | Program Memory               |  |  |  |  |

| Note: *See Table 32 on page 56 for a list of the interrupt vectors. |                              |  |  |  |  |

| Table 5. Z8 Encore! XP F082A Series P | Program Memory Maps (Continued) |

|---------------------------------------|---------------------------------|

|---------------------------------------|---------------------------------|

### **Data Memory**

The Z8 Encore! XP F082A Series does not use the eZ8 CPU's 64 KB Data Memory address space.

# **Flash Information Area**

Table 6 describes the Z8 Encore! XP F082A Series Flash Information Area. This 128B Information Area is accessed by setting bit 7 of the Flash Page Select Register to 1. When access is enabled, the Flash Information Area is mapped into the Program Memory and overlays the 128 bytes at addresses FE00H to FF7FH. When the Information Area access is enabled, all reads from these Program Memory addresses return the Information Area data rather than the Program Memory data. Access to the Flash Information Area is read-only.

Table 6. Z8 Encore! XP F082A Series Flash Memory Information Area Map

| Program Memory |                                                                                           |

|----------------|-------------------------------------------------------------------------------------------|

| Address (Hex)  | Function                                                                                  |

| FE00–FE3F      | Zilog Option Bits/Calibration Data                                                        |

| FE40-FE53      | Part Number<br>20-character ASCII alphanumeric code<br>Left-justified and filled with FFH |

| FE54–FE5F      | Reserved                                                                                  |

| FE60–FE7F      | Zilog Calibration Data                                                                    |

| FE80–FFFF      | Reserved                                                                                  |

# HALT Mode

Executing the eZ8 CPU's HALT instruction places the device into HALT Mode, which powers down the CPU but leaves all other peripherals active. In HALT Mode, the operating characteristics are:

- Primary oscillator is enabled and continues to operate

- System clock is enabled and continues to operate

- eZ8 CPU is stopped

- Program counter (PC) stops incrementing

- Watchdog Timer's internal RC oscillator continues to operate

- If enabled, the Watchdog Timer continues to operate

- All other on-chip peripherals continue to operate, if enabled

The eZ8 CPU can be brought out of HALT Mode by any of the following operations:

- Interrupt

- Watchdog Timer time-out (interrupt or reset)

- Power-On Reset

- Voltage Brown-Out reset

- External **RESET** pin assertion

To minimize current in HALT Mode, all GPIO pins that are configured as inputs must be driven to one of the supply rails ( $V_{CC}$  or GND).

# **Peripheral-Level Power Control**

In addition to the STOP and HALT modes, it is possible to disable each peripheral on each of the Z8 Encore! XP F082A Series devices. Disabling a given peripheral minimizes its power consumption.

# **Power Control Register Definitions**

The following sections define the Power Control registers.

#### **Power Control Register 0**

Each bit of the following registers disables a peripheral block, either by gating its system clock input or by removing power from the block. The default state of the low-power

| Port                | Pin | Mnemonic                           | Alternate Function Description            | Alternate Function<br>Set Register AFS1 |

|---------------------|-----|------------------------------------|-------------------------------------------|-----------------------------------------|

| Port C <sup>5</sup> | PC0 | Reserved                           |                                           | AFS1[0]: 0                              |

|                     |     | ANA4/CINP                          | ADC or Comparator Input                   | AFS1[0]: 1                              |

|                     | PC1 | Reserved                           |                                           | AFS1[1]: 0                              |

|                     |     | ANA5/CINN                          | ADC or Comparator Input                   | AFS1[1]: 1                              |

|                     | PC2 | Reserved                           |                                           | AFS1[2]: 0                              |

| F                   |     | ANA6/V <sub>REF</sub> <sup>4</sup> | ADC Analog Input or ADC Voltage Reference | AFS1[2]: 1                              |

|                     | PC3 | COUT                               | Comparator Output                         | AFS1[3]: 0                              |

|                     |     | Reserved                           |                                           | AFS1[3]: 1                              |

|                     | PC4 | Reserved                           |                                           | AFS1[4]: 0                              |

|                     |     |                                    |                                           | AFS1[4]: 1                              |

|                     | PC5 | Reserved                           |                                           | AFS1[5]: 0                              |

|                     |     |                                    |                                           | AFS1[5]: 1                              |

|                     | PC6 | Reserved                           |                                           | AFS1[6]: 0                              |

|                     |     |                                    |                                           | AFS1[6]: 1                              |

|                     | PC7 | Reserved                           |                                           | AFS1[7]: 0                              |

|                     |     |                                    |                                           | AFS1[7]: 1                              |

| Port D <sup>6</sup> | PD0 | RESET                              | External Reset                            | N/A                                     |

#### Table 15. Port Alternate Function Mapping (Non 8-Pin Parts) (Continued)

Notes:

2. Whether PA0/PA6 takes on the timer input or timer output complement function depends on the timer configuration. See the <u>Timer Pin Signal Operation</u> section on page 84 for details.

Because there are at most two choices of alternate function for any pin of Port B, the Alternate Function Set Register AFS2 is not used to select the function. Alternate function selection must also be enabled. See the <u>Port</u> <u>A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

4. V<sub>REF</sub> is available on PB5 in 28-pin products and on PC2 in 20-pin parts.

Because there are at most two choices of alternate function for any pin of Port C, the Alternate Function Set Register AFS2 is not used to select the function. Alternate function selection must also be enabled. See the <u>Port</u> <u>A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

6. Because there is only a single alternate function for the Port PD0 pin, the Alternate Function Set registers are not implemented for Port D. Enabling alternate function selections automatically enables the associated alternate function. See the Port A–D Alternate Function Subregisters (PxAF) section on page 47 for details.

Because there is only a single alternate function for each Port A pin, the Alternate Function Set registers are not implemented for Port A. Enabling alternate function selections automatically enables the associated alternate function. See the <u>Port A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

| Bit           | Description (Continued)                                                  |

|---------------|--------------------------------------------------------------------------|

| [4]<br>U0RENL | UART 0 Receive Interrupt Request Enable Low Bit                          |

| [3]<br>U0TENL | UART 0 Transmit Interrupt Request Enable Low Bit                         |

| [2:1]         | <b>Reserved</b><br>These bits are reserved and must be programmed to 00. |

| [0]<br>ADCENL | ADC Interrupt Request Enable Low Bit                                     |

#### **IRQ1 Enable High and Low Bit Registers**

Table 41 describes the priority control for IRQ1. The IRQ1 Enable High and Low Bit registers, shown in Tables 41 and 42, form a priority-encoded enabling for interrupts in the Interrupt Request 1 Register.

| IRQ1ENH[x]                           | IRQ1ENL[x] | Priority | Description |  |  |  |  |

|--------------------------------------|------------|----------|-------------|--|--|--|--|

| 0                                    | 0          | Disabled | Disabled    |  |  |  |  |

| 0                                    | 1          | Level 1  | Low         |  |  |  |  |

| 1                                    | 0          | Level 2  | Medium      |  |  |  |  |

| 1                                    | 1          | Level 3  | High        |  |  |  |  |

| Note: x indicates register bits 0–7. |            |          |             |  |  |  |  |

#### Table 41. IRQ1 Enable and Priority Encoding

- Set the initial logic level (High or Low) for the Timer Output alternate function, if appropriate

- 2. Write to the Timer High and Low Byte registers to set the starting count value.

- 3. Write to the Timer Reload High and Low Byte registers to set the Compare value.

- 4. Enable the timer interrupt, if appropriate and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 6. Write to the Timer Control Register to enable the timer and initiate counting.

In COMPARE Mode, the system clock always provides the timer input. The Compare time can be calculated by the following equation:

COMPARE Mode Time (s) = (Compare Value – Start Value) × Prescale System Clock Frequency (Hz)

#### GATED Mode

In GATED Mode, the timer counts only when the Timer Input signal is in its active state (asserted), as determined by the TPOL bit in the Timer Control Register. When the Timer Input signal is asserted, counting begins. A timer interrupt is generated when the Timer Input signal is deasserted or a timer reload occurs. To determine if a Timer Input signal deassertion generated the interrupt, read the associated GPIO input value and compare to the value stored in the TPOL bit.

The timer counts up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. When reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes (assuming the Timer Input signal remains asserted). Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer reset.

Observe the following steps for configuring a timer for GATED Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Set the Capture edge (rising or falling) for the Timer Input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the Compare value.

- 4. Enable the timer interrupt, if appropriate and set the timer interrupt priority by writing to the relevant interrupt registers.By default, the timer interrupt are generated for both input capture and reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the reload event by setting TICONFIG field of the TxCTL0 Register.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control Register to enable the timer.

- 7. Counting begins on the first appropriate transition of the Timer Input signal. No interrupt is generated by this first edge.

In CAPTURE/COMPARE Mode, the elapsed time from timer start to Capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

#### **Reading the Timer Count Values**

The current count value in the timers can be read while counting (enabled). This capability has no effect on timer operation. When the timer is enabled and the Timer High Byte Register is read, the contents of the Timer Low Byte Register are placed in a holding register. A subsequent read from the Timer Low Byte Register returns the value in the holding register. This operation allows accurate reads of the full 16-bit timer count value while enabled. When the timers are not enabled, a read from the Timer Low Byte Register returns the actual value in the counter.

#### **Timer Pin Signal Operation**

The timer output function is a GPIO port pin alternate function. The Timer Output is toggled every time the counter is reloaded.

### Timer 0–1 PWM High and Low Byte Registers

The Timer 0–1 PWM High and Low Byte (TxPWMH and TxPWML) registers, shown in Tables 56 and 57, control Pulse-Width Modulator (PWM) operations. These registers also store the Capture values for the CAPTURE and CAPTURE/COMPARE modes.

| Bit     | 7          | 6    | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|------------|------|-----|-----|-----|-----|-----|-----|

| Field   |            | PWMH |     |     |     |     |     |     |

| RESET   | 0          | 0    | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W        | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | F04H, F0CH |      |     |     |     |     |     |     |

#### Table 56. Timer 0–1 PWM High Byte Register (TxPWMH)

#### Table 57. Timer 0–1 PWM Low Byte Register (TxPWML)

| Bit     | 7          | 6    | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|------------|------|-----|-----|-----|-----|-----|-----|

| Field   |            | PWML |     |     |     |     |     |     |

| RESET   | 0          | 0    | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W        | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | F05H, F0DH |      |     |     |     |     |     |     |

#### Bit Description

| [7:0] | Pulse-Width Modulator High and Low Bytes                                                     |

|-------|----------------------------------------------------------------------------------------------|

| PWMH, | These two bytes, {PWMH[7:0], PWML[7:0]}, form a 16-bit value that is compared to the current |

| PWML  | 16-bit timer count. When a match occurs, the PWM output changes state. The PWM output        |

|       | value is set by the TPOL bit in the Timer Control Register (TxCTL1) Register.                |

The TxPWMH and TxPWML registers also store the 16-bit captured timer value when operating in CAPTURE or CAPTURE/COMPARE modes.

Rate Generator to function as an additional counter if the UART functionality is not employed.

#### **UART Baud Rate Generator**

The UART Baud Rate Generator creates a lower frequency baud rate clock for data transmission. The input to the Baud Rate Generator is the system clock. The UART Baud Rate High and Low Byte registers combine to create a 16-bit baud rate divisor value (BRG[15:0]) that sets the data transmission rate (baud rate) of the UART. The UART data rate is calculated using the following equation:

UART Data Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

When the UART is disabled, the Baud Rate Generator functions as a basic 16-bit timer with an interrupt upon time-out. Observe the following steps to configure the Baud Rate Generator as a timer with an interrupt upon time-out:

- 1. Disable the UART by clearing the REN and TEN bits in the UART Control 0 Register to 0.

- 2. Load the acceptable 16-bit count value into the UART Baud Rate High and Low Byte registers.

- 3. Enable the Baud Rate Generator timer function and associated interrupt by setting the BRGCTL bit in the UART Control 1 Register to 1.

When configured as a general purpose timer, the interrupt interval is calculated using the following equation:

Interrupt Interval(s) = System Clock Period (s)  $\times$  BRG[15:0]

# **UART Control Register Definitions**

The UART Control registers support the UART and the associated Infrared Encoder/ Decoders. For more information about infrared operation, see the <u>Infrared Encoder/</u><u>Decoder</u> chapter on page 120.

### **UART Control 0 and Control 1 Registers**

The UART Control 0 (UxCTL0) and Control 1 (UxCTL1) registers, shown in Tables 63 and 64, configure the properties of the UART's transmit and receive operations. The UART Control registers must not be written while the UART is enabled.

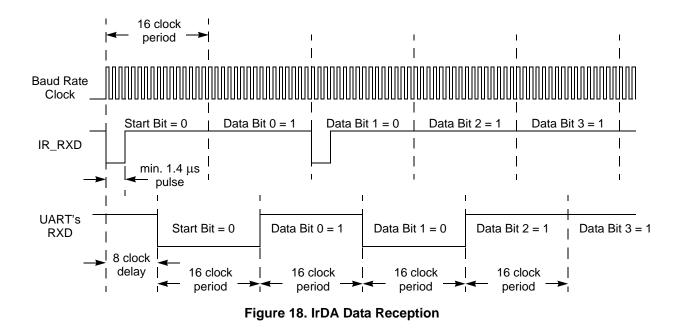

#### **Receiving IrDA Data**

Data received from the infrared transceiver using the IR\_RXD signal through the RXD pin is decoded by the infrared endec and passed to the UART. The UART's baud rate clock is used by the infrared endec to generate the demodulated signal (RXD) that drives the UART. Each UART/Infrared data bit is 16-clocks wide. Figure 18 displays data reception. When the infrared endec is enabled, the UART's RXD signal is internal to the Z8 Encore! XP F082A Series products while the IR\_RXD signal is received through the RXD pin.

#### **Infrared Data Reception**

**Caution:** The system clock frequency must be at least 1.0MHz to ensure proper reception of the 1.4µs minimum width pulses allowed by the IrDA standard.

#### **Endec Receiver Synchronization**

The IrDA receiver uses a local baud rate clock counter (0 to 15 clock periods) to generate an input stream for the UART and to create a sampling window for detection of incoming pulses. The generated UART input (UART RXD) is delayed by 8 baud rate clock periods with respect to the incoming IrDA data stream. When a falling edge in the input data stream is detected, the Endec counter is reset. When the count reaches a value of 8, the UART RXD value is updated to reflect the value of the decoded data. When the count reaches 12 baud clock periods, the sampling window for the next incoming pulse opens.

Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

125

Figure 19. Analog-to-Digital Converter Block Diagram

# Operation

In both SINGLE-ENDED and DIFFERENTIAL modes, the effective output of the ADC is an 11-bit, signed, two's complement digital value. In DIFFERENTIAL Mode, the ADC can output values across the entire 11-bit range, from -1024 to +1023. In SINGLE-ENDED Mode, the output generally ranges from 0 to +1023, but offset errors can cause small negative values. in DEBUG Mode or the Flash Read Protect Option bit is enabled, this command reads and discards one byte.

DBG  $\leftarrow$  12H DBG  $\leftarrow$  1-5 byte opcode

# **On-Chip Debugger Control Register Definitions**

This section describes the features of the On-Chip Debugger Control and Status registers.

### **OCD Control Register**

The OCD Control Register controls the state of the On-Chip Debugger. This register is used to enter or exit DEBUG Mode and to enable the BRK instruction. It can also reset the Z8 Encore! XP F082A Series device.

A reset and stop function can be achieved by writing 81H to this register. A reset and go function can be achieved by writing 41H to this register. If the device is in DEBUG Mode, a run function can be implemented by writing 40H to this register.

| Bit   | 7       | 6     | 5      | 4 | 3        | 2 | 1 | 0   |

|-------|---------|-------|--------|---|----------|---|---|-----|

| Field | DBGMODE | BRKEN | DBGACK |   | Reserved |   |   |     |

| RESET | 0       | 0     | 0      | 0 | 0        | 0 | 0 | 0   |

| R/W   | R/W     | R/W   | R/W    | R | R        | R | R | R/W |

Table 110. OCD Control Register (OCDCTL)

#### Bit Description

#### [7] **DEBUG Mode** DBGMODE The device enters DEBUG Mode when this bit is 1. When in DEBUG Mode, the eZ8 CPU stops fetching new instructions. Clearing this bit causes the eZ8 CPU to restart. This bit is automatically set when a BRK instruction is decoded and Breakpoints are enabled. If the Flash Read Protect Option Bit is enabled, this bit can only be cleared by resetting the device. It cannot be written to 0. 0 = The Z8 Encore! XP F082A Series device is operating in NORMAL Mode. 1 = The Z8 Encore! XP F082A Series device is in DEBUG Mode. [6] **Breakpoint Enable** BRKEN This bit controls the behavior of the BRK instruction (opcode 00H). By default, Breakpoints are disabled and the BRK instruction behaves similar to an NOP instruction. If this bit is 1, when a BRK instruction is decoded, the DBGMODE bit of the OCDCTL Register is automatically set to 1. 0 = Breakpoints are disabled. 1 = Breakpoints are enabled.

# **Crystal Oscillator**

The products in the Z8 Encore! XP F082A Series contain an on-chip crystal oscillator for use with external crystals with 32kHz to 20MHz frequencies. In addition, the oscillator supports external RC networks with oscillation frequencies up to 4MHz or ceramic resonators with frequencies up to 8MHz. The on-chip crystal oscillator can be used to generate the primary system clock for the internal eZ8 CPU and the majority of the on-chip peripherals. Alternatively, the  $X_{IN}$  input pin can also accept a CMOS-level clock input signal (32kHz–20MHz). If an external clock generator is used, the  $X_{OUT}$  pin must be left unconnected. The Z8 Encore! XP F082A Series products do not contain an internal clock divider. The frequency of the signal on the  $X_{IN}$  input pin determines the frequency of the system clock.

**Note:** Although the X<sub>IN</sub> pin can be used as an input for an external clock generator, the CLKIN pin is better suited for such use (see the <u>System Clock Selection</u> section on page 193).

# **Operating Modes**

The Z8 Encore! XP F082A Series products support four oscillator modes:

- Minimum power for use with very low frequency crystals (32kHz-1MHz)

- Medium power for use with medium frequency crystals or ceramic resonators (0.5 MHz to 8MHz)

- Maximum power for use with high frequency crystals (8MHz to 20MHz)

- On-chip oscillator configured for use with external RC networks (<4MHz)

The oscillator mode is selected via user-programmable Flash option bits. See **the** <u>Flash</u> <u>Option Bits</u> chapter on page 159 for information.

# **Crystal Oscillator Operation**

The XTLDIS Flash option bit controls whether the crystal oscillator is enabled during reset. The crystal may later be disabled after reset if a new oscillator has been selected as the system clock. If the crystal is manually enabled after reset through the OSCCTL Register, the user code must wait at least 1000 crystal oscillator cycles for the crystal to stabilize. After this, the crystal oscillator may be selected as the system clock.

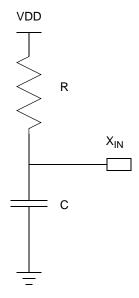

# **Oscillator Operation with an External RC Network**

Figure 28 displays a recommended configuration for connection with an external resistorcapacitor (RC) network.

#### Figure 28. Connecting the On-Chip Oscillator to an External RC Network

An external resistance value of  $45 \text{ k}\Omega$  is recommended for oscillator operation with an external RC network. The minimum resistance value to ensure operation is 40 k $\Omega$ . The typical oscillator frequency can be estimated from the values of the resistor (*R* in k $\Omega$ ) and capacitor (*C* in pF) elements using the following equation:

Oscillator Frequency (kHz) =  $\frac{1 \times 10^6}{(0.4 \times R \times C) + (4 \times C)}$

Figure 29 displays the typical  $(3.3 \text{ V} \text{ and } 25^{\circ}\text{C})$  oscillator frequency as a function of the capacitor (C, in pF) employed in the RC network assuming a  $45 \text{ K}\Omega$  external resistor. For very small values of C, the parasitic capacitance of the oscillator X<sub>IN</sub> pin and the printed circuit board must be included in the estimation of the oscillator frequency.

It is possible to operate the RC oscillator using only the parasitic capacitance of the package and printed circuit board. To minimize sensitivity to external parasitics, external capacitance values in excess of 20pF are recommended.

| Notation | Description    | Operand | Range                                                                                                                     |

|----------|----------------|---------|---------------------------------------------------------------------------------------------------------------------------|

| Vector   | Vector address | Vector  | Vector represents a number in the range of 00H to FFH.                                                                    |

| Х        | Indexed        | #Index  | The register or register pair to be indexed is off-<br>set by the signed Index value (#Index) in a +127<br>to –128 range. |

#### Table 118. Notational Shorthand (Continued)

Table 119 lists additional symbols that are used throughout the Instruction Summary and Instruction Set Description sections.

| Symbol | Definition                |

|--------|---------------------------|

| dst    | Destination Operand       |

| src    | Source Operand            |

| @      | Indirect Address Prefix   |

| SP     | Stack Pointer             |

| PC     | Program Counter           |

| FLAGS  | Flags Register            |

| RP     | Register Pointer          |

| #      | Immediate Operand Prefix  |

| В      | Binary Number Suffix      |

| %      | Hexadecimal Number Prefix |

| Н      | Hexadecimal Number Suffix |

|        |                           |

Table 119. Additional Symbols

Assignment of a value is indicated by an arrow, as shown in the following example.

$dst \leftarrow dst + src$

This example indicates that the source data is added to the destination data; the result is stored in the destination location.

# eZ8 CPU Instruction Classes

eZ8 CPU instructions can be divided functionally into the following groups:

- Arithmetic

- Bit Manipulation

| ning (Continued) |  |

|------------------|--|

|                  |  |

#### Table 139. Analog-to-Digital Converter Electrical Characteristics and Timing (Continued)

#### $V_{DD}$ = 3.0 V to 3.6 V T<sub>A</sub> = 0°C to +70°C (unless otherwise stated)

| Symbol         | Parameter                               | Minimum | Typical | Maximum              | Units                          | Conditions                                                                                                                                                                                                                                |

|----------------|-----------------------------------------|---------|---------|----------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | Continuous Conversion<br>Time           | -       | 256     | _                    | Sys-<br>tem<br>clock<br>cycles | All measurements but temperature sensor                                                                                                                                                                                                   |

|                |                                         |         | 512     |                      |                                | Temperature sensor measurement                                                                                                                                                                                                            |

|                | Signal Input Bandwidth                  | _       | 10      |                      | kHz                            | As defined by -3 dB point                                                                                                                                                                                                                 |

| R <sub>S</sub> | Analog Source<br>Impedance <sup>4</sup> | _       | _       | 10                   | kΩ                             | In unbuffered mode                                                                                                                                                                                                                        |

|                |                                         |         |         | 500                  | kΩ                             | In buffered modes                                                                                                                                                                                                                         |

| Zin            | Input Impedance                         | -       | 150     |                      | kΩ                             | In unbuffered mode at 20MHz <sup>5</sup>                                                                                                                                                                                                  |

|                |                                         | 10      | _       |                      | MΩ                             | In buffered modes                                                                                                                                                                                                                         |

| Vin            | Input Voltage Range                     | 0       |         | V <sub>DD</sub>      | V                              | Unbuffered Mode                                                                                                                                                                                                                           |

|                |                                         | 0.3     |         | V <sub>DD</sub> -1.1 | V                              | Buffered Modes<br>These values define<br>the range over which<br>the ADC performs<br>within spec; exceeding<br>these values does not<br>cause damage or insta-<br>bility; see DC Charac-<br>teristics for absolute<br>pin voltage limits. |

Notes:

1. Analog source impedance affects the ADC offset voltage (because of pin leakage) and input settling time.

2. Devices are factory calibrated at  $V_{DD}$  = 3.3 V and  $T_A$  = +30°C, so the ADC is maximally accurate under these conditions.

3. LSBs are defined assuming 10-bit resolution.

- 4. This is the maximum recommended resistance seen by the ADC input pin.

- 5. The input impedance is inversely proportional to the system clock frequency.

|                    | o 3.6 V<br>+105°C                             |         |            |                    |       |                                 |

|--------------------|-----------------------------------------------|---------|------------|--------------------|-------|---------------------------------|

| Symbol             | Parameter                                     | Minimum | Typical    | Maximum            | Units | Conditions                      |

| Av                 | Open loop voltage gain                        |         | 80         |                    | dB    |                                 |

| GBW                | Gain/Bandwidth product                        |         | 500        |                    | kHz   |                                 |

| РМ                 | Phase Margin                                  |         | 50         |                    | deg   | Assuming 13pF load capacitance. |

| V <sub>osLPO</sub> | Input Offset Voltage                          |         | <u>+</u> 1 | <u>+</u> 4         | mV    |                                 |

| V <sub>osLPO</sub> | Input Offset Voltage (Tem-<br>perature Drift) |         | 1          | 10                 | μV/C  |                                 |

| V <sub>IN</sub>    | Input Voltage Range                           | 0.3     |            | V <sub>DD</sub> -1 | V     |                                 |

| V <sub>OUT</sub>   | Output Voltage Range                          | 0.3     |            | V <sub>DD</sub> -1 | V     | Ι <sub>ΟUT</sub> = 45μΑ.        |

#### Table 140. Low Power Operational Amplifier Electrical Characteristics

#### Table 141. Comparator Electrical Characteristics

| V <sub>DD</sub> = 2.7 V to 3.6 V<br>T <sub>A</sub> = -40°C to +105°C |                                            |                 |            |                    |       |                         |  |

|----------------------------------------------------------------------|--------------------------------------------|-----------------|------------|--------------------|-------|-------------------------|--|

| Symbol                                                               | Parameter                                  | Minimum         | Typical    | Maximum            | Units | Conditions              |  |

| V <sub>OS</sub>                                                      | Input DC Offset                            |                 | 5          |                    | mV    |                         |  |

| V <sub>CREF</sub>                                                    | Programmable Internal<br>Reference Voltage |                 | <u>+</u> 5 |                    | %     | 20- and 28-pin devices. |  |

|                                                                      |                                            |                 | <u>+</u> 3 |                    | %     | 8-pin devices.          |  |

| T <sub>PROP</sub>                                                    | Propagation Delay                          |                 | 200        |                    | ns    |                         |  |

| V <sub>HYS</sub>                                                     | Input Hysteresis                           |                 | 4          |                    | mV    |                         |  |

| V <sub>IN</sub>                                                      | Input Voltage Range                        | V <sub>SS</sub> |            | V <sub>DD</sub> -1 | V     |                         |  |

### General Purpose I/O Port Output Timing

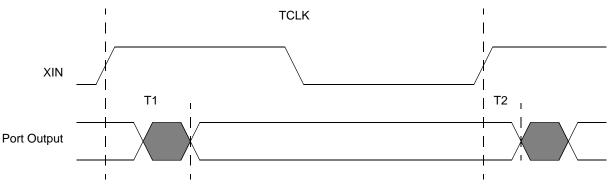

Figure 35 and Table 144 provide timing information for GPIO port pins.

| Figure 35 | . GPIO | Port | Output | Timing |

|-----------|--------|------|--------|--------|

|-----------|--------|------|--------|--------|

|                |                                                 | Delay (ns) |         |  |

|----------------|-------------------------------------------------|------------|---------|--|

| Parameter      | Abbreviation                                    | Minimum    | Maximum |  |

| GPIO port pi   | ns                                              |            |         |  |

| T <sub>1</sub> | X <sub>IN</sub> Rise to Port Output Valid Delay | -          | 15      |  |

| T <sub>2</sub> | X <sub>IN</sub> Rise to Port Output Hold Time   | 2          | _       |  |

#### Table 144. GPIO Port Output Timing

#### 242

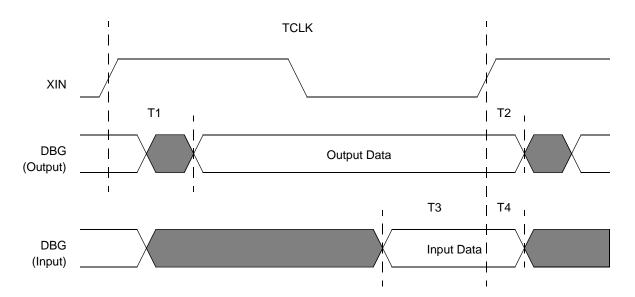

# **On-Chip Debugger Timing**

Figure 36 and Table 145 provide timing information for the DBG pin. The DBG pin timing specifications assume a 4 ns maximum rise and fall time.

Figure 36. On-Chip Debugger Timing

|                |                                              | Delay (ns) |         |

|----------------|----------------------------------------------|------------|---------|

| Parameter      | Abbreviation                                 | Minimum    | Maximum |

| DBG            |                                              |            |         |

| T <sub>1</sub> | X <sub>IN</sub> Rise to DBG Valid Delay      | _          | 15      |

| T <sub>2</sub> | X <sub>IN</sub> Rise to DBG Output Hold Time | 2          | -       |

| T <sub>3</sub> | DBG to XIN Rise Input Setup Time             | 5          | -       |

| T <sub>4</sub> | DBG to XIN Rise Input Hold Time              | 5          | -       |

#### Table 145. On-Chip Debugger Timing