Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 23                                                           |

| Program Memory Size        | 1KB (1K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 16 × 8                                                       |

| RAM Size                   | 256 x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 8x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 105°C (TA)                                           |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 28-SSOP (0.173", 4.40mm Width)                               |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f012ahj020eg    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

| Table 59. | Watchdog Timer Control Register (WDTCTL)                   |

|-----------|------------------------------------------------------------|

| Table 60. | Watchdog Timer Reload Upper Byte Register (WDTU)           |

| Table 61. | Watchdog Timer Reload High Byte Register (WDTH)            |

| Table 62. | Watchdog Timer Reload Low Byte Register (WDTL)             |

| Table 63. | UART Control 0 Register (U0CTL0) 111                       |

| Table 64. | UART Control 1 Register (U0CTL1) 112                       |

| Table 65. | UART Status 0 Register (U0STAT0) 114                       |

| Table 66. | UART Status 1 Register (U0STAT1) 115                       |

| Table 67. | UART Transmit Data Register (U0TXD) 116                    |

| Table 68. | UART Receive Data Register (U0RXD) 116                     |

| Table 69. | UART Address Compare Register (U0ADDR) 117                 |

| Table 70. | UART Baud Rate High Byte Register (U0BRH) 117              |

| Table 71. | UART Baud Rate Low Byte Register (U0BRL) 117               |

| Table 72. | UART Baud Rates                                            |

| Table 73. | ADC Control Register 0 (ADCCTL0)                           |

| Table 74. | ADC Control/Status Register 1 (ADCCTL1)                    |

| Table 75. | ADC Data High Byte Register (ADCD_H) 137                   |

| Table 76. | ADC Data Low Byte Register (ADCD_L) 137                    |

| Table 77. | Comparator Control Register (CMP0) 141                     |

| Table 78. | Z8 Encore! XP F082A Series Flash Memory Configurations 146 |

| Table 79. | Flash Code Protection Using the Flash Option Bits          |

| Table 80. | Flash Status Register (FSTAT) 155                          |

| Table 81. | Flash Control Register (FCTL) 155                          |

| Table 82. | Flash Page Select Register (FPS) 156                       |

| Table 83. | Flash Sector Protect Register (FPROT) 157                  |

| Table 84. | Flash Frequency High Byte Register (FFREQH)                |

| Table 85. | Flash Frequency Low Byte Register (FFREQL)                 |

| Table 86. | Trim Bit Address Register (TRMADR) 161                     |

| Table 87. | Trim Bit Data Register (TRMDR) 162                         |

| Table 88. | Flash Option Bits at Program Memory Address 0000H 162      |

| Address (Hex)           | Register Description    | Mnemonic | Reset (Hex) | Page       |  |

|-------------------------|-------------------------|----------|-------------|------------|--|

| F85                     | Reserved                | —        | XX          |            |  |

| <b>Oscillator Contr</b> | ol                      |          |             |            |  |

| F86                     | Oscillator Control      | OSCCTL   | A0          | <u>196</u> |  |

| F87–F8F                 | Reserved                | _        | XX          |            |  |

| Comparator 0            |                         |          |             |            |  |

| F90                     | Comparator 0 Control    | CMP0     | 14          | <u>141</u> |  |

| F91–FBF                 | Reserved                | _        | XX          |            |  |

| Interrupt Contro        | oller                   |          |             |            |  |

| FC0                     | Interrupt Request 0     | IRQ0     | 00          | <u>60</u>  |  |

| FC1                     | IRQ0 Enable High Bit    | IRQ0ENH  | 00          | <u>63</u>  |  |

| FC2                     | IRQ0 Enable Low Bit     | IRQ0ENL  | 00          | <u>63</u>  |  |

| FC3                     | Interrupt Request 1     | IRQ1     | 00          | <u>61</u>  |  |

| FC4                     | IRQ1 Enable High Bit    | IRQ1ENH  | 00          | <u>65</u>  |  |

| FC5                     | IRQ1 Enable Low Bit     | IRQ1ENL  | 00          | <u>65</u>  |  |

| FC6                     | Interrupt Request 2     | IRQ2     | 00          | <u>62</u>  |  |

| FC7                     | IRQ2 Enable High Bit    | IRQ2ENH  | 00          | <u>66</u>  |  |

| FC8                     | IRQ2 Enable Low Bit     | IRQ2ENL  | 00          | <u>67</u>  |  |

| FC9–FCC                 | Reserved                | —        | XX          |            |  |

| FCD                     | Interrupt Edge Select   | IRQES    | 00          | <u>68</u>  |  |

| FCE                     | Shared Interrupt Select | IRQSS    | 00          | <u>68</u>  |  |

| FCF                     | Interrupt Control       | IRQCTL   | 00          | <u>69</u>  |  |

| GPIO Port A             |                         |          |             |            |  |

| FD0                     | Port A Address          | PAADDR   | 00          | <u>44</u>  |  |

| FD1                     | Port A Control          | PACTL    | 00          | <u>46</u>  |  |

| FD2                     | Port A Input Data       | PAIN     | XX          | <u>46</u>  |  |

| FD3                     | Port A Output Data      | PAOUT    | 00          | <u>46</u>  |  |

| GPIO Port B             |                         |          |             |            |  |

| FD4                     | Port B Address          | PBADDR   | 00          | <u>44</u>  |  |

| FD5                     | Port B Control          | PBCTL    | 00          | <u>46</u>  |  |

| FD6                     | Port B Input Data       | PBIN     | XX          | <u>46</u>  |  |

| FD7                     | Port B Output Data      | PBOUT    | 00          | <u>46</u>  |  |

| GPIO Port C             |                         |          |             |            |  |

| FD8                     | Port C Address          | PCADDR   | 00          | 44         |  |

### Table 7. Register File Address Map (Continued)

1. XX = Undefined.

2. Refer to the eZ8 CPU Core User Manual (UM0128).

| FDAFFDBFGPIO Port DFDCFFDDF   | Port C Control<br>Port C Input Data<br>Port C Output Data<br>Port D Address<br>Port D Control | PCCTL<br>PCIN<br>PCOUT<br>PDADDR | 00<br>XX<br>00 | <u>46</u><br><u>46</u><br><u>46</u> |

|-------------------------------|-----------------------------------------------------------------------------------------------|----------------------------------|----------------|-------------------------------------|

| FDBFGPIO Port DFDCFFDDF       | Port C Output Data Port D Address                                                             | PCOUT                            | 00             |                                     |

| GPIO Port D<br>FDC F<br>FDD F | Port D Address                                                                                |                                  |                | <u>46</u>                           |

| FDC F<br>FDD F                |                                                                                               | PDADDR                           |                |                                     |

| FDD F                         |                                                                                               | PDADDR                           |                |                                     |

|                               | Port D Control                                                                                |                                  | 00             | <u>44</u>                           |

| FDE F                         |                                                                                               | PDCTL                            | 00             | <u>46</u>                           |

|                               | Reserved                                                                                      | —                                | XX             |                                     |

| FDF F                         | Port D Output Data                                                                            | PDOUT                            | 00             | <u>46</u>                           |

| FE0–FEF F                     | Reserved                                                                                      | _                                | XX             |                                     |

| Watchdog Timer (              | WDT)                                                                                          |                                  |                |                                     |

| FF0 F                         | Reset Status (Read-only)                                                                      | RSTSTAT                          | X0             | <u>29</u>                           |

| Ī                             | Watchdog Timer Control (Write-only)                                                           | WDTCTL                           | N/A            | <u>96</u>                           |

| FF1 V                         | Watchdog Timer Reload Upper Byte                                                              | WDTU                             | 00             | <u>97</u>                           |

| FF2 V                         | Watchdog Timer Reload High Byte                                                               | WDTH                             | 04             | <u>97</u>                           |

| FF3 V                         | Watchdog Timer Reload Low Byte                                                                | WDTL                             | 00             | <u>98</u>                           |

| FF4–FF5 F                     | Reserved                                                                                      | _                                | XX             |                                     |

| Trim Bit Control              |                                                                                               |                                  |                |                                     |

| FF6 1                         | Trim Bit Address                                                                              | TRMADR                           | 00             | <u>161</u>                          |

| FF7 1                         | Trim Bit Data                                                                                 | TRMDR                            | 00             | <u>162</u>                          |

| Flash Memory Cor              | ntroller                                                                                      |                                  |                |                                     |

| FF8 F                         | Flash Control                                                                                 | FCTL                             | 00             | <u>155</u>                          |

| FF8 F                         | Flash Status                                                                                  | FSTAT                            | 00             | <u>155</u>                          |

| FF9 F                         | Flash Page Select                                                                             | FPS                              | 00             | <u>156</u>                          |

| F                             | Flash Sector Protect                                                                          | FPROT                            | 00             | <u>157</u>                          |

| FFA F                         | Flash Programming Frequency High Byte                                                         | FFREQH                           | 00             | <u>158</u>                          |

| FFB F                         | Flash Programming Frequency Low Byte                                                          | FFREQL                           | 00             | <u>158</u>                          |

| eZ8 CPU                       |                                                                                               |                                  |                |                                     |

| FFC F                         | Flags                                                                                         | _                                | XX             | See                                 |

| FFD F                         | Register Pointer                                                                              | RP                               | XX             | foot-                               |

| FFE S                         | Stack Pointer High Byte                                                                       | SPH                              | XX             | -note 2                             |

| FFF S                         | Stack Pointer Low Byte                                                                        | SPL                              | XX             |                                     |

| Notes:                        |                                                                                               |                                  |                |                                     |

#### Table 7. Register File Address Map (Continued)

1. XX = Undefined.

2. Refer to the <u>eZ8</u> CPU Core User Manual (UM0128).

# General-Purpose Input/Output

The Z8 Encore! XP F082A Series products support a maximum of 25 port pins (Ports A–D) for general-purpose input/output (GPIO) operations. Each port contains control and data registers. The GPIO control registers determine data direction, open-drain, output drive current, programmable pull-ups, Stop Mode Recovery functionality and alternate pin functions. Each port pin is individually programmable. In addition, the Port C pins are capable of direct LED drive at programmable drive strengths.

### **GPIO Port Availability By Device**

Table 14 lists the port pins available with each device and package type.

| Devices                                                                                                                                  | Package | ADC | Port A | Port B | Port C | Port D | Total I/O |

|------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|--------|--------|--------|--------|-----------|

| Z8F082ASB, Z8F082APB, Z8F082AQB<br>Z8F042ASB, Z8F042APB, Z8F042AQB<br>Z8F022ASB, Z8F022APB, Z8F022AQB<br>Z8F012ASB, Z8F012APB, Z8F012AQB | 8-pin   | Yes | [5:0]  | No     | No     | No     | 6         |

| Z8F081ASB, Z8F081APB, Z8F081AQB<br>Z8F041ASB, Z8F041APB, Z8F041AQB<br>Z8F021ASB, Z8F021APB, Z8F021AQB<br>Z8F011ASB, Z8F011APB, Z8F011AQB | 8-pin   | No  | [5:0]  | No     | No     | No     | 6         |

| Z8F082APH, Z8F082AHH, Z8F082ASH<br>Z8F042APH, Z8F042AHH, Z8F042ASH<br>Z8F022APH, Z8F022AHH, Z8F022ASH<br>Z8F012APH, Z8F012AHH, Z8F012ASH | 20-pin  | Yes | [7:0]  | [3:0]  | [3:0]  | [0]    | 17        |

| Z8F081APH, Z8F081AHH, Z8F081ASH<br>Z8F041APH, Z8F041AHH, Z8F041ASH<br>Z8F021APH, Z8F021AHH, Z8F021ASH<br>Z8F011APH, Z8F011AHH, Z8F011ASH | 20-pin  | No  | [7:0]  | [3:0]  | [3:0]  | [0]    | 17        |

| Z8F082APJ, Z8F082ASJ, Z8F082AHJ<br>Z8F042APJ, Z8F042ASJ, Z8F042AHJ<br>Z8F022APJ, Z8F022ASJ, Z8F022AHJ<br>Z8F012APJ, Z8F012ASJ, Z8F012AHJ | 28-pin  | Yes | [7:0]  | [5:0]  | [7:0]  | [0]    | 23        |

| Z8F081APJ, Z8F081ASJ, Z8F081AHJ<br>Z8F041APJ, Z8F041ASJ, Z8F041AHJ<br>Z8F021APJ, Z8F021ASJ, Z8F021AHJ<br>Z8F011APJ, Z8F011ASJ, Z8F011AHJ | 28-pin  | No  | [7:0]  | [7:0]  | [7:0]  | [0]    | 25        |

Table 14. Port Availability by Device and Package Type

### Port A–D Pull-up Enable Subregisters

The Port A–D Pull-up Enable Subregister, shown in Table 26, is accessed through the Port A–D Control Register by writing 06H to the Port A–D Address Register. Setting the bits in the Port A–D Pull-up Enable subregisters enables a weak internal resistive pull-up on the specified port pins.

| Bit     | 7                                                                                     | 6                                                           | 5     | 4     | 3     | 2     | 1     | 0     |  |  |

|---------|---------------------------------------------------------------------------------------|-------------------------------------------------------------|-------|-------|-------|-------|-------|-------|--|--|

| Field   | PPUE7                                                                                 | PPUE6                                                       | PPUE5 | PPUE4 | PPUE3 | PPUE2 | PPUE1 | PPUE0 |  |  |

| RESET   |                                                                                       | 00H (Ports A-C); 01H (Port D); 04H (Port A of 8-pin device) |       |       |       |       |       |       |  |  |

| R/W     | R/W                                                                                   | R/W                                                         | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |  |  |

| Address | If 06H in Port A–D Address Register, accessible through the Port A–D Control Register |                                                             |       |       |       |       |       |       |  |  |

| Bit     | Description                                                                           | n                                                           |       |       |       |       |       |       |  |  |

| Table 26 | Dort    | וויים ח_א | IIn Enab |           | istors ( |        |

|----------|---------|-----------|----------|-----------|----------|--------|

| Table 20 | ). FUIL | A-D Fuii  | -∪p ⊏nau | le Subreg | isters ( | FXFUE) |

| Bit        | Description                                       |

|------------|---------------------------------------------------|

| [7:0]      | Port Pull-up Enabled                              |

| PPUEx      | 0 = The weak pull-up on the port pin is disabled. |

|            | 1 = The weak pull-up on the port pin is enabled.  |

| Note: x ii | ndicates the specific GPIO port pin number (7–0). |

#### Port A–D Alternate Function Set 1 Subregisters

The Port A–D Alternate Function Set1 Subregister, shown in Table 27, is accessed through the Port A–D Control Register by writing 07H to the Port A–D Address Register. The Alternate Function Set 1 subregisters selects the alternate function available at a port pin. Alternate Functions selected by setting or clearing bits of this register are defined in the <u>GPIO Alternate Functions</u> section on page 37.

**Note:** Alternate function selection on port pins must also be enabled as described in the <u>Port A</u>– <u>D Alternate Function Subregisters</u> section on page 47.

| Bit     | 7          | 6                                                                                     | 5        | 4      | 3      | 2      | 1      | 0      |

|---------|------------|---------------------------------------------------------------------------------------|----------|--------|--------|--------|--------|--------|

| Field   | PAFS17     | PAFS16                                                                                | PAFS15   | PAFS14 | PAFS13 | PAFS12 | PAFS11 | PAFS10 |

| RESET   | 0          | 0                                                                                     | 0        | 0      | 0      | 0      | 0      | 0      |

| R/W     | R/W        | R/W                                                                                   | R/W      | R/W    | R/W    | R/W    | R/W    | R/W    |

| Address | If 07H in  | If 07H in Port A–D Address Register, accessible through the Port A–D Control Register |          |        |        |        |        |        |

| Bit     | Descriptio | n                                                                                     |          |        |        |        |        |        |

| [7:0]   | •          | ate Functio                                                                           | on Set 1 |        |        |        |        |        |

| Table 27. Port A–D Alternate Function Set | 1 Subregisters (PxAFS1) |

|-------------------------------------------|-------------------------|

|                                           |                         |

| Bit   | Description                                                                      |

|-------|----------------------------------------------------------------------------------|

| [7:0] | Port Alternate Function Set 1                                                    |

| PAFSx | 0 = Port Alternate Function selected, as defined in Tables 15 and 16 on page 43. |

|       | 1 = Port Alternate Function selected, as defined in Tables 15 and 16 on page 43. |

Note: x indicates the specific GPIO port pin number (7–0).

#### Port A–D Alternate Function Set 2 Subregisters

The Port A–D Alternate Function Set 2 Subregister, shown in Table 28, is accessed through the Port A–D Control Register by writing 08H to the Port A–D Address Register. The Alternate Function Set 2 subregisters selects the alternate function available at a port pin. Alternate Functions selected by setting or clearing bits of this register is defined in Table 16 on page 43.

Note: Alternate function selection on the port pins must also be enabled. See the Port A–D Alternate Function Subregisters section on page 47 for details.

| Bit     | 7         | 6                                                                                     | 5      | 4      | 3      | 2      | 1      | 0      |  |  |

|---------|-----------|---------------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--|--|

| Field   | PAFS27    | PAFS26                                                                                | PAFS25 | PAFS24 | PAFS23 | PAFS22 | PAFS21 | PAFS20 |  |  |

| RESET   |           | 00H (all ports of 20/28 pin devices); 04H (Port A of 8-pin device)                    |        |        |        |        |        |        |  |  |

| R/W     | R/W       | R/W                                                                                   | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |  |  |

| Address | If 08H ir | If 08H in Port A–D Address Register, accessible through the Port A–D Control Register |        |        |        |        |        |        |  |  |

#### Bit Description

#### [7] **Port Alternate Function Set 2**

- PAFS2x 0 = Port Alternate Function selected, as defined in Table 16.

- 1 = Port Alternate Function selected, as defined in Table 16.

Note: x indicates the specific GPIO port pin number (7-0).

51

# **Timers**

These Z8 Encore! XP F082A Series products contain two 16-bit reloadable timers that can be used for timing, event counting, or generation of pulse-width modulated (PWM) signals. The timers' feature include:

- 16-bit reload counter

- Programmable prescaler with prescale values from 1 to 128

- PWM output generation

- Capture and compare capability

- External input pin for timer input, clock gating, or capture signal. External input pin signal frequency is limited to a maximum of one-fourth the system clock frequency

- Timer output pin

- Timer interrupt

In addition to the timers described in this chapter, the Baud Rate Generator of the UART (if unused) may also provide basic timing functionality. For information about using the Baud Rate Generator as an additional timer, see the <u>Universal Asynchronous Receiver/</u> <u>Transmitter</u> chapter on page 99.

### Architecture

Figure 9 displays the architecture of the timers.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. Clear the Timer PWM High and Low Byte registers to 0000H. This allows the software to determine if interrupts were generated by either a capture event or a reload. If the PWM High and Low Byte registers still contain 0000H after the interrupt, the interrupt was generated by a Reload.

- 5. Enable the timer interrupt, if appropriate and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input capture and reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the reload event by setting TICONFIG field of the TxCTL0 Register.

- 6. Configure the associated GPIO port pin for the Timer Input alternate function.

- 7. Write to the Timer Control Register to enable the timer and initiate counting.

In CAPTURE Mode, the elapsed time from timer start to Capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

#### **COMPARE Mode**

In COMPARE Mode, the timer counts up to the 16-bit maximum Compare value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the Compare value, the timer generates an interrupt and counting continues (the timer value is not reset to 0001H). Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) upon Compare.

If the Timer reaches FFFFH, the timer rolls over to 0000H and continue counting.

Observe the following steps for configuring a timer for COMPARE Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for COMPARE Mode

- Set the prescale value

| Bit               | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [6:5]<br>TICONFIG | <ul> <li>Timer Interrupt Configuration</li> <li>This field configures timer interrupt definition.</li> <li>0x = Timer Interrupt occurs on all defined Reload, Compare and Input Events.</li> <li>10 = Timer Interrupt only on defined Input Capture/Deassertion Events.</li> <li>11 = Timer Interrupt only on defined Reload/Compare Events.</li> </ul>                                                             |

| [4]               | <b>Reserved</b><br>This bit is reserved and must be programmed to 0.                                                                                                                                                                                                                                                                                                                                                |

| [3:1]<br>PWMD     | <b>PWM Delay Value</b><br>This field is a programmable delay to control the number of system clock cycles delay<br>before the Timer Output and the Timer Output Complement are forced to their active state.<br>000 = No delay.<br>001 = 2 cycles delay.<br>010 = 4 cycles delay.<br>011 = 8 cycles delay.<br>100 = 16 cycles delay.<br>101 = 32 cycles delay.<br>101 = 64 cycles delay.<br>111 = 128 cycles delay. |

| [0]<br>INPCAP     | <ul> <li>Input Capture Event</li> <li>This bit indicates if the most recent timer interrupt is caused by a Timer Input Capture Event.</li> <li>0 = Previous timer interrupt is not a result of Timer Input Capture Event.</li> <li>1 = Previous timer interrupt is a result of Timer Input Capture Event.</li> </ul>                                                                                                |

#### Timer 0–1 Control Register 1

The Timer 0–1 Control (TxCTL1) registers, shown in Table 51, enable and disable the timers, set the prescaler value and determine the timer operating mode.

| Bit     | 7          | 6    | 5   | 4    | 3   | 2     | 1   | 0   |  |

|---------|------------|------|-----|------|-----|-------|-----|-----|--|

| Field   | TEN        | TPOL |     | PRES |     | TMODE |     |     |  |

| RESET   | 0          | 0    | 0   | 0    | 0   | 0     | 0   | 0   |  |

| R/W     | R/W        | R/W  | R/W | R/W  | R/W | R/W   | R/W | R/W |  |

| Address | F07H, F0FH |      |     |      |     |       |     |     |  |

| Bit | Description |  |

|-----|-------------|--|

|     |             |  |

- Timer Enable [7] TEN

- 0 = Timer is disabled.

- 1 = Timer enabled to count.

| Bit     | 7          | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|------------|-----|-----|-----|-----|-----|-----|-----|--|

| Field   |            | TH  |     |     |     |     |     |     |  |

| RESET   | 0          | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |

| R/W     | R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address | F00H, F08H |     |     |     |     |     |     |     |  |

#### Table 52. Timer 0–1 High Byte Register (TxH)

#### Table 53. Timer 0–1 Low Byte Register (TxL)

| Bit     | 7   | 6          | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|-----|------------|-----|-----|-----|-----|-----|-----|--|

| Field   | TL  |            |     |     |     |     |     |     |  |

| RESET   | 0   | 0          | 0   | 0   | 0   | 0   | 0   | 1   |  |

| R/W     | R/W | R/W        | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address |     | F01H, F09H |     |     |     |     |     |     |  |

| Bit    | Description                                                                      |

|--------|----------------------------------------------------------------------------------|

| [7:0]  | Timer High and Low Bytes                                                         |

| TH, TL | These 2 bytes, {TH[7:0], TL[7:0]}, contain the current 16-bit timer count value. |

In MULTIPROCESSOR (9-bit) Mode, the Parity (9th) bit location becomes the multiprocessor control bit. The UART Control 1 and Status 1 registers provide MULTIPROCES-SOR (9-bit) Mode control and status information. If an automatic address matching scheme is enabled, the UART Address Compare Register holds the network address of the device.

#### **MULTIPROCESSOR (9-bit) Mode Receive Interrupts**

When MULTIPROCESSOR Mode is enabled, the UART only processes frames addressed to it. The determination of whether a frame of data is addressed to the UART can be made in hardware, software or some combination of the two, depending on the multiprocessor configuration bits. In general, the address compare feature reduces the load on the CPU, because it does not require access to the UART when it receives data directed to other devices on the multi-node network. The following three MULTIPROCESSOR Modes are available in hardware:

- Interrupt on all address bytes

- Interrupt on matched address bytes and correctly framed data bytes

- Interrupt only on correctly framed data bytes

These modes are selected with MPMD[1:0] in the UART Control 1 Register. For all multiprocessor modes, bit MPEN of the UART Control 1 Register must be set to 1.

The first scheme is enabled by writing 01b to MPMD[1:0]. In this mode, all incoming address bytes cause an interrupt, while data bytes never cause an interrupt. The interrupt service routine must manually check the address byte that caused triggered the interrupt. If it matches the UART address, the software clears MPMD[0]. Each new incoming byte interrupts the CPU. The software is responsible for determining the end of the frame. It checks for the end-of-frame by reading the MPRX bit of the UART Status 1 Register for each incoming byte. If MPRX=1, a new frame has begun. If the address of this new frame is different from the UART's address, MPMD[0] must be set to 1 causing the UART interrupts to go inactive until the next address byte. If the new frame's address matches the UART's, the data in the new frame is processed as well.

The second scheme requires the following: set MPMD[1:0] to 10B and write the UART's address into the UART Address Compare Register. This mode introduces additional hard-ware control, interrupting only on frames that match the UART's address. When an incoming address byte does not match the UART's address, it is ignored. All successive data bytes in this frame are also ignored. When a matching address byte occurs, an interrupt is issued and further interrupts now occur on each successive data byte. When the first data byte in the frame is read, the NEWFRM bit of the UART Status 1 Register is asserted. All successive data bytes have NEWFRM=0. When the next address byte occurs, the hardware compares it to the UART's address. If there is a match, the interrupts continues and the NEWFRM bit is set for the first byte of the new frame. If there is no match, the UART ignores all incoming bytes until the next address match.

112

| Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7                                                                                                                                                                                                                                                                                                                                                                                                          | 6                                            | 5                                                           | 4                         | 3     | 2      | 1      | 0    |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-------------------------------------------------------------|---------------------------|-------|--------|--------|------|--|--|

| Field                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | MPMD[1]                                                                                                                                                                                                                                                                                                                                                                                                    | MPEN                                         | MPMD[0]                                                     | MPBT                      | DEPOL | BRGCTL | RDAIRQ | IREN |  |  |

| RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0                                                                                                                                                                                                                                                                                                                                                                                                          | 0                                            | 0                                                           | 0                         | 0     | 0      | 0      | 0    |  |  |

| R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W                                                                                                                                                                                                                                                                                                                                                                                                        | R/W                                          | R/W                                                         | R/W                       | R/W   | R/W    | R/W    | R/W  |  |  |

| Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                            |                                              |                                                             | F4                        | 3H    |        |        |      |  |  |

| Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Descript                                                                                                                                                                                                                                                                                                                                                                                                   | Description                                  |                                                             |                           |       |        |        |      |  |  |

| <ul> <li>[7,5] MULTIPROCESSOR Mode</li> <li>MPMD[1,0] If MULTIPROCESSOR (9-bit) Mode is enabled:</li> <li>00 = The UART generates an interrupt request on all received bytes (data and address).</li> <li>01 = The UART generates an interrupt request only on received address bytes.</li> <li>10 = The UART generates an interrupt request when a received address byte matches the value stored in the Address Compare Register and on all successive data bytes until an address mismatch occurs.</li> <li>11 = The UART generates an interrupt request on all received data bytes for which the most recent address byte matched the value in the Address Compare Register.</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                            |                                              |                                                             |                           |       |        |        |      |  |  |

| [6]<br>MPEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | This bit is<br>0 = Disal                                                                                                                                                                                                                                                                                                                                                                                   | s used to er<br>ble MULTIP                   | <b>R (9-bit) Ena</b><br>hable MULTI<br>ROCESSOF<br>ROCESSOR | PROCESSC<br>R (9-bit) Moc | le.   | ode.   |        |      |  |  |

| [4]<br>MPBT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <ul> <li>Multiprocessor Bit Transmit This bit is applicable only when MULTIPROCESSOR (9-bit) Mode is enabled. The 9th bit is used by the receiving device to determine if the data byte contains address or data information. 0 = Send a 0 in the multiprocessor bit location of the data stream (data byte). 1 = Send a 1 in the multiprocessor bit location of the data stream (address byte).</li></ul> |                                              |                                                             |                           |       |        |        |      |  |  |

| [3]<br>DEPOL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0 = DE s                                                                                                                                                                                                                                                                                                                                                                                                   | nable Pola<br>ignal is Acti<br>ignal is Acti | ve High.                                                    |                           |       |        |        |      |  |  |

#### Table 64. UART Control 1 Register (U0CTL1)

The window remains open until the count again reaches 8 (that is, 24 baud clock periods since the previous pulse was detected), giving the Endec a sampling window of minus four baud rate clocks to plus eight baud rate clocks around the expected time of an incoming pulse. If an incoming pulse is detected inside this window this process is repeated. If the incoming data is a logical 1 (no pulse), the Endec returns to the initial state and waits for the next falling edge. As each falling edge is detected, the Endec clock counter is reset, resynchronizing the Endec to the incoming signal, allowing the Endec to tolerate jitter and baud rate errors in the incoming datastream. Resynchronizing the Endec does not alter the operation of the UART, which ultimately receives the data. The UART is only synchronized to the incoming data stream when a Start bit is received.

### Infrared Encoder/Decoder Control Register Definitions

All infrared endec configuration and status information is set by the UART Control registers as defined in the <u>Universal Asynchronous Receiver/Transmitter</u> section on page 99.

**Caution:** To prevent spurious signals during IrDA data transmission, set the IREN bit in the UART Control 1 Register to 1 to enable the Infrared Encoder/Decoder before enabling the GPIO Port alternate function for the corresponding pin.

### Trim Bit Address 0002H

#### Table 92. Trim Option Bits at 0002H (TIPO)

| Bit                                             | 7                             | 6        | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------------------------------------------------|-------------------------------|----------|---|---|---|---|---|---|--|--|

| Field                                           |                               | IPO_TRIM |   |   |   |   |   |   |  |  |

| RESET                                           |                               | U        |   |   |   |   |   |   |  |  |

| R/W                                             |                               | R/W      |   |   |   |   |   |   |  |  |

| Address                                         | Information Page Memory 0022H |          |   |   |   |   |   |   |  |  |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                               |          |   |   |   |   |   |   |  |  |

|                                                 |                               |          |   |   |   |   |   |   |  |  |

| Bit      | Description                                                   |

|----------|---------------------------------------------------------------|

| [7:0]    | Internal Precision Oscillator Trim Byte                       |

| IPO_TRIM | Contains trimming bits for the Internal Precision Oscillator. |

### Trim Bit Address 0003H

**Note:** The LVD is available on 8-pin devices only.

#### Table 93. Trim Option Bits at Address 0003H (TLVD)

| Bit                                             | 7                             | 6        | 5   | 4        | 3   | 2   | 1   | 0   |

|-------------------------------------------------|-------------------------------|----------|-----|----------|-----|-----|-----|-----|

| Field                                           |                               | Reserved |     | LVD_TRIM |     |     |     |     |

| RESET                                           | U                             | U        | U   | U        | U   | U   | U   | U   |

| R/W                                             | R/W                           | R/W      | R/W | R/W      | R/W | R/W | R/W | R/W |

| Address                                         | Information Page Memory 0023H |          |     |          |     |     |     |     |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                               |          |     |          |     |     |     |     |

Note: U = Unchanged by Reset. R/W = Read/Write.

| Bit               | Description                                                                                                                                                                                                                                                            |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:5]             | Reserved<br>These bits are reserved and must be programmed to 111.                                                                                                                                                                                                     |

| [4:0]<br>LVD_TRIM | <b>Low Voltage Detect Trimm</b><br>This trimming affects the low voltage detection threshold. Each LSB represents a 50mV change in the threshold level. Alternatively, the low voltage threshold may be computed from the options bit value by the following equation: |

|                   | $LVD_LVL = 3.6 V - LVD_TRIM \times 0.05 V$                                                                                                                                                                                                                             |

|                   | These values are tabulated in Table 94.                                                                                                                                                                                                                                |

### Operation

This section describes the interface and modes of operation of the On-Chip Debugger.

### **OCD** Interface

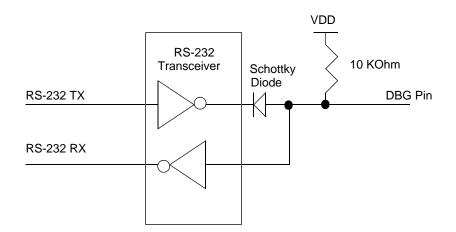

The on-chip debugger uses the DBG pin for communication with an external host. This one-pin interface is a bidirectional, open-drain interface that transmits and receives data. Data transmission is half-duplex, in that transmit and receive cannot occur simultaneously. The serial data on the DBG pin is sent using the standard asynchronous data format defined in RS-232. This pin creates an interface from the Z8 Encore! XP F082A Series products to the serial port of a host PC using minimal external hardware. Two different methods for connecting the DBG pin to an RS-232 interface are displayed in Figure 24 and Figure 25. The recommended method is the buffered implementation displayed in Figure 25. The DBG pin has a internal pull-up resistor which is sufficient for some applications (for more details about the pull-up current, see the <u>Electrical Characteristics</u> chapter on page 226). For OCD operation at higher data rates or in noisy systems, an external pull-up resistor is recommended.

**Caution:** For operation of the on-chip debugger, all power pins (V<sub>DD</sub> and AV<sub>DD</sub>) must be supplied with power and all ground pins (V<sub>SS</sub> and AV<sub>SS</sub>) must be properly grounded. The DBG pin is open-drain and may require an external pull-up resistor to ensure proper operation.

Figure 24. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface; #1 of 2

Unlock and write Oscillator Control

Register (OSCCTL) to enable and

select oscillator at either 5.53MHz or

• Configure Flash option bits for correct

Unlock and write OSCCTL to enable

crystal oscillator, wait for it to stabilize and select as system clock (if the XTLDIS option bit has been deasserted, no waiting is required)

Configure Flash option bits for correct

Unlock and write OSCCTL to enable crystal oscillator and select as system

• Write GPIO registers to configure PB3

Unlock and write OSCCTL to select

Apply external clock signal to GPIO

· Enable WDT if not enabled and wait

until WDT Oscillator is operating Unlock and write Oscillator Control

pin for external clock function

external system clock

external oscillator mode

external oscillator mode

| Very low power consumption                                                                                                                        | Register (OSCCTL) to enable and select oscillator |

|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

|                                                                                                                                                   |                                                   |

| <b>Caution:</b> Unintentional accesses to the Oscillator C switching to a nonfunctioning oscillator. T block employs a register unlocking/locking | To prevent this condition, the oscillator con     |

| OSC Control Register Unlocking/L                                                                                                                  | _ocking                                           |

| To write the Oscillator Control Register, unl<br>Register with the values E7H followed by 11<br>changes the value of the actual register and r    | 8H. A third write to the OSCCTL Register          |

**Required Setup**

32.8kHz

clock

> s to the OSCCTL CTL Register ed state. Any other sequence of Oscillator Control Register writes has no effect. The values written to unlock the register must be ordered correctly, but are not necessarily consecutive. It is possible to write to or read from other registers within the unlocking/locking operation.

**Clock Source**

**RC** Oscillator

Internal Precision

External Crystal/

External Clock

Internal Watchdog

Timer Oscillator

Resonator

tor

Drive

Characteristics

High accuracy

• 32kHz to 20MHz

ponents

0 to 20MHz

• 10kHz nominal

nents required

source

•

External RC Oscilla- • 32kHz to 4MHz

• 32.8kHz or 5.53MHz

No external components required

Very high accuracy (dependent on

· Accuracy dependent on external com-

Accuracy dependent on external clock

Low accuracy; no external compo-

crystal or resonator used)

Requires external components

| 24 | 0 |

|----|---|

| 21 | Ö |

| Assembly     |                                                                          |     | lress<br>ode | _ Opcode(s) |   |   | Fla | ags |   |   | Fetch<br>Cycle | Instr.<br>Cycle |

|--------------|--------------------------------------------------------------------------|-----|--------------|-------------|---|---|-----|-----|---|---|----------------|-----------------|

| Mnemonic     | Symbolic Operation                                                       | dst | src          | (Hex)       |   | Ζ | S   | V   | D | Н | s              | S               |

| ORX dst, src | $dst \gets dst \ OR \ src$                                               | ER  | ER           | 48          | - | * | *   | 0   | - | - | 4              | 3               |

|              |                                                                          | ER  | IM           | 49          | - |   |     |     |   |   | 4              | 3               |

| POP dst      | dst ← @SP                                                                | R   |              | 50          | - | _ | -   | -   | - | - | 2              | 2               |

|              | $SP \leftarrow SP + 1$                                                   | IR  |              | 51          | - |   |     |     |   |   | 2              | 3               |

| POPX dst     | dst $\leftarrow @SP$<br>SP $\leftarrow$ SP + 1                           | ER  |              | D8          | - | _ | -   | -   | _ | - | 3              | 2               |

| PUSH src     | $SP \leftarrow SP - 1$                                                   | R   |              | 70          | - | - | _   | -   | - | - | 2              | 2               |

|              | $@SP \leftarrow src$                                                     | IR  |              | 71          | - |   |     |     |   |   | 2              | 3               |

|              |                                                                          | IM  |              | IF70        |   |   |     |     |   |   | 3              | 2               |

| PUSHX src    | $SP \leftarrow SP - 1$<br>@ $SP \leftarrow src$                          | ER  |              | C8          | _ | - | _   | -   | _ | _ | 3              | 2               |

| RCF          | C ← 0                                                                    |     |              | CF          | 0 | _ | _   | _   | _ | - | 1              | 2               |

| RET          | $\begin{array}{l} PC \leftarrow @SP \\ SP \leftarrow SP + 2 \end{array}$ |     |              | AF          | _ | - | _   | _   | _ | _ | 1              | 4               |

| RL dst       |                                                                          | R   |              | 90          | * | * | *   | *   | _ | - | 2              | 2               |

|              | C                                                                        | IR  |              | 91          | _ |   |     |     |   |   | 2              | 3               |

| RLC dst      |                                                                          | R   |              | 10          | * | * | *   | *   | _ | _ | 2              | 2               |

|              | C                                                                        | IR  |              | 11          | - |   |     |     |   |   | 2              | 3               |

| RR dst       |                                                                          | R   |              | E0          | * | * | *   | *   | _ | _ | 2              | 2               |

|              | ► D7 D6 D5 D4 D3 D2 D1 D0 C<br>dst                                       | IR  |              | E1          |   |   |     |     |   |   | 2              | 3               |

#### Table 128. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

|                     |                          | V <sub>DD</sub> = 2.7 V to 3.6 V<br>T <sub>A</sub> = -40°C to +105°C<br>(unless otherwise stated) |         |             |       |                                                                                                    |  |

|---------------------|--------------------------|---------------------------------------------------------------------------------------------------|---------|-------------|-------|----------------------------------------------------------------------------------------------------|--|

| Symbol              | Parameter                | Minimum                                                                                           | Typical | Maximum     | Units | Conditions                                                                                         |  |

| F <sub>WDT</sub>    | WDT Oscillator Frequency |                                                                                                   | 10      |             | kHz   |                                                                                                    |  |

| F <sub>WDT</sub>    | WDT Oscillator Error     |                                                                                                   |         | <u>+</u> 50 | %     |                                                                                                    |  |

| T <sub>WDTCAL</sub> | WDT Calibrated Time-out  | 0.98                                                                                              | 1       | 1.02        | S     | V <sub>DD</sub> = 3.3V;<br>T <sub>A</sub> = 30°C                                                   |  |

|                     |                          | 0.70                                                                                              | 1       | 1.30        | S     | $V_{DD} = 2.7 V \text{ to } 3.6 V$<br>$T_A = 0^{\circ}\text{C} \text{ to } 70^{\circ}\text{C}$     |  |

|                     |                          | 0.50                                                                                              | 1       | 1.50        | S     | $V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$<br>$T_A = -40^{\circ}\text{C to } +105^{\circ}\text{C}$ |  |

#### Table 137. Watchdog Timer Electrical Characteristics and Timing

#### Table 138. Non-Volatile Data Storage

|                        |         | = 2.7 V to<br>-40°C to + |         |        |                                           |

|------------------------|---------|--------------------------|---------|--------|-------------------------------------------|

| Parameter              | Minimum | Typical                  | Maximum | Units  | Notes                                     |

| NVDS Byte Read Time    | 34      | _                        | 519     | μs     | With system clock at 20MHz                |

| NVDS Byte Program Time | 0.171   | _                        | 39.7    | ms     | With system clock at 20MHz                |

| Data Retention         | 100     | _                        | -       | years  | 25°C                                      |

| Endurance              | 160,000 | _                        | _       | cycles | Cumulative write cycles for entire memory |

### Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

260

LEA 210 load 210 load constant 209 load constant to/from program memory 210 load constant with auto-increment addresses 210 load effective address 210 load external data 210 load external data to/from data memory and autoincrement addresses 209 load external to/from data memory and auto-increment addresses 210 load using extended addressing 210 logical AND 210 logical AND/extended addressing 210 logical exclusive OR 210 logical exclusive OR/extended addressing 210 logical instructions 210 logical OR 210 logical OR/extended addressing 210 low power modes 32

### Μ

master interrupt enable 57 memory data 17 program 15 mode **CAPTURE 87, 88 CAPTURE/COMPARE 88** CONTINUOUS 87 COUNTER 87 GATED 88 **ONE-SHOT 87** PWM 87, 88 modes 87 **MULT 208** multiply 208 multiprocessor mode, UART 105

### Ν

NOP (no operation) 209 notation

## 0

b 206

cc 206

DA 206

ER 206

IM 206

IR 206

Ir 206

**IRR 206**

Irr 206

p 206

R 206

r 206

RA 206

**RR 206**

vector 207

notational shorthand 206

rr 206

X 207

OCD architecture 180 auto-baud detector/generator 183 baud rate limits 184 block diagram 180 breakpoints 185 commands 186 control register 191 data format 183 DBG pin to RS-232 Interface 181 debug mode 182 debugger break 211 interface 181 serial errors 184 status register 192 timing 242 OCD commands execute instruction (12H) 190 read data memory (0DH) 190 read OCD control register (05H) 188 read OCD revision (00H) 187 read OCD status register (02H) 187 read program counter (07H) 188

Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

UARTx control 1 (UxCTL1) 112 UARTx receive data (UxRXD) 116 UARTx status 0 (UxSTAT0) 114 UARTx status 1 (UxSTAT1) 115 UARTx transmit data (UxTXD) 116 Watchdog Timer control (WDTCTL) 30, 96, 141, 196 Watchdog Timer reload high byte (WDTH) 97 Watchdog Timer reload low byte (WDTL) 98 Watchdog Timer reload upper byte (WDTU) 97 register file 15 register pair 206 register pointer 207 reset and stop mode characteristics 23 and Stop Mode Recovery 22 carry flag 209 sources 24 **RET 211** return 211 RL 211 **RLC 211** rotate and shift instuctions 211 rotate left 211 rotate left through carry 211 rotate right 211 rotate right through carry 211 **RP 207** RR 206, 211

rr 206 RRC 211

### S

SBC 208 SCF 209, 210 second opcode map after 1FH 225 set carry flag 209, 210 set register pointer 210 shift right arithmatic 211 shift right logical 211 signal descriptions 10 single-shot conversion (ADC) 126 software trap 211 source operand 207 SP 207 SRA 211 src 207 SRL 211 **SRP 210** stack pointer 207 **STOP 210** STOP mode 32 stop mode 210 Stop Mode Recovery sources 27 using a GPIO port pin transition 28 using Watchdog Timer time-out 28 stop mode recovery sources 29 using a GPIO port pin transition 29 **SUB 208** subtract 208 subtract - extended addressing 208 subtract with carry 208 subtract with carry - extended addressing 208 **SUBX 208 SWAP 211** swap nibbles 211 symbols, additional 207

## Т

PRELIMINARY

TCM 209 TCMX 209 test complement under mask 209 test complement under mask - extended addressing 209 test under mask 209 test under mask - extended addressing 209 timer signals 10 timers 70 architecture 70 block diagram 71 CAPTURE mode 79, 80, 87, 88 CAPTURE/COMPARE mode 83, 88 COMPARE mode 81, 87