Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 23                                                           |

| Program Memory Size        | 1KB (1K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 16 x 8                                                       |

| RAM Size                   | 256 x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 8x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | 0°C ~ 70°C (TA)                                              |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 28-SSOP (0.173", 4.40mm Width)                               |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f012ahj020sg    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

and as long as four. A reset pulse three clock cycles in duration might trigger a reset; a pulse four cycles in duration always triggers a reset.

While the RESET input pin is asserted Low, the Z8 Encore! XP F082A Series devices remain in the Reset state. If the RESET pin is held Low beyond the System Reset timeout, the device exits the Reset state on the system clock rising edge following RESET pin deassertion. Following a System Reset initiated by the external RESET pin, the EXT status bit in the Reset Status (RSTSTAT) Register is set to 1.

## **External Reset Indicator**

During System Reset or when enabled by the GPIO logic (see <u>Table 20 on page 46</u>), the <u>RESET</u> pin functions as an open-drain (active Low) reset mode indicator in addition to the input functionality. This reset output feature allows a Z8 Encore! XP F082A Series device to reset other components to which it is connected, even if that reset is caused by internal sources such as POR, VBO or WDT events.

After an internal reset event occurs, the internal circuitry begins driving the RESET pin Low. The RESET pin is held Low by the internal circuitry until the appropriate delay listed in Table 8 has elapsed.

## **On-Chip Debugger Initiated Reset**

A Power-On Reset can be initiated using the On-Chip Debugger by setting the RST bit in the OCD Control Register. The On-Chip Debugger block is not reset but the rest of the chip goes through a normal system reset. The RST bit automatically clears during the system reset. Following the system reset the POR bit in the Reset Status (RSTSTAT) Register is set.

# Stop Mode Recovery

STOP Mode is entered by execution of a STOP instruction by the eZ8 CPU. See the <u>Low-Power Modes</u> chapter on page 32 for detailed STOP Mode information. During Stop Mode Recovery (SMR), the CPU is held in reset for 66 IPO cycles if the crystal oscillator is disabled or 5000 cycles if it is enabled. The SMR delay (see <u>Table 135</u> on page 233)  $T_{SMR}$ , also includes the time required to start up the IPO.

Stop Mode Recovery does not affect on-chip registers other than the Watchdog Timer Control Register (WDTCTL) and the Oscillator Control Register (OSCCTL). After any Stop Mode Recovery, the IPO is enabled and selected as the system clock. If another system clock source is required, the Stop Mode Recovery code must reconfigure the oscillator control block such that the correct system clock source is enabled and selected.

The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset vec-

| Bit     | 7           | 6                                                                                     | 5    | 4    | 3    | 2    | 1    | 0    |  |  |

|---------|-------------|---------------------------------------------------------------------------------------|------|------|------|------|------|------|--|--|

| Field   | POC7        | POC6                                                                                  | POC5 | POC4 | POC3 | POC2 | POC1 | POC0 |  |  |

| RESET   |             | 00H (Ports A-C); 01H (Port D)                                                         |      |      |      |      |      |      |  |  |

| R/W     | R/W         | R/W                                                                                   | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |  |  |

| Address | If 03H ii   | If 03H in Port A–D Address Register, accessible through the Port A–D Control Register |      |      |      |      |      |      |  |  |

| D:4     | Decertation |                                                                                       |      |      |      |      |      |      |  |  |

#### Table 23. Port A–D Output Control Subregisters (PxOC)

| Bit   | Description                                                                                                                |

|-------|----------------------------------------------------------------------------------------------------------------------------|

| [7:0] | Port Output Control                                                                                                        |

| POCx  | These bits function independently of the alternate function bit and always disable the drains if set to 1.                 |

|       | 0 = The source current is enabled for any output mode unless overridden by the alternate func-<br>tion (push-pull output). |

|       | 1 = The source current for the associated pin is disabled (open-drain mode).                                               |

### Port A–D High Drive Enable Subregisters

The Port A–D High Drive Enable Subregister, shown in Table 24, is accessed through the port A–D Control Register by writing 04H to the Port A–D Address Register. Setting the bits in the Port A–D High Drive Enable subregisters to 1 configures the specified port pins for high current output drive operation. The Port A–D High Drive Enable subregister affects the pins directly and, as a result, alternate functions are also affected.

| Bit     | 7         | 6            | 5           | 4             | 3            | 2            | 1            | 0        |

|---------|-----------|--------------|-------------|---------------|--------------|--------------|--------------|----------|

| Field   | PHDE7     | PHDE6        | PHDE5       | PHDE4         | PHDE3        | PHDE2        | PHDE1        | PHDE0    |

| RESET   | 0         | 0            | 0           | 0             | 0            | 0            | 0            | 0        |

| R/W     | R/W       | R/W          | R/W         | R/W           | R/W          | R/W          | R/W          | R/W      |

| Address | lf 04H ir | n Port A–D A | Address Reg | jister, acces | sible throug | h the Port A | –D Control F | Register |

Table 24. Port A–D High Drive Enable Subregisters (PxHDE)

| Bit        | Description                                                       |  |  |  |  |  |

|------------|-------------------------------------------------------------------|--|--|--|--|--|

| [7:0]      | Port High Drive Enabled                                           |  |  |  |  |  |

| PHDEx      | 0 = The port pin is configured for standard output current drive. |  |  |  |  |  |

|            | 1 = The port pin is configured for high output current drive.     |  |  |  |  |  |

| Note: x in | Note: x indicates the specific GPIO port pin number (7–0).        |  |  |  |  |  |

# Port A–C Input Data Registers

Reading from the Port A–C Input Data registers, shown in Table 29, return the sampled values from the corresponding port pins. The Port A–C Input Data registers are read-only. The value returned for any unused ports is 0. Unused ports include those missing on the 8-and 28-pin packages, as well as those missing on the ADC-enabled 28-pin packages.

| Bit       | 7              | 6                | 5    | 4    | 3    | 2    | 1    | 0    |  |

|-----------|----------------|------------------|------|------|------|------|------|------|--|

| Field     | PIN7           | PIN6             | PIN5 | PIN4 | PIN3 | PIN2 | PIN1 | PIN0 |  |

| RESET     | Х              | Х                | Х    | Х    | Х    | Х    | Х    | Х    |  |

| R/W       | R              | R                | R    | R    | R    | R    | R    | R    |  |

| Address   |                | FD2H, FD6H, FDAH |      |      |      |      |      |      |  |

| X = Undef | X = Undefined. |                  |      |      |      |      |      |      |  |

Table 29. Port A–C Input Data Registers (PxIN)

| Bit   | Description                                         |

|-------|-----------------------------------------------------|

| [7:0] | Port Input Data                                     |

| PxIN  | Sampled data from the corresponding port pin input. |

|       | 0 = Input data is logical 0 (Low).                  |

|       | 1 = Input data is logical 1 (High).                 |

Note: x indicates the specific GPIO port pin number (7–0).

# Port A–D Output Data Register

The Port A–D Output Data Register, shown in Table 30, controls the output data to the pins.

| Bit     | 7     | 6                      | 5     | 4     | 3     | 2     | 1     | 0     |  |  |

|---------|-------|------------------------|-------|-------|-------|-------|-------|-------|--|--|

| Field   | POUT7 | POUT6                  | POUT5 | POUT4 | POUT3 | POUT2 | POUT1 | POUT0 |  |  |

| RESET   | 0     | 0                      | 0     | 0     | 0     | 0     | 0     | 0     |  |  |

| R/W     | R/W   | R/W                    | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |  |  |

| Address |       | FD3H, FD7H, FDBH, FDFH |       |       |       |       |       |       |  |  |

Table 30. Port A–D Output Data Register (PxOUT)

#### Bit Description

[7:0] **Port Output Data** PxOUT These bits contain the data to be driven to the port pins. The values are only driven if the corresponding pin is configured as an output and the pin is not configured for alternate function operation. 0 = Drive a logical 0 (Low).

1 = Drive a logical 1 (High). High value is not driven if the drain has been disabled by setting the corresponding Port Output Control Register bit to 1.

Note: x indicates the specific GPIO port pin number (7–0).

it is appropriate to have the Timer Output make a state change at a One-Shot time-out (rather than a single cycle pulse), first set the TPOL bit in the Timer Control Register to the start value before enabling ONE-SHOT Mode. After starting the timer, set TPOL to the opposite bit value.

Observe the following steps for configuring a timer for ONE-SHOT Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for ONE-SHOT Mode.

- Set the prescale value.

- Set the initial output level (High or Low) if using the Timer Output alternate function.

- 2. Write to the Timer High and Low Byte registers to set the starting count value.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 6. Write to the Timer Control Register to enable the timer and initiate counting.

In ONE-SHOT Mode, the system clock always provides the timer input. The timer period is computed via the following equation:

$ONE-SHOT \text{ Mode Time-Out Period } (s) = \frac{\text{Reload Value} - \text{Start Value} \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$

#### **CONTINUOUS Mode**

In CONTINUOUS Mode, the timer counts up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer Reload.

Observe the following steps for configuring a timer for CONTINUOUS Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CONTINUOUS Mode

The timer input can be used as a selectable counting source. It shares the same pin as the complementary timer output. When selected by the GPIO Alternate Function registers, this pin functions as a timer input in all modes except for the DUAL PWM OUTPUT mode. For this mode, there is no timer input available.

# **Timer Control Register Definitions**

This section defines the features of the following Timer Control registers.

<u>Timer 0–1 Control Registers</u>: see page 85

<u>Timer 0–1 High and Low Byte Registers</u>: see page 89

Timer Reload High and Low Byte Registers: see page 91

Timer 0-1 PWM High and Low Byte Registers: see page 92

## Timer 0–1 Control Registers

The Timer Control registers are 8-bit read/write registers that control the operation of their associated counter/timers.

## Time 0–1 Control Register 0

The Timer Control Register 0 (TxCTL0) and Timer Control Register 1 (TxCTL1), shown in Table 50, determine the timer operating mode. These registers each include a programmable PWM deadband delay, two bits to configure timer interrupt definition and a status bit to identify if the most recent timer interrupt is caused by an input capture event.

| Bit            | 7                   | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5                            | 4                                              | 3              | 2           | 1            | 0          |  |

|----------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------------------------|----------------|-------------|--------------|------------|--|

| Field          | TMODEHI             | TICO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | NFIG                         | Reserved                                       |                | PWMD        |              | INPCAP     |  |

| RESET          | 0                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                            | 0                                              | 0              | 0           | 0            | 0          |  |

| R/W            | R/W                 | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R/W                          | R/W                                            | R/W            | R/W         | R/W          | R          |  |

| Address        |                     | F06H, F0EH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                              |                                                |                |             |              |            |  |

| Bit            | Descript            | tion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                              |                                                |                |             |              |            |  |

| [7]<br>TMODEHI | This bit, a mode of | the timer. The timer the timer the time | ne TMODE f<br>nis bit is the | field in the T<br>most signific<br>Control Reg | cant bit of th | e Timer moo | de selection | value. See |  |

Table 50. Timer 0–1 Control Register 0 (TxCTL0)

| Bit               | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [6:5]<br>TICONFIG | <ul> <li>Timer Interrupt Configuration</li> <li>This field configures timer interrupt definition.</li> <li>0x = Timer Interrupt occurs on all defined Reload, Compare and Input Events.</li> <li>10 = Timer Interrupt only on defined Input Capture/Deassertion Events.</li> <li>11 = Timer Interrupt only on defined Reload/Compare Events.</li> </ul>                                                             |

| [4]               | <b>Reserved</b><br>This bit is reserved and must be programmed to 0.                                                                                                                                                                                                                                                                                                                                                |

| [3:1]<br>PWMD     | <b>PWM Delay Value</b><br>This field is a programmable delay to control the number of system clock cycles delay<br>before the Timer Output and the Timer Output Complement are forced to their active state.<br>000 = No delay.<br>001 = 2 cycles delay.<br>010 = 4 cycles delay.<br>011 = 8 cycles delay.<br>100 = 16 cycles delay.<br>101 = 32 cycles delay.<br>101 = 64 cycles delay.<br>111 = 128 cycles delay. |

| [0]<br>INPCAP     | <ul> <li>Input Capture Event</li> <li>This bit indicates if the most recent timer interrupt is caused by a Timer Input Capture Event.</li> <li>0 = Previous timer interrupt is not a result of Timer Input Capture Event.</li> <li>1 = Previous timer interrupt is a result of Timer Input Capture Event.</li> </ul>                                                                                                |

## Timer 0–1 Control Register 1

The Timer 0–1 Control (TxCTL1) registers, shown in Table 51, enable and disable the timers, set the prescaler value and determine the timer operating mode.

| Bit     | 7   | 6          | 5   | 4    | 3   | 2     | 1   | 0   |  |  |

|---------|-----|------------|-----|------|-----|-------|-----|-----|--|--|

| Field   | TEN | TPOL       |     | PRES |     | TMODE |     |     |  |  |

| RESET   | 0   | 0          | 0   | 0    | 0   | 0     | 0   | 0   |  |  |

| R/W     | R/W | R/W        | R/W | R/W  | R/W | R/W   | R/W | R/W |  |  |

| Address |     | F07H, F0FH |     |      |     |       |     |     |  |  |

| Bit | Description |  |

|-----|-------------|--|

|     |             |  |

- Timer Enable [7] TEN

- 0 = Timer is disabled.

- 1 = Timer enabled to count.

| Bit     | 7          | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|------------|-----|-----|-----|-----|-----|-----|-----|

| Field   |            | TH  |     |     |     |     |     |     |

| RESET   | 0          | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | F00H, F08H |     |     |     |     |     |     |     |

### Table 52. Timer 0–1 High Byte Register (TxH)

### Table 53. Timer 0–1 Low Byte Register (TxL)

| Bit     | 7   | 6          | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----|------------|-----|-----|-----|-----|-----|-----|

| Field   |     | TL         |     |     |     |     |     |     |

| RESET   | 0   | 0          | 0   | 0   | 0   | 0   | 0   | 1   |

| R/W     | R/W | R/W        | R/W | R/W | R/W | R/W | R/W | R/W |

| Address |     | F01H, F09H |     |     |     |     |     |     |

| Bit    | Description                                                                      |

|--------|----------------------------------------------------------------------------------|

| [7:0]  | Timer High and Low Bytes                                                         |

| TH, TL | These 2 bytes, {TH[7:0], TL[7:0]}, contain the current 16-bit timer count value. |

into the Watchdog Timer Reload registers results in a one-second time-out at room temperature and 3.3V supply voltage. Time-outs other than one second may be obtained by scaling the calibration values up or down as required.

**Note:** The Watchdog Timer accuracy still degrades as temperature and supply voltage vary. See <u>Table 137</u> on page 235 for details.

# Watchdog Timer Control Register Definitions

This section defines the features of the following Watchdog Timer Control registers.

Watchdog Timer Control Register (WDTCTL): see page 96

Watchdog Timer Reload Upper Byte Register (WDTU): see page 97

Watchdog Timer Reload High Byte Register (WDTH): see page 97

Watchdog Timer Reload Low Byte Register (WDTL): see page 98

## Watchdog Timer Control Register

The Watchdog Timer Control (WDTCTL) Register is a write-only control register. Writing the 55H, AAH unlock sequence to the WDTCTL Register address unlocks the three Watchdog Timer Reload Byte registers (WDTU, WDTH and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL Register address produce no effect on the bits in the WDTCTL Register. The locking mechanism prevents spurious writes to the reload registers. This register address is shared with the read-only Reset Status Register.

| Bit       | 7          | 6       | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-----------|------------|---------|---|---|---|---|---|---|--|

| Field     |            | WDTUNLK |   |   |   |   |   |   |  |

| RESET     | Х          | Х       | Х | Х | Х | Х | Х | Х |  |

| R/W       | W          | W       | W | W | W | W | W | W |  |

| Address   |            | FF0H    |   |   |   |   |   |   |  |

| Note: X = | Undefined. |         |   |   |   |   |   |   |  |

| DIL     | Description                                                                                  |

|---------|----------------------------------------------------------------------------------------------|

| [7:0]   | Watchdog Timer Unlock                                                                        |

| WDTUNLK | The software must write the correct unlocking sequence to this register before it is allowed |

|         | to modify the contents of the Watchdog Timer reload registers.                               |

Description

Dit

- Set or clear the CTSE bit to enable or disable control from the remote receiver using the  $\overline{\text{CTS}}$  pin

- 6. Check the TDRE bit in the UART Status 0 Register to determine if the Transmit Data Register is empty (indicated by a 1). If empty, continue to <u>Step 7</u>. If the Transmit Data Register is full (indicated by a 0), continue to monitor the TDRE bit until the Transmit Data Register becomes available to receive new data.

- 7. Write the UART Control 1 Register to select the outgoing address bit.

- 8. Set the Multiprocessor Bit Transmitter (MPBT) if sending an address byte, clear it if sending a data byte.

- 9. Write the data byte to the UART Transmit Data Register. The transmitter automatically transfers the data to the Transmit Shift Register and transmits the data.

- 10. Make any changes to the Multiprocessor Bit Transmitter (MPBT) value, if appropriate and MULTIPROCESSOR Mode is enabled.

- 11. To transmit additional bytes, return to <u>Step 5</u>.

## Transmitting Data using the Interrupt-Driven Method

The UART Transmitter interrupt indicates the availability of the Transmit Data Register to accept new data for transmission. Observe the following steps to configure the UART for interrupt-driven data transmission:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the appropriate baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Execute a DI instruction to disable interrupts.

- 4. Write to the Interrupt control registers to enable the UART Transmitter interrupt and set the acceptable priority.

- 5. Write to the UART Control 1 Register to enable MULTIPROCESSOR (9-bit) Mode functions, if MULTIPROCESSOR Mode is appropriate.

- 6. Set the MULTIPROCESSOR Mode Select (MPEN) to Enable MULTIPROCESSOR Mode.

- 7. Write to the UART Control 0 Register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission

- Enable parity, if appropriate and if MULTIPROCESSOR Mode is not enabled and select either even or odd parity

| Bit          | 7                                                       | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5       | 4    | 3     | 2      | 1      | 0    |  |

|--------------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|--------|--------|------|--|

| Field        | MPMD[1]                                                 | MPEN                                                                                                                                                                                                                                                                                                                                                                                                                                                          | MPMD[0] | MPBT | DEPOL | BRGCTL | RDAIRQ | IREN |  |

| RESET        | 0                                                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0       | 0    | 0     | 0      | 0      | 0    |  |

| R/W          | R/W                                                     | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W     | R/W  | R/W   | R/W    | R/W    | R/W  |  |

| Address      |                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         | F4   | 3H    |        |        |      |  |

| Bit          | Descript                                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |      |       |        |        |      |  |

| [6]<br>MPEN  |                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |      |       |        |        |      |  |

| [4]<br>MPBT  | Multipro<br>This bit is<br>used by<br>tion.<br>0 = Send | <ul> <li>1 = Enable MULTIPROCESSOR (9-bit) Mode.</li> <li>Multiprocessor Bit Transmit This bit is applicable only when MULTIPROCESSOR (9-bit) Mode is enabled. The 9th bit is used by the receiving device to determine if the data byte contains address or data informa- tion. 0 = Send a 0 in the multiprocessor bit location of the data stream (data byte). 1 = Send a 1 in the multiprocessor bit location of the data stream (address byte).</li></ul> |         |      |       |        |        |      |  |

| [3]<br>DEPOL | <b>Driver E</b><br>0 = DE s                             | Driver Enable Polarity         0 = DE signal is Active High.         1 = DE signal is Active Low.                                                                                                                                                                                                                                                                                                                                                             |         |      |       |        |        |      |  |

### Table 64. UART Control 1 Register (U0CTL1)

## 173

#### Table 101. Watchdog Calibration Low Byte at 007FH (WDTCALL)

| Bit                                             | 7                             | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------------------------------------------------|-------------------------------|-----|-----|-----|-----|-----|-----|-----|

| Field                                           | WDTCALL                       |     |     |     |     |     |     |     |

| RESET                                           | U                             | U   | U   | U   | U   | U   | U   | U   |

| R/W                                             | R/W                           | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address                                         | Information Page Memory 007FH |     |     |     |     |     |     |     |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                               |     |     |     |     |     |     |     |

| Bit     | Description                                                                              |

|---------|------------------------------------------------------------------------------------------|

| [7:0]   | Watchdog Timer Calibration Low Byte                                                      |

| WDTCALL | The WDTCALH and WDTCALL bytes, when loaded into the Watchdog Timer reload regis-         |

|         | ters result in a one second time-out at room temperature and 3.3V supply voltage. To use |

|         | the Watchdog Timer calibration, user code must load WDTU with 0x00, WDTH with WDT-       |

|         | CALH and WDTL with WDTCALL.                                                              |

# **Serialization Data**

#### Table 102. Serial Number at 001C - 001F (S\_NUM)

| Bit                                             | 7   | 6                                 | 5   | 4   | 3   | 2   | 1   | 0   |

|-------------------------------------------------|-----|-----------------------------------|-----|-----|-----|-----|-----|-----|

| Field                                           |     | S_NUM                             |     |     |     |     |     |     |

| RESET                                           | U   | U                                 | U   | U   | U   | U   | U   | U   |

| R/W                                             | R/W | R/W                               | R/W | R/W | R/W | R/W | R/W | R/W |

| Address                                         |     | Information Page Memory 001C-001F |     |     |     |     |     |     |

| Note: U = Unchanged by Reset. R/W = Read/Write. |     |                                   |     |     |     |     |     |     |

| Bit   | Description                                                          |

|-------|----------------------------------------------------------------------|

| [7:0] | Serial Number Byte                                                   |

| S_NUM | The serial number is a unique four-byte binary value. See Table 103. |

#### Table 103. Serialization Data Locations

| Info Page<br>Address | Memory<br>Address | Usage                                     |

|----------------------|-------------------|-------------------------------------------|

| 1C                   | FE1C              | Serial Number Byte 3 (most significant).  |

| 1D                   | FE1D              | Serial Number Byte 2.                     |

| 1E                   | FE1E              | Serial Number Byte 1.                     |

| 1F                   | FE1F              | Serial Number Byte 0 (least significant). |

## **Byte Read**

To read a byte from the NVDS array, user code must first push the address onto the stack. User code issues a CALL instruction to the address of the byte-read routine  $(0 \times 1000)$ . At the return from the sub-routine, the read byte resides in working register R0 and the read status byte resides in working register R1. The contents of the status byte are undefined for read operations to illegal addresses. Also, the user code must pop the address byte off the stack.

The read routine uses 9 bytes of stack space in addition to the one byte of address pushed by the user. Sufficient memory must be available for this stack usage.

Because of the Flash memory architecture, NVDS reads exhibit a nonuniform execution time. A read operation takes between 44  $\mu$ s and 489  $\mu$ s (assuming a 20MHz system clock). Slower system clock speeds result in proportionally higher execution times.

NVDS byte reads from invalid addresses (those exceeding the NVDS array size) return 0xff. Illegal read operations have a 2  $\mu$ s execution time.

The status byte returned by the NVDS read routine is zero for successful read, as determined by a CRC check. If the status byte is nonzero, there was a corrupted value in the NVDS array at the location being read. In this case, the value returned in R0 is the byte most recently written to the array that does not have a CRC error.

## **Power Failure Protection**

The NVDS routines employ error checking mechanisms to ensure a power failure endangers only the most recently written byte. Bytes previously written to the array are not perturbed.

A system reset (such as a pin reset or Watchdog Timer reset) that occurs during a write operation also perturbs the byte currently being written. All other bytes in the array are unperturbed.

## **Optimizing NVDS Memory Usage for Execution Speed**

NVDS read time can vary drastically. This discrepancy is a trade-off for minimizing the frequency of writes that require post-write page erases, as indicated in Table 107. The NVDS read time of address N is a function of the number of writes to addresses other than N since the most recent write to address N, plus the number of writes since the most recent page erase. Neglecting effects caused by page erases and results caused by the initial condition in which the NVDS is blank, a rule of thumb is that every write since the most recent page erase causes read times of unwritten addresses to increase by 1 µs up to a maximum of (511-NVDS\_SIZE)µs.

# **Oscillator Control**

The Z8 Encore! XP F082A Series devices uses five possible clocking schemes, each user-selectable:

- Internal precision trimmed RC oscillator (IPO)

- On-chip oscillator using off-chip crystal or resonator

- On-chip oscillator using external RC network

- External clock drive

- On-chip low power Watchdog Timer oscillator

- Clock failure detection circuitry

In addition, Z8 Encore! XP F082A Series devices contain clock failure detection and recovery circuitry, allowing continued operation despite a failure of the system clock oscillator.

# Operation

This chapter discusses the logic used to select the system clock and handle primary oscillator failures.

# **System Clock Selection**

The oscillator control block selects from the available clocks. Table 112 details each clock source and its usage.

| Assembly     |                                                                                                                   |         | ress<br>ode | _ Opcode(s) | Flags |   |   |      |   |   | Fetch<br>Cycle | Instr.<br>Cycle |

|--------------|-------------------------------------------------------------------------------------------------------------------|---------|-------------|-------------|-------|---|---|------|---|---|----------------|-----------------|

| Mnemonic     | Symbolic Operation                                                                                                | dst src |             | (Hex)       |       | Ζ | S | SVDH |   |   | S              | S               |

| DA dst       | $dst \gets DA(dst)$                                                                                               | R       |             | 40          | *     | * | * | Х    | _ | _ | 2              | 2               |

|              |                                                                                                                   | IR      |             | 41          | =     |   |   |      |   |   | 2              | 3               |

| DEC dst      | dst ← dst - 1                                                                                                     | R       |             | 30          | _     | * | * | *    | _ | _ | 2              | 2               |

|              |                                                                                                                   | IR      |             | 31          | -     |   |   |      |   |   | 2              | 3               |

| DECW dst     | dst ← dst - 1                                                                                                     | RR      |             | 80          | -     | * | * | *    | - | - | 2              | 5               |

|              |                                                                                                                   | IRR     |             | 81          | -     |   |   |      |   |   | 2              | 6               |

| DI           | $IRQCTL[7] \leftarrow 0$                                                                                          |         |             | 8F          | -     | - | - | -    | - | - | 1              | 2               |

| DJNZ dst, RA | $dst \leftarrow dst - 1$<br>if dst $\neq 0$<br>PC $\leftarrow$ PC + X                                             | r       |             | 0A-FA       | _     | _ | _ | _    | _ | - | 2              | 3               |

| EI           | $IRQCTL[7] \leftarrow 1$                                                                                          |         |             | 9F          | -     | - | - | -    | - | - | 1              | 2               |

| HALT         | Halt Mode                                                                                                         |         |             | 7F          | -     | _ | _ | _    | - | - | 1              | 2               |

| INC dst      | dst ← dst + 1                                                                                                     | R       |             | 20          | -     | * | * | _    | _ | - | 2              | 2               |

|              |                                                                                                                   | IR      |             | 21          | -     |   |   |      |   |   | 2              | 3               |

|              |                                                                                                                   | r       |             | 0E-FE       | -     |   |   |      |   |   | 1              | 2               |

| INCW dst     | dst ← dst + 1                                                                                                     | RR      |             | A0          | -     | * | * | *    | - | - | 2              | 5               |

|              |                                                                                                                   | IRR     |             | A1          | -     |   |   |      |   |   | 2              | 6               |

| IRET         | $FLAGS \leftarrow @SP$ $SP \leftarrow SP + 1$ $PC \leftarrow @SP$ $SP \leftarrow SP + 2$ $IRQCTL[7] \leftarrow 1$ |         |             | BF          | *     | * | * | *    | * | * | 1              | 5               |

| JP dst       | $PC \leftarrow dst$                                                                                               | DA      |             | 8D          | -     | _ | _ | _    | _ | - | 3              | 2               |

|              |                                                                                                                   | IRR     |             | C4          | =     |   |   |      |   |   | 2              | 3               |

| JP cc, dst   | if cc is true<br>PC $\leftarrow$ dst                                                                              | DA      |             | 0D-FD       | _     | _ | _ | -    | _ | _ | 3              | 2               |

### Table 128. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 =Set to 1.

Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

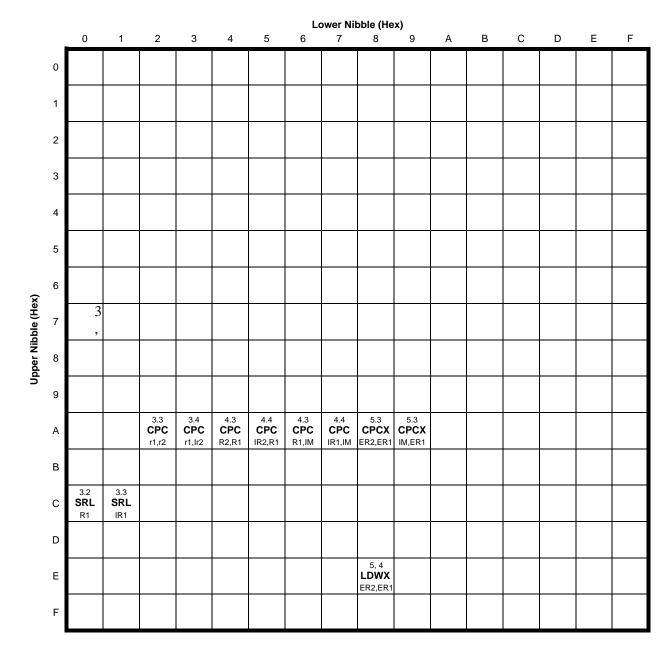

Figure 32. Second Opcode Map after 1FH

# **Electrical Characteristics**

The data in this chapter represents all known data prior to qualification and characterization of the F082A Series of products, and is therefore subject to change. Additional electrical characteristics may be found in the individual chapters of this document.

# **Absolute Maximum Ratings**

Stresses greater than those listed in Table 130 may cause permanent damage to the device. These ratings are stress ratings only. Operation of the device at any condition outside those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. For improved reliability, tie unused inputs to one of the supply voltages ( $V_{DD}$  or  $V_{SS}$ ).

| Parameter                                           | Minimum | Maximum | Units | Notes |

|-----------------------------------------------------|---------|---------|-------|-------|

| Ambient temperature under bias                      | -40     | +105    | °C    |       |

| Storage temperature                                 | -65     | +150    | °C    |       |

| Voltage on any pin with respect to V <sub>SS</sub>  | -0.3    | +5.5    | V     | 1     |

|                                                     | -0.3    | +3.9    | V     | 2     |

| Voltage on $V_{DD}$ pin with respect to $V_{SS}$    | -0.3    | +3.6    | V     |       |

| Maximum current on input and/or inactive output pin | -5      | +5      | μA    |       |

| Maximum output current from active output pin       | -25     | +25     | mA    |       |

| 8-pin Packages Maximum Ratings at 0°C to 70°C       |         |         |       |       |

| Total power dissipation                             |         | 220     | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$    |         | 60      | mA    |       |

| 20-pin Packages Maximum Ratings at 0°C to 70°C      |         |         |       |       |

| Total power dissipation                             |         | 430     | mW    |       |

| Table 130. Absolute Maximum Ratings | Table | 130. | Absolute | Maximum | Ratings |

|-------------------------------------|-------|------|----------|---------|---------|

|-------------------------------------|-------|------|----------|---------|---------|

|                         |                                                    | V <sub>DD</sub>      | ) = 2.7 V to 3 | 3.6 V                            |       |                                                                  |

|-------------------------|----------------------------------------------------|----------------------|----------------|----------------------------------|-------|------------------------------------------------------------------|

| Symbol                  | Parameter                                          | Typical <sup>1</sup> |                | Maximum<br>Ext Temp <sup>3</sup> | Units | Conditions                                                       |

| I <sub>DD</sub><br>Stop | Supply Current in STOP Mode                        | 0.1                  |                |                                  | μA    | No peripherals enabled. All pins driven to $V_{DD}$ or $V_{SS}.$ |

| I <sub>DD</sub> Halt    | Supply Current in                                  | 35                   | 55             | 65                               | μA    | 32kHz.                                                           |

|                         | HALT Mode (with                                    | 520                  |                |                                  | μA    | 5.5MHz.                                                          |

|                         | all peripherals dis abled)                         | 2.1                  | 2.85           | 2.85                             | mA    | 20MHz.                                                           |

| I <sub>DD</sub>         | Supply Current in                                  | 2.8                  |                |                                  | mA    | 32kHz.                                                           |

|                         | ACTIVE Mode<br>(with all peripherals               | 4.5                  | 5.2            | 5.2                              | mA    | 5.5MHz.                                                          |

|                         | disabled)                                          | 5.5                  | 6.5            | 6.5                              | mA    | 10MHz.                                                           |

|                         | ,                                                  | 7.9                  | 11.5           | 11.5                             | mA    | 20MHz.                                                           |

| I <sub>DD</sub><br>WDT  | Watchdog Timer<br>Supply Current                   | 0.9                  | 1.0            | 1.1                              | μA    |                                                                  |

| I <sub>DD</sub>         | Crystal Oscillator                                 | 40                   |                |                                  | μA    | 32kHz.                                                           |

| XTAL                    | Supply Current                                     | 230                  |                |                                  | μA    | 4MHz.                                                            |

|                         |                                                    | 760                  |                |                                  | μA    | 20MHz.                                                           |

| I <sub>DD</sub> IPO     | Internal Precision<br>Oscillator Supply<br>Current | 350                  | 500            | 550                              | μA    |                                                                  |

| I <sub>DD</sub><br>VBO  | Voltage Brown-Out<br>and Low-Voltage               | 50                   |                |                                  | μA    | For 20-/28-pin devices (VBO only); See Note 4.                   |

|                         | Detect Supply Cur-                                 |                      |                |                                  |       | For 8-pin devices; See Note 4.                                   |

| I <sub>DD</sub>         | Analog to Digital                                  | 2.8                  | 3.1            | 3.2                              | mA    | 32kHz.                                                           |

| ADC                     | Converter Supply                                   | 3.1                  | 3.6            | 3.7                              | mA    | 5.5MHz.                                                          |

|                         | Current (with External Refer-                      | 3.3                  | 3.7            | 3.8                              | mA    | 10MHz.                                                           |

|                         | ence)                                              | 3.7                  | 4.2            | 4.3                              | mA    | 20MHz.                                                           |

#### Table 132. Power Consumption

Notes:

1. Typical conditions are defined as  $V_{DD}$  = 3.3 V and +30°C.

2. Standard temperature is defined as  $\overline{T}_A = 0^{\circ}C$  to +70°C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

3. Extended temperature is defined as  $T_A = -40^{\circ}$ C to +105°C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

4. For this block to operate, the bandgap circuit is automatically turned on and must be added to the total supply current. This bandgap current is only added once, regardless of how many peripherals are using it.

## **UART** Timing

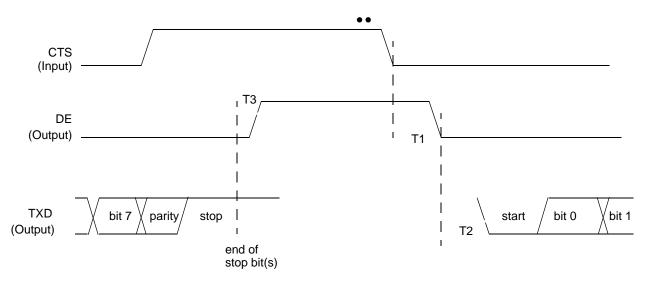

Figure 37 and Table 146 provide timing information for UART pins for the case where CTS is used for flow control. The CTS to DE assertion delay (T1) assumes the Transmit Data Register has been loaded with data prior to CTS assertion.

| Figure 37. | UART | Timing | With C | ٢S |

|------------|------|--------|--------|----|

|------------|------|--------|--------|----|

|                |                                                    | Delay (ns)                 |                                            |  |  |

|----------------|----------------------------------------------------|----------------------------|--------------------------------------------|--|--|

| Parameter      | Abbreviation                                       | Minimum                    | Maximum                                    |  |  |

| UART           |                                                    |                            |                                            |  |  |

| T <sub>1</sub> | CTS Fall to DE output delay                        | 2 * X <sub>IN</sub> period | 2 * X <sub>IN</sub> period +<br>1 bit time |  |  |

| T <sub>2</sub> | DE assertion to TXD falling edge (start bit) delay | Ŧ                          | - 5                                        |  |  |

| T <sub>3</sub> | End of Stop Bit(s) to DE deassertion delay         | ±                          | : 5                                        |  |  |

| Table 146. | IIART | Timina | With   | <b>CTS</b> |

|------------|-------|--------|--------|------------|

| Table 140. |       | runng  | VVILII | 613        |

| Part Number         | Flash     | RAM     | NVDS    | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |

|---------------------|-----------|---------|---------|-----------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|

| Z8 Encore! XP F082A |           |         | (B Flas | sh        |            |                     |                     |                |            |                    |                     |

| Standard Temperatu  |           |         |         |           |            |                     |                     |                |            |                    |                     |

| Z8F081APB020SG      | 8KB       | 1KB     | 0       | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 8-pin package  |

| Z8F081AQB020SG      | 8KB       | 1KB     | 0       | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | QFN 8-pin package   |

| Z8F081ASB020SG      | 8KB       | 1KB     | 0       | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 8-pin package  |

| Z8F081ASH020SG      | 8KB       | 1KB     | 0       | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 20-pin package |

| Z8F081AHH020SG      | 8KB       | 1KB     | 0       | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 20-pin package |

| Z8F081APH020SG      | 8KB       | 1KB     | 0       | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 20-pin package |

| Z8F081ASJ020SG      | 8KB       | 1KB     | 0       | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 28-pin package |

| Z8F081AHJ020SG      | 8KB       | 1KB     | 0       | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 28-pin package |

| Z8F081APJ020SG      | 8KB       | 1KB     | 0       | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 28-pin package |

| Extended Temperatu  | ıre: –40° | C to 10 | 5°C     |           |            |                     |                     |                |            |                    |                     |

| Z8F081APB020EG      | 8KB       | 1KB     | 0       | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 8-pin package  |

| Z8F081AQB020EG      | 8KB       | 1KB     | 0       | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | QFN 8-pin package   |

| Z8F081ASB020EG      | 8KB       | 1KB     | 0       | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 8-pin package  |

| Z8F081ASH020EG      | 8KB       | 1KB     | 0       | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 20-pin package |

| Z8F081AHH020EG      | 8KB       | 1KB     | 0       | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 20-pin package |

| Z8F081APH020EG      | 8KB       | 1KB     | 0       | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 20-pin package |

| Z8F081ASJ020EG      | 8KB       | 1KB     | 0       | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 28-pin package |

| Z8F081AHJ020EG      | 8KB       | 1KB     | 0       | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 28-pin package |

| Z8F081APJ020EG      | 8KB       | 1KB     | 0       | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 28-pin package |

## Table 148. Z8 Encore! XP F082A Series Ordering Matrix

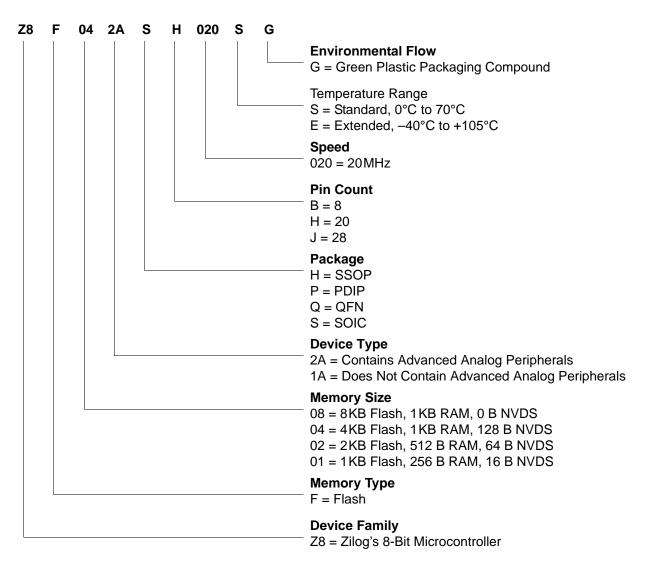

# Part Number Suffix Designations

Zilog part numbers consist of a number of components, as indicated in the following example.

**Example.** Part number Z8F042ASH020SG is an 8-bit Flash MCU with 4KB of Program Memory, equipped with advanced analog peripherals in a 20-pin SOIC package, operating within a 0°C to +70°C temperature range and built using lead-free solder.