Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 23                                                           |

| Program Memory Size        | 1KB (1K × 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 16 x 8                                                       |

| RAM Size                   | 256 x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 8x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | 0°C ~ 70°C (TA)                                              |

| Mounting Type              | Through Hole                                                 |

| Package / Case             | 28-DIP (0.600", 15.24mm)                                     |

| Supplier Device Package    | ·                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f012apj020sg    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Revision History**

Each instance in this document's revision history reflects a change from its previous edition. For more details, refer to the corresponding page(s) or appropriate links furnished in the table below.

| Date        | Revision<br>Level | Chapter/Section                                                                                                               | Description                                                                                                                                                                                 | Page<br>No.                                                |

|-------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| Dec<br>2012 | 27                | Port Alternate Function Map-<br>ping (Non 8-Pin Parts), Port<br>Alternate Function Mapping (8-<br>Pin Parts)                  | Added missing Port D data to Table 15; cor-<br>rected active Low status (set overlines) for<br>PA0 (T0OUT), PA2 (RESET) and PA5<br>(T1OUT) in Table 16.                                     | <u>40, 43</u>                                              |

| Sep<br>2011 | 26                | LED Drive Enable Register                                                                                                     | Clarified statement surrounding the Alternate<br>Function Register as it relates to the LED<br>function; revised Flash Sector Protect Regis-<br>ter description; revised Packaging chapter. | <u>53,</u><br><u>157,</u><br>245                           |

| Sep<br>2008 | 25                | Overview, Address Space,<br>Register Map, General-Pur-<br>pose Input/Output, Available<br>Packages, Ordering Informa-<br>tion | Added references to F042A Series back in Table 1, Table 5, Table 7 and Table 14.                                                                                                            | <u>2, 8,</u><br><u>16, 18,</u><br><u>36,</u><br><u>246</u> |

| May<br>2008 | 24                | Overview, Address Space,<br>Register Map, General-Pur-<br>pose Input/Output, Available<br>Packages, Ordering Informa-<br>tion | Changed title to Z8 Encore! XP F082A Series<br>and removed references to F042A Series in<br>Table 1, Table 5, Table 7 and Table 14.                                                         | <u>2, 8,</u><br><u>16, 18,</u><br><u>36,</u><br><u>246</u> |

| Dec<br>2007 | 23                | Pin Description, General-Pur-<br>pose Input/Output, Watchdog<br>Timer                                                         | Updated Figure 3, Table 15, Tables 60 through 62.                                                                                                                                           | <u>9, 40,</u><br><u>97</u>                                 |

| Jul<br>2007 | 22                | Electrical Characteristics                                                                                                    | Updated Tables 16 and 132; power con-<br>sumption data.                                                                                                                                     | <u>43,</u><br>229                                          |

| Jun<br>2007 | 21                | n/a                                                                                                                           | Revision number update.                                                                                                                                                                     | All                                                        |

iii

# **Table of Contents**

| Revision History                                                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| List of Figures                                                                                                                                                                                        |

| List of Tables                                                                                                                                                                                         |

| Overview1Features1Part Selection Guide2Block Diagram3CPU and Peripheral Overview410-Bit Analog-to-Digital Converter4Low-Power Operational Amplifier4Internal Precision Oscillator5Temperature Sensor5  |

| Analog Comparator5External Crystal Oscillator5Low Voltage Detector5On-Chip Debugger5Universal Asynchronous Receiver/Transmitter5Timers5General-Purpose Input/Output6Direct LED Drive6Flash Controller6 |

| Non-Volatile Data Storage 6   Interrupt Controller 6   Reset Controller 6                                                                                                                              |

| Pin Description8Available Packages8Pin Configurations8Signal Descriptions10Pin Characteristics12                                                                                                       |

| Address Space15Register File15Program Memory15Data Memory17Flash Information Area17                                                                                                                    |

| Register Map                                                                                                                                                                                           |

7

warning signal. The  $\overline{\text{RESET}}$  pin is bidirectional, that is, it functions as reset source and as a reset indicator.

| Signal Mnemonic     | I/O     | Description                                                                                                                                                                                                                                                                 |

|---------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog              |         |                                                                                                                                                                                                                                                                             |

| ANA[7:0]            | Ι       | Analog Port. These signals are used as inputs to the analog-to-digital converter (ADC).                                                                                                                                                                                     |

| VREF                | I/O     | Analog-to-digital converter reference voltage input, or buffered output for internal reference.                                                                                                                                                                             |

| Low-Power Operation | onal Ar | nplifier (LPO)                                                                                                                                                                                                                                                              |

| AMPINP/AMPINN       | I       | LPO inputs. If enabled, these pins drive the positive and negative amplifier inputs respectively.                                                                                                                                                                           |

| AMPOUT              | 0       | LPO output. If enabled, this pin is driven by the on-chip LPO.                                                                                                                                                                                                              |

| Oscillators         |         |                                                                                                                                                                                                                                                                             |

| XIN                 | I       | External Crystal Input. This is the input pin to the crystal oscillator. A crystal can be connected between it and the $X_{OUT}$ pin to form the oscillator. In addition, this pin is used with external RC networks or external clock drivers to provide the system clock. |

| X <sub>OUT</sub>    | 0       | External Crystal Output. This pin is the output of the crystal oscillator. A crystal can be connected between it and the <b>XIN</b> pin to form the oscillator.                                                                                                             |

| Clock Input         |         |                                                                                                                                                                                                                                                                             |

| CLKIN               | I       | Clock Input Signal. This pin may be used to input a TTL-level signal to be used as the system clock.                                                                                                                                                                        |

| LED Drivers         |         |                                                                                                                                                                                                                                                                             |

| LED                 | 0       | Direct LED drive capability. All port C pins have the capability to drive an LED without any other external components. These pins have programma ble drive strengths set by the GPIO block.                                                                                |

| On-Chip Debugger    |         |                                                                                                                                                                                                                                                                             |

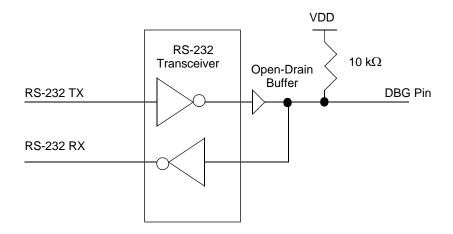

| DBG                 | I/O     | Debug. This signal is the control and data input and output to and from the On-Chip Debugger.                                                                                                                                                                               |

|                     |         | <b>Caution:</b> The DBG pin is open-drain and requires a pull-up resistor to ensure proper operation.                                                                                                                                                                       |

#### **Table 2. Signal Descriptions (Continued)**

replaced by  $AV_{DD}$  and  $AV_{SS}$ . 2. The  $AV_{DD}$  and  $AV_{SS}$  signals are available only in 28-pin packages with ADC. They are replaced by PB6 and PB7 on 28-pin packages without ADC.

# **Reset Sources**

Table 9 lists the possible sources of a system reset.

| Table 9. Reset Sources and Resulting Reset Type |  |

|-------------------------------------------------|--|

| Operating Mode       | Reset Source                                          | Special Conditions                                                                            |

|----------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| NORMAL or HALT modes | Power-On Reset/Voltage Brown-<br>Out                  | Reset delay begins after supply voltage exceeds POR level.                                    |

|                      | Watchdog Timer time-out when configured for Reset     | None.                                                                                         |

|                      | RESET pin assertion                                   | All reset pulses less than three system clocks in width are ignored.                          |

|                      | On-Chip Debugger initiated Reset (OCDCTL[0] set to 1) | System Reset, except the On-Chip Debugger is unaffected by the reset.                         |

| STOP Mode            | Power-On Reset/Voltage Brown-<br>Out                  | Reset delay begins after supply voltage exceeds POR level.                                    |

|                      | RESET pin assertion                                   | All reset pulses less than the specified analog delay are ignored. See Table 131 on page 229. |

|                      | DBG pin driven Low                                    | None.                                                                                         |

# **Power-On Reset**

Z8 Encore! XP F082A Series devices contain an internal Power-On Reset circuit. The POR circuit monitors the supply voltage and holds the device in the Reset state until the supply voltage reaches a safe operating level. After the supply voltage exceeds the POR voltage threshold (VPOR), the device is held in the Reset state until the POR Counter has timed out. If the crystal oscillator is enabled by the option bits, this time-out is longer.

After the Z8 Encore! XP F082A Series device exits the Power-On Reset state, the eZ8 CPU fetches the Reset vector. Following Power-On Reset, the POR status bit in the Reset Status (RSTSTAT) Register is set to 1.

Figure 5 displays Power-On Reset operation. See Electrical Characteristics on page 221 for the POR threshold voltage (V<sub>POR</sub>).

| Port                | Pin | Mnemonic                      | Alternate Function Description | Alternate Function<br>Set Register AFS1 |

|---------------------|-----|-------------------------------|--------------------------------|-----------------------------------------|

| Port B <sup>3</sup> | PB0 | Reserved                      |                                | AFS1[0]: 0                              |

|                     |     | ANA0/AMPOUT                   | ADC Analog Input/LPO Output    | AFS1[0]: 1                              |

|                     | PB1 | Reserved                      |                                | AFS1[1]: 0                              |

|                     |     | ANA1/AMPINN                   | ADC Analog Input/LPO Input (N) | AFS1[1]: 1                              |

|                     | PB2 | Reserved                      |                                | AFS1[2]: 0                              |

|                     |     | ANA2/AMPINP                   | ADC Analog Input/LPO Input (P) | AFS1[2]: 1                              |

|                     | PB3 | CLKIN                         | External Clock Input           | AFS1[3]: 0                              |

|                     |     | ANA3                          | ADC Analog Input               | AFS1[3]: 1                              |

|                     | PB4 | Reserved                      |                                | AFS1[4]: 0                              |

|                     |     | ANA7                          | ADC Analog Input               | AFS1[4]: 1                              |

|                     | PB5 | Reserved                      |                                | AFS1[5]: 0                              |

|                     |     | V <sub>REF</sub> <sup>4</sup> | ADC Voltage Reference          | AFS1[5]: 1                              |

|                     | PB6 | Reserved                      |                                | AFS1[6]: 0                              |

|                     |     | Reserved                      |                                | AFS1[6]: 1                              |

|                     | PB7 | Reserved                      |                                | AFS1[7]: 0                              |

|                     |     | Reserved                      |                                | AFS1[7]: 1                              |

#### Table 15. Port Alternate Function Mapping (Non 8-Pin Parts) (Continued)

Notes:

- Because there is only a single alternate function for each Port A pin, the Alternate Function Set registers are not implemented for Port A. Enabling alternate function selections automatically enables the associated alternate function. See the <u>Port A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

- 2. Whether PA0/PA6 takes on the timer input or timer output complement function depends on the timer configuration. See the <u>Timer Pin Signal Operation</u> section on page 84 for details.

- Because there are at most two choices of alternate function for any pin of Port B, the Alternate Function Set Register AFS2 is not used to select the function. Alternate function selection must also be enabled. See the <u>Port</u> <u>A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

- 4. V<sub>RFF</sub> is available on PB5 in 28-pin products and on PC2 in 20-pin parts.

- Because there are at most two choices of alternate function for any pin of Port C, the Alternate Function Set Register AFS2 is not used to select the function. Alternate function selection must also be enabled. See the <u>Port</u> <u>A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

- 6. Because there is only a single alternate function for the Port PD0 pin, the Alternate Function Set registers are not implemented for Port D. Enabling alternate function selections automatically enables the associated alternate function. See the Port A–D Alternate Function Subregisters (PxAF) section on page 47 for details.

# **Caution:** The frequency of the comparator output signal must not exceed one-fourth the system clock frequency. Further, the high or low state of the comparator output signal pulse must be no less than twice the system clock period. A shorter pulse may not be captured.

After reaching the reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer Reload.

Observe the following steps for configuring a timer for COMPARATOR COUNTER Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer.

- Configure the timer for COMPARATOR COUNTER Mode.

- Select either the rising edge or falling edge of the comparator output signal for the count. This also sets the initial logic level (High or Low) for the Timer Output alternate function. However, the Timer Output function is not required to be enabled.

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This action only affects the first pass in COMPARATOR COUNTER Mode. After the first timer Reload in COMPARATOR COUNTER Mode, counting always begins at the reset value of 0001H. Generally, in COMPARATOR COUNTER Mode the Timer High and Low Byte registers must be written with the value 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 6. Write to the Timer Control Register to enable the timer.

In COMPARATOR COUNTER Mode, the number of comparator output transitions since the timer start is computed via the following equation:

Comparator Output Transitions = Current Count Value – Start Value

- Configure the timer for GATED Mode

- Set the prescale value

- 2. Write to the Timer High and Low Byte registers to set the starting count value. Writing these registers only affects the first pass in GATED Mode. After the first timer reset in GATED Mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. Enable the timer interrupt, if appropriate and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input deassertion and reload events. If appropriate, configure the timer interrupt to be generated only at the input deassertion event or the reload event by setting TICONFIG field of the TxCTL0 Register.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control Register to enable the timer.

- 7. Assert the Timer Input signal to initiate the counting.

#### CAPTURE/COMPARE Mode

In CAPTURE/COMPARE Mode, the timer begins counting on the first external Timer Input transition. The acceptable transition (rising edge or falling edge) is set by the TPOL bit in the Timer Control Register. The timer input is the system clock.

Every subsequent acceptable transition (after the first) of the Timer Input signal captures the current count value. The Capture value is written to the Timer PWM High and Low Byte registers. When the Capture event occurs, an interrupt is generated, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL0 Register is set to indicate the timer interrupt is caused by an input capture event.

If no Capture event occurs, the timer counts up to the 16-bit Compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the Compare value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL0 Register is cleared to indicate the timer interrupt is not because of an input capture event.

Observe the following steps for configuring a timer for CAPTURE/COMPARE Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE/COMPARE Mode

- Set the prescale value

# Analog-to-Digital Converter

The analog-to-digital converter (ADC) converts an analog input signal to its digital representation. The features of this sigma-delta ADC include:

- 11-bit resolution in DIFFERENTIAL Mode

- 10-bit resolution in SINGLE-ENDED Mode

- Eight single-ended analog input sources are multiplexed with general-purpose I/O ports

- 9<sup>th</sup> analog input obtained from temperature sensor peripheral

- 11 pairs of differential inputs also multiplexed with general-purpose I/O ports

- Low-power operational amplifier (LPO)

- Interrupt on conversion complete

- Bandgap generated internal voltage reference with two selectable levels

- Manual in-circuit calibration is possible employing user code (offset calibration)

- Factory calibrated for in-circuit error compensation

# Architecture

Figure 19 displays the major functional blocks of the ADC. An analog multiplexer network selects the ADC input from the available analog pins, ANA0 through ANA7.

The input stage of the ADC allows both differential gain and buffering. The following input options are available:

- Unbuffered input (SINGLE-ENDED and DIFFERENTIAL modes)

- Buffered input with unity gain (SINGLE-ENDED and DIFFERENTIAL modes)

- LPO output with full pin access to the feedback path

# **Calibration and Compensation**

The Z8 Encore! XP F082A Series ADC is factory calibrated for offset error and gain error, with the compensation data stored in Flash memory. Alternatively, you can perform your own calibration, storing the values into Flash themselves. Thirdly, the user code can perform a manual offset calibration during DIFFERENTIAL Mode operation.

### **Factory Calibration**

Devices that have been factory calibrated contain 30 bytes of calibration data in the Flash option bit space. This data consists of 3 bytes for each input mode, one for offset and two for gain correction. For a list of input modes for which calibration data exists, see the <u>Zilog Calibration Data</u> section on page 168.

#### **User Calibration**

If you have precision references available, its own external calibration can be performed using any input modes. This calibration data takes into account buffer offset and nonlinearity; therefore Zilog recommends that this calibration be performed separately for each of the ADC input modes planned for use.

#### **Manual Offset Calibration**

When uncalibrated, the ADC has significant offset (see <u>Table 139</u> on page 236). Subsequently, manual offset calibration capability is built into the block. When the ADC Control Register 0 sets the input mode (ANAIN[2:0]) to MANUAL OFFSET CALIBRATION Mode, the differential inputs to the ADC are shorted together by an internal switch. Reading the ADC value at this point produces 0 in an ideal system. The value actually read is the ADC offset. This value can be stored in nonvolatile memory (see the <u>Nonvolatile Data Storage</u> chapter on page 176) and accessed by user code to compensate for the input offset error. There is no provision for manual gain calibration.

### Software Compensation Procedure Using Factory Calibration Data

The value read from the ADC high and low byte registers is uncompensated. The user mode software must apply gain and offset correction to this uncompensated value for maximum accuracy. The following equation yields the compensated value:

$$ADC_{comp} = (ADC_{uncomp} - OFFCAL) + ((ADC_{uncomp} - OFFCAL) \times GAINCAL)/2$$

where GAINCAL is the gain calibration value, OFFCAL is the offset calibration value and  $ADC_{uncomp}$  is the uncompensated value read from the ADC. All values are in two's complement format.

# **Temperature Sensor**

The on-chip Temperature Sensor allows you to measure temperature on the die with either the on-board ADC or on-board comparator. This block is factory calibrated for in-circuit software correction. Uncalibrated accuracy is significantly worse, therefore the temperature sensor is not recommended for uncalibrated use.

# **Temperature Sensor Operation**

The on-chip temperature sensor is a Proportional to Absolute Temperature (PTAT) topology. A pair of Flash option bytes contain the calibration data. The temperature sensor can be disabled by a bit in the <u>Power Control Register 0</u> section on page 33 to reduce power consumption.

The temperature sensor can be directly read by the ADC to determine the absolute value of its output. The temperature sensor output is also available as an input to the comparator for threshold type measurement determination. The accuracy of the sensor when used with the comparator is substantially less than when measured by the ADC.

If the temperature sensor is routed to the ADC, the ADC must be configured in unity-gain buffered mode (for details, see the <u>Input Buffer Stage</u> section on page 133). The value read back from the ADC is a signed number, although it is always positive.

The sensor is factory-trimmed through the ADC using the external 2.0 V reference. Unless the sensor is retrimmed for use with a different reference, it is most accurate when used with the external 2.0 V reference.

Because this sensor is an on-chip sensor, Zilog recommends that the user account for the difference between ambient and die temperature when inferring ambient temperature conditions.

During normal operation, the die undergoes heating that causes a mismatch between the ambient temperature and that measured by the sensor. For best results, the Z8 Encore! XP device must be placed into STOP Mode for sufficient time such that the die and ambient temperatures converge (this time is dependent on the thermal design of the system). The temperature sensor measurement must then be made immediately after recovery from STOP Mode.

The following equation defines the transfer function between the temperature sensor output voltage and the die temperature. This is needed for comparator threshold measurements.

$V = 0.01 \times T + 0.65$

In the above equation, T is the temperature in °C; V is the sensor output in volts.

Assuming a compensated ADC measurement, the following equation defines the relationship between the ADC reading and the die temperature:

$T = (25/128) \times (ADC - TSCAL[11:2]) + 30$

In the above equation, T is the temperature in C; ADC is the 10-bit compensated ADC value; and TSCAL is the temperature sensor calibration value, ignoring the two least significant bits of the 12-bit value.

See the <u>Temperature Sensor Calibration Data</u> section on page 171 for the location of TSCAL.

#### Calibration

The temperature sensor undergoes calibration during the manufacturing process and is maximally accurate at 30°C. Accuracy decreases as measured temperatures move further from the calibration point.

These serial numbers are stored in the Flash information page and are unaffected by mass erasure of the device's Flash memory. See the Reading the Flash Information Page section below and the <u>Serialization Data section on page 173</u> for more details.

#### **Randomized Lot Identification Bits**

As an optional feature, Zilog is able to provide a factory-programmed random lot identifier. With this feature, all devices in a given production lot are programmed with the same random number. This random number is uniquely regenerated for each successive production lot and is not likely to be repeated.

The randomized lot identifier is a 32 byte binary value, stored in the Flash information page and is unaffected by mass erasure of the device's Flash memory. See Reading the Flash Information Page, below, and the <u>Randomized Lot Identifier section on page 174</u> for more details.

## **Reading the Flash Information Page**

The following code example shows how to read data from the Flash information area.

; get value at info address 60 (FE60h) ldx FPS, #%80 ; enable access to flash info page ld R0, #%FE ld R1, #%60 ldc R2, @RR0 ; R2 now contains the calibration value

# **Flash Option Bit Control Register Definitions**

This section briefly describes the features of the Trim Bit Address and Data registers.

### **Trim Bit Address Register**

The Trim Bit Address (TRMADR) Register contains the target address for an access to the trim option bits (Table 86).

| Bit     | 7                                     | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|---------------------------------------|-----|-----|-----|-----|-----|-----|-----|

| Field   | TRMADR: Trim Bit Address (00H to 1FH) |     |     |     |     |     |     |     |

| RESET   | 0                                     | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W                                   | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | FF6H                                  |     |     |     |     |     |     |     |

Table 86. Trim Bit Address Register (TRMADR)

Figure 25. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface; #2 of 2

## **DEBUG Mode**

The operating characteristics of the devices in DEBUG Mode are:

- The eZ8 CPU fetch unit stops, idling the eZ8 CPU, unless directed by the OCD to execute specific instructions

- The system clock operates unless in STOP Mode

- All enabled on-chip peripherals operate unless in STOP Mode

- Automatically exits HALT Mode

- Constantly refreshes the Watchdog Timer, if enabled

### **Entering DEBUG Mode**

The operating characteristics of the devices entering DEBUG Mode are:

- The device enters DEBUG Mode after the eZ8 CPU executes a BRK (Breakpoint) instruction

- If the DBG pin is held Low during the final clock cycle of system reset, the part enters DEBUG Mode immediately (20-/28-pin products only)

**Note:** Holding the DBG pin Low for an additional 5000 (minimum) clock cycles after reset (making sure to account for any specified frequency error if using an internal oscillator) prevents a false interpretation of an Autobaud sequence (see the <u>OCD Auto-Baud Detector/Generator</u> section on page 183).

# **Oscillator Control**

The Z8 Encore! XP F082A Series devices uses five possible clocking schemes, each user-selectable:

- Internal precision trimmed RC oscillator (IPO)

- On-chip oscillator using off-chip crystal or resonator

- On-chip oscillator using external RC network

- External clock drive

- On-chip low power Watchdog Timer oscillator

- Clock failure detection circuitry

In addition, Z8 Encore! XP F082A Series devices contain clock failure detection and recovery circuitry, allowing continued operation despite a failure of the system clock oscillator.

# Operation

This chapter discusses the logic used to select the system clock and handle primary oscillator failures.

# **System Clock Selection**

The oscillator control block selects from the available clocks. Table 112 details each clock source and its usage.

| Parameter                           | Value       | Units | Comments |

|-------------------------------------|-------------|-------|----------|

| Frequency                           | 20          | MHz   |          |

| Resonance                           | Parallel    |       |          |

| Mode                                | Fundamental |       |          |

| Series Resistance (R <sub>S</sub> ) | 60          | W     | Maximum  |

| Load Capacitance (C <sub>L</sub> )  | 30          | pF    | Maximum  |

| Shunt Capacitance (C <sub>0</sub> ) | 7           | pF    | Maximum  |

| Drive Level                         | 1           | mW    | Maximum  |

Table 114. Recommended Crystal Oscillator Specifications

| Table 115. Transconductance Values for Low, Medium and High Gain Operating Mode | Table 115. Tra | ansconductance V | Values for Low. | Medium and High | Gain Operating Modes |

|---------------------------------------------------------------------------------|----------------|------------------|-----------------|-----------------|----------------------|

|---------------------------------------------------------------------------------|----------------|------------------|-----------------|-----------------|----------------------|

| Mode         | Crystal<br>Frequency<br>de Range Function |                                     | (U៖  | nductanc<br>se this rar<br>calculatio | nge  |

|--------------|-------------------------------------------|-------------------------------------|------|---------------------------------------|------|

| Low Gain*    | 32kHz-1MHz                                | Low Power/Frequency Applications    | 0.02 | 0.04                                  | 0.09 |

| Medium Gain* | 0.5MHz-10MHz                              | Medium Power/Frequency Applications | 0.84 | 1.7                                   | 3.1  |

| High Gain*   | 8MHz–20MHz                                | High Power/Frequency Applications   | 1.1  | 2.3                                   | 4.2  |

if no oscillation occurs, reduce the values of the capacitors C1 and C2 to decrease the loading.

205

#### Assembly Language Source Program Example

| JP START      | ; Everything after the semicolon is a comment.                                                                                                                                                                                                                                      |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| START:        | ; A label called 'START'. The first instruction (JP START) in this ; example causes program execution to jump to the point within the ; program where the START label occurs.                                                                                                       |

| LD R4, R7     | ; A Load (LD) instruction with two operands. The first operand,<br>; Working Register R4, is the destination. The second operand,<br>; Working Register R7, is the source. The contents of R7 is<br>; written into R4.                                                              |

| LD 234H, #%01 | ; Another Load (LD) instruction with two operands.<br>; The first operand, Extended Mode Register Address 234H,<br>; identifies the destination. The second operand, Immediate Data<br>; value 01H, is the source. The value 01H is written into the<br>; Register at address 234H. |

# Assembly Language Syntax

For proper instruction execution, eZ8 CPU assembly language syntax requires that the operands be written as 'destination, source'. After assembly, the object code usually has the operands in the order 'source, destination', but ordering is opcode-dependent. The following instruction examples illustrate the format of some basic assembly instructions and the resulting object code produced by the assembler. This binary format must be followed if manual program coding is preferred or if you intend to implement your own assembler.

**Example 1.** If the contents of registers 43H and 08H are added and the result is stored in 43H, the assembly syntax and resulting object code is:

| Assembly Language Code | ADD | 43H, | 08H | (ADD dst, src) |

|------------------------|-----|------|-----|----------------|

| Object Code            | 04  | 08   | 43  | (OPC src, dst) |

**Example 2.** In general, when an instruction format requires an 8-bit register address, that address can specify any register location in the range 0–255 or, using Escaped Mode Addressing, a Working Register R0–R15. If the contents of Register 43H and Working Register R8 are added and the result is stored in 43H, the assembly syntax and resulting object code is:

| Assembly Language Code | ADD | 43H, | R8 | (ADD dst, src) |

|------------------------|-----|------|----|----------------|

| Object Code            | 04  | E8   | 43 | (OPC src, dst) |

|                                                        | V <sub>DE</sub>                                                                                                                                                                                          | ) = 2.7 V to 3                                                                                                                                                                                                      | 3.6 V                                                                                                                                                                                                                                              |                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                 |  |  |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Parameter                                              | Typical <sup>1</sup>                                                                                                                                                                                     |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                    | Units                                                                                                                                                                                            | Conditions                                                                                                                                                                                                                                                                                                                      |  |  |

| ADC Internal Ref-<br>erence Supply Cur-<br>rent        | 0                                                                                                                                                                                                        |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                    | μA                                                                                                                                                                                               | See Note 4.                                                                                                                                                                                                                                                                                                                     |  |  |

| Comparator sup-<br>ply Current                         | 150                                                                                                                                                                                                      | 180                                                                                                                                                                                                                 | 190                                                                                                                                                                                                                                                | μA                                                                                                                                                                                               | See Note 4.                                                                                                                                                                                                                                                                                                                     |  |  |

| Low-Power Opera-<br>tional Amplifier<br>Supply Current | 3                                                                                                                                                                                                        | 5                                                                                                                                                                                                                   | 5                                                                                                                                                                                                                                                  | μA                                                                                                                                                                                               | Driving a high-impedance load                                                                                                                                                                                                                                                                                                   |  |  |

| Temperature Sen-<br>sor Supply Current                 | 60                                                                                                                                                                                                       |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                    | μA                                                                                                                                                                                               | See Note 4.                                                                                                                                                                                                                                                                                                                     |  |  |

| Band Gap Supply                                        | 320                                                                                                                                                                                                      | 480                                                                                                                                                                                                                 | 500                                                                                                                                                                                                                                                | μA                                                                                                                                                                                               | For 20-/28-pin devices.                                                                                                                                                                                                                                                                                                         |  |  |

| Current                                                |                                                                                                                                                                                                          |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                    |                                                                                                                                                                                                  | For 8-pin devices.                                                                                                                                                                                                                                                                                                              |  |  |

|                                                        | ADC Internal Ref-<br>erence Supply Cur-<br>rent<br>Comparator sup-<br>ply Current<br>Low-Power Opera-<br>tional Amplifier<br>Supply Current<br>Temperature Sen-<br>sor Supply Current<br>Band Gap Supply | ParameterTypical1ADC Internal Ref-<br>erence Supply Cur-<br>rent0Comparator sup-<br>ply Current150Low-Power Opera-<br>tional Amplifier<br>Supply Current3Temperature Sen-<br>sor Supply Current60Band Gap Supply320 | ParameterTypical1Maximum<br>Std Temp2ADC Internal Ref-<br>erence Supply Cur-<br>rent060Comparator sup-<br>ply Current150180Low-Power Opera-<br>tional Amplifier<br>Supply Current35Temperature Sen-<br>sor Supply Current6060Band Gap Supply320480 | ADC Internal Ref-<br>erence Supply Cur-<br>rent<br>Comparator sup-<br>ply Current<br>Low-Power Opera-<br>Supply Current<br>Temperature Sen-<br>sor Supply Current<br>Band Gap Supply 320 480 500 | ParameterTypical <sup>1</sup> Maximum<br>Std Temp <sup>2</sup> Maximum<br>Ext Temp <sup>3</sup> UnitsADC Internal Ref-<br>erence Supply Cur-<br>rent0μAComparator sup-<br>ply Current150180190μALow-Power Opera-<br>tional Amplifier<br>Supply Current355μATemperature Sen-<br>sor Supply Current60μABand Gap Supply320480500μA |  |  |

#### Table 132. Power Consumption (Continued)

Notes:

1. Typical conditions are defined as  $V_{DD} = 3.3 V$  and  $+30^{\circ}C$ .

2. Standard temperature is defined as  $T_A = 0^{\circ}C$  to +70°C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

3. Extended temperature is defined as  $T_A = -40^{\circ}$ C to +105°C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

4. For this block to operate, the bandgap circuit is automatically turned on and must be added to the total supply current. This bandgap current is only added once, regardless of how many peripherals are using it.

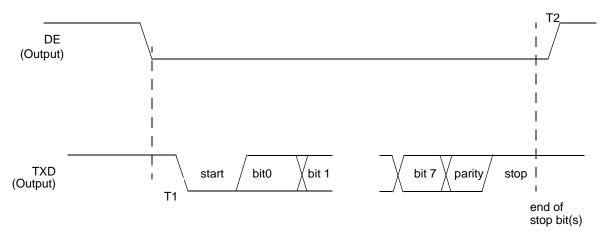

Figure 38 and Table 147 provide timing information for UART pins for the case where CTS is not used for flow control. DE asserts after the Transmit Data Register has been written. DE remains asserted for multiple characters as long as the Transmit Data Register is written with the next character before the current character has completed.

| Table 147 | UART T | imina Wit | hout CTS |

|-----------|--------|-----------|----------|

|           |        |           |          |

|                |                                                                        | Delay (ns)                 |            |  |  |  |

|----------------|------------------------------------------------------------------------|----------------------------|------------|--|--|--|

| Parameter      | Abbreviation                                                           | Minimum                    | Maximum    |  |  |  |

| UART           |                                                                        |                            |            |  |  |  |

| T <sub>1</sub> | DE assertion to TXD falling edge (start bit) delay                     | 1 * X <sub>IN</sub> period | 1 bit time |  |  |  |

| T <sub>2</sub> | End of Stop Bit(s) to DE deassertion delay (Tx Data Register is empty) | ± 5                        |            |  |  |  |

254

|                        | Flash | RAM     | NVDS    | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description |

|------------------------|-------|---------|---------|-----------|------------|---------------------|---------------------|----------------|------------|--------------------|-------------|

| Z8 Encore! XP F082A Se | eries | Develo  | pment   | Kit       |            |                     |                     |                |            |                    |             |

| Z8F08A28100KITG        |       | Z8 Enco | ore! XP | F082/     | A Ser      | ies 2               | 8-Pin               | Dev            | elopn      | nent K             | it          |

| Z8F04A28100KITG        |       | Z8 Enco | ore! XP | F042/     | A Ser      | ies 2               | 8-Pin               | Dev            | elopn      | nent K             | it          |

| Z8F04A08100KITG        |       | Z8 Enco | ore! XP | F042/     | A Ser      | ies 8               | -Pin l              | Deve           | opme       | ent Kit            |             |

| ZUSBSC00100ZACG        |       | USB Sn  | nart Ca | ble Ac    | cess       | ory K               | it                  |                |            |                    |             |

| ZUSBOPTSC01ZACG        |       | USB Op  | to-Isol | ated S    | mart       | Cabl                | e Aco               | cesso          | ry Kit     |                    |             |

| ZENETSC0100ZACG        |       | Etherne | t Smar  | t Cable   | e Acc      | esso                | ry Kit              |                |            |                    |             |

### Table 148. Z8 Encore! XP F082A Series Ordering Matrix