#### Zilog - Z8F012AQB020SG Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                       |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 6                                                            |

| Program Memory Size        | 1KB (1K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 16 x 8                                                       |

| RAM Size                   | 256 x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 4x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | 0°C ~ 70°C (TA)                                              |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 8-VDFN Exposed Pad                                           |

| Supplier Device Package    | 8-QFN (5x6)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f012aqb020sg    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Pin Description**

The Z8 Encore! XP F082A Series products are available in a variety of packages styles and pin configurations. This chapter describes the signals and available pin configurations for each of the package styles. For information about physical package specifications, see the <u>Packaging</u> chapter on page 245.

## **Available Packages**

The following package styles are available for each device in the Z8 Encore! XP F082A Series product line:

- SOIC: 8-, 20- and 28-pin

- PDIP: 8-, 20- and 28-pin

- SSOP: 20- and 28- pin

- QFN 8-pin (MLF-S, a QFN-style package with an 8-pin SOIC footprint)

In addition, the Z8 Encore! XP F082A Series devices are available both with and without advanced analog capability (ADC, temperature sensor and op amp). Devices Z8F082A, Z8F042A, Z8F022A and Z8F012A contain the advanced analog, while devices Z8F081A, Z8F041A, Z8F021A and Z8F011A do not have the advanced analog capability.

## **Pin Configurations**

Figure 2 through Figure 4 display the pin configurations for all the packages available in the Z8 Encore! XP F082A Series. See <u>Table 2</u> on page 10 for a description of the signals. The analog input alternate functions (ANA*x*) are not available on the Z8F081A, Z8F041A, Z8F021A and Z8F011A devices. The analog supply pins (AV<sub>DD</sub> and AV<sub>SS</sub>) are also not available on these parts and are replaced by PB6 and PB7.

At reset, all Port A, B and C pins default to an input state. In addition, any alternate functionality is not enabled, so the pins function as general purpose input ports until programmed otherwise. At powerup, the PD0 pin defaults to the **RESET** alternate function.

The pin configurations listed are preliminary and subject to change based on manufacturing limitations.

#### 15

# **Address Space**

The eZ8 CPU can access the following three distinct address spaces:

- The Register File contains addresses for the general-purpose registers and the eZ8 CPU, peripheral and general-purpose I/O port control registers.

- The Program Memory contains addresses for all memory locations having executable code and/or data.

- The Data Memory contains addresses for all memory locations that contain data only.

These three address spaces are covered briefly in the following subsections. For more information about eZ8 CPU and its address space, refer to the <u>eZ8 CPU Core User Manual</u> (<u>UM0128</u>), which is available for download on <u>www.zilog.com</u>.

## **Register File**

The Register File address space in the Z8 Encore! MCU is 4 KB (4096 bytes). The Register File is composed of two sections: control registers and general-purpose registers. When instructions are executed, registers defined as sources are read and registers defined as destinations are written. The architecture of the eZ8 CPU allows all general-purpose registers to function as accumulators, address pointers, index registers, stack areas, or scratch pad memory.

The upper 256 bytes of the 4 KB Register File address space are reserved for control of the eZ8 CPU, the on-chip peripherals and the I/O ports. These registers are located at addresses from F00H to FFFH. Some of the addresses within the 256 B control register section are reserved (unavailable). Reading from a reserved Register File address returns an undefined value. Writing to reserved Register File addresses is not recommended and can produce unpredictable results.

The on-chip RAM always begins at address 000H in the Register File address space. The Z8 Encore!  $XP^{TM}$  F082A Series devices contain 256 B to 1KB of on-chip RAM. Reading from Register File addresses outside the available RAM addresses (and not within the control register address space) returns an undefined value. Writing to these Register File addresses produces no effect.

## **Program Memory**

The eZ8 CPU supports 64 KB of Program Memory address space. The Z8 Encore! XP F082A Series devices contain 1 KB to 8KB of on-chip Flash memory in the Program Memory address space, depending on the device. Reading from Program Memory

addresses outside the available Flash memory addresses returns FFH. Writing to these unimplemented Program Memory addresses produces no effect. Table 5 describes the Program Memory Maps for the Z8 Encore! XP F082A Series products.

| Program Memory Address (Hex) | Function                     |

|------------------------------|------------------------------|

| Z8F082A and Z8F081A Products |                              |

| 0000–0001                    | Flash Option Bits            |

| 0002–0003                    | Reset Vector                 |

| 0004–0005                    | WDT Interrupt Vector         |

| 0006–0007                    | Illegal Instruction Trap     |

| 0008–0037                    | Interrupt Vectors*           |

| 0038–0039                    | Reserved                     |

| 003A-003D                    | Oscillator Fail Trap Vectors |

| 003E-1FFF                    | Program Memory               |

| Z8F042A and Z8F041A Products |                              |

| 0000–0001                    | Flash Option Bits            |

| 0002–0003                    | Reset Vector                 |

| 0004–0005                    | WDT Interrupt Vector         |

| 0006–0007                    | Illegal Instruction Trap     |

| 0008–0037                    | Interrupt Vectors*           |

| 0038–0039                    | Reserved                     |

| 003A-003D                    | Oscillator Fail Trap Vectors |

| 003E-0FFF                    | Program Memory               |

| Z8F022A and Z8F021A Products |                              |

| 0000–0001                    | Flash Option Bits            |

| 0002–0003                    | Reset Vector                 |

| 0004–0005                    | WDT Interrupt Vector         |

| 0006–0007                    | Illegal Instruction Trap     |

| 0008–0037                    | Interrupt Vectors*           |

| 0038–0039                    | Reserved                     |

| 003A-003D                    | Oscillator Fail Trap Vectors |

| 003E-07FF                    | Program Memory               |

| Z8F012A and Z8F011A Products |                              |

| 0000–0001                    | Flash Option Bits            |

|                              |                              |

#### Table 5. Z8 Encore! XP F082A Series Program Memory Maps

Note: \*See Table 32 on page 56 for a list of the interrupt vectors.

tor address. Following Stop Mode Recovery, the STOP bit in the Reset Status (RSTSTAT) Register is set to 1. Table 10 lists the Stop Mode Recovery sources and resulting actions. The text following provides more detailed information about each of the Stop Mode Recovery sources.

| Operating Mode | Stop Mode Recovery Source                                                   | Action                                                               |  |  |

|----------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------|--|--|

| STOP Mode      | Watchdog Timer time-out when configured for Reset                           | Stop Mode Recovery                                                   |  |  |

|                | Watchdog Timer time-out when configured for interrupt                       | Stop Mode Recovery followed by interrupt (if interrupts are enabled) |  |  |

|                | Data transition on any GPIO port pin enabled as a Stop Mode Recovery source | Stop Mode Recovery                                                   |  |  |

|                | Assertion of external RESET Pin                                             | System Reset                                                         |  |  |

|                | Debug Pin driven Low                                                        | System Reset                                                         |  |  |

#### Table 10. Stop Mode Recovery Sources and Resulting Action

## Stop Mode Recovery Using Watchdog Timer Time-Out

If the Watchdog Timer times out during STOP Mode, the device undergoes a Stop Mode Recovery sequence. In the Reset Status (RSTSTAT) Register, the WDT and STOP bits are set to 1. If the Watchdog Timer is configured to generate an interrupt upon time-out and the Z8 Encore! XP F082A Series device is configured to respond to interrupts, the eZ8 CPU services the Watchdog Timer interrupt request following the normal Stop Mode Recovery sequence.

## Stop Mode Recovery Using a GPIO Port Pin Transition

Each of the GPIO port pins may be configured as a Stop Mode Recovery input source. On any GPIO pin enabled as a Stop Mode Recovery source, a change in the input pin value (from High to Low or from Low to High) initiates Stop Mode Recovery.

• Note: SMR pulses shorter than specified do not trigger a recovery (see <u>Table 135</u> on page 233). In this instance, the STOP bit in the Reset Status (RSTSTAT) Register is set to 1.

**Caution:** In STOP Mode, the GPIO Port Input Data registers (PxIN) are disabled. The Port Input Data registers record the Port transition only if the signal stays on the Port pin through the end of the Stop Mode Recovery delay. As a result, short pulses on the Port pin can initiate Stop Mode Recovery without being written to the Port Input Data Register or

| Port                | Pin | Mnemonic                           | Alternate Function Description            | Alternate Function<br>Set Register AFS1 |

|---------------------|-----|------------------------------------|-------------------------------------------|-----------------------------------------|

| Port C <sup>5</sup> | PC0 | Reserved                           |                                           | AFS1[0]: 0                              |

|                     |     | ANA4/CINP                          | ADC or Comparator Input                   | AFS1[0]: 1                              |

|                     | PC1 | Reserved                           |                                           | AFS1[1]: 0                              |

|                     |     | ANA5/CINN                          | ADC or Comparator Input                   | AFS1[1]: 1                              |

|                     | PC2 | Reserved                           |                                           | AFS1[2]: 0                              |

|                     |     | ANA6/V <sub>REF</sub> <sup>4</sup> | ADC Analog Input or ADC Voltage Reference | AFS1[2]: 1                              |

|                     | PC3 | COUT                               | Comparator Output                         | AFS1[3]: 0                              |

|                     |     | Reserved                           |                                           | AFS1[3]: 1                              |

|                     | PC4 | Reserved                           |                                           | AFS1[4]: 0                              |

|                     |     |                                    |                                           | AFS1[4]: 1                              |

|                     | PC5 | Reserved                           |                                           | AFS1[5]: 0                              |

|                     |     |                                    |                                           | AFS1[5]: 1                              |

|                     | PC6 | Reserved                           |                                           | AFS1[6]: 0                              |

|                     |     |                                    |                                           | AFS1[6]: 1                              |

|                     | PC7 | Reserved                           |                                           | AFS1[7]: 0                              |

|                     |     |                                    |                                           | AFS1[7]: 1                              |

| Port D <sup>6</sup> | PD0 | RESET                              | External Reset                            | N/A                                     |

#### Table 15. Port Alternate Function Mapping (Non 8-Pin Parts) (Continued)

Notes:

2. Whether PA0/PA6 takes on the timer input or timer output complement function depends on the timer configuration. See the <u>Timer Pin Signal Operation</u> section on page 84 for details.

Because there are at most two choices of alternate function for any pin of Port B, the Alternate Function Set Register AFS2 is not used to select the function. Alternate function selection must also be enabled. See the <u>Port</u> <u>A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

4. V<sub>REF</sub> is available on PB5 in 28-pin products and on PC2 in 20-pin parts.

Because there are at most two choices of alternate function for any pin of Port C, the Alternate Function Set Register AFS2 is not used to select the function. Alternate function selection must also be enabled. See the <u>Port</u> <u>A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

6. Because there is only a single alternate function for the Port PD0 pin, the Alternate Function Set registers are not implemented for Port D. Enabling alternate function selections automatically enables the associated alternate function. See the Port A–D Alternate Function Subregisters (PxAF) section on page 47 for details.

Because there is only a single alternate function for each Port A pin, the Alternate Function Set registers are not implemented for Port A. Enabling alternate function selections automatically enables the associated alternate function. See the <u>Port A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

delay ensures a time gap between the deassertion of one PWM output to the assertion of its complement.

Observe the following steps for configuring a timer for PWM DUAL OUTPUT Mode and initiating the PWM operation:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for PWM DUAL OUTPUT Mode by writing the TMODE bits in the TxCTL1 Register and the TMODEHI bit in TxCTL0 Register

- Set the prescale value

- Set the initial logic level (High or Low) and PWM High/Low transition for the Timer Output alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H). This only affects the first pass in PWM mode. After the first timer reset in PWM mode, counting always begins at the reset value of 0001H.

- 3. Write to the PWM High and Low Byte registers to set the PWM value.

- 4. Write to the PWM Control Register to set the PWM dead band delay value. The deadband delay must be less than the duration of the positive phase of the PWM signal (as defined by the PWM high and low byte registers). It must also be less than the duration of the negative phase of the PWM signal (as defined by the difference between the PWM registers and the Timer Reload registers).

- 5. Write to the Timer Reload High and Low Byte registers to set the reload value (PWM period). The reload value must be greater than the PWM value.

- 6. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 7. Configure the associated GPIO port pin for the Timer Output and Timer Output Complement alternate functions. The Timer Output Complement function is shared with the Timer Input function for both timers. Setting the timer mode to Dual PWM automatically switches the function from Timer In to Timer Out Complement.

- 8. Write to the Timer Control Register to enable the timer and initiate counting.

The PWM period is represented by the following equation:

PWM Period (s) =  $\frac{\text{Reload Value xPrescale}}{\text{System Clock Frequency (Hz)}}$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, the ONE-SHOT Mode equation determines the first PWM time-out period.

If TPOL is set to 0, the ratio of the PWM output High time to the total period is represented by:

PWM Output High Time Ratio (%) =  $\frac{\text{Reload Value} - \text{PWM Value}}{\text{Reload Value}} \times 100$

If TPOL is set to 1, the ratio of the PWM output High time to the total period is represented by:

PWM Output High Time Ratio (%) =  $\frac{PWM \text{ Value}}{\text{Reload Value}} \times 100$

### **CAPTURE Mode**

In CAPTURE Mode, the current timer count value is recorded when the appropriate external Timer Input transition occurs. The Capture count value is written to the Timer PWM High and Low Byte registers. The timer input is the system clock. The TPOL bit in the Timer Control Register determines if the Capture occurs on a rising edge or a falling edge of the Timer Input signal. When the Capture event occurs, an interrupt is generated and the timer continues counting. The INPCAP bit in TxCTL0 Register is set to indicate the timer interrupt is because of an input capture event.

The timer continues counting up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt and continues counting. The INPCAP bit in TxCTL0 Register clears indicating the timer interrupt is not because of an input capture event.

Observe the following steps for configuring a timer for CAPTURE Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE Mode

- Set the prescale value

- Set the Capture edge (rising or falling) for the Timer Input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. Clear the Timer PWM High and Low Byte registers to 0000H. Clearing these registers allows the software to determine if interrupts were generated by either a capture event or a reload. If the PWM High and Low Byte registers still contain 0000H after the interrupt, the interrupt was generated by a Reload.

- Configure the timer for GATED Mode

- Set the prescale value

- 2. Write to the Timer High and Low Byte registers to set the starting count value. Writing these registers only affects the first pass in GATED Mode. After the first timer reset in GATED Mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. Enable the timer interrupt, if appropriate and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input deassertion and reload events. If appropriate, configure the timer interrupt to be generated only at the input deassertion event or the reload event by setting TICONFIG field of the TxCTL0 Register.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control Register to enable the timer.

- 7. Assert the Timer Input signal to initiate the counting.

#### CAPTURE/COMPARE Mode

In CAPTURE/COMPARE Mode, the timer begins counting on the first external Timer Input transition. The acceptable transition (rising edge or falling edge) is set by the TPOL bit in the Timer Control Register. The timer input is the system clock.

Every subsequent acceptable transition (after the first) of the Timer Input signal captures the current count value. The Capture value is written to the Timer PWM High and Low Byte registers. When the Capture event occurs, an interrupt is generated, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL0 Register is set to indicate the timer interrupt is caused by an input capture event.

If no Capture event occurs, the timer counts up to the 16-bit Compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the Compare value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL0 Register is cleared to indicate the timer interrupt is not because of an input capture event.

Observe the following steps for configuring a timer for CAPTURE/COMPARE Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE/COMPARE Mode

- Set the prescale value

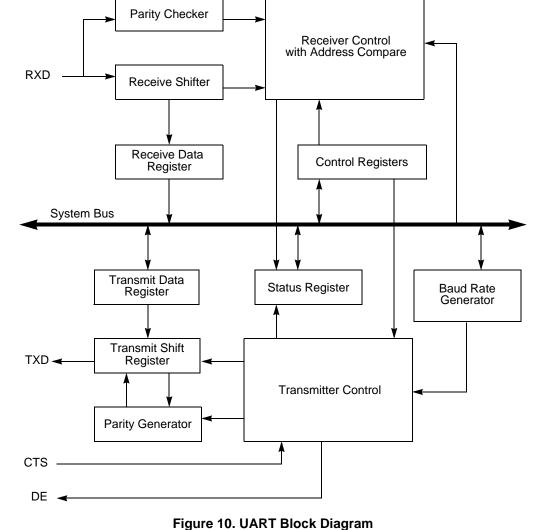

first. An even or odd parity bit can be added to the data stream. Each character begins with an active Low start bit and ends with either 1 or 2 active High stop bits. Figures 11 and 12 display the asynchronous data format employed by the UART without parity and with parity, respectively.

| Bit   | Description (Continued)                                                                                         |

|-------|-----------------------------------------------------------------------------------------------------------------|

| [2:1] | Reserved                                                                                                        |

|       | These bits are reserved and must be undefined.                                                                  |

| [0]   | Overflow Status                                                                                                 |

| OVF   | 0 = A hardware overflow did not occur in the ADC for the current sample.                                        |

|       | 1= A hardware overflow did occur in the ADC for the current sample, therefore the current<br>sample is invalid. |

The following code example illustrates how to safely enable the comparator:

```

di

ld cmp0, r0 ; load some new configuration

nop

nop        ; wait for output to settle

clr irq0 ; clear any spurious interrupts pending

ei

```

# **Comparator Control Register Definition**

The Comparator Control Register (CMP0) configures the comparator inputs and sets the value of the internal voltage reference.

| Bit     | 7      | 6      | 5   | 4   | 1                                       | 0   |  |  |  |  |

|---------|--------|--------|-----|-----|-----------------------------------------|-----|--|--|--|--|

| Field   | INPSEL | INNSEL |     | REF | Reserved (20-/28-pin)<br>REFLVL (8-pin) |     |  |  |  |  |

| RESET   | 0      | 0      | 0   | 1   | 0                                       | 0   |  |  |  |  |

| R/W     | R/W    | R/W    | R/W | R/W | R/W                                     | R/W |  |  |  |  |

| Address |        | F90H   |     |     |                                         |     |  |  |  |  |

Table 77. Comparator Control Register (CMP0)

| Bit    | Description                                                                                                                                                            |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]    | Signal Select for Positive Input                                                                                                                                       |

| INPSEL | 0 = GPIO pin used as positive comparator input.                                                                                                                        |

|        | <ol> <li>Temperature sensor used as positive comparator input.</li> </ol>                                                                                              |

| [6]    | Signal Select for Negative Input                                                                                                                                       |

| INNSEL | <ul> <li>0 = Internal reference disabled, GPIO pin used as negative comparator input.</li> <li>1 = Internal reference enabled as negative comparator input.</li> </ul> |

# **Temperature Sensor**

The on-chip Temperature Sensor allows you to measure temperature on the die with either the on-board ADC or on-board comparator. This block is factory calibrated for in-circuit software correction. Uncalibrated accuracy is significantly worse, therefore the temperature sensor is not recommended for uncalibrated use.

# **Temperature Sensor Operation**

The on-chip temperature sensor is a Proportional to Absolute Temperature (PTAT) topology. A pair of Flash option bytes contain the calibration data. The temperature sensor can be disabled by a bit in the <u>Power Control Register 0</u> section on page 33 to reduce power consumption.

The temperature sensor can be directly read by the ADC to determine the absolute value of its output. The temperature sensor output is also available as an input to the comparator for threshold type measurement determination. The accuracy of the sensor when used with the comparator is substantially less than when measured by the ADC.

If the temperature sensor is routed to the ADC, the ADC must be configured in unity-gain buffered mode (for details, see the <u>Input Buffer Stage</u> section on page 133). The value read back from the ADC is a signed number, although it is always positive.

The sensor is factory-trimmed through the ADC using the external 2.0 V reference. Unless the sensor is retrimmed for use with a different reference, it is most accurate when used with the external 2.0 V reference.

Because this sensor is an on-chip sensor, Zilog recommends that the user account for the difference between ambient and die temperature when inferring ambient temperature conditions.

During normal operation, the die undergoes heating that causes a mismatch between the ambient temperature and that measured by the sensor. For best results, the Z8 Encore! XP device must be placed into STOP Mode for sufficient time such that the die and ambient temperatures converge (this time is dependent on the thermal design of the system). The temperature sensor measurement must then be made immediately after recovery from STOP Mode.

The following equation defines the transfer function between the temperature sensor output voltage and the die temperature. This is needed for comparator threshold measurements.

$V = 0.01 \times T + 0.65$

| 8KB Flash<br>Program Memor | y<br>Addresses (hex)<br>T 1FFF | 4KB Flash<br>Program Memory | /<br>Addresses (hex)<br>1 0FFF | 2KB Flash<br>Program Memory<br>Addresse | s (hex)                  |

|----------------------------|--------------------------------|-----------------------------|--------------------------------|-----------------------------------------|--------------------------|

| Sector 7                   | 1C00                           | Sector 7                    | 0E00                           | Sector 3                                | 07FF<br>0600<br>05FF     |

| Sector 6                   | 1BFF                           | Sector 6                    | 0DFF                           |                                         | 0400<br>03FF             |

|                            | 1800<br>17FF                   | October 5                   | 0C00<br>0BFF                   | Sector 1                                | 0200<br>01FF             |

| Sector 5                   | 1400<br>13FF                   | Sector 5                    | 0A00<br>09FF                   | Sector 0                                | 0000                     |

| Sector 4                   | 1000                           | Sector 4                    | 0800                           |                                         |                          |

| Sector 3                   | 0FFF<br>0C00                   | Sector 3                    | 07FF<br>0600                   | 1 KB Flash<br>Program Memory            | (1 )                     |

| Sector 2                   | 0BFF<br>0800                   | Sector 2                    | 05FF<br>0400                   | Addresse<br>Sector 1                    | es (nex)<br>03FF<br>0200 |

| Sector 1                   | 07FF<br>0400                   | Sector 1                    | 03FF<br>0200                   | Sector 0                                | 01FF                     |

| Sector 0                   | 03FF<br>0000                   | Sector 0                    | 01FF<br>0000                   |                                         |                          |

Figure 21. Flash Memory Arrangement

# **Flash Information Area**

The Flash information area is separate from Program Memory and is mapped to the address range FE00H to FFFFH. This area is readable but cannot be erased or overwritten. Factory trim values for the analog peripherals are stored here. Factory calibration data for the ADC is also stored here.

# Operation

The Flash Controller programs and erases Flash memory. The Flash Controller provides the proper Flash controls and timing for Byte Programming, Page Erase and Mass Erase of Flash memory.

The Flash Controller contains several protection mechanisms to prevent accidental programming or erasure. These mechanism operate on the page, sector and full-memory levels.

## Flash Operation Timing Using the Flash Frequency Registers

Before performing either a program or erase operation on Flash memory, you must first configure the Flash Frequency High and Low Byte registers. The Flash Frequency registers allow programming and erasing of the Flash with system clock frequencies ranging from 32kHz (32768Hz) through 20MHz.

The Flash Frequency High and Low Byte registers combine to form a 16-bit value, FFREQ, to control timing for Flash program and erase operations. The 16-bit binary Flash Frequency value must contain the system clock frequency (in kHz). This value is calculated using the following equation:

$FFREQ[15:0] = \frac{System Clock Frequency (Hz)}{1000}$

**Caution:** Flash programming and erasure are not supported for system clock frequencies below 32kHz (32768Hz) or above 20MHz. The Flash Frequency High and Low Byte registers must be loaded with the correct value to ensure operation of the Z8 Encore! XP F082A Series devices.

## Flash Code Protection Against External Access

The user code contained within the Flash memory can be protected against external access by the on-chip debugger. Programming the FRP Flash option bit prevents reading of the user code with the On-Chip Debugger. See the <u>Flash Option Bits</u> chapter on page 159 and the <u>On-Chip Debugger</u> chapter on page 180 for more information.

# Flash Code Protection Against Accidental Program and Erasure

The Z8 Encore! XP F082A Series provides several levels of protection against accidental program and erasure of the Flash memory contents. This protection is provided by a combination of the Flash option bits, the register locking mechanism, the page select redundancy and the sector level protection control of the Flash Controller.

#### Flash Code Protection Using the Flash Option Bits

The FRP and FWP Flash option bits combine to provide three levels of Flash Program Memory protection, as shown in Table 79. See the <u>Flash Option Bits</u> chapter on page 159 for more information.

enabled, the OCD ignores the BRK signal and the BRK instruction operates as an NOP instruction.

#### **Breakpoints in Flash Memory**

The BRK instruction is opcode 00H, which corresponds to the fully programmed state of a byte in Flash memory. To implement a Breakpoint, write 00H to the required break address, overwriting the current instruction. To remove a Breakpoint, the corresponding page of Flash memory must be erased and reprogrammed with the original data.

### **Runtime Counter**

The On-Chip Debugger contains a 16-bit Runtime Counter. It counts system clock cycles between Breakpoints. The counter starts counting when the On-Chip Debugger leaves DEBUG Mode and stops counting when it enters DEBUG Mode again or when it reaches the maximum count of FFFFH.

## **On-Chip Debugger Commands**

The host communicates to the on-chip debugger by sending OCD commands using the DBG interface. During normal operation, only a subset of the OCD commands are available. In DEBUG Mode, all OCD commands become available unless the user code and control registers are protected by programming the Flash Read Protect Option bit (FRP). The Flash Read Protect Option bit prevents the code in memory from being read out of the Z8 Encore! XP F082A Series device. When this option is enabled, several of the OCD commands are disabled. See Table 109.

<u>Table 110</u> on page 191 is a summary of the on-chip debugger commands. Each OCD command is described in further detail in the bulleted list following this table. Table 110 also indicates those commands that operate when the device is not in DEBUG Mode (normal operation) and those commands that are disabled by programming the Flash Read Protect Option bit.

| Debug Command              | Command<br>Byte | Enabled when<br>Not in DEBUG<br>Mode? | Disabled by Flash Read Protect<br>Option Bit |

|----------------------------|-----------------|---------------------------------------|----------------------------------------------|

| Read OCD Revision          | 00H             | Yes                                   | -                                            |

| Reserved                   | 01H             | _                                     | -                                            |

| Read OCD Status Register   | 02H             | Yes                                   | -                                            |

| Read Runtime Counter       | 03H             | -                                     | -                                            |

| Write OCD Control Register | 04H             | Yes                                   | Cannot clear DBGMODE bit.                    |

| Read OCD Control Register  | 05H             | Yes                                   | -                                            |

| Table 109. Debug Command Enable/Disable | Table 109. | Debug | Command | Enable/Disable |

|-----------------------------------------|------------|-------|---------|----------------|

|-----------------------------------------|------------|-------|---------|----------------|

DBG  $\leftarrow$  Size[15:8] DBG  $\leftarrow$  Size[7:0] DBG  $\leftarrow$  1-65536 data bytes

**Read Data Memory (0DH).** The Read Data Memory command reads from Data Memory. This command is equivalent to the LDE and LDEI instructions. Data can be read 1 to 65536 bytes at a time (65536 bytes can be read by setting size to 0). If the device is not in DEBUG Mode, this command returns FFH for the data.

```

DBG \leftarrow 0DH

DBG \leftarrow Data Memory Address[15:8]

DBG \leftarrow Data Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-65536 data bytes

```

**Read Program Memory CRC (0EH).** The Read Program Memory CRC command computes and returns the Cyclic Redundancy Check (CRC) of Program Memory using the 16bit CRC-CCITT polynomial. If the device is not in DEBUG Mode, this command returns FFFFH for the CRC value. Unlike most other OCD Read commands, there is a delay from issuing of the command until the OCD returns the data. The OCD reads the Program Memory, calculates the CRC value and returns the result. The delay is a function of the Program Memory size and is approximately equal to the system clock period multiplied by the number of bytes in the Program Memory.

DBG  $\leftarrow$  0EH DBG  $\rightarrow$  CRC[15:8] DBG  $\rightarrow$  CRC[7:0]

**Step Instruction (10H).** The Step Instruction command steps one assembly instruction at the current Program Counter (PC) location. If the device is not in DEBUG Mode or the Flash Read Protect Option bit is enabled, the OCD ignores this command.

DBG  $\leftarrow$  10H

**Stuff Instruction (11H).** The Stuff Instruction command steps one assembly instruction and allows specification of the first byte of the instruction. The remaining 0-4 bytes of the instruction are read from Program Memory. This command is useful for stepping over instructions where the first byte of the instruction has been overwritten by a Breakpoint. If the device is not in DEBUG Mode or the Flash Read Protect Option bit is enabled, the OCD ignores this command.

DBG ← 11H DBG ← opcode[7:0]

**Execute Instruction (12H).** The Execute Instruction command allows sending an entire instruction to be executed to the eZ8 CPU. This command can also step over Breakpoints. The number of bytes to send for the instruction depends on the opcode. If the device is not

214

| Assembly      |                        |     | ress<br>ode | _ Opcode(s) |   |   | Fla | ags |   |   | Fetch<br>Cycle | Instr.<br>Cycle |

|---------------|------------------------|-----|-------------|-------------|---|---|-----|-----|---|---|----------------|-----------------|

| Mnemonic      | Symbolic Operation     | dst | src         | (Hex)       | С | Ζ | S   | ۷   | D | Н | S              | S               |

| CALL dst      | $SP \leftarrow SP - 2$ | IRR |             | D4          | _ | _ | _   | _   | - | _ | 2              | 6               |

|               | @SP ← PC<br>PC ← dst   | DA  |             | D6          | - |   |     |     |   |   | 3              | 3               |

| CCF           | $C \leftarrow \sim C$  |     |             | EF          | * | - | _   | -   | - |   | 1              | 2               |

| CLR dst       | dst ← 00H              | R   |             | B0          | - | _ | _   | -   | _ | _ | 2              | 2               |

|               |                        | IR  |             | B1          | - |   |     |     |   |   | 2              | 3               |

| COM dst       | dst ← ~dst             | R   |             | 60          | _ | * | *   | 0   | _ | _ | 2              | 2               |

|               |                        | IR  |             | 61          | - |   |     |     |   |   | 2              | 3               |

| CP dst, src   | dst - src              | r   | r           | A2          | * | * | *   | *   | _ | _ | 2              | 3               |

|               |                        | r   | Ir          | A3          | - |   |     |     |   |   | 2              | 4               |

|               |                        | R   | R           | A4          | - |   |     |     |   |   | 3              | 3               |

|               |                        | R   | IR          | A5          | - |   |     |     |   |   | 3              | 4               |

|               |                        | R   | IM          | A6          | - |   |     |     |   |   | 3              | 3               |

|               |                        | IR  | IM          | A7          | - |   |     |     |   |   | 3              | 4               |

| CPC dst, src  | dst - src - C          | r   | r           | 1F A2       | * | * | *   | *   | _ | _ | 3              | 3               |

|               |                        | r   | Ir          | 1F A3       | - |   |     |     |   |   | 3              | 4               |

|               |                        | R   | R           | 1F A4       | - |   |     |     |   |   | 4              | 3               |

|               |                        | R   | IR          | 1F A5       | - |   |     |     |   |   | 4              | 4               |

|               |                        | R   | IM          | 1F A6       | - |   |     |     |   |   | 4              | 3               |

|               |                        | IR  | IM          | 1F A7       | - |   |     |     |   |   | 4              | 4               |

| CPCX dst, src | dst - src - C          | ER  | ER          | 1F A8       | * | * | *   | *   | _ | _ | 5              | 3               |

|               |                        | ER  | IM          | 1F A9       | - |   |     |     |   |   | 5              | 3               |

| CPX dst, src  | dst - src              | ER  | ER          | A8          | * | * | *   | *   | _ | _ | 4              | 3               |

|               |                        | ER  | IM          | A9          | - |   |     |     |   |   | 4              | 3               |

#### Table 128. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 =Set to 1.

| Abbreviation | Description                         | Abbreviation                                      | Description             |

|--------------|-------------------------------------|---------------------------------------------------|-------------------------|

| b            | Bit position.                       | IRR                                               | Indirect register pair. |

| СС           | Condition code.                     | р                                                 | Polarity (0 or 1).      |

| Х            | 8-bit signed index or displacement. | r                                                 | 4-bit working register. |

| DA           | Destination address.                | R                                                 | 8-bit register.         |

| ER           | Extended addressing register.       | r1, R1, Ir1, Irr1,<br>IR1, rr1, RR1,<br>IRR1, ER1 | Destination address.    |

| IM           | Immediate data value.               | r2, R2, Ir2, Irr2,<br>IR2, rr2, RR2,<br>IRR2, ER2 | Source address.         |

| Ir           | Indirect working register.          | RA                                                | Relative.               |

| IR           | Indirect register.                  | rr                                                | Working register pair.  |

| Irr          | Indirect working register pair.     | RR                                                | Register pair.          |

#### Table 129. Opcode Map Abbreviations

## General Purpose I/O Port Output Timing

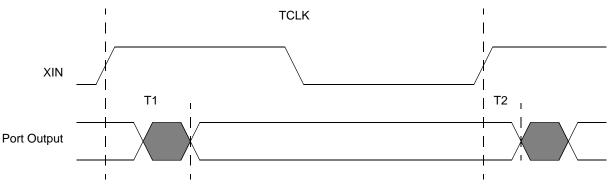

Figure 35 and Table 144 provide timing information for GPIO port pins.

| Figure 35 | . GPIO | Port | Output | Timing |

|-----------|--------|------|--------|--------|

|-----------|--------|------|--------|--------|

|                |                                                 | Delay (ns) |         |

|----------------|-------------------------------------------------|------------|---------|

| Parameter      | Abbreviation                                    | Minimum    | Maximum |

| GPIO port pi   | ns                                              |            |         |

| T <sub>1</sub> | X <sub>IN</sub> Rise to Port Output Valid Delay | -          | 15      |

| T <sub>2</sub> | X <sub>IN</sub> Rise to Port Output Hold Time   | 2          | _       |

#### Table 144. GPIO Port Output Timing

# G

GATED mode 88 general-purpose I/O 36 GPIO 6.36 alternate functions 37 architecture 37 control register definitions 44 input data sample timing 240 interrupts 44 port A-C pull-up enable sub-registers 50, 51 port A-H address registers 45 port A-H alternate function sub-registers 47 port A-H control registers 46 port A-H data direction sub-registers 46 port A-H high drive enable sub-registers 48 port A-H input data registers 52 port A-H output control sub-registers 47 port A-H output data registers 52, 53 port A-H stop mode recovery sub-registers 49 port availability by device 36 port input timing 240 port output timing 241

## Η

H 207 HALT 209 halt mode 33, 209 hexadecimal number prefix/suffix 207

## I

I2C 6 IM 206 immediate data 206 immediate operand prefix 207 INC 208 increment 208 increment word 208 INCW 208 indexed 207 indirect address prefix 207 indirect register 206 indirect register pair 206 indirect working register 206 indirect working register pair 206 infrared encoder/decoder (IrDA) 120 Instruction Set 204 instruction set, eZ8 CPU 204 instructions ADC 208 **ADCX 208** ADD 208 **ADDX 208** AND 210 **ANDX 210** arithmetic 208 **BCLR 209 BIT 209** bit manipulation 209 block transfer 209 **BRK 211 BSET 209** BSWAP 209, 211 BTJ 211 BTJNZ 211 **BTJZ 211** CALL 211 **CCF 209** CLR 210 COM 210 **CP 208 CPC 208 CPCX 208** CPU control 209 **CPX 208** DA 208 **DEC 208 DECW 208** DI 209 **DJNZ 211** EI 209 **HALT 209 INC 208 INCW 208 IRET 211**

JP 211

258