# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 17                                                           |

| Program Memory Size        | 1KB (1K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 16 x 8                                                       |

| RAM Size                   | 256 x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 7x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | 0°C ~ 70°C (TA)                                              |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                               |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f012ash020sg    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

7

warning signal. The  $\overline{\text{RESET}}$  pin is bidirectional, that is, it functions as reset source and as a reset indicator.

addresses outside the available Flash memory addresses returns FFH. Writing to these unimplemented Program Memory addresses produces no effect. Table 5 describes the Program Memory Maps for the Z8 Encore! XP F082A Series products.

| Program Memory Address (Hex) | Function                     |

|------------------------------|------------------------------|

| Z8F082A and Z8F081A Products |                              |

| 0000–0001                    | Flash Option Bits            |

| 0002–0003                    | Reset Vector                 |

| 0004–0005                    | WDT Interrupt Vector         |

| 0006–0007                    | Illegal Instruction Trap     |

| 0008–0037                    | Interrupt Vectors*           |

| 0038–0039                    | Reserved                     |

| 003A-003D                    | Oscillator Fail Trap Vectors |

| 003E-1FFF                    | Program Memory               |

| Z8F042A and Z8F041A Products |                              |

| 0000–0001                    | Flash Option Bits            |

| 0002–0003                    | Reset Vector                 |

| 0004–0005                    | WDT Interrupt Vector         |

| 0006–0007                    | Illegal Instruction Trap     |

| 0008–0037                    | Interrupt Vectors*           |

| 0038–0039                    | Reserved                     |

| 003A-003D                    | Oscillator Fail Trap Vectors |

| 003E-0FFF                    | Program Memory               |

| Z8F022A and Z8F021A Products |                              |

| 0000–0001                    | Flash Option Bits            |

| 0002–0003                    | Reset Vector                 |

| 0004–0005                    | WDT Interrupt Vector         |

| 0006–0007                    | Illegal Instruction Trap     |

| 0008–0037                    | Interrupt Vectors*           |

| 0038–0039                    | Reserved                     |

| 003A-003D                    | Oscillator Fail Trap Vectors |

| 003E-07FF                    | Program Memory               |

| Z8F012A and Z8F011A Products |                              |

| 0000–0001                    | Flash Option Bits            |

|                              |                              |

### Table 5. Z8 Encore! XP F082A Series Program Memory Maps

Note: \*See Table 32 on page 56 for a list of the interrupt vectors.

| Address (Hex)    | Register Description                 | Mnemonic      | Reset (Hex) | Page       |

|------------------|--------------------------------------|---------------|-------------|------------|

| Timer 1          |                                      |               |             |            |

| F08              | Timer 1 High Byte                    | T1H           | 00          | <u>90</u>  |

| F09              | Timer 1 Low Byte                     | T1L           | 01          | <u>90</u>  |

| F0A              | Timer 1 Reload High Byte             | T1RH          | FF          | <u>91</u>  |

| Timer 1 (cont'd) |                                      |               |             |            |

| F0B              | Timer 1 Reload Low Byte              | T1RL          | FF          | <u>91</u>  |

| F0C              | Timer 1 PWM High Byte                | T1PWMH        | 00          | <u>92</u>  |

| F0D              | Timer 1 PWM Low Byte                 | T1PWML        | 00          | <u>92</u>  |

| F0E              | Timer 1 Control 0                    | T1CTL0        | 00          | <u>85</u>  |

| F0F              | Timer 1 Control 1                    | T1CTL1        | 00          | <u>86</u>  |

| F10–F6F          | Reserved                             | —             | XX          |            |

| UART             |                                      |               |             |            |

| F40              | UART Transmit/Receive Data registers | TXD, RXD      | XX          | <u>115</u> |

| F41              | UART Status 0 Register               | U0STAT0       | 00          | <u>114</u> |

| F42              | UART Control 0 Register              | U0CTL0        | 00          | <u>110</u> |

| F43              | UART Control 1 Register              | U0CTL1        | 00          | <u>110</u> |

| F44              | UART Status 1 Register               | U0STAT1       | 00          | <u>115</u> |

| F45              | UART Address Compare Register        | <b>U0ADDR</b> | 00          | <u>116</u> |

| F46              | UART Baud Rate High Byte Register    | U0BRH         | FF          | <u>117</u> |

| F47              | UART Baud Rate Low Byte Register     | U0BRL         | FF          | <u>117</u> |

| Analog-to-Digita | al Converter (ADC)                   |               |             |            |

| F70              | ADC Control 0                        | ADCCTL0       | 00          | <u>134</u> |

| F71              | ADC Control 1                        | ADCCTL1       | 80          | <u>136</u> |

| F72              | ADC Data High Byte                   | ADCD_H        | XX          | <u>137</u> |

| F73              | ADC Data Low Byte                    | ADCD_L        | XX          | 137        |

| F74–F7F          | Reserved                             |               | XX          |            |

| Low Power Con    | trol                                 |               |             |            |

| F80              | Power Control 0                      | PWRCTL0       | 80          | <u>34</u>  |

| F81              | Reserved                             | —             | XX          |            |

| LED Controller   |                                      |               |             |            |

| F82              | LED Drive Enable                     | LEDEN         | 00          | <u>53</u>  |

| F83              | LED Drive Level High Byte            | LEDLVLH       | 00          | <u>53</u>  |

| F84              | LED Drive Level Low Byte             | LEDLVLL       | 00          | <u>54</u>  |

### Table 7. Register File Address Map (Continued)

1. XX = Undefined.

2. Refer to the eZ8 CPU Core User Manual (UM0128).

| Address (Hex)           | Register Description    | Mnemonic | Reset (Hex) | Page       |

|-------------------------|-------------------------|----------|-------------|------------|

| F85                     | Reserved                | —        | XX          |            |

| <b>Oscillator Contr</b> | ol                      |          |             |            |

| F86                     | Oscillator Control      | OSCCTL   | A0          | <u>196</u> |

| F87–F8F                 | Reserved                | _        | XX          |            |

| Comparator 0            |                         |          |             |            |

| F90                     | Comparator 0 Control    | CMP0     | 14          | <u>141</u> |

| F91–FBF                 | Reserved                | _        | XX          |            |

| Interrupt Contro        | oller                   |          |             |            |

| FC0                     | Interrupt Request 0     | IRQ0     | 00          | <u>60</u>  |

| FC1                     | IRQ0 Enable High Bit    | IRQ0ENH  | 00          | <u>63</u>  |

| FC2                     | IRQ0 Enable Low Bit     | IRQ0ENL  | 00          | <u>63</u>  |

| FC3                     | Interrupt Request 1     | IRQ1     | 00          | <u>61</u>  |

| FC4                     | IRQ1 Enable High Bit    | IRQ1ENH  | 00          | <u>65</u>  |

| FC5                     | IRQ1 Enable Low Bit     | IRQ1ENL  | 00          | <u>65</u>  |

| FC6                     | Interrupt Request 2     | IRQ2     | 00          | <u>62</u>  |

| FC7                     | IRQ2 Enable High Bit    | IRQ2ENH  | 00          | <u>66</u>  |

| FC8                     | IRQ2 Enable Low Bit     | IRQ2ENL  | 00          | <u>67</u>  |

| FC9–FCC                 | Reserved                | —        | XX          |            |

| FCD                     | Interrupt Edge Select   | IRQES    | 00          | <u>68</u>  |

| FCE                     | Shared Interrupt Select | IRQSS    | 00          | <u>68</u>  |

| FCF                     | Interrupt Control       | IRQCTL   | 00          | <u>69</u>  |

| GPIO Port A             |                         |          |             |            |

| FD0                     | Port A Address          | PAADDR   | 00          | <u>44</u>  |

| FD1                     | Port A Control          | PACTL    | 00          | <u>46</u>  |

| FD2                     | Port A Input Data       | PAIN     | XX          | <u>46</u>  |

| FD3                     | Port A Output Data      | PAOUT    | 00          | <u>46</u>  |

| GPIO Port B             |                         |          |             |            |

| FD4                     | Port B Address          | PBADDR   | 00          | <u>44</u>  |

| FD5                     | Port B Control          | PBCTL    | 00          | <u>46</u>  |

| FD6                     | Port B Input Data       | PBIN     | XX          | <u>46</u>  |

| FD7                     | Port B Output Data      | PBOUT    | 00          | <u>46</u>  |

| GPIO Port C             |                         |          |             |            |

| FD8                     | Port C Address          | PCADDR   | 00          | 44         |

### Table 7. Register File Address Map (Continued)

1. XX = Undefined.

2. Refer to the eZ8 CPU Core User Manual (UM0128).

operational amplifier (LPO) is OFF. To use the LPO, clear the LPO bit, turning it ON. Clearing this bit might interfere with normal ADC measurements on ANA0 (the LPO output). This bit enables the amplifier even in STOP Mode. If the amplifier is not required in STOP Mode, disable it. Failure to perform this results in STOP Mode currents greater than specified.

**Note:** This register is only reset during a POR sequence. Other system reset events do not affect it.

| Bit         | 7                                                                                                                            | 6                                                                                                                       | 5     | 4   | 3           | 2            | 1            | 0             |

|-------------|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------|-----|-------------|--------------|--------------|---------------|

| Field       | LPO                                                                                                                          | Rese                                                                                                                    | erved | VBO | TEMP        | ADC          | COMP         | Reserved      |

| RESET       | 1                                                                                                                            | 0                                                                                                                       | 0     | 0   | 0           | 0            | 0            | 0             |

| R/W         | R/W                                                                                                                          | R/W                                                                                                                     | R/W   | R/W | R/W         | R/W          | R/W          | R/W           |

| Address     |                                                                                                                              |                                                                                                                         |       | F8  | ОH          |              | •            | ·             |

| Bit         | Descriptio                                                                                                                   | Description                                                                                                             |       |     |             |              |              |               |

| [7]<br>LPO  | 0 = LPO is                                                                                                                   | Low-Power Operational Amplifier Disable<br>0 = LPO is enabled (this applies even in STOP Mode).<br>1 = LPO is disabled. |       |     |             |              |              |               |

| [6:5]       | Reserved<br>These bits a                                                                                                     | <b>Reserved</b><br>These bits are reserved and must be programmed to 00.                                                |       |     |             |              |              |               |

| [4]<br>VBO  |                                                                                                                              | nabled.                                                                                                                 |       |     | both enable | e the VBO fo | or the VBO t | to be active. |

| [3]<br>TEMP | <b>Temperature Sensor Disable</b><br>0 = Temperature Sensor enabled.<br>1 = Temperature Sensor disabled.                     |                                                                                                                         |       |     |             |              |              |               |

| [2]<br>ADC  | Analog-to-Digital Converter Disable<br>0 = Analog-to-Digital Converter enabled.<br>1 = Analog-to-Digital Converter disabled. |                                                                                                                         |       |     |             |              |              |               |

| [1]<br>COMP |                                                                                                                              | or Disable<br>rator is enat<br>rator is disal                                                                           |       |     |             |              |              |               |

| [0]         | Reserved       This bit is reserved and must be programmed to 0.                                                             |                                                                                                                         |       |     |             |              |              |               |

### Table 13. Power Control Register 0 (PWRCTL0)

# Port A–D Address Registers

The Port A–D Address registers select the GPIO port functionality accessible through the Port A–D Control registers. The Port A–D Address and Control registers combine to provide access to all GPIO port controls; see Tables 18 and 19.

| Bit     | 7                      | 6          | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|------------------------|------------|-----|-----|-----|-----|-----|-----|

| Field   |                        | PADDR[7:0] |     |     |     |     |     |     |

| RESET   |                        | 00H        |     |     |     |     |     |     |

| R/W     | R/W                    | R/W        | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | FD0H, FD4H, FD8H, FDCH |            |     |     |     |     |     |     |

### Table 18. Port A–D GPIO Address Registers (PxADDR)

| Bit | Description                                                                                                                                        |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------|

| []  | Port Address                                                                                                                                       |

|     | The Port Address selects one of the subregisters accessible through the Port Control Register.<br>dicates the specific GPIO port pin number (7–0). |

### Table 19. Port A–D GPIO Address Registers by Bit Description

| PADDR[7:0] | Port Control Subregister accessible using the Port A–D Control Registers       |

|------------|--------------------------------------------------------------------------------|

| 00H        | No function. Provides some protection against accidental port reconfiguration. |

| 01H        | Data Direction.                                                                |

| 02H        | Alternate Function.                                                            |

| 03H        | Output Control (Open-Drain).                                                   |

| 04H        | High Drive Enable.                                                             |

| 05H        | Stop Mode Recovery Source Enable.                                              |

| 06H        | Pull-up Enable.                                                                |

| 07H        | Alternate Function Set 1.                                                      |

| 08H        | Alternate Function Set 2.                                                      |

| 09H–FFH    | No function.                                                                   |

# **Caution:** The frequency of the comparator output signal must not exceed one-fourth the system clock frequency. Further, the high or low state of the comparator output signal pulse must be no less than twice the system clock period. A shorter pulse may not be captured.

After reaching the reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer Reload.

Observe the following steps for configuring a timer for COMPARATOR COUNTER Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer.

- Configure the timer for COMPARATOR COUNTER Mode.

- Select either the rising edge or falling edge of the comparator output signal for the count. This also sets the initial logic level (High or Low) for the Timer Output alternate function. However, the Timer Output function is not required to be enabled.

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This action only affects the first pass in COMPARATOR COUNTER Mode. After the first timer Reload in COMPARATOR COUNTER Mode, counting always begins at the reset value of 0001H. Generally, in COMPARATOR COUNTER Mode the Timer High and Low Byte registers must be written with the value 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 6. Write to the Timer Control Register to enable the timer.

In COMPARATOR COUNTER Mode, the number of comparator output transitions since the timer start is computed via the following equation:

Comparator Output Transitions = Current Count Value – Start Value

# Watchdog Timer Refresh

When first enabled, the Watchdog Timer is loaded with the value in the Watchdog Timer Reload registers. The Watchdog Timer counts down to 000000H unless a WDT instruction is executed by the eZ8 CPU. Execution of the WDT instruction causes the downcounter to be reloaded with the WDT reload value stored in the Watchdog Timer Reload registers. Counting resumes following the reload operation.

When the Z8 Encore! XP F082A Series devices are operating in DEBUG Mode (using the on-chip debugger), the Watchdog Timer is continuously refreshed to prevent any Watchdog Timer time-outs.

# Watchdog Timer Time-Out Response

The Watchdog Timer times out when the counter reaches 000000H. A time-out of the Watchdog Timer generates either an interrupt or a system reset. The WDT\_RES Flash option bit determines the time-out response of the Watchdog Timer. For information about programming the WDT\_RES Flash option bit, see the <u>Flash Option Bits</u> chapter on page 159.

### WDT Interrupt in Normal Operation

If configured to generate an interrupt when a time-out occurs, the Watchdog Timer issues an interrupt request to the interrupt controller and sets the WDT status bit in the Reset Status (RSTSTAT) Register; see the <u>Reset Status Register</u> on page 29. If interrupts are enabled, the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executing code from the vector address. After time-out and interrupt generation, the Watchdog Timer counter rolls over to its maximum value of FFFFFH and continues counting. The Watchdog Timer counter is not automatically returned to its reload value.

The Reset Status (RSTSTAT) Register must be read before clearing the WDT interrupt. This read clears the WDT time-out Flag and prevents further WDT interrupts from immediately occurring.

### WDT Interrupt in STOP Mode

If configured to generate an interrupt when a time-out occurs and the Z8 Encore! XP F082A Series devices are in STOP Mode, the Watchdog Timer automatically initiates a Stop Mode Recovery and generates an interrupt request. Both the WDT status bit and the STOP bit in the Reset Status (RSTSTAT) Register are set to 1 following a WDT time-out in STOP Mode. For more information about Stop Mode Recovery, see the <u>Reset, Stop</u> <u>Mode Recovery and Low Voltage Detection</u> chapter on page 22.

If interrupts are enabled, following completion of the Stop Mode Recovery the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executing code from the vector address.

# **UART Interrupts**

The UART features separate interrupts for the transmitter and the receiver. In addition, when the UART primary functionality is disabled, the Baud Rate Generator can also function as a basic timer with interrupt capability.

### **Transmitter Interrupts**

The transmitter generates a single interrupt when the Transmit Data Register Empty bit (TDRE) is set to 1. This indicates that the transmitter is ready to accept new data for transmission. The TDRE interrupt occurs after the Transmit Shift Register has shifted the first bit of data out. The Transmit Data Register can now be written with the next character to send. This action provides 7 bit periods of latency to load the Transmit Data Register before the Transmit Shift Register completes shifting the current character. Writing to the UART Transmit Data Register clears the TDRE bit to 0.

### **Receiver Interrupts**

The receiver generates an interrupt when any of the following actions occur:

• A data byte is received and is available in the UART Receive Data Register. This interrupt can be disabled independently of the other receiver interrupt sources. The received data interrupt occurs after the receive character has been received and placed in the Receive Data Register. To avoid an overrun error, software must respond to this received data available condition before the next character is completely received.

**Note:** In MULTIPROCESSOR Mode (MPEN=1), the receive data interrupts are dependent on the multiprocessor configuration and the most recent address byte.

- A break is received.

- An overrun is detected.

- A data framing error is detected.

### **UART Overrun Errors**

When an overrun error condition occurs the UART prevents overwriting of the valid data currently in the Receive Data Register. The Break Detect and Overrun status bits are not displayed until after the valid data has been read.

After the valid data has been read, the UART Status 0 Register is updated to indicate the overrun condition (and Break Detect, if applicable). The RDA bit is set to 1 to indicate that the Receive Data Register contains a data byte. However, because the overrun error occurred, this byte may not contain valid data and must be ignored. The BRKD bit indicates if the overrun was caused by a break condition on the line. After reading the status

| Bit           | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [2]<br>BRGCTL | <ul> <li>Baud Rate Control</li> <li>This bit causes an alternate UART behavior depending on the value of the REN bit in the UART Control 0 Register. When the UART receiver is not enabled (REN=0), this bit determines whether the Baud Rate Generator issues interrupts.</li> <li>0 = Reads from the Baud Rate High and Low Byte registers return the BRG reload value.</li> <li>1 = The Baud Rate Generator generates a receive interrupt when it counts down to 0. Reads from the Baud Rate High and Low Byte registers return the current BRG count value.</li> <li>When the UART receiver is enabled (REN=1), this bit allows reads from the Baud Rate registers to return the BRG count value instead of the reload value.</li> <li>0 = Reads from the Baud Rate High and Low Byte registers return the BRG reload value.</li> <li>1 = Reads from the Baud Rate High and Low Byte registers return the BRG reload value.</li> <li>1 = Reads from the Baud Rate High and Low Byte registers return the BRG reload value.</li> </ul> |

| [1]<br>RDAIRQ | <ul> <li>Receive Data Interrupt Enable</li> <li>0 = Received data and receiver errors generates an interrupt request to the Interrupt Controller.</li> <li>1 = Received data does not generate an interrupt request to the Interrupt Controller. Only receiver errors generate an interrupt request.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| [0]<br>IREN   | <ul> <li>Infrared Encoder/Decoder Enable</li> <li>0 = Infrared Encoder/Decoder is disabled. UART operates normally.</li> <li>1 = Infrared Encoder/Decoder is enabled. The UART transmits and receives data through the Infrared Encoder/Decoder.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

113

The window remains open until the count again reaches 8 (that is, 24 baud clock periods since the previous pulse was detected), giving the Endec a sampling window of minus four baud rate clocks to plus eight baud rate clocks around the expected time of an incoming pulse. If an incoming pulse is detected inside this window this process is repeated. If the incoming data is a logical 1 (no pulse), the Endec returns to the initial state and waits for the next falling edge. As each falling edge is detected, the Endec clock counter is reset, resynchronizing the Endec to the incoming signal, allowing the Endec to tolerate jitter and baud rate errors in the incoming datastream. Resynchronizing the Endec does not alter the operation of the UART, which ultimately receives the data. The UART is only synchronized to the incoming data stream when a Start bit is received.

# Infrared Encoder/Decoder Control Register Definitions

All infrared endec configuration and status information is set by the UART Control registers as defined in the <u>Universal Asynchronous Receiver/Transmitter</u> section on page 99.

**Caution:** To prevent spurious signals during IrDA data transmission, set the IREN bit in the UART Control 1 Register to 1 to enable the Infrared Encoder/Decoder before enabling the GPIO Port alternate function for the corresponding pin.

# **Temperature Sensor**

The on-chip Temperature Sensor allows you to measure temperature on the die with either the on-board ADC or on-board comparator. This block is factory calibrated for in-circuit software correction. Uncalibrated accuracy is significantly worse, therefore the temperature sensor is not recommended for uncalibrated use.

# **Temperature Sensor Operation**

The on-chip temperature sensor is a Proportional to Absolute Temperature (PTAT) topology. A pair of Flash option bytes contain the calibration data. The temperature sensor can be disabled by a bit in the <u>Power Control Register 0</u> section on page 33 to reduce power consumption.

The temperature sensor can be directly read by the ADC to determine the absolute value of its output. The temperature sensor output is also available as an input to the comparator for threshold type measurement determination. The accuracy of the sensor when used with the comparator is substantially less than when measured by the ADC.

If the temperature sensor is routed to the ADC, the ADC must be configured in unity-gain buffered mode (for details, see the <u>Input Buffer Stage</u> section on page 133). The value read back from the ADC is a signed number, although it is always positive.

The sensor is factory-trimmed through the ADC using the external 2.0 V reference. Unless the sensor is retrimmed for use with a different reference, it is most accurate when used with the external 2.0 V reference.

Because this sensor is an on-chip sensor, Zilog recommends that the user account for the difference between ambient and die temperature when inferring ambient temperature conditions.

During normal operation, the die undergoes heating that causes a mismatch between the ambient temperature and that measured by the sensor. For best results, the Z8 Encore! XP device must be placed into STOP Mode for sufficient time such that the die and ambient temperatures converge (this time is dependent on the thermal design of the system). The temperature sensor measurement must then be made immediately after recovery from STOP Mode.

The following equation defines the transfer function between the temperature sensor output voltage and the die temperature. This is needed for comparator threshold measurements.

$V = 0.01 \times T + 0.65$

Debugger. Writing an invalid value or an invalid sequence returns the Flash Controller to its locked state. The Write-only Flash Control Register shares its Register File address with the read-only Flash Status Register.

These serial numbers are stored in the Flash information page and are unaffected by mass erasure of the device's Flash memory. See the Reading the Flash Information Page section below and the <u>Serialization Data section on page 173</u> for more details.

### **Randomized Lot Identification Bits**

As an optional feature, Zilog is able to provide a factory-programmed random lot identifier. With this feature, all devices in a given production lot are programmed with the same random number. This random number is uniquely regenerated for each successive production lot and is not likely to be repeated.

The randomized lot identifier is a 32 byte binary value, stored in the Flash information page and is unaffected by mass erasure of the device's Flash memory. See Reading the Flash Information Page, below, and the <u>Randomized Lot Identifier section on page 174</u> for more details.

### **Reading the Flash Information Page**

The following code example shows how to read data from the Flash information area.

; get value at info address 60 (FE60h) ldx FPS, #%80 ; enable access to flash info page ld R0, #%FE ld R1, #%60 ldc R2, @RR0 ; R2 now contains the calibration value

# **Flash Option Bit Control Register Definitions**

This section briefly describes the features of the Trim Bit Address and Data registers.

### **Trim Bit Address Register**

The Trim Bit Address (TRMADR) Register contains the target address for an access to the trim option bits (Table 86).

| Bit     | 7   | 6                                     | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----|---------------------------------------|-----|-----|-----|-----|-----|-----|

| Field   |     | TRMADR: Trim Bit Address (00H to 1FH) |     |     |     |     |     |     |

| RESET   | 0   | 0                                     | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W | R/W                                   | R/W | R/W | R/W | R/W | R/W | R/W |

| Address |     | FF6H                                  |     |     |     |     |     |     |

Table 86. Trim Bit Address Register (TRMADR)

## Trim Bit Address 0002H

### Table 92. Trim Option Bits at 0002H (TIPO)

| Bit       | 7           | 6                                     | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------|-------------|---------------------------------------|---|---|---|---|---|---|

| Field     |             | IPO_TRIM                              |   |   |   |   |   |   |

| RESET     |             | U                                     |   |   |   |   |   |   |

| R/W       |             | R/W                                   |   |   |   |   |   |   |

| Address   |             | Information Page Memory 0022H         |   |   |   |   |   |   |

| Note: U = | Unchanged b | Inchanged by Reset. R/W = Read/Write. |   |   |   |   |   |   |

|           |             |                                       |   |   |   |   |   |   |

| Bit      | Description                                                   |

|----------|---------------------------------------------------------------|

| [7:0]    | Internal Precision Oscillator Trim Byte                       |

| IPO_TRIM | Contains trimming bits for the Internal Precision Oscillator. |

# Trim Bit Address 0003H

**Note:** The LVD is available on 8-pin devices only.

### Table 93. Trim Option Bits at Address 0003H (TLVD)

| Bit                                             | 7                             | 6        | 5   | 4        | 3             | 3 2 1 |  |  |  |  |  |  |

|-------------------------------------------------|-------------------------------|----------|-----|----------|---------------|-------|--|--|--|--|--|--|

| Field                                           |                               | Reserved |     | LVD_TRIM |               |       |  |  |  |  |  |  |

| RESET                                           | U                             | U        | U   | U        | U U U         |       |  |  |  |  |  |  |

| R/W                                             | R/W                           | R/W      | R/W | R/W      | V R/W R/W R/W |       |  |  |  |  |  |  |

| Address                                         | Information Page Memory 0023H |          |     |          |               |       |  |  |  |  |  |  |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                               |          |     |          |               |       |  |  |  |  |  |  |

Note: U = Unchanged by Reset. R/W = Read/Write.

| Bit               | Description                                                                                                                                                                                                                                                            |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:5]             | Reserved<br>These bits are reserved and must be programmed to 111.                                                                                                                                                                                                     |

| [4:0]<br>LVD_TRIM | <b>Low Voltage Detect Trimm</b><br>This trimming affects the low voltage detection threshold. Each LSB represents a 50mV change in the threshold level. Alternatively, the low voltage threshold may be computed from the options bit value by the following equation: |

|                   | $LVD_LVL = 3.6 V - LVD_TRIM \times 0.05 V$                                                                                                                                                                                                                             |

|                   | These values are tabulated in Table 94.                                                                                                                                                                                                                                |

the Watchdog Timer failure can be detected. A very slow system clock results in very slow detection times.

**Caution:** It is possible to disable the clock failure detection circuitry and all functioning clock sources. In this case, the Z8 Encore! XP F082A Series device ceases functioning and can only be recovered by Power-On-Reset.

# **Oscillator Control Register Definitions**

The Oscillator Control Register (OSCCTL) enables/disables the various oscillator circuits, enables/disables the failure detection/recovery circuitry and selects the primary oscillator, which becomes the system clock.

The Oscillator Control Register must be unlocked before writing. Unlock the Oscillator Control Register by writing the two-step sequence E7H followed by 18H. The register is locked at successful completion of a register write to the OSCCTL.

| Bit     | 7     | 6     | 5     | 4     | 3     | 2      | 1   | 0   |  |  |  |

|---------|-------|-------|-------|-------|-------|--------|-----|-----|--|--|--|

| Field   | INTEN | XTLEN | WDTEN | SOFEN | WDFEN | SCKSEL |     |     |  |  |  |

| RESET   | 1     | 0     | 1     | 0     | 0     | 0      | 0   | 0   |  |  |  |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W    | R/W | R/W |  |  |  |

| Address |       |       |       | F8    | 6H    |        |     |     |  |  |  |

Table 113. Oscillator Control Register (OSCCTL)

| Bit          | Description                                                                                                                                                                                         |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>INTEN | Internal Precision Oscillator Enable<br>1 = Internal precision oscillator is enabled.<br>0 = Internal precision oscillator is disabled.                                                             |

| [6]<br>XTLEN | Crystal Oscillator Enable; this setting overrides the GPIO register control for PA0 and PA1<br>1 = Crystal oscillator is enabled.<br>0 = Crystal oscillator is disabled.                            |

| [5]<br>WDTEN | Watchdog Timer Oscillator Enable<br>1 = Watchdog Timer oscillator is enabled.<br>0 = Watchdog Timer oscillator is disabled.                                                                         |

| [4]<br>SOFEN | System Clock Oscillator Failure Detection Enable1 = Failure detection and recovery of system clock oscillator is enabled.0 = Failure detection and recovery of system clock oscillator is disabled. |

| Parameter                           | Value       | Units | Comments |

|-------------------------------------|-------------|-------|----------|

| Frequency                           | 20          | MHz   |          |

| Resonance                           | Parallel    |       |          |

| Mode                                | Fundamental |       |          |

| Series Resistance (R <sub>S</sub> ) | 60          | W     | Maximum  |

| Load Capacitance (CL)               | 30          | pF    | Maximum  |

| Shunt Capacitance (C <sub>0</sub> ) | 7           | pF    | Maximum  |

| Drive Level                         | 1           | mW    | Maximum  |

Table 114. Recommended Crystal Oscillator Specifications

| Mode         | Crystal<br>Frequency<br>Range | Function                            | Transconductance (mA/V)<br>(Use this range<br>for calculations) |      |      |  |  |

|--------------|-------------------------------|-------------------------------------|-----------------------------------------------------------------|------|------|--|--|

| Low Gain*    | 32kHz-1MHz                    | Low Power/Frequency Applications    | 0.02                                                            | 0.04 | 0.09 |  |  |

| Medium Gain* | 0.5MHz-10MHz                  | Medium Power/Frequency Applications | 0.84                                                            | 1.7  | 3.1  |  |  |

| High Gain*   | 8MHz–20MHz                    | High Power/Frequency Applications   | 1.1                                                             | 2.3  | 4.2  |  |  |

if no oscillation occurs, reduce the values of the capacitors C1 and C2 to decrease the loading.

### Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

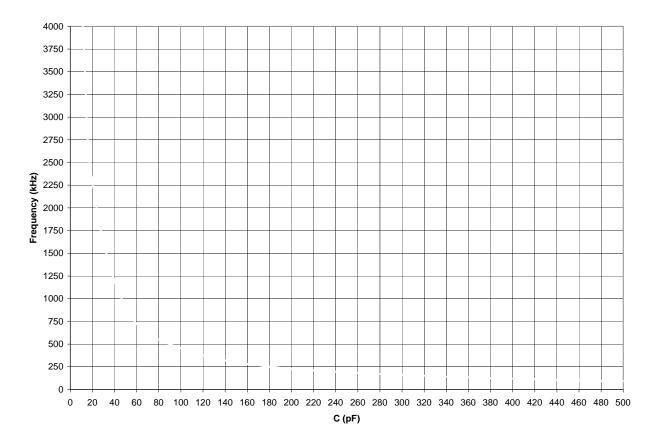

Figure 29. Typical RC Oscillator Frequency as a Function of the External Capacitance with a  $45k\Omega$  Resistor

**Caution:** When using the external RC oscillator mode, the oscillator can stop oscillating if the power supply drops below 2.7 V, but before the power supply drops to the Voltage Brown-Out threshold. The oscillator resumes oscillation when the supply voltage exceeds 2.7 V.

202

| Assembly      |                                         | Address<br>Mode |      | _ Opcode(s) | Flags |   |   |   |   |   | Fetch<br>Cycle | Instr.<br>Cycle |  |

|---------------|-----------------------------------------|-----------------|------|-------------|-------|---|---|---|---|---|----------------|-----------------|--|

| Mnemonic      | Symbolic Operation                      | dst             | src  | (Hex)       |       | Ζ | S | V | D | Н | S              | S               |  |

| JR dst        | $PC \gets PC + X$                       | DA              |      | 8B          | _     | _ | _ | _ | _ | _ | 2              | 2               |  |

| JR cc, dst    | if cc is true<br>PC $\leftarrow$ PC + X | DA              |      | 0B-FB       | _     | - | - | _ | - | _ | 2              | 2               |  |

| LD dst, rc    | dst $\leftarrow$ src                    | r               | IM   | 0C-FC       | _     | _ | _ | _ | _ | _ | 2              | 2               |  |

|               |                                         | r               | X(r) | C7          | -     |   |   |   |   |   | 3              | 3               |  |

|               |                                         | X(r)            | r    | D7          | -     |   |   |   |   |   | 3              | 4               |  |

|               |                                         | r               | lr   | E3          | -     |   |   |   |   |   | 2              | 3               |  |

|               |                                         | R               | R    | E4          | -     |   |   |   |   |   | 3              | 2               |  |

|               |                                         | R               | IR   | E5          | -     |   |   |   |   |   | 3              | 4               |  |

|               |                                         | R               | IM   | E6          | _     |   |   |   |   |   | 3              | 2               |  |

|               |                                         | IR              | IM   | E7          | _     |   |   |   |   |   | 3              | 3               |  |

|               |                                         | lr              | r    | F3          | _     |   |   |   |   |   | 2              | 3               |  |

|               |                                         | IR              | R    | F5          | _     |   |   |   |   |   | 3              | 3               |  |

| LDC dst, src  | dst $\leftarrow$ src                    | r               | Irr  | C2          | _     | _ | _ | _ | _ | _ | 2              | 5               |  |

|               |                                         | lr              | Irr  | C5          | _     |   |   |   |   |   | 2              | 9               |  |

|               |                                         | Irr             | r    | D2          | _     |   |   |   |   |   | 2              | 5               |  |

| LDCI dst, src | dst ← src                               | lr              | Irr  | C3          | _     | _ | _ | _ | _ | _ | 2              | 9               |  |

|               | r ← r + 1<br>rr ← rr + 1                | Irr             | lr   | D3          | -     |   |   |   |   |   | 2              | 9               |  |

| LDE dst, src  | dst ← src                               | r               | Irr  | 82          | _     | _ | _ | _ | _ | _ | 2              | 5               |  |

|               |                                         | Irr             | r    | 92          | -     |   |   |   |   |   | 2              | 5               |  |

| LDEI dst, src | dst $\leftarrow$ src                    | lr              | Irr  | 83          | _     | - | _ | _ | _ | - | 2              | 9               |  |

|               | r ← r + 1<br>rr ← rr + 1                | Irr             | lr   | 93          | -     |   |   |   |   |   | 2              | 9               |  |

| LDWX dst, src | dst ← src                               | ER              | ER   | 1FE8        | _     | _ | _ | - | _ | _ | 5              | 4               |  |

### Table 128. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 =Set to 1.

# Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

260

LEA 210 load 210 load constant 209 load constant to/from program memory 210 load constant with auto-increment addresses 210 load effective address 210 load external data 210 load external data to/from data memory and autoincrement addresses 209 load external to/from data memory and auto-increment addresses 210 load using extended addressing 210 logical AND 210 logical AND/extended addressing 210 logical exclusive OR 210 logical exclusive OR/extended addressing 210 logical instructions 210 logical OR 210 logical OR/extended addressing 210 low power modes 32

# Μ

master interrupt enable 57 memory data 17 program 15 mode **CAPTURE 87, 88 CAPTURE/COMPARE 88** CONTINUOUS 87 COUNTER 87 GATED 88 **ONE-SHOT 87** PWM 87, 88 modes 87 **MULT 208** multiply 208 multiprocessor mode, UART 105

# Ν

NOP (no operation) 209 notation

# 0

b 206

cc 206

DA 206

ER 206

IM 206

IR 206

Ir 206

**IRR 206**

Irr 206

p 206

R 206

r 206

RA 206

**RR 206**

vector 207

notational shorthand 206

rr 206

X 207

OCD architecture 180 auto-baud detector/generator 183 baud rate limits 184 block diagram 180 breakpoints 185 commands 186 control register 191 data format 183 DBG pin to RS-232 Interface 181 debug mode 182 debugger break 211 interface 181 serial errors 184 status register 192 timing 242 OCD commands execute instruction (12H) 190 read data memory (0DH) 190 read OCD control register (05H) 188 read OCD revision (00H) 187 read OCD status register (02H) 187 read program counter (07H) 188