Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT           |

| Number of I/O              | 25                                                        |

| Program Memory Size        | 2KB (2K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | 64 x 8                                                    |

| RAM Size                   | 512 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SSOP (0.173", 4.40mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f021ahj020eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

tor address. Following Stop Mode Recovery, the STOP bit in the Reset Status (RSTSTAT) Register is set to 1. Table 10 lists the Stop Mode Recovery sources and resulting actions. The text following provides more detailed information about each of the Stop Mode Recovery sources.

| Operating Mode | Stop Mode Recovery Source                                                   | Action                                                               |

|----------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------|

| STOP Mode      | Watchdog Timer time-out when configured for Reset                           | Stop Mode Recovery                                                   |

|                | Watchdog Timer time-out when configured for interrupt                       | Stop Mode Recovery followed by interrupt (if interrupts are enabled) |

|                | Data transition on any GPIO port pin enabled as a Stop Mode Recovery source | Stop Mode Recovery                                                   |

|                | Assertion of external RESET Pin                                             | System Reset                                                         |

|                | Debug Pin driven Low                                                        | System Reset                                                         |

### Table 10. Stop Mode Recovery Sources and Resulting Action

# Stop Mode Recovery Using Watchdog Timer Time-Out

If the Watchdog Timer times out during STOP Mode, the device undergoes a Stop Mode Recovery sequence. In the Reset Status (RSTSTAT) Register, the WDT and STOP bits are set to 1. If the Watchdog Timer is configured to generate an interrupt upon time-out and the Z8 Encore! XP F082A Series device is configured to respond to interrupts, the eZ8 CPU services the Watchdog Timer interrupt request following the normal Stop Mode Recovery sequence.

# Stop Mode Recovery Using a GPIO Port Pin Transition

Each of the GPIO port pins may be configured as a Stop Mode Recovery input source. On any GPIO pin enabled as a Stop Mode Recovery source, a change in the input pin value (from High to Low or from Low to High) initiates Stop Mode Recovery.

• Note: SMR pulses shorter than specified do not trigger a recovery (see <u>Table 135</u> on page 233). In this instance, the STOP bit in the Reset Status (RSTSTAT) Register is set to 1.

**Caution:** In STOP Mode, the GPIO Port Input Data registers (PxIN) are disabled. The Port Input Data registers record the Port transition only if the signal stays on the Port pin through the end of the Stop Mode Recovery delay. As a result, short pulses on the Port pin can initiate Stop Mode Recovery without being written to the Port Input Data Register or

| Reset or Stop Mode Recovery Event                     | POR | STOP | WDT | EXT |

|-------------------------------------------------------|-----|------|-----|-----|

| Power-On Reset                                        | 1   | 0    | 0   | 0   |

| Reset using RESET pin assertion                       | 0   | 0    | 0   | 1   |

| Reset using Watchdog Timer time-out                   | 0   | 0    | 1   | 0   |

| Reset using the On-Chip Debugger (OCTCTL[1] set to 1) | 1   | 0    | 0   | 0   |

| Reset from STOP Mode using DBG Pin driven Low         | 1   | 0    | 0   | 0   |

| Stop Mode Recovery using GPIO pin transition          | 0   | 1    | 0   | 0   |

| Stop Mode Recovery using Watchdog Timer time-out      | 0   | 1    | 1   | 0   |

# Table 12. Reset and Stop Mode Recovery Bit Descriptions

**Note:** Asserting any power control bit disables the targeted block regardless of any enable bits contained in the target block's control registers.

>

| Table 46. IRQ2 Enable Low Bit Register (IRQ2ENL |

|-------------------------------------------------|

|-------------------------------------------------|

| Bit     | 7    | 6    | 5     | 4   | 3     | 2     | 1     | 0     |

|---------|------|------|-------|-----|-------|-------|-------|-------|

| Field   |      | Rese | erved |     | C3ENL | C2ENL | C1ENL | C0ENL |

| RESET   | 0    | 0    | 0     | 0   | 0     | 0     | 0     | 0     |

| R/W     | R/W  | R/W  | R/W   | R/W | R/W   | R/W   | R/W   | R/W   |

| Address | FC8H |      |       |     |       |       |       |       |

| Bit          | Description                                                         |

|--------------|---------------------------------------------------------------------|

| [7:4]        | Reserved<br>These bits are reserved and must be programmed to 0000. |

| [3]<br>C3ENL | Port C3 Interrupt Request Enable Low Bit                            |

| [2]<br>C2ENL | Port C2 Interrupt Request Enable Low Bit                            |

| [1]<br>C1ENL | Port C1 Interrupt Request Enable Low Bit                            |

| [0]<br>COENL | Port C0 Interrupt Request Enable Low Bit                            |

# Interrupt Edge Select Register

The Interrupt Edge Select (IRQES) Register, shown in Table 47, determines whether an interrupt is generated for the rising edge or falling edge on the selected GPIO Port A input pin.

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Field   | IES7 | IES6 | IES5 | IES4 | IES3 | IES2 | IES1 | IES0 |

| RESET   | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| R/W     | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| Address |      |      |      | FC   | DH   |      |      |      |

| Table 47. | Interrupt | Edge | Select | Register | (IRQES) |

|-----------|-----------|------|--------|----------|---------|

|           |           |      |        |          | (       |

| Bit   | Description                                                                 |

|-------|-----------------------------------------------------------------------------|

| [7:0] | Interrupt Edge Select x                                                     |

| IESx  | 0 = An interrupt request is generated on the falling edge of the PAx input. |

|       | 1 = An interrupt request is generated on the rising edge of the PAx input.  |

| Note: | x indicates the specific GPIO port pin number (0–7).                        |

Rate Generator to function as an additional counter if the UART functionality is not employed.

# **UART Baud Rate Generator**

The UART Baud Rate Generator creates a lower frequency baud rate clock for data transmission. The input to the Baud Rate Generator is the system clock. The UART Baud Rate High and Low Byte registers combine to create a 16-bit baud rate divisor value (BRG[15:0]) that sets the data transmission rate (baud rate) of the UART. The UART data rate is calculated using the following equation:

UART Data Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

When the UART is disabled, the Baud Rate Generator functions as a basic 16-bit timer with an interrupt upon time-out. Observe the following steps to configure the Baud Rate Generator as a timer with an interrupt upon time-out:

- 1. Disable the UART by clearing the REN and TEN bits in the UART Control 0 Register to 0.

- 2. Load the acceptable 16-bit count value into the UART Baud Rate High and Low Byte registers.

- 3. Enable the Baud Rate Generator timer function and associated interrupt by setting the BRGCTL bit in the UART Control 1 Register to 1.

When configured as a general purpose timer, the interrupt interval is calculated using the following equation:

Interrupt Interval(s) = System Clock Period (s)  $\times$  BRG[15:0]

# **UART Control Register Definitions**

The UART Control registers support the UART and the associated Infrared Encoder/ Decoders. For more information about infrared operation, see the <u>Infrared Encoder/</u><u>Decoder</u> chapter on page 120.

# **UART Control 0 and Control 1 Registers**

The UART Control 0 (UxCTL0) and Control 1 (UxCTL1) registers, shown in Tables 63 and 64, configure the properties of the UART's transmit and receive operations. The UART Control registers must not be written while the UART is enabled.

- Write to BUFMODE[2:0] to select SINGLE-ENDED or DIFFERENTIAL mode, plus unbuffered or buffered mode.

- Write the REFSELH bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELL bit is contained in the ADC Control Register 0.

- 3. Write to the ADC Control Register 0 to configure the ADC for continuous conversion. The bit fields in the ADC Control Register may be written simultaneously:

- Write to the ANAIN[3:0] field to select from the available analog input sources (different input pins available depending on the device).

- Set CONT to 1 to select continuous conversion.

- If the internal VREF must be output to a pin, set the REFEXT bit to 1. The internal voltage reference must be enabled in this case.

- Write the REFSELL bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELH bit is contained in ADC Control/Status Register 1.

- Set CEN to 1 to start the conversions.

- 4. When the first conversion in continuous operation is complete (after 5129 system clock cycles, plus the 40 cycles for power-up, if necessary), the ADC control logic performs the following operations:

- CEN resets to 0 to indicate the first conversion is complete. CEN remains 0 for all subsequent conversions in continuous operation

- An interrupt request is sent to the Interrupt Controller to indicate the conversion is complete

- 5. The ADC writes a new data result every 256 system clock cycles. For each completed conversion, the ADC control logic performs the following operations:

- Writes the 13-bit two's complement result to {ADCD\_H[7:0], ADCD\_L[7:3]}

- Sends an interrupt request to the Interrupt Controller denoting conversion complete

- 6. To disable continuous conversion, clear the CONT bit in the ADC Control Register to 0.

### Interrupts

The ADC is able to interrupt the CPU when a conversion has been completed. When the ADC is disabled, no new interrupts are asserted; however, an interrupt pending when the ADC is disabled is not cleared.

| Bit       | 7            | 6 | 5 | 4   | 3   | 2 | 1 | 0 |

|-----------|--------------|---|---|-----|-----|---|---|---|

| Field     |              |   |   | ADO | CDH |   |   |   |

| RESET     | Х            | Х | Х | Х   | Х   | Х | Х | Х |

| R/W       | R            | R | R | R   | R   | R | R | R |

| Address   | F72H         |   |   |     |     |   |   |   |

| X = Undef | = Undefined. |   |   |     |     |   |   |   |

|           |              |   |   |     |     |   |   |   |

### Table 75. ADC Data High Byte Register (ADCD\_H)

# Bit Description [7:0] ADC Data High Byte ADCDH This byte contains the upper eight bits of the ADC output. These bits are not valid during a single-shot conversion. During a continuous conversion, the most recent conversion output is held in this register. These bits are undefined after a Reset.

# ADC Data Low Byte Register

The ADC Data Low Byte (ADCD\_L) Register contains the lower bits of the ADC output plus an overflow status bit. The output is a 13-bit two's complement value. During a single-shot conversion, this value is invalid. Access to the ADC Data Low Byte Register is read-only. Reading the ADC Data High Byte Register latches data in the ADC Low Bits Register.

| Bit            | 7    | 6 | 5     | 4 | 3 | 2    | 1     | 0   |

|----------------|------|---|-------|---|---|------|-------|-----|

| Field          |      |   | ADCDL |   |   | Rese | erved | OVF |

| RESET          | Х    | Х | Х     | Х | Х | Х    | Х     | Х   |

| R/W            | R    | R | R     | R | R | R    | R     | R   |

| Address        | F73H |   |       |   |   |      |       |     |

| X = Undefined. |      |   |       |   |   |      |       |     |

Table 76. ADC Data Low Byte Register (ADCD\_L)

| Bit            | Description                                                                                                                                      |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:3]<br>ADCDL | ADC Data Low Bits<br>These bits are the least significant five bits of the 13-bits of the ADC output. These bits are<br>undefined after a Reset. |

| Bit   | Description (Continued)                                                                                         |

|-------|-----------------------------------------------------------------------------------------------------------------|

| [2:1] | Reserved                                                                                                        |

|       | These bits are reserved and must be undefined.                                                                  |

| [0]   | Overflow Status                                                                                                 |

| OVF   | 0 = A hardware overflow did not occur in the ADC for the current sample.                                        |

|       | 1= A hardware overflow did occur in the ADC for the current sample, therefore the current<br>sample is invalid. |

# **Comparator**

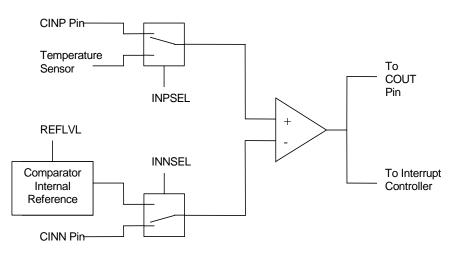

The Z8 Encore! XP F082A Series devices feature a general purpose comparator that compares two analog input signals. These analog signals may be external stimulus from a pin (CINP and/or CINN) or internally generated signals. Both a programmable voltage reference and the temperature sensor output voltage are available internally. The output is available as an interrupt source or can be routed to an external pin.

Figure 20. Comparator Block Diagram

# Operation

When the positive comparator input exceeds the negative input by more than the specified hysteresis, the output is a logic High. When the negative input exceeds the positive by more than the hysteresis, the output is a logic Low. Otherwise, the comparator output retains its present value. See <u>Table 141</u> on page 238 for details.

The comparator may be powered down to reduce supply current. See the <u>Power Control</u> <u>Register 0</u> section on page 33 for details.

**Caution:** Because of the propagation delay of the comparator, Zilog does not recommend enabling or reconfiguring the comparator without first disabling the interrupts and waiting for the comparator output to settle. Doing so can result in spurious interrupts.

| Bit    | Description (Continued)                                                                     |

|--------|---------------------------------------------------------------------------------------------|

| [5:2]  | Internal Reference Voltage Level                                                            |

| REFLVL | This reference is independent of the ADC voltage reference. Note: 8-pin devices contain two |

|        | additional LSBs for increased resolution.                                                   |

|        | For 20-/28-pin devices:                                                                     |

|        | 0000 = 0.0 V                                                                                |

|        | 0001 = 0.2 V                                                                                |

|        | 0010 = 0.4 V                                                                                |

|        | 0011 = 0.6 V                                                                                |

|        | 0100 = 0.8 V                                                                                |

|        | 0101 = 1.0 V (Default)                                                                      |

|        | 0110 = 1.2 V                                                                                |

|        | 0111 = 1.4 V                                                                                |

|        | 1000 = 1.6 V                                                                                |

|        | 1001 = 1.8 V                                                                                |

|        | 1010–1111 = Reserved                                                                        |

# Operation

This section describes the interface and modes of operation of the On-Chip Debugger.

# **OCD** Interface

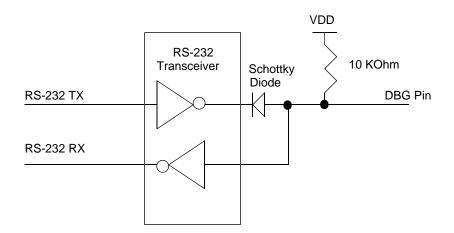

The on-chip debugger uses the DBG pin for communication with an external host. This one-pin interface is a bidirectional, open-drain interface that transmits and receives data. Data transmission is half-duplex, in that transmit and receive cannot occur simultaneously. The serial data on the DBG pin is sent using the standard asynchronous data format defined in RS-232. This pin creates an interface from the Z8 Encore! XP F082A Series products to the serial port of a host PC using minimal external hardware. Two different methods for connecting the DBG pin to an RS-232 interface are displayed in Figure 24 and Figure 25. The recommended method is the buffered implementation displayed in Figure 25. The DBG pin has a internal pull-up resistor which is sufficient for some applications (for more details about the pull-up current, see the <u>Electrical Characteristics</u> chapter on page 226). For OCD operation at higher data rates or in noisy systems, an external pull-up resistor is recommended.

**Caution:** For operation of the on-chip debugger, all power pins (V<sub>DD</sub> and AV<sub>DD</sub>) must be supplied with power and all ground pins (V<sub>SS</sub> and AV<sub>SS</sub>) must be properly grounded. The DBG pin is open-drain and may require an external pull-up resistor to ensure proper operation.

Figure 24. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface; #1 of 2

enabled, the OCD ignores the BRK signal and the BRK instruction operates as an NOP instruction.

### **Breakpoints in Flash Memory**

The BRK instruction is opcode 00H, which corresponds to the fully programmed state of a byte in Flash memory. To implement a Breakpoint, write 00H to the required break address, overwriting the current instruction. To remove a Breakpoint, the corresponding page of Flash memory must be erased and reprogrammed with the original data.

# **Runtime Counter**

The On-Chip Debugger contains a 16-bit Runtime Counter. It counts system clock cycles between Breakpoints. The counter starts counting when the On-Chip Debugger leaves DEBUG Mode and stops counting when it enters DEBUG Mode again or when it reaches the maximum count of FFFFH.

# **On-Chip Debugger Commands**

The host communicates to the on-chip debugger by sending OCD commands using the DBG interface. During normal operation, only a subset of the OCD commands are available. In DEBUG Mode, all OCD commands become available unless the user code and control registers are protected by programming the Flash Read Protect Option bit (FRP). The Flash Read Protect Option bit prevents the code in memory from being read out of the Z8 Encore! XP F082A Series device. When this option is enabled, several of the OCD commands are disabled. See Table 109.

<u>Table 110</u> on page 191 is a summary of the on-chip debugger commands. Each OCD command is described in further detail in the bulleted list following this table. Table 110 also indicates those commands that operate when the device is not in DEBUG Mode (normal operation) and those commands that are disabled by programming the Flash Read Protect Option bit.

| Debug Command              | Command<br>Byte | Enabled when<br>Not in DEBUG<br>Mode? | Disabled by Flash Read Protect<br>Option Bit |

|----------------------------|-----------------|---------------------------------------|----------------------------------------------|

| Read OCD Revision          | 00H             | Yes                                   | -                                            |

| Reserved                   | 01H             | _                                     | -                                            |

| Read OCD Status Register   | 02H             | Yes                                   | -                                            |

| Read Runtime Counter       | 03H             | -                                     | -                                            |

| Write OCD Control Register | 04H             | Yes                                   | Cannot clear DBGMODE bit.                    |

| Read OCD Control Register  | 05H             | Yes                                   | -                                            |

| Table 109. Debug Command Enable/Disable | Table 109. | Debug | Command | Enable/Disable |

|-----------------------------------------|------------|-------|---------|----------------|

|-----------------------------------------|------------|-------|---------|----------------|

| Assembly         |                                                                                           |     | lress<br>ode | _ Opcode(s) |   |   | Fla | ags |   |   | Fetch<br>Cycle | Instr.<br>Cycle |

|------------------|-------------------------------------------------------------------------------------------|-----|--------------|-------------|---|---|-----|-----|---|---|----------------|-----------------|

| Mnemonic         | Symbolic Operation                                                                        | dst | src          | (Hex)       | С | Ζ | S   | V   | D | Н | s Cycle        | Cycle<br>S      |

| AND dst, src     | $dst \gets dst \ AND \ src$                                                               | r   | r            | 52          | _ | * | *   | 0   | _ | _ | 2              | 3               |

|                  |                                                                                           | r   | Ir           | 53          |   |   |     |     |   |   | 2              | 4               |

|                  |                                                                                           | R   | R            | 54          |   |   |     |     |   |   | 3              | 3               |

|                  |                                                                                           | R   | IR           | 55          |   |   |     |     |   |   | 3              | 4               |

|                  |                                                                                           | R   | IM           | 56          |   |   |     |     |   |   | 3              | 3               |

|                  |                                                                                           | IR  | IM           | 57          |   |   |     |     |   |   | 3              | 4               |

| ANDX dst, src    | $dst \gets dst \ AND \ src$                                                               | ER  | ER           | 58          | - | * | *   | 0   | - | - | 4              | 3               |

|                  |                                                                                           | ER  | IM           | 59          |   |   |     |     |   |   | 4              | 3               |

| ATM              | Block all interrupt and<br>DMA requests during<br>execution of the next<br>3 instructions |     |              | 2F          | - | - | _   | _   | _ | _ | 1              | 2               |

| BCLR bit, dst    | dst[bit] ← 0                                                                              | r   |              | E2          | - | _ | _   | _   | _ | _ | 2              | 2               |

| BIT p, bit, dst  | dst[bit] ← p                                                                              | r   |              | E2          | - | _ | -   | -   | - | - | 2              | 2               |

| BRK              | Debugger Break                                                                            |     |              | 00          | - | _ | -   | -   | - | - | 1              | 1               |

| BSET bit, dst    | dst[bit] ← 1                                                                              | r   |              | E2          | - | _ | -   | -   | - | - | 2              | 2               |

| BSWAP dst        | $dst[7:0] \leftarrow dst[0:7]$                                                            | R   |              | D5          | Х | * | *   | 0   | - | - | 2              | 2               |

| BTJ p, bit, src, | if src[bit] = p                                                                           |     | r            | F6          | - | _ | -   | -   | - | - | 3              | 3               |

| dst              | $PC \leftarrow PC + X$                                                                    |     | lr           | F7          |   |   |     |     |   |   | 3              | 4               |

| BTJNZ bit, src,  | if src[bit] = 1                                                                           |     | r            | F6          | - | _ | -   | -   | - | - | 3              | 3               |

| dst              | $PC \leftarrow PC + X$                                                                    |     | lr           | F7          |   |   |     |     |   |   | 3              | 4               |

| BTJZ bit, src,   | if src[bit] = 0                                                                           |     | r            | F6          | - | _ | -   | -   | - | - | 3              | 3               |

| dst              | $PC \leftarrow PC + X$                                                                    |     | lr           | F7          |   |   |     |     |   |   | 3              | 4               |

### Table 128. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

| Assembly        |                                     |       | ress<br>ode | _ Opcode(s) |   |   | Fla | ags |   |   | Fetch<br>Cycle | Instr.<br>Cycle |

|-----------------|-------------------------------------|-------|-------------|-------------|---|---|-----|-----|---|---|----------------|-----------------|

| Mnemonic        | Symbolic Operation                  | dst   | src         | (Hex)       | С | Ζ | S   | v   | D | н | S              | S               |

| LDX dst, src    | $dst \leftarrow src$                | r     | ER          | 84          | - | - | -   | -   | _ | - | 3              | 2               |

|                 |                                     | lr    | ER          | 85          |   |   |     |     |   |   | 3              | 3               |

|                 |                                     | R     | IRR         | 86          | - |   |     |     |   |   | 3              | 4               |

|                 |                                     | IR    | IRR         | 87          |   |   |     |     |   |   | 3              | 5               |

|                 |                                     | r     | X(rr)       | 88          |   |   |     |     |   |   | 3              | 4               |

|                 |                                     | X(rr) | r           | 89          |   |   |     |     |   |   | 3              | 4               |

|                 |                                     | ER    | r           | 94          |   |   |     |     |   |   | 3              | 2               |

|                 |                                     | ER    | lr          | 95          |   |   |     |     |   |   | 3              | 3               |

|                 |                                     | IRR   | R           | 96          |   |   |     |     |   |   | 3              | 4               |

|                 |                                     | IRR   | IR          | 97          | - |   |     |     |   |   | 3              | 5               |

|                 |                                     | ER    | ER          | E8          | - |   |     |     |   |   | 4              | 2               |

|                 |                                     | ER    | IM          | E9          | - |   |     |     |   |   | 4              | 2               |

| LEA dst, X(src) | $dst \gets src + X$                 | r     | X(r)        | 98          | _ | - | _   | -   | - | _ | 3              | 3               |

|                 |                                     | rr    | X(rr)       | 99          |   |   |     |     |   |   | 3              | 5               |

| MULT dst        | dst[15:0] ←<br>dst[15:8] * dst[7:0] | RR    |             | F4          | _ | - | _   | -   | - | _ | 2              | 8               |

| NOP             | No operation                        |       |             | 0F          | - | - | -   | -   | - | - | 1              | 2               |

| OR dst, src     | $dst \gets dst  OR  src$            | r     | r           | 42          | _ | * | *   | 0   | _ | _ | 2              | 3               |

|                 |                                     | r     | lr          | 43          |   |   |     |     |   |   | 2              | 4               |

|                 |                                     | R     | R           | 44          |   |   |     |     |   |   | 3              | 3               |

|                 |                                     | R     | IR          | 45          |   |   |     |     |   |   | 3              | 4               |

|                 |                                     | R     | IM          | 46          | - |   |     |     |   |   | 3              | 3               |

|                 |                                     | IR    | IM          | 47          | - |   |     |     |   |   | 3              | 4               |

### Table 128. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation: \* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 =Set to 1.

| Abbreviation | Description                         | Abbreviation                                      | Description             |

|--------------|-------------------------------------|---------------------------------------------------|-------------------------|

| b            | Bit position.                       | IRR                                               | Indirect register pair. |

| СС           | Condition code.                     | р                                                 | Polarity (0 or 1).      |

| Х            | 8-bit signed index or displacement. | r                                                 | 4-bit working register. |

| DA           | Destination address.                | R                                                 | 8-bit register.         |

| ER           | Extended addressing register.       | r1, R1, Ir1, Irr1,<br>IR1, rr1, RR1,<br>IRR1, ER1 | Destination address.    |

| IM           | Immediate data value.               | r2, R2, Ir2, Irr2,<br>IR2, rr2, RR2,<br>IRR2, ER2 | Source address.         |

| Ir           | Indirect working register.          | RA                                                | Relative.               |

| IR           | Indirect register.                  | rr                                                | Working register pair.  |

| Irr          | Indirect working register pair.     | RR                                                | Register pair.          |

### Table 129. Opcode Map Abbreviations

|                                                        |                                                                                                                                                                                                          |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                      | •                                                                                                                                                                                                                                                                                                                               |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                        | V <sub>DE</sub>                                                                                                                                                                                          | ) = 2.7 V to 3                                                                                                                                                                                                      | 3.6 V                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                 |

| Parameter                                              |                                                                                                                                                                                                          |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                         | Units                                                                                                                                                                                                                | Conditions                                                                                                                                                                                                                                                                                                                      |

| ADC Internal Ref-<br>erence Supply Cur-<br>rent        | 0                                                                                                                                                                                                        |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                         | μA                                                                                                                                                                                                                   | See Note 4.                                                                                                                                                                                                                                                                                                                     |

| Comparator sup-<br>ply Current                         | 150                                                                                                                                                                                                      | 180                                                                                                                                                                                                                 | 190                                                                                                                                                                                                                                                     | μA                                                                                                                                                                                                                   | See Note 4.                                                                                                                                                                                                                                                                                                                     |

| Low-Power Opera-<br>tional Amplifier<br>Supply Current | 3                                                                                                                                                                                                        | 5                                                                                                                                                                                                                   | 5                                                                                                                                                                                                                                                       | μA                                                                                                                                                                                                                   | Driving a high-impedance load.                                                                                                                                                                                                                                                                                                  |

| Temperature Sen-<br>sor Supply Current                 | 60                                                                                                                                                                                                       |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                         | μA                                                                                                                                                                                                                   | See Note 4.                                                                                                                                                                                                                                                                                                                     |

| Band Gap Supply                                        | 320                                                                                                                                                                                                      | 480                                                                                                                                                                                                                 | 500                                                                                                                                                                                                                                                     | μA                                                                                                                                                                                                                   | For 20-/28-pin devices.                                                                                                                                                                                                                                                                                                         |

| Current                                                |                                                                                                                                                                                                          |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                      | For 8-pin devices.                                                                                                                                                                                                                                                                                                              |

|                                                        | ADC Internal Ref-<br>erence Supply Cur-<br>rent<br>Comparator sup-<br>ply Current<br>Low-Power Opera-<br>tional Amplifier<br>Supply Current<br>Temperature Sen-<br>sor Supply Current<br>Band Gap Supply | ParameterTypical1ADC Internal Ref-<br>erence Supply Cur-<br>rent0Comparator sup-<br>ply Current150Low-Power Opera-<br>tional Amplifier<br>Supply Current3Temperature Sen-<br>sor Supply Current60Band Gap Supply320 | ParameterTypical1Maximum<br>Std Temp2ADC Internal Ref-<br>erence Supply Cur-<br>rent0150180Comparator sup-<br>ply Current150180Low-Power Opera-<br>tional Amplifier<br>Supply Current35Temperature Sen-<br>sor Supply Current60180Band Gap Supply320480 | ADC Internal Ref-<br>erence Supply Cur-<br>rent<br>Comparator sup-<br>ply Current<br>Low-Power Opera-<br>tional Amplifier<br>Supply Current<br>Temperature Sen-<br>sor Supply Current<br>Band Gap Supply 320 480 500 | ParameterTypical <sup>1</sup> Maximum<br>Std Temp <sup>2</sup> Maximum<br>Ext Temp <sup>3</sup> UnitsADC Internal Ref-<br>erence Supply Cur-<br>rent0μAComparator sup-<br>ply Current150180190μALow-Power Opera-<br>tional Amplifier<br>Supply Current355μATemperature Sen-<br>sor Supply Current60μABand Gap Supply320480500μA |

### Table 132. Power Consumption (Continued)

Notes:

1. Typical conditions are defined as  $V_{DD} = 3.3 V$  and  $+30^{\circ}C$ .

2. Standard temperature is defined as  $T_A = 0^{\circ}C$  to +70°C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

3. Extended temperature is defined as  $T_A = -40^{\circ}$ C to +105°C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

4. For this block to operate, the bandgap circuit is automatically turned on and must be added to the total supply current. This bandgap current is only added once, regardless of how many peripherals are using it.

# **On-Chip Peripheral AC and DC Electrical Characteristics**

Table 135 tabulates the electrical characteristics of the POR and VBO blocks.

### Table 135. Power-On Reset and Voltage Brown-Out Electrical Characteristics and Timing

|                  |                                                                  | T <sub>A</sub> = | –40°C to +′          |         |       |                                                                                                             |

|------------------|------------------------------------------------------------------|------------------|----------------------|---------|-------|-------------------------------------------------------------------------------------------------------------|

| Symbol           | Parameter                                                        | Minimum          | Typical <sup>1</sup> | Maximum | Units | Conditions                                                                                                  |

| V <sub>POR</sub> | Power-On Reset Voltage Thresh-<br>old                            | 2.20             | 2.45                 | 2.70    | V     | $V_{DD} = V_{POR}$                                                                                          |

| V <sub>VBO</sub> | Voltage Brown-Out Reset Voltage<br>Threshold                     | 2.15             | 2.40                 | 2.65    | V     | $V_{DD} = V_{VBO}$                                                                                          |

|                  | V <sub>POR</sub> to V <sub>VBO</sub> hysteresis                  |                  | 50                   | 75      | mV    |                                                                                                             |

|                  | Starting V <sub>DD</sub> voltage to ensure valid Power-On Reset. | -                | $V_{SS}$             | _       | V     |                                                                                                             |

| T <sub>ANA</sub> | Power-On Reset Analog Delay                                      | -                | 70                   | -       | μs    | V <sub>DD</sub> > V <sub>POR</sub> ;<br>T <sub>POR</sub> Digital<br>Reset delay<br>follows T <sub>ANA</sub> |

| T <sub>POR</sub> | Power-On Reset Digital Delay                                     |                  | 16                   |         | μs    | 66 Internal<br>Precision<br>Oscillator<br>cycles + IPO<br>startup time<br>(T <sub>IPOST</sub> )             |

| T <sub>POR</sub> | Power-On Reset Digital Delay                                     |                  | 1                    |         | ms    | 5000 Internal<br>Precision<br>Oscillator<br>cycles                                                          |

| T <sub>SMR</sub> | Stop Mode Recovery with crystal oscillator disabled              |                  | 16                   |         | μs    | 66 Internal<br>Precision<br>Oscillator<br>cycles                                                            |

| T <sub>SMR</sub> | Stop Mode Recovery with crystal oscillator enabled               |                  | 1                    |         | ms    | 5000 Internal<br>Precision<br>Oscillator<br>cycles                                                          |

| T <sub>VBO</sub> | Voltage Brown-Out Pulse Rejec-<br>tion Period                    | _                | 10                   | _       | μs    | Period of time<br>in which $V_{DD} < V_{VBO}$ without<br>generating a<br>Reset.                             |

Note: Data in the typical column is from characterization at 3.3 V and 30°C. These values are provided for design guidance only and are not tested in production.

|                     |                          | T <sub>A</sub> = - | = 2.7 V to<br>-40°C to +<br>otherwise | -105°C      |       |                                                                                            |  |  |

|---------------------|--------------------------|--------------------|---------------------------------------|-------------|-------|--------------------------------------------------------------------------------------------|--|--|

| Symbol              | Parameter                | Minimum            | Typical                               | Maximum     | Units | Conditions                                                                                 |  |  |

| F <sub>WDT</sub>    | WDT Oscillator Frequency |                    | 10                                    |             | kHz   |                                                                                            |  |  |

| F <sub>WDT</sub>    | WDT Oscillator Error     |                    |                                       | <u>+</u> 50 | %     |                                                                                            |  |  |

| T <sub>WDTCAL</sub> | WDT Calibrated Time-out  | 0.98               | 1                                     | 1.02        | S     | V <sub>DD</sub> = 3.3V;<br>T <sub>A</sub> = 30°C                                           |  |  |

|                     |                          | 0.70               | 1                                     | 1.30        | S     | $V_{DD} = 2.7 V \text{ to } 3.6 V$<br>$T_A = 0^{\circ}C \text{ to } 70^{\circ}C$           |  |  |

|                     |                          | 0.50               | 1                                     | 1.50        | S     | $V_{DD} = 2.7 V \text{ to } 3.6 V$<br>$T_A = -40^{\circ}\text{C to } +105^{\circ}\text{C}$ |  |  |

## Table 137. Watchdog Timer Electrical Characteristics and Timing

### Table 138. Non-Volatile Data Storage

|                        |         | = 2.7 V to<br>-40°C to + |         |        |                                           |  |  |

|------------------------|---------|--------------------------|---------|--------|-------------------------------------------|--|--|

| Parameter              | Minimum | Typical                  | Maximum | Units  | Notes                                     |  |  |

| NVDS Byte Read Time    | 34      | _                        | 519     | μs     | With system clock at 20MHz                |  |  |

| NVDS Byte Program Time | 0.171   | _                        | 39.7    | ms     | With system clock at 20MHz                |  |  |

| Data Retention         | 100     | _                        | -       | years  | 25°C                                      |  |  |

| Endurance              | 160,000 | _                        | _       | cycles | Cumulative write cycles for entire memory |  |  |

| Lart Number                                                                                                         | Elash    | RAM     | SQ N<br>N<br>KB Elas | // I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |

|---------------------------------------------------------------------------------------------------------------------|----------|---------|----------------------|--------------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|

| Z8 Encore! XP F082A Series with 4 KB Flash, 10-Bit Analog-to-Digital Converter<br>Standard Temperature: 0°C to 70°C |          |         |                      |              |            |                     |                     |                |            |                    |                     |

| Z8F042APB020SG                                                                                                      | 4 KB     | 1KB     | ,<br>128 B           | 6            | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F042AQB020SG                                                                                                      | 4 KB     | 1KB     | 128 B                | 6            | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F042ASB020SG                                                                                                      | 4 KB     | 1KB     | 128 B                | 6            | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F042ASH020SG                                                                                                      | 4 KB     | 1KB     | 128 B                | 17           | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F042AHH020SG                                                                                                      | 4 KB     | 1KB     | 128 B                | 17           | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F042APH020SG                                                                                                      | 4 KB     | 1KB     | 128 B                | 17           | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |

| Z8F042ASJ020SG                                                                                                      | 4 KB     | 1KB     | 128 B                | 23           | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F042AHJ020SG                                                                                                      | 4 KB     | 1KB     | 128 B                | 23           | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F042APJ020SG                                                                                                      | 4 KB     | 1KB     | 128 B                | 23           | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |

| Extended Temperatu                                                                                                  | re: –40° | C to 10 | )5°C                 |              |            |                     |                     |                |            |                    |                     |

| Z8F042APB020EG                                                                                                      | 4 KB     | 1KB     | 128 B                | 6            | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |

| Z8F042AQB020EG                                                                                                      | 4 KB     | 1KB     | 128 B                | 6            | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |

| Z8F042ASB020EG                                                                                                      | 4 KB     | 1KB     | 128 B                | 6            | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |

| Z8F042ASH020EG                                                                                                      | 4 KB     | 1KB     | 128 B                | 17           | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |

| Z8F042AHH020EG                                                                                                      | 4 KB     | 1KB     | 128 B                | 17           | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |

| Z8F042APH020EG                                                                                                      | 4 KB     | 1KB     | 128 B                | 17           | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |

| Z8F042ASJ020EG                                                                                                      | 4 KB     | 1KB     | 128 B                | 23           | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |

| Z8F042AHJ020EG                                                                                                      | 4 KB     | 1KB     | 128 B                | 23           | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |

| Z8F042APJ020EG                                                                                                      | 4 KB     | 1KB     | 128 B                | 23           | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |

# Table 148. Z8 Encore! XP F082A Series Ordering Matrix

PS022827-1212

| Jaquin<br>Munu<br>Lue<br>Z8 Encore! XP F082A | Lash<br>E<br>Series | W<br>V<br>With 11 | SO<br>N<br>(B Flas | y<br>1/0 Lines | Hit Interrupts | e 16-Bit Timers w/PWM | 6<br>4<br>10-Bit A/D Channels | ici<br>UART with IrDA | D Comparator | Temperature Sensor | Description         |

|----------------------------------------------|---------------------|-------------------|--------------------|----------------|----------------|-----------------------|-------------------------------|-----------------------|--------------|--------------------|---------------------|

| Standard Temperature: 0°C to 70°C            |                     |                   |                    |                |                |                       |                               |                       |              |                    |                     |

| Z8F012APB020SG                               | 1KB                 | 256 B             | 16 B               | 6              | 14             | 2                     | 4                             | 1                     | 1            | 1                  | PDIP 8-pin package  |

| Z8F012AQB020SG                               | 1KB                 | 256 B             | 16 B               | 6              | 14             | 2                     | 4                             | 1                     | 1            | 1                  | QFN 8-pin package   |

| Z8F012ASB020SG                               | 1KB                 | 256 B             | 16 B               | 6              | 14             | 2                     | 4                             | 1                     | 1            | 1                  | SOIC 8-pin package  |

| Z8F012ASH020SG                               | 1KB                 | 256 B             | 16 B               | 17             | 20             | 2                     | 7                             | 1                     | 1            | 1                  | SOIC 20-pin package |

| Z8F012AHH020SG                               | 1KB                 | 256 B             | 16 B               | 17             | 20             | 2                     | 7                             | 1                     | 1            | 1                  | SSOP 20-pin package |

| Z8F012APH020SG                               | 1KB                 | 256 B             | 16 B               | 17             | 20             | 2                     | 7                             | 1                     | 1            | 1                  | PDIP 20-pin package |

| Z8F012ASJ020SG                               | 1KB                 | 256 B             | 16 B               | 23             | 20             | 2                     | 8                             | 1                     | 1            | 1                  | SOIC 28-pin package |

| Z8F012AHJ020SG                               | 1KB                 | 256 B             | 16 B               | 23             | 20             | 2                     | 8                             | 1                     | 1            | 1                  | SSOP 28-pin package |

| Z8F012APJ020SG                               | 1KB                 | 256 B             | 16 B               | 23             | 20             | 2                     | 8                             | 1                     | 1            | 1                  | PDIP 28-pin package |

| Extended Temperatu                           | re: –40'            | °C to 10          | 5°C                |                |                |                       |                               |                       |              |                    |                     |

| Z8F012APB020EG                               | 1KB                 | 256 B             | 16 B               | 6              | 14             | 2                     | 4                             | 1                     | 1            | 1                  | PDIP 8-pin package  |

| Z8F012AQB020EG                               | 1KB                 | 256 B             | 16 B               | 6              | 14             | 2                     | 4                             | 1                     | 1            | 1                  | QFN 8-pin package   |

| Z8F012ASB020EG                               | 1KB                 | 256 B             | 16 B               | 6              | 14             | 2                     | 4                             | 1                     | 1            | 1                  | SOIC 8-pin package  |

| Z8F012ASH020EG                               | 1KB                 | 256 B             | 16 B               | 17             | 20             | 2                     | 7                             | 1                     | 1            | 1                  | SOIC 20-pin package |

| Z8F012AHH020EG                               | 1KB                 | 256 B             | 16 B               | 17             | 20             | 2                     | 7                             | 1                     | 1            | 1                  | SSOP 20-pin package |

| Z8F012APH020EG                               | 1KB                 | 256 B             | 16 B               | 17             | 20             | 2                     | 7                             | 1                     | 1            | 1                  | PDIP 20-pin package |

| Z8F012ASJ020EG                               | 1KB                 | 256 B             | 16 B               | 23             | 20             | 2                     | 8                             | 1                     | 1            | 1                  | SOIC 28-pin package |

| Z8F012AHJ020EG                               | 1KB                 | 256 B             | 16 B               | 23             | 20             | 2                     | 8                             | 1                     | 1            | 1                  | SSOP 28-pin package |

| Z8F012APJ020EG                               | 1KB                 | 256 B             | 16 B               | 23             | 20             | 2                     | 8                             | 1                     | 1            | 1                  | PDIP 28-pin package |

# Table 148. Z8 Encore! XP F082A Series Ordering Matrix