Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT           |

| Number of I/O              | 17                                                        |

| Program Memory Size        | 2KB (2K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | 64 x 8                                                    |

| RAM Size                   | 512 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f021aph020sg |

# **Table of Contents**

| Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| List of Figuresx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| List of Tablesxii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Overview Features Part Selection Guide Block Diagram CPU and Peripheral Overview 10-Bit Analog-to-Digital Converter Low-Power Operational Amplifier Internal Precision Oscillator Temperature Sensor Analog Comparator External Crystal Oscillator  External Crystal Oscillator Low Voltage Detector On-Chip Debugger Universal Asynchronous Receiver/Transmitter Timers General-Purpose Input/Output Direct LED Drive Flash Controller Non-Volatile Data Storage Interrupt Controller Reset Controller |

| Pin Description8Available Packages8Pin Configurations8Signal Descriptions10Pin Characteristics12                                                                                                                                                                                                                                                                                                                                                                                                        |

| Address Space 15 Register File 15 Program Memory 15 Data Memory 17 Flash Information Area 17                                                                                                                                                                                                                                                                                                                                                                                                            |

| Register Man 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

## Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

xii

| Figure 25. | Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface; #2 of 2                                    |

|------------|-----------------------------------------------------------------------------------------------------------------|

| Figure 26. | OCD Data Format                                                                                                 |

| Figure 27. | Recommended 20MHz Crystal Oscillator Configuration 199                                                          |

| Figure 28. | Connecting the On-Chip Oscillator to an External RC Network 201                                                 |

| Figure 29. | Typical RC Oscillator Frequency as a Function of the External Capacitance with a $45 \mathrm{k}\Omega$ Resistor |

| Figure 30. | Opcode Map Cell Description                                                                                     |

| Figure 31. | First Opcode Map                                                                                                |

| Figure 32. | Second Opcode Map after 1FH                                                                                     |

| Figure 33. | Typical Active Mode IDD Versus System Clock Frequency                                                           |

| Figure 34. | Port Input Sample Timing                                                                                        |

| Figure 35. | GPIO Port Output Timing                                                                                         |

| Figure 36. | On-Chip Debugger Timing                                                                                         |

| Figure 37. | UART Timing With CTS                                                                                            |

| Figure 38. | UART Timing Without CTS                                                                                         |

## Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

xvii

| Table 119. | Additional Symbols                                                         |

|------------|----------------------------------------------------------------------------|

| Table 120. | Arithmetic Instructions                                                    |

| Table 121. | Bit Manipulation Instructions                                              |

| Table 122. | Block Transfer Instructions                                                |

| Table 123. | CPU Control Instructions                                                   |

| Table 124. | Load Instructions                                                          |

| Table 125. | Logical Instructions                                                       |

| Table 126. | Program Control Instructions                                               |

| Table 127. | Rotate and Shift Instructions                                              |

| Table 128. | eZ8 CPU Instruction Summary                                                |

| Table 129. | Opcode Map Abbreviations                                                   |

| Table 130. | Absolute Maximum Ratings                                                   |

| Table 131. | DC Characteristics                                                         |

| Table 132. | Power Consumption                                                          |

| Table 133. | AC Characteristics                                                         |

| Table 134. | Internal Precision Oscillator Electrical Characteristics                   |

| Table 135. | Power-On Reset and Voltage Brown-Out Electrical Characteristics and Timing |

| Table 136. | Flash Memory Electrical Characteristics and Timing                         |

| Table 137. | Watchdog Timer Electrical Characteristics and Timing                       |

| Table 138. | Non-Volatile Data Storage                                                  |

| Table 139. | Analog-to-Digital Converter Electrical Characteristics and Timing 236      |

| Table 140. | Low Power Operational Amplifier Electrical Characteristics 238             |

| Table 141. | Comparator Electrical Characteristics                                      |

| Table 142. | Temperature Sensor Electrical Characteristics                              |

| Table 143. | GPIO Port Input Timing                                                     |

| Table 144. | GPIO Port Output Timing                                                    |

| Table 145. | On-Chip Debugger Timing                                                    |

| Table 146. | UART Timing With CTS                                                       |

| Table 147. | UART Timing Without CTS                                                    |

| Table 148. | Z8 Encore! XP F082A Series Ordering Matrix                                 |

Table 3. Pin Characteristics (20- and 28-pin Devices)

| Symbol<br>Mnemonic | Direction | Reset<br>Direction            | Active<br>Low<br>or<br>Active<br>High | Tristate<br>Output   | Internal<br>Pull-up or<br>Pull-down                  | Schmitt-<br>Trigger<br>Input | Open Drain<br>Output                                 | 5 V<br>Tolerance                          |

|--------------------|-----------|-------------------------------|---------------------------------------|----------------------|------------------------------------------------------|------------------------------|------------------------------------------------------|-------------------------------------------|

| AVDD               | N/A       | N/A                           | N/A                                   | N/A                  | N/A                                                  | N/A                          | N/A                                                  | N/A                                       |

| AVSS               | N/A       | N/A                           | N/A                                   | N/A                  | N/A                                                  | N/A                          | N/A                                                  | NA                                        |

| DBG                | I/O       | I                             | N/A                                   | Yes                  | Yes                                                  | Yes                          | Yes                                                  | No                                        |

| PA[7:0]            | I/O       | I                             | N/A                                   | Yes                  | Programma-<br>ble<br>Pull-up                         | Yes                          | Yes,<br>Programma-<br>ble                            | PA[7:2]<br>unless pul-<br>lups<br>enabled |

| PB[7:0]            | I/O       | I                             | N/A                                   | Yes                  | Programma-<br>ble<br>Pull-up                         | Yes                          | Yes,<br>Programma-<br>ble                            | PB[7:6]<br>unless pul-<br>lups<br>enabled |

| PC[7:0]            | I/O       | I                             | N/A                                   | Yes                  | Programma-<br>ble<br>Pull-up                         | Yes                          | Yes,<br>Programma-<br>ble                            | PC[7:3]<br>unless pul-<br>lups<br>enabled |

| RESET/<br>PD0      | I/O       | I/O<br>(defaults to<br>RESET) | Low (in<br>Reset<br>mode)             | Yes<br>(PD0<br>only) | Programma-<br>ble for PD0;<br>always on for<br>RESET | Yes                          | Programma-<br>ble for PD0;<br>always on for<br>RESET | Yes,<br>unless pul-<br>lups<br>enabled    |

| VDD                | N/A       | N/A                           | N/A                                   | N/A                  |                                                      |                              | N/A                                                  | N/A                                       |

| VSS                | N/A       | N/A                           | N/A                                   | N/A                  |                                                      |                              | N/A                                                  | N/A                                       |

**Note:** PB6 and PB7 are available only in those devices without ADC.

#### **Reset Sources**

Table 9 lists the possible sources of a system reset.

Table 9. Reset Sources and Resulting Reset Type

| Operating Mode       | Reset Source                                          | Special Conditions                                                                            |

|----------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| NORMAL or HALT modes | Power-On Reset/Voltage Brown-Out                      | Reset delay begins after supply voltage exceeds POR level.                                    |

|                      | Watchdog Timer time-out when configured for Reset     | None.                                                                                         |

|                      | RESET pin assertion                                   | All reset pulses less than three system clocks in width are ignored.                          |

|                      | On-Chip Debugger initiated Reset (OCDCTL[0] set to 1) | System Reset, except the On-Chip Debugger is unaffected by the reset.                         |

| STOP Mode            | Power-On Reset/Voltage Brown-Out                      | Reset delay begins after supply voltage exceeds POR level.                                    |

|                      | RESET pin assertion                                   | All reset pulses less than the specified analog delay are ignored. See Table 131 on page 229. |

| _                    | DBG pin driven Low                                    | None.                                                                                         |

#### **Power-On Reset**

Z8 Encore! XP F082A Series devices contain an internal Power-On Reset circuit. The POR circuit monitors the supply voltage and holds the device in the Reset state until the supply voltage reaches a safe operating level. After the supply voltage exceeds the POR voltage threshold  $(V_{POR})$ , the device is held in the Reset state until the POR Counter has timed out. If the crystal oscillator is enabled by the option bits, this time-out is longer.

After the Z8 Encore! XP F082A Series device exits the Power-On Reset state, the eZ8 CPU fetches the Reset vector. Following Power-On Reset, the POR status bit in the Reset Status (RSTSTAT) Register is set to 1.

Figure 5 displays Power-On Reset operation. See Electrical Characteristics on page 221 for the POR threshold voltage ( $V_{POR}$ ).

#### Port A–D Address Registers

The Port A–D Address registers select the GPIO port functionality accessible through the Port A–D Control registers. The Port A–D Address and Control registers combine to provide access to all GPIO port controls; see Tables 18 and 19.

Table 18. Port A–D GPIO Address Registers (PxADDR)

| Bit     | 7          | 6                       | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|------------|-------------------------|---|---|---|---|---|---|--|

| Field   | PADDR[7:0] |                         |   |   |   |   |   |   |  |

| RESET   | 00H        |                         |   |   |   |   |   |   |  |

| R/W     | R/W        | R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |

| Address |            | FD0H, FD4H, FD8H, FDCH  |   |   |   |   |   |   |  |

| Bit        | Description                                                                                    |

|------------|------------------------------------------------------------------------------------------------|

| [7:0]      | Port Address                                                                                   |

| PADDRx     | The Port Address selects one of the subregisters accessible through the Port Control Register. |

| Note: x in | dicates the specific GPIO port pin number (7–0).                                               |

Table 19. Port A-D GPIO Address Registers by Bit Description

| PADDR[7:0] | Port Control Subregister accessible using the Port A–D Control Registers       |

|------------|--------------------------------------------------------------------------------|

| 00H        | No function. Provides some protection against accidental port reconfiguration. |

| 01H        | Data Direction.                                                                |

| 02H        | Alternate Function.                                                            |

| 03H        | Output Control (Open-Drain).                                                   |

| 04H        | High Drive Enable.                                                             |

| 05H        | Stop Mode Recovery Source Enable.                                              |

| 06H        | Pull-up Enable.                                                                |

| 07H        | Alternate Function Set 1.                                                      |

| 08H        | Alternate Function Set 2.                                                      |

| 09H-FFH    | No function.                                                                   |

#### **LED Drive Level Low Register**

The LED Drive Level registers contain two control bits for each Port C pin (Table 33). These two bits select between four programmable drive levels. Each pin is individually programmable.

Table 33. LED Drive Level Low Register (LEDLVLL)

| Bit     | 7            | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|--------------|-----|-----|-----|-----|-----|-----|-----|--|

| Field   | LEDLVLL[7:0] |     |     |     |     |     |     |     |  |

| RESET   | 0            | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |

| R/W     | R/W          | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address | F84H         |     |     |     |     |     |     |     |  |

| Bit      | Description                                                                             |

|----------|-----------------------------------------------------------------------------------------|

| [7:0]    | LED Level Low Bit                                                                       |

| LEDLVLLx | {LEDLVLH, LEDLVLL} select one of four programmable current drive levels for each Port C |

|          | pin.                                                                                    |

|          | 00 = 3 mA                                                                               |

|          | 01 = 7 mA                                                                               |

|          | 10 = 13  mA                                                                             |

|          | 11 = 20mA                                                                               |

Note: x indicates the specific GPIO port pin number (7–0).

**Example 1.** A poor coding style that can result in lost interrupt requests:

```

LDX r0, IRQ0

AND r0, MASK

LDX IRQ0, r0

```

To avoid missing interrupts, use the coding style in Example 2 to clear bits in the Interrupt Request 0 Register:

**Example 2.** A good coding style that avoids lost interrupt requests:

```

ANDX IRQ0, MASK

```

#### **Software Interrupt Assertion**

Program code can generate interrupts directly. Writing a 1 to the correct bit in the Interrupt Request Register triggers an interrupt (assuming that interrupt is enabled). When the interrupt request is acknowledged by the eZ8 CPU, the bit in the Interrupt Request Register is automatically cleared to 0.

**Caution:** Zilog recommends not using a coding style to generate software interrupts by setting bits in the Interrupt Request registers. All incoming interrupts received between execution of the first LDX command and the final LDX command are lost. See Example 3, which follows.

**Example 3.** A poor coding style that can result in lost interrupt requests:

```

LDX r0, IRQ0

OR r0, MASK

LDX IRQ0, r0

```

To avoid missing interrupts, use the coding style in Example 4 to set bits in the Interrupt Request registers:

**Example 4.** A good coding style that avoids lost interrupt requests:

```

ORX IRQ0, MASK

```

## **Watchdog Timer Interrupt Assertion**

The Watchdog Timer interrupt behavior is different from interrupts generated by other sources. The Watchdog Timer continues to assert an interrupt as long as the time-out condition continues. As it operates on a different (and usually slower) clock domain than the rest of the device, the Watchdog Timer continues to assert this interrupt for many system clocks until the counter rolls over.

#### **PWM SINGLE OUTPUT Mode**

In PWM SINGLE OUTPUT Mode, the timer outputs a Pulse-Width Modulator (PWM) output signal through a GPIO port pin. The timer input is the system clock. The timer first counts up to the 16-bit PWM match value stored in the Timer PWM High and Low Byte registers. When the timer count value matches the PWM value, the Timer Output toggles. The timer continues counting until it reaches the reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

If the TPOL bit in the Timer Control Register is set to 1, the Timer Output signal begins as a High (1) and transitions to a Low (0) when the timer value matches the PWM value. The Timer Output signal returns to a High (1) after the timer reaches the reload value and is reset to 0001H.

If the TPOL bit in the Timer Control Register is set to 0, the Timer Output signal begins as a Low (0) and transitions to a High (1) when the timer value matches the PWM value. The Timer Output signal returns to a Low (0) after the timer reaches the reload value and is reset to 0001H.

Observe the following steps for configuring a timer for PWM SINGLE OUTPUT Mode and initiating the PWM operation:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for PWM SINGLE OUTPUT Mode

- Set the prescale value

- Set the initial logic level (High or Low) and PWM High/Low transition for the Timer Output alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H). This only affects the first pass in PWM mode. After the first timer reset in PWM mode, counting always begins at the reset value of 0001H.

- 3. Write to the PWM High and Low Byte registers to set the PWM value.

- 4. Write to the Timer Reload High and Low Byte registers to set the reload value (PWM period). The reload value must be greater than the PWM value.

- 5. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 6. Configure the associated GPIO port pin for the Timer Output alternate function.

- 7. Write to the Timer Control Register to enable the timer and initiate counting.

Table 62. Watchdog Timer Reload Low Byte Register (WDTL)

| Bit        | 7                                                                                            | 6   | 5 | 4 | 3 | 2 | 1 | 0 |  |

|------------|----------------------------------------------------------------------------------------------|-----|---|---|---|---|---|---|--|

| Field      | WDTL                                                                                         |     |   |   |   |   |   |   |  |

| RESET      |                                                                                              | 00H |   |   |   |   |   |   |  |

| R/W        | R/W*                                                                                         |     |   |   |   |   |   |   |  |

| Address    | FF3H                                                                                         |     |   |   |   |   |   |   |  |

| Note: A re | Note: A read returns the current WDT count value; a write sets the appropriate reload value. |     |   |   |   |   |   |   |  |

| L - 3 | Reload Low significant byte (LSB), Bits[7:0], of the 24-bit WDT reload value. |

|-------|-------------------------------------------------------------------------------|

- Set or clear the CTSE bit to enable or disable control from the remote receiver using the CTS pin

- 6. Check the TDRE bit in the UART Status 0 Register to determine if the Transmit Data Register is empty (indicated by a 1). If empty, continue to <u>Step 7</u>. If the Transmit Data Register is full (indicated by a 0), continue to monitor the TDRE bit until the Transmit Data Register becomes available to receive new data.

- 7. Write the UART Control 1 Register to select the outgoing address bit.

- 8. Set the Multiprocessor Bit Transmitter (MPBT) if sending an address byte, clear it if sending a data byte.

- 9. Write the data byte to the UART Transmit Data Register. The transmitter automatically transfers the data to the Transmit Shift Register and transmits the data.

- 10. Make any changes to the Multiprocessor Bit Transmitter (MPBT) value, if appropriate and MULTIPROCESSOR Mode is enabled.

- 11. To transmit additional bytes, return to <u>Step 5</u>.

#### Transmitting Data using the Interrupt-Driven Method

The UART Transmitter interrupt indicates the availability of the Transmit Data Register to accept new data for transmission. Observe the following steps to configure the UART for interrupt-driven data transmission:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the appropriate baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Execute a DI instruction to disable interrupts.

- 4. Write to the Interrupt control registers to enable the UART Transmitter interrupt and set the acceptable priority.

- 5. Write to the UART Control 1 Register to enable MULTIPROCESSOR (9-bit) Mode functions, if MULTIPROCESSOR Mode is appropriate.

- 6. Set the MULTIPROCESSOR Mode Select (MPEN) to Enable MULTIPROCESSOR Mode.

- 7. Write to the UART Control 0 Register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission

- Enable parity, if appropriate and if MULTIPROCESSOR Mode is not enabled and select either even or odd parity

# Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

154

Debugger. Writing an invalid value or an invalid sequence returns the Flash Controller to its locked state. The Write-only Flash Control Register shares its Register File address with the read-only Flash Status Register.

#### Flash Sector Protect Register

The Flash Sector Protect (FPROT) Register is shared with the Flash Page Select Register. When the Flash Control Register is written with 5EH, the next write to this address targets the Flash Sector Protect Register. In all other cases, it targets the Flash Page Select Register.

This register selects one of the 8 available Flash memory sectors to be protected. The reset state of each Sector Protect bit is an unprotected state. After a sector is protected by setting its corresponding register bit, it cannot be unprotected (the register bit cannot be cleared) without powering down the device.

Table 83. Flash Sector Protect Register (FPROT)

| Bit     | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|

| Field   | SPROT7 | SPROT6 | SPROT5 | SPROT4 | SPROT3 | SPROT2 | SPROT1 | SPROT0 |

| RESET   | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| R/W     | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

| Address |        |        |        | FF     | 9H     |        |        |        |

#### Bit Description

#### [7:0] Sector Protection

SPROT*n* Each bit corresponds to a 1024-byte Flash sector on devices in the 8K range, while the remaining devices correspond to a 512-byte Flash sector. To determine the appropriate Flash memory sector address range and sector number for your Z8F082A Series product, please refer to <u>Table 78</u> on page 146 and to Figure 21, which follows the table.

- For Z8F08xA and Z8F04xA devices, all bits are used.

- For Z8F02xA devices, the upper 4 bits are unused.

- For Z8F01xA devices, the upper 6 bits are unused.

#### Flash Frequency High and Low Byte Registers

The Flash Frequency High (FFREQH) and Low Byte (FFREQL) registers combine to form a 16-bit value, FFREQ, to control timing for Flash program and erase operations. The 16-bit binary Flash Frequency value must contain the system clock frequency (in kHz) and is calculated using the following equation:

$$FFREQ[15:0] = \{FFREQH[7:0], FFREQL[7:0]\} = \frac{System Clock Frequency}{1000}$$

**Caution:** The Flash Frequency High and Low Byte registers must be loaded with the correct value to ensure proper operation of the device. Also, Flash programming and erasure is not supported for system clock frequencies below 20kHz or above 20MHz.

Table 84. Flash Frequency High Byte Register (FFREQH)

| Bit     | 7   | 6      | 5   | 4   | 3   | 2           | 1 | 0 |  |  |  |  |

|---------|-----|--------|-----|-----|-----|-------------|---|---|--|--|--|--|

| Field   |     | FFREQH |     |     |     |             |   |   |  |  |  |  |

| RESET   | 0   | 0      | 0   | 0   | 0   | 0           | 0 | 0 |  |  |  |  |

| R/W     | R/W | R/W    | R/W | R/W | R/W | R/W R/W R/W |   |   |  |  |  |  |

| Address |     |        |     | FF. | AH  |             |   |   |  |  |  |  |

| Bit    | Description                                    |

|--------|------------------------------------------------|

| [7:0]  | Flash Frequency High Byte                      |

| FFREQH | High byte of the 16-bit Flash Frequency value. |

Table 85. Flash Frequency Low Byte Register (FFREQL)

| Bit     | 7      | 6   | 5 | 4  | 3  | 2 1 0 |  |  |  |  |  |  |

|---------|--------|-----|---|----|----|-------|--|--|--|--|--|--|

| Field   | FFREQL |     |   |    |    |       |  |  |  |  |  |  |

| RESET   |        |     |   | (  | )  |       |  |  |  |  |  |  |

| R/W     |        | R/W |   |    |    |       |  |  |  |  |  |  |

| Address |        |     |   | FF | ВН |       |  |  |  |  |  |  |

| Bit    | Description                                   |

|--------|-----------------------------------------------|

| [7:0]  | Flash Frequency Low Byte                      |

| FFREQL | Low byte of the 16-bit Flash Frequency value. |

## Nonvolatile Data Storage

The Z8 Encore! XP F082A Series devices contain a nonvolatile data storage (NVDS) element of up to 128 bytes. This memory can perform over 100,000 write cycles.

## **Operation**

The NVDS is implemented by special purpose Zilog software stored in areas of program memory, which are not user-accessible. These special-purpose routines use the Flash memory to store the data. The routines incorporate a dynamic addressing scheme to maximize the write/erase endurance of the Flash.

Note:

Different members of the Z8 Encore! XP F082A Series feature multiple NVDS array sizes; see the <u>Part Selection Guide</u> section on page 2 for details. Devices containing 8KB of Flash memory do not include the NVDS feature.

#### **NVDS Code Interface**

Two routines are required to access the NVDS: a write routine and a read routine. Both of these routines are accessed with a CALL instruction to a predefined address outside of the user-accessible program memory. Both the NVDS address and data are single-byte values. Because these routines disturb the working register set, user code must ensure that any required working register values are preserved by pushing them onto the stack or by changing the working register pointer just prior to NVDS execution.

During both read and write accesses to the NVDS, interrupt service is NOT disabled. Any interrupts that occur during the NVDS execution must take care not to disturb the working register and existing stack contents or else the array may become corrupted. Disabling interrupts before executing NVDS operations is recommended.

Use of the NVDS requires 15 bytes of available stack space. Also, the contents of the working register set are overwritten.

For correct NVDS operation, the Flash Frequency registers must be programmed based on the system clock frequency (see **the** <u>Flash Operation Timing Using the Flash Frequency Registers</u> **section on page 149**).

#### **Byte Write**

To write a byte to the NVDS array, the user code must first push the address, then the data byte onto the stack. The user code issues a CALL instruction to the address of the byte-write routine (0x10B3). At the return from the sub-routine, the write status byte resides in working register R0. The bit fields of this status byte are defined in Table 106. The contents of the status byte are undefined for write operations to illegal addresses. Also, user code must pop the address and data bytes off the stack.

The write routine uses 13 bytes of stack space in addition to the two bytes of address and data pushed by the user. Sufficient memory must be available for this stack usage.

Because of the Flash memory architecture, NVDS writes exhibit a nonuniform execution time. In general, a write takes  $251\,\mu s$  (assuming a 20MHz system clock). Every 400 to 500 writes, however, a maintenance operation is necessary. In this rare occurrence, the write takes up to 61 ms to complete. Slower system clock speeds result in proportionally higher execution times.

NVDS byte writes to invalid addresses (those exceeding the NVDS array size) have no effect. Illegal write operations have a  $2\mu s$  execution time.

Table 106. Write Status Byte

| Bit              | 7 | 6    | 5     | 4 | 3    | 2  | 1   | 0   |

|------------------|---|------|-------|---|------|----|-----|-----|

| Field            |   | Rese | erved |   | RCPY | PF | AWE | DWE |

| Default<br>Value | 0 | 0    | 0     | 0 | 0    | 0  | 0   | 0   |

| Bit         | Description                                                                                                                            |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------|

| [7:4]       | Reserved These bits are reserved and must be programmed to 0000.                                                                       |

| [3]<br>RCPY | Recopy Subroutine Executed A recopy subroutine was executed. These operations take significantly longer than a normal write operation. |

| [2]<br>PF   | Power Failure Indicator A power failure or system reset occurred during the most recent attempted write to the NVDS array.             |

| [1]<br>AWE  | Address Write Error An address byte failure occurred during the most recent attempted write to the NVDS array.                         |

| [0]<br>DWE  | Data Write Error A data byte failure occurred during the most recent attempted write to the NVDS array.                                |

Table 128. eZ8 CPU Instruction Summary (Continued)

| Assembly     |                                                                                                                               | Add<br>Mo |     | _ Opcode(s) |    |   | Fla | ags |   |   | Fetch<br>Cycle | Instr.<br>Cycle |

|--------------|-------------------------------------------------------------------------------------------------------------------------------|-----------|-----|-------------|----|---|-----|-----|---|---|----------------|-----------------|

| Mnemonic     | Symbolic Operation                                                                                                            | dst       | src | (Hex)       | С  | Z | S   | ٧   | D | Н | S              | S               |

| DA dst       | dst ← DA(dst)                                                                                                                 | R         |     | 40          | *  | * | *   | Χ   | - | - | 2              | 2               |

|              |                                                                                                                               | IR        |     | 41          | -  |   |     |     |   |   | 2              | 3               |

| DEC dst      | dst ← dst - 1                                                                                                                 | R         |     | 30          | -  | * | *   | *   | - | - | 2              | 2               |

|              |                                                                                                                               | IR        |     | 31          | -  |   |     |     |   |   | 2              | 3               |

| DECW dst     | dst ← dst - 1                                                                                                                 | RR        |     | 80          | -  | * | *   | *   | - | - | 2              | 5               |

|              |                                                                                                                               | IRR       |     | 81          | -  |   |     |     |   |   | 2              | 6               |

| DI           | IRQCTL[7] ← 0                                                                                                                 |           |     | 8F          | -  | - | -   | -   | - | - | 1              | 2               |

| DJNZ dst, RA | $dst \leftarrow dst - 1$ if $dst \neq 0$ $PC \leftarrow PC + X$                                                               | r         |     | 0A-FA       | -  | - | -   | -   | - | - | 2              | 3               |

| EI           | IRQCTL[7] ← 1                                                                                                                 |           |     | 9F          | -  | - | -   | -   | - | - | 1              | 2               |

| HALT         | Halt Mode                                                                                                                     |           |     | 7F          | -  | _ | _   | _   | _ | - | 1              | 2               |

| INC dst      | dst ← dst + 1                                                                                                                 | R         |     | 20          | -  | * | *   | -   | - | - | 2              | 2               |

|              |                                                                                                                               | IR        |     | 21          | -  |   |     |     |   |   | 2              | 3               |

|              |                                                                                                                               | r         |     | 0E-FE       | -  |   |     |     |   |   | 1              | 2               |

| INCW dst     | dst ← dst + 1                                                                                                                 | RR        |     | A0          | -  | * | *   | *   | - | - | 2              | 5               |

|              |                                                                                                                               | IRR       |     | A1          | =" |   |     |     |   |   | 2              | 6               |

| IRET         | FLAGS $\leftarrow$ @SP<br>SP $\leftarrow$ SP + 1<br>PC $\leftarrow$ @SP<br>SP $\leftarrow$ SP + 2<br>IRQCTL[7] $\leftarrow$ 1 |           |     | BF          | *  | * | *   | *   | * | * | 1              | 5               |

| JP dst       | PC ← dst                                                                                                                      | DA        |     | 8D          | _  | _ | _   | _   | _ | - | 3              | 2               |

|              |                                                                                                                               | IRR       |     | C4          | 5  |   |     |     |   |   | 2              | 3               |

| JP cc, dst   | if cc is true<br>PC ← dst                                                                                                     | DA        |     | 0D-FD       | -  | - | -   | -   | - | - | 3              | 2               |

Note: Flags Notation:

<sup>\* =</sup> Value is a function of the result of the operation.

<sup>-</sup> = Unaffected.

X = Undefined.

<sup>0 =</sup> Reset to 0.

<sup>1 =</sup> Set to 1.

**Table 132. Power Consumption (Continued)**

|                           |                                                | $V_{DD}$             | = 2.7 V to 3 | 3.6 V                            |       |                                |

|---------------------------|------------------------------------------------|----------------------|--------------|----------------------------------|-------|--------------------------------|

| Symbol                    | Parameter                                      | Typical <sup>1</sup> | _            | Maximum<br>Ext Temp <sup>3</sup> | Units | Conditions                     |

| I <sub>DD</sub><br>ADCRef | ADC Internal Reference Supply Current          | 0                    |              |                                  | μA    | See Note 4.                    |

| I <sub>DD</sub><br>CMP    | Comparator sup-<br>ply Current                 | 150                  | 180          | 190                              | μΑ    | See Note 4.                    |

| I <sub>DD</sub> LPO       | Low-Power Operational Amplifier Supply Current | 3                    | 5            | 5                                | μA    | Driving a high-impedance load. |

| I <sub>DD</sub> TS        | Temperature Sensor Supply Current              | 60                   |              |                                  | μA    | See Note 4.                    |

| I <sub>DD</sub> BG        | Band Gap Supply                                | 320                  | 480          | 500                              | μΑ    | For 20-/28-pin devices.        |

|                           | Current                                        |                      |              |                                  |       | For 8-pin devices.             |

#### Notes

- 1. Typical conditions are defined as  $V_{DD} = 3.3 V$  and  $+30 ^{\circ} C$ .

- 2. Standard temperature is defined as  $T_A = 0$ °C to +70°C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

- 3. Extended temperature is defined as  $T_A = -40$ °C to +105°C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

- 4. For this block to operate, the bandgap circuit is automatically turned on and must be added to the total supply current. This bandgap current is only added once, regardless of how many peripherals are using it.

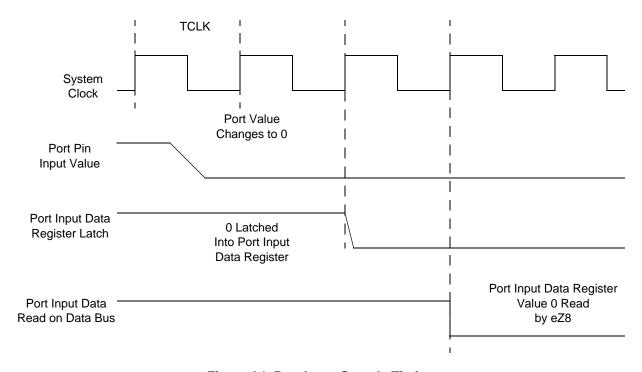

#### General Purpose I/O Port Input Data Sample Timing

Figure 34 displays timing of the GPIO Port input sampling. The input value on a GPIO port pin is sampled on the rising edge of the system clock. The Port value is available to the eZ8 CPU on the second rising clock edge following the change of the Port value.

Figure 34. Port Input Sample Timing

**Table 143. GPIO Port Input Timing**

|                     |                                                                                                    | Delay (ns) |         |  |  |

|---------------------|----------------------------------------------------------------------------------------------------|------------|---------|--|--|

| Parameter           | Abbreviation                                                                                       | Minimum    | Maximum |  |  |

| T <sub>S_PORT</sub> | Port Input Transition to X <sub>IN</sub> Rise Setup Time (not pictured)                            | 5          | _       |  |  |

| T <sub>H_PORT</sub> | X <sub>IN</sub> Rise to Port Input Transition Hold Time (not pictured)                             | 0          | _       |  |  |

| T <sub>SMR</sub>    | GPIO Port Pin Pulse Width to ensure Stop Mode Recovery (for GPIO port pins enabled as SMR sources) | 1 μs       |         |  |  |

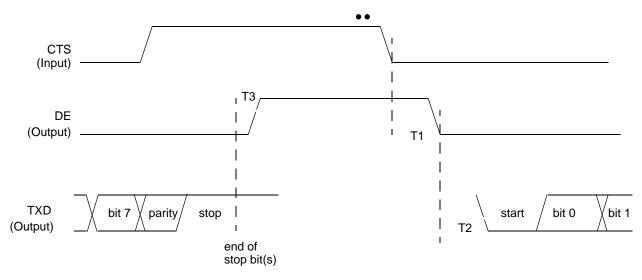

## **UART Timing**

Figure 37 and Table 146 provide timing information for UART pins for the case where CTS is used for flow control. The CTS to DE assertion delay (T1) assumes the Transmit Data Register has been loaded with data prior to CTS assertion.

Figure 37. UART Timing With CTS

**Table 146. UART Timing With CTS**

|                |                                                    | Delay (ns)                 |                                            |  |  |

|----------------|----------------------------------------------------|----------------------------|--------------------------------------------|--|--|

| Parameter      | Abbreviation                                       | Minimum                    | Maximum                                    |  |  |

| UART           |                                                    |                            |                                            |  |  |

| T <sub>1</sub> | CTS Fall to DE output delay                        | 2 * X <sub>IN</sub> period | 2 * X <sub>IN</sub> period +<br>1 bit time |  |  |

| T <sub>2</sub> | DE assertion to TXD falling edge (start bit) delay | ± 5                        |                                            |  |  |

| T <sub>3</sub> | End of Stop Bit(s) to DE deassertion delay         | =                          | ± 5                                        |  |  |