Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT           |

| Number of I/O              | 25                                                        |

| Program Memory Size        | 2KB (2K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | 64 x 8                                                    |

| RAM Size                   | 512 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 28-DIP (0.600", 15.24mm)                                  |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f021apj020sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| LED Drive Level Low Register 54                          |

|----------------------------------------------------------|

| GPIO Mode Interrupt Controller                           |

| Interrupt Vector Listing                                 |

| Architecture                                             |

| Operation                                                |

| Master Interrupt Enable                                  |

| Interrupt Vectors and Priority 58                        |

| Interrupt Assertion                                      |

| Software Interrupt Assertion 59                          |

| Watchdog Timer Interrupt Assertion 59                    |

| Interrupt Control Register Definitions                   |

| Interrupt Request 0 Register 60                          |

| Interrupt Request 1 Register                             |

| Interrupt Request 2 Register                             |

| IRQ0 Enable High and Low Bit Registers                   |

| IRQ1 Enable High and Low Bit Registers64                 |

| IRQ2 Enable High and Low Bit Registers                   |

| Interrupt Edge Select Register 67                        |

| Shared Interrupt Select Register 68                      |

| Interrupt Control Register 69                            |

| Timers                                                   |

| Architecture                                             |

| Operation                                                |

| Timer Operating Modes                                    |

| Reading the Timer Count Values                           |

| Timer Pin Signal Operation                               |

| Timer Control Register Definitions                       |

| Timer 0–1 Control Registers                              |

| Timer 0–1 High and Low Byte Registers                    |

| Timer Reload High and Low Byte Registers                 |

| Timer 0–1 PWM High and Low Byte Registers                |

| Watchdog Timer                                           |

| Operation                                                |

| Watchdog Timer Refresh                                   |

| Watchdog Timer Time-Out Response                         |

| Watchdog Timer Reload Unlock Sequence                    |

| Watchdog Timer Calibration                               |

| Watchdog Timer Control Register Definitions              |

| Watchdog Timer Control Register                          |

| Watchdog Timer Reload Upper, High and Low Byte Registers |

|                                                          |

### vi

### **Internal Precision Oscillator**

The internal precision oscillator (IPO) is a trimmable clock source that requires no external components.

### **Temperature Sensor**

The optional temperature sensor produces an analog output proportional to the device temperature. This signal can be sent to either the ADC or the analog comparator.

### **Analog Comparator**

The analog comparator compares the signal at an input pin with either an internal programmable voltage reference or a second input pin. The comparator output can be used to drive either an output pin or to generate an interrupt.

# **External Crystal Oscillator**

The crystal oscillator circuit provides highly accurate clock frequencies with the use of an external crystal, ceramic resonator or RC network.

# Low Voltage Detector

The low voltage detector (LVD) is able to generate an interrupt when the supply voltage drops below a user-programmable level. The LVD is available on 8-pin devices only.

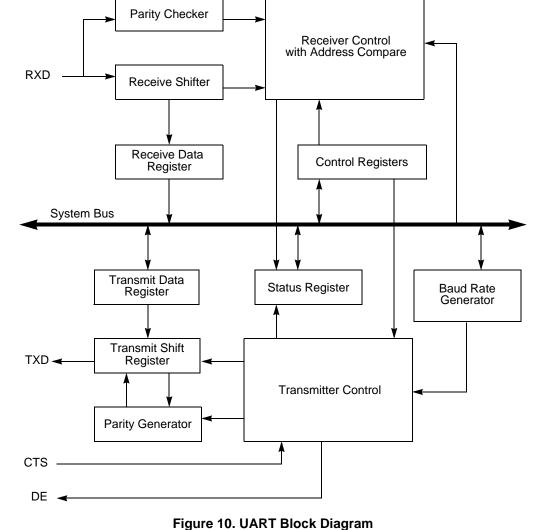

# **On-Chip Debugger**

The Z8 Encore! XP F082A Series products feature an integrated on-chip debugger (OCD) accessed via a single-pin interface. The OCD provides a rich-set of debugging capabilities, such as reading and writing registers, programming Flash memory, setting breakpoints and executing code.

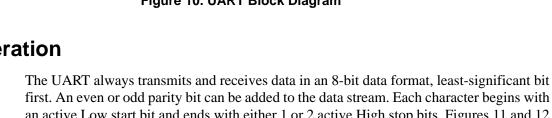

# **Universal Asynchronous Receiver/Transmitter**

The full-duplex universal asynchronous receiver/transmitter (UART) is included in all Z8 Encore! XP package types. The UART supports 8- and 9-bit data modes and selectable parity. The UART also supports multi-drop address processing in hardware. The UART baud rate generator (BRG) can be configured and used as a basic 16-bit timer.

### Timers

Two enhanced 16-bit reloadable timers can be used for timing/counting events or for motor control operations. These timers provide a 16-bit programmable reload counter and

# General-Purpose Input/Output

The Z8 Encore! XP F082A Series products support a maximum of 25 port pins (Ports A–D) for general-purpose input/output (GPIO) operations. Each port contains control and data registers. The GPIO control registers determine data direction, open-drain, output drive current, programmable pull-ups, Stop Mode Recovery functionality and alternate pin functions. Each port pin is individually programmable. In addition, the Port C pins are capable of direct LED drive at programmable drive strengths.

# **GPIO Port Availability By Device**

Table 14 lists the port pins available with each device and package type.

| Devices                                                                                                                                  | Package | ADC | Port A | Port B | Port C | Port D | Total I/O |

|------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|--------|--------|--------|--------|-----------|

| Z8F082ASB, Z8F082APB, Z8F082AQB<br>Z8F042ASB, Z8F042APB, Z8F042AQB<br>Z8F022ASB, Z8F022APB, Z8F022AQB<br>Z8F012ASB, Z8F012APB, Z8F012AQB | 8-pin   | Yes | [5:0]  | No     | No     | No     | 6         |

| Z8F081ASB, Z8F081APB, Z8F081AQB<br>Z8F041ASB, Z8F041APB, Z8F041AQB<br>Z8F021ASB, Z8F021APB, Z8F021AQB<br>Z8F011ASB, Z8F011APB, Z8F011AQB | 8-pin   | No  | [5:0]  | No     | No     | No     | 6         |

| Z8F082APH, Z8F082AHH, Z8F082ASH<br>Z8F042APH, Z8F042AHH, Z8F042ASH<br>Z8F022APH, Z8F022AHH, Z8F022ASH<br>Z8F012APH, Z8F012AHH, Z8F012ASH | 20-pin  | Yes | [7:0]  | [3:0]  | [3:0]  | [0]    | 17        |

| Z8F081APH, Z8F081AHH, Z8F081ASH<br>Z8F041APH, Z8F041AHH, Z8F041ASH<br>Z8F021APH, Z8F021AHH, Z8F021ASH<br>Z8F011APH, Z8F011AHH, Z8F011ASH | 20-pin  | No  | [7:0]  | [3:0]  | [3:0]  | [0]    | 17        |

| Z8F082APJ, Z8F082ASJ, Z8F082AHJ<br>Z8F042APJ, Z8F042ASJ, Z8F042AHJ<br>Z8F022APJ, Z8F022ASJ, Z8F022AHJ<br>Z8F012APJ, Z8F012ASJ, Z8F012AHJ | 28-pin  | Yes | [7:0]  | [5:0]  | [7:0]  | [0]    | 23        |

| Z8F081APJ, Z8F081ASJ, Z8F081AHJ<br>Z8F041APJ, Z8F041ASJ, Z8F041AHJ<br>Z8F021APJ, Z8F021ASJ, Z8F021AHJ<br>Z8F011APJ, Z8F011ASJ, Z8F011AHJ | 28-pin  | No  | [7:0]  | [7:0]  | [7:0]  | [0]    | 25        |

Table 14. Port Availability by Device and Package Type

it is appropriate to have the Timer Output make a state change at a One-Shot time-out (rather than a single cycle pulse), first set the TPOL bit in the Timer Control Register to the start value before enabling ONE-SHOT Mode. After starting the timer, set TPOL to the opposite bit value.

Observe the following steps for configuring a timer for ONE-SHOT Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for ONE-SHOT Mode.

- Set the prescale value.

- Set the initial output level (High or Low) if using the Timer Output alternate function.

- 2. Write to the Timer High and Low Byte registers to set the starting count value.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 6. Write to the Timer Control Register to enable the timer and initiate counting.

In ONE-SHOT Mode, the system clock always provides the timer input. The timer period is computed via the following equation:

$ONE-SHOT \text{ Mode Time-Out Period } (s) = \frac{\text{Reload Value} - \text{Start Value} \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$

### **CONTINUOUS Mode**

In CONTINUOUS Mode, the timer counts up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer Reload.

Observe the following steps for configuring a timer for CONTINUOUS Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CONTINUOUS Mode

first. An even or odd parity bit can be added to the data stream. Each character begins with an active Low start bit and ends with either 1 or 2 active High stop bits. Figures 11 and 12 display the asynchronous data format employed by the UART without parity and with parity, respectively.

- Set or clear the CTSE bit to enable or disable control from the remote receiver using the  $\overline{\text{CTS}}$  pin

- 6. Check the TDRE bit in the UART Status 0 Register to determine if the Transmit Data Register is empty (indicated by a 1). If empty, continue to <u>Step 7</u>. If the Transmit Data Register is full (indicated by a 0), continue to monitor the TDRE bit until the Transmit Data Register becomes available to receive new data.

- 7. Write the UART Control 1 Register to select the outgoing address bit.

- 8. Set the Multiprocessor Bit Transmitter (MPBT) if sending an address byte, clear it if sending a data byte.

- 9. Write the data byte to the UART Transmit Data Register. The transmitter automatically transfers the data to the Transmit Shift Register and transmits the data.

- 10. Make any changes to the Multiprocessor Bit Transmitter (MPBT) value, if appropriate and MULTIPROCESSOR Mode is enabled.

- 11. To transmit additional bytes, return to <u>Step 5</u>.

### Transmitting Data using the Interrupt-Driven Method

The UART Transmitter interrupt indicates the availability of the Transmit Data Register to accept new data for transmission. Observe the following steps to configure the UART for interrupt-driven data transmission:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the appropriate baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Execute a DI instruction to disable interrupts.

- 4. Write to the Interrupt control registers to enable the UART Transmitter interrupt and set the acceptable priority.

- 5. Write to the UART Control 1 Register to enable MULTIPROCESSOR (9-bit) Mode functions, if MULTIPROCESSOR Mode is appropriate.

- 6. Set the MULTIPROCESSOR Mode Select (MPEN) to Enable MULTIPROCESSOR Mode.

- 7. Write to the UART Control 0 Register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission

- Enable parity, if appropriate and if MULTIPROCESSOR Mode is not enabled and select either even or odd parity

# **UART Status 0 Register**

The UART Status 0 (UxSTAT0) and Status 1(UxSTAT1) registers, shown in Tables 65 and 66, identify the current UART operating configuration and status.

| Table 65. | UART | Status 0 | Register | (U0STAT0) |

|-----------|------|----------|----------|-----------|

|-----------|------|----------|----------|-----------|

| Bit         | 7                                                                                                                                                                                                                                           | 6                                                                                                                                                                                                                                                                                                                                                                                                                   | 5  | 4  | 3    | 2    | 1   | 0   |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|------|------|-----|-----|--|

| Field       | RDA                                                                                                                                                                                                                                         | PE                                                                                                                                                                                                                                                                                                                                                                                                                  | OE | FE | BRKD | TDRE | TXE | CTS |  |

| RESET       | 0                                                                                                                                                                                                                                           | 0                                                                                                                                                                                                                                                                                                                                                                                                                   | 0  | 0  | 0    | 1    | 1   | Х   |  |

| R/W         | R                                                                                                                                                                                                                                           | R                                                                                                                                                                                                                                                                                                                                                                                                                   | R  | R  | R    | R    | R   | R   |  |

| Address     |                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                     |    | F4 | 1H   |      |     |     |  |

| Bit         | Descriptio                                                                                                                                                                                                                                  | n                                                                                                                                                                                                                                                                                                                                                                                                                   |    |    |      |      |     |     |  |

| [7]<br>RDA  | This bit indi<br>Receive Da<br>0 = The UA                                                                                                                                                                                                   | <b>Receive Data Available</b><br>This bit indicates that the UART Receive Data Register has received data. Reading the UART<br>Receive Data Register clears this bit.<br>0 = The UART Receive Data Register is empty.<br>1 = There is a byte in the UART Receive Data Register.                                                                                                                                     |    |    |      |      |     |     |  |

| [6]<br>PE   | <ul> <li>Parity Error</li> <li>This bit indicates that a parity error has occurred. Reading the UART Receive Data Register clears this bit.</li> <li>0 = No parity error has occurred.</li> <li>1 = A parity error has occurred.</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                     |    |    |      |      |     |     |  |

| [5]<br>OE   | This bit indi<br>received an<br>reading the<br>0 = No over                                                                                                                                                                                  | <ul> <li>1 = A parity error has occurred.</li> <li>Overrun Error</li> <li>This bit indicates that an overrun error has occurred. An overrun occurs when new data is received and the UART Receive Data Register has not been read. If the RDA bit is reset to 0, reading the UART Receive Data Register clears this bit.</li> <li>0 = No overrun error occurred.</li> <li>1 = An overrun error occurred.</li> </ul> |    |    |      |      |     |     |  |

| [4]<br>FE   | Framing Error<br>This bit indicates that a framing error (no Stop bit following data reception) was detected.<br>Reading the UART Receive Data Register clears this bit.<br>0 = No framing error occurred.<br>1 = A framing error occurred. |                                                                                                                                                                                                                                                                                                                                                                                                                     |    |    |      |      |     |     |  |

| [3]<br>BRKD | This bit indi<br>are all 0s th<br>0 = No brea                                                                                                                                                                                               | <ul> <li>1 = A framing error occurred.</li> <li>Break Detect</li> <li>This bit indicates that a break occurred. If the data bits, parity/multiprocessor bit and Stop bit(s) are all 0s this bit is set to 1. Reading the UART Receive Data Register clears this bit.</li> <li>0 = No break occurred.</li> <li>1 = A break occurred.</li> </ul>                                                                      |    |    |      |      |     |     |  |

The ADC registers actually return 13 bits of data, but the two LSBs are intended for compensation use only. When the software compensation routine is performed on the 13 bit raw ADC value, two bits of resolution are lost because of a rounding error. As a result, the final value is an 11-bit number.

### Hardware Overflow

When the hardware overflow bit (OVF) is set in ADC Data Low Byte (ADCD\_L) Register, all other data bits are invalid. The hardware overflow bit is set for values greater than  $V_{REF}$  and less than  $-V_{REF}$  (DIFFERENTIAL Mode).

### Automatic Powerdown

If the ADC is idle (no conversions in progress) for 160 consecutive system clock cycles, portions of the ADC are automatically powered down. From this powerdown state, the ADC requires 40 system clock cycles to power up. The ADC powers up when a conversion is requested by the ADC Control Register.

### Single-Shot Conversion

When configured for single-shot conversion, the ADC performs a single analog-to-digital conversion on the selected analog input channel. After completion of the conversion, the ADC shuts down. Observe the following steps for setting up the ADC and initiating a single-shot conversion:

- 1. Enable the appropriate analog inputs by configuring the general-purpose I/O pins for alternate analog function. This configuration disables the digital input and output drivers.

- 2. Write the ADC Control/Status Register 1 to configure the ADC.

- Write to BUFMODE[2:0] to select SINGLE-ENDED or DIFFERENTIAL mode, plus unbuffered or buffered mode.

- Write the REFSELH bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELL bit is. contained in the ADC Control Register 0.

- 3. Write to the ADC Control Register 0 to configure the ADC and begin the conversion. The bit fields in the ADC Control Register can be written simultaneously (the ADC can be configured and enabled with the same write instruction):

- Write to the ANAIN[3:0] field to select from the available analog input sources (different input pins available depending on the device).

- Clear CONT to 0 to select a single-shot conversion.

### **ADC Control Register 0**

The ADC Control Register 0 (ADCCTL0) selects the analog input channel and initiates the analog-to-digital conversion. It also selects the voltage reference configuration.

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                        |                                                              |                           | •                                    | -                            |                             |                              |  |  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|---------------------------|--------------------------------------|------------------------------|-----------------------------|------------------------------|--|--|

| Bit                 | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6                                                                                                                                                                                                                                                                                                                                                                                      | 5                                                            | 4                         | 3                                    | 2                            | 1                           | 0                            |  |  |

| Field               | CEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CEN REFSELL REFOUT CONT ANAIN[3:0]                                                                                                                                                                                                                                                                                                                                                     |                                                              |                           |                                      |                              |                             |                              |  |  |

| RESET               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0                                                                                                                                                                                                                                                                                                                                                                                      | 0                                                            | 0                         | 0                                    | 0                            | 0                           | 0                            |  |  |

| R/W                 | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W                                                                                                                                                                                                                                                                                                                                                                                    | R/W                                                          | R/W                       | R/W                                  | R/W                          | R/W                         | R/W                          |  |  |

| Address             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                        |                                                              | F7                        | 0H                                   |                              |                             |                              |  |  |

| Bit                 | Descrip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | tion                                                                                                                                                                                                                                                                                                                                                                                   |                                                              |                           |                                      |                              |                             |                              |  |  |

| [7]<br>CEN          | 0 = Conv<br>this I<br>1 = Begi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <ul> <li>Conversion Enable</li> <li>0 = Conversion is complete. Writing a 0 produces no effect. The ADC automatically clears this bit to 0 when a conversion is complete.</li> <li>1 = Begin conversion. Writing a 1 to this bit starts a conversion. If a conversion is already in progress, the conversion restarts. This bit remains 1 until the conversion is complete.</li> </ul> |                                                              |                           |                                      |                              |                             |                              |  |  |

| [6]<br>REFSELL      | <ul> <li>Voltage Reference Level Select Low Bit</li> <li>In conjunction with the High bit (REFSELH) in ADC Control/Status Register 1, this determines the level of the internal voltage reference; the following details the effects of {REF-SELH, REFSELL}; note that this reference is independent of the Comparator reference.</li> <li>00 = Internal Reference Disabled, reference comes from external pin.</li> <li>01 = Internal Reference set to 1.0 V.</li> <li>10 = Internal Reference set to 2.0 V (default).</li> <li>11 = Reserved.</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                        |                                                              |                           |                                      |                              |                             |                              |  |  |

| [5]<br>REFOUT       | Internal Reference Output Enable<br>0 = Reference buffer is disabled; Vref pin is available for GPIO or analog functions.<br>1 = The internal ADC reference is buffered and driven out to the V <sub>REF</sub> pin.<br>Caution: When the ADC is used with an external reference ({REFSELH,REFSELL}=00),<br>the REFOUT bit must be set to 0.                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                        |                                                              |                           |                                      |                              |                             |                              |  |  |

| [4]<br>CONT         | <ul> <li>Conversion</li> <li>0 = Single-shot conversion. ADC data is output once at completion of the 5129 system clock cycles (measurements of the internal temperature sensor take twice as long).</li> <li>1 = Continuous conversion. ADC data updated every 256 system clock cycles after an initial 5129 clock conversion (measurements of the internal temperature sensor take twice as long).</li> </ul>                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                        |                                                              |                           |                                      |                              |                             |                              |  |  |

| [3:0]<br>ANAIN[3:0] | These bi<br>all packa<br>with eacl<br>able ana                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Input Select<br>ts select the<br>ages for the 2<br>h package s<br>log inputs. L<br>ntrol/Status                                                                                                                                                                                                                                                                                        | analog inpu<br>Z8 Encore! ><br>tyle, see the<br>Jsage of the | KP F082A S<br>Pin Descrip | eries. For in<br><u>otion</u> chapte | formation al<br>r on page 8. | oout port pin<br>Do not ena | is available<br>ble unavail- |  |  |

Table 73. ADC Control Register 0 (ADCCTL0)

Debugger. Writing an invalid value or an invalid sequence returns the Flash Controller to its locked state. The Write-only Flash Control Register shares its Register File address with the read-only Flash Status Register.

### Flash Page Select Register

The Flash Page Select (FPS) Register shares address space with the Flash Sector Protect Register. Unless the Flash controller is unlocked and written with 5EH, writes to this address target the Flash Page Select Register.

The register is used to select one of the available Flash memory pages to be programmed or erased. Each Flash Page contains 512 bytes of Flash memory. During a Page Erase operation, all Flash memory having addresses with the most significant 7 bits given by FPS[6:0] are chosen for program/erase operation.

| Bit     | 7       | 6   | 5                       | 4  | 3  | 2 | 1 | 0 |  |  |

|---------|---------|-----|-------------------------|----|----|---|---|---|--|--|

| Field   | INFO_EN |     | PAGE                    |    |    |   |   |   |  |  |

| RESET   | 0       | 0   | 0                       | 0  | 0  | 0 | 0 | 0 |  |  |

| R/W     | R/W     | R/W | R/W R/W R/W R/W R/W R/W |    |    |   |   |   |  |  |

| Address |         |     |                         | FF | 9H |   |   |   |  |  |

#### Table 82. Flash Page Select Register (FPS)

#### Bit Description

#### [7] Information Area Enable

INFO\_EN 0 = Information Area us not selected.

1 = Information Area is selected. The Information Area is mapped into the Program Memory address space at addresses FE00H through FFFFH.

#### [6:0] Page Select

PAGE This 7-bit field identifies the Flash memory page for Page Erase and page unlocking. Program Memory Address[15:9] = PAGE[6:0]. For the Z8F08xx devices, the upper 3 bits must be zero. For the Z8F04xx devices, the upper 4 bits must be zero. For Z8F02xx devices, the upper 5 bits must always be 0. For the Z8F01xx devices, the upper 6 bits must always be 0.

### 173

#### Table 101. Watchdog Calibration Low Byte at 007FH (WDTCALL)

| Bit       | 7                             | 6            | 5              | 4   | 3   | 2   | 1   | 0   |  |

|-----------|-------------------------------|--------------|----------------|-----|-----|-----|-----|-----|--|

| Field     |                               | WDTCALL      |                |     |     |     |     |     |  |

| RESET     | U                             | U            | U              | U   | U   | U   | U   | U   |  |

| R/W       | R/W                           | R/W          | R/W            | R/W | R/W | R/W | R/W | R/W |  |

| Address   | Information Page Memory 007FH |              |                |     |     |     |     |     |  |

| Note: U = | Unchanged b                   | y Reset. R/W | / = Read/Write | Э.  |     |     |     |     |  |

| Bit     | Description                                                                              |

|---------|------------------------------------------------------------------------------------------|

| [7:0]   | Watchdog Timer Calibration Low Byte                                                      |

| WDTCALL | The WDTCALH and WDTCALL bytes, when loaded into the Watchdog Timer reload regis-         |

|         | ters result in a one second time-out at room temperature and 3.3V supply voltage. To use |

|         | the Watchdog Timer calibration, user code must load WDTU with 0x00, WDTH with WDT-       |

|         | CALH and WDTL with WDTCALL.                                                              |

# **Serialization Data**

#### Table 102. Serial Number at 001C - 001F (S\_NUM)

| Bit       | 7                                 | 6             | 5             | 4   | 3   | 2   | 1   | 0   |

|-----------|-----------------------------------|---------------|---------------|-----|-----|-----|-----|-----|

| Field     | S_NUM                             |               |               |     |     |     |     |     |

| RESET     | U                                 | U             | U             | U   | U   | U   | U   | U   |

| R/W       | R/W                               | R/W           | R/W           | R/W | R/W | R/W | R/W | R/W |

| Address   | Information Page Memory 001C-001F |               |               |     |     |     |     |     |

| Note: U = | Unchanged b                       | by Reset. R/W | / = Read/Writ | e.  |     |     |     |     |

| Bit   | Description                                                          |

|-------|----------------------------------------------------------------------|

| [7:0] | Serial Number Byte                                                   |

| S_NUM | The serial number is a unique four-byte binary value. See Table 103. |

#### Table 103. Serialization Data Locations

| Info Page<br>Address | Memory<br>Address | Usage                                     |

|----------------------|-------------------|-------------------------------------------|

| 1C                   | FE1C              | Serial Number Byte 3 (most significant).  |

| 1D                   | FE1D              | Serial Number Byte 2.                     |

| 1E                   | FE1E              | Serial Number Byte 1.                     |

| 1F                   | FE1F              | Serial Number Byte 0 (least significant). |

Figure 25. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface; #2 of 2

### **DEBUG Mode**

The operating characteristics of the devices in DEBUG Mode are:

- The eZ8 CPU fetch unit stops, idling the eZ8 CPU, unless directed by the OCD to execute specific instructions

- The system clock operates unless in STOP Mode

- All enabled on-chip peripherals operate unless in STOP Mode

- Automatically exits HALT Mode

- Constantly refreshes the Watchdog Timer, if enabled

### **Entering DEBUG Mode**

The operating characteristics of the devices entering DEBUG Mode are:

- The device enters DEBUG Mode after the eZ8 CPU executes a BRK (Breakpoint) instruction

- If the DBG pin is held Low during the final clock cycle of system reset, the part enters DEBUG Mode immediately (20-/28-pin products only)

**Note:** Holding the DBG pin Low for an additional 5000 (minimum) clock cycles after reset (making sure to account for any specified frequency error if using an internal oscillator) prevents a false interpretation of an Autobaud sequence (see the <u>OCD Auto-Baud Detector/Generator</u> section on page 183).

When selecting a new clock source, the system clock oscillator failure detection circuitry and the Watchdog Timer oscillator failure circuitry must be disabled. If SOFEN and WOFEN are not disabled prior to a clock switch-over, it is possible to generate an interrupt for a failure of either oscillator. The Failure detection circuitry can be enabled anytime after a successful write of OSCSEL in the OSCCTL Register.

The internal precision oscillator is enabled by default. If the user code changes to a different oscillator, it may be appropriate to disable the IPO for power savings. Disabling the IPO does not occur automatically.

### **Clock Failure Detection and Recovery**

Should an oscillator or timer fail, there are methods of recovery, as this section describes.

### System Clock Oscillator Failure

The Z8F04xA family devices can generate nonmaskable interrupt-like events when the primary oscillator fails. To maintain system function in this situation, the clock failure recovery circuitry automatically forces the Watchdog Timer oscillator to drive the system clock. The Watchdog Timer oscillator must be enabled to allow the recovery. Although this oscillator runs at a much slower speed than the original system clock, the CPU continues to operate, allowing execution of a clock failure vector and software routines that either remedy the oscillator failure or issue a failure alert. This automatic switch-over is not available if the Watchdog Timer oscillator is disabled, though it is not necessary to enable the Watchdog Timer reset function (see the <u>Watchdog Timer</u> chapter on page 93).

The primary oscillator failure detection circuitry asserts if the system clock frequency drops below  $1 \text{ kHz} \pm 50\%$ . If an external signal is selected as the system oscillator, it is possible that a very slow but nonfailing clock can generate a failure condition. Under these conditions, do not enable the clock failure circuitry (SOFEN must be deasserted in the OSCCTL Register).

### Watchdog Timer Failure

In the event of a Watchdog Timer oscillator failure, a similar nonmaskable interrupt-like event is issued. This event does not trigger an attendant clock switch-over, but alerts the CPU of the failure. After a Watchdog Timer failure, it is no longer possible to detect a primary oscillator failure. The failure detection circuitry does not function if the Watchdog Timer is used as the system clock oscillator or if the Watchdog Timer oscillator has been disabled. For either of these cases, it is necessary to disable the detection circuitry by deasserting the WDFEN bit of the OSCCTL Register.

The Watchdog Timer oscillator failure detection circuit counts system clocks while looking for a Watchdog Timer clock. The logic counts 8004 system clock cycles before determining that a failure has occurred. The system clock rate determines the speed at which

# **Crystal Oscillator**

The products in the Z8 Encore! XP F082A Series contain an on-chip crystal oscillator for use with external crystals with 32kHz to 20MHz frequencies. In addition, the oscillator supports external RC networks with oscillation frequencies up to 4MHz or ceramic resonators with frequencies up to 8MHz. The on-chip crystal oscillator can be used to generate the primary system clock for the internal eZ8 CPU and the majority of the on-chip peripherals. Alternatively, the  $X_{IN}$  input pin can also accept a CMOS-level clock input signal (32kHz–20MHz). If an external clock generator is used, the  $X_{OUT}$  pin must be left unconnected. The Z8 Encore! XP F082A Series products do not contain an internal clock divider. The frequency of the signal on the  $X_{IN}$  input pin determines the frequency of the system clock.

**Note:** Although the X<sub>IN</sub> pin can be used as an input for an external clock generator, the CLKIN pin is better suited for such use (see the <u>System Clock Selection</u> section on page 193).

# **Operating Modes**

The Z8 Encore! XP F082A Series products support four oscillator modes:

- Minimum power for use with very low frequency crystals (32kHz-1MHz)

- Medium power for use with medium frequency crystals or ceramic resonators (0.5 MHz to 8MHz)

- Maximum power for use with high frequency crystals (8MHz to 20MHz)

- On-chip oscillator configured for use with external RC networks (<4MHz)

The oscillator mode is selected via user-programmable Flash option bits. See **the** <u>Flash</u> <u>Option Bits</u> chapter on page 159 for information.

# **Crystal Oscillator Operation**

The XTLDIS Flash option bit controls whether the crystal oscillator is enabled during reset. The crystal may later be disabled after reset if a new oscillator has been selected as the system clock. If the crystal is manually enabled after reset through the OSCCTL Register, the user code must wait at least 1000 crystal oscillator cycles for the crystal to stabilize. After this, the crystal oscillator may be selected as the system clock.

| Assembly        |                                     |         | ress<br>ode | _ Opcode(s) | Flags |   |   |   |   |   | Fetch<br>Cycle | Instr.<br>Cycle |

|-----------------|-------------------------------------|---------|-------------|-------------|-------|---|---|---|---|---|----------------|-----------------|

| Mnemonic        | Symbolic Operation                  | dst src |             | (Hex)       | С     | Ζ | S | v | D | н | S              | S               |

| LDX dst, src    | $dst \leftarrow src$                | r       | ER          | 84          | -     |   |   |   |   | - | 3              | 2               |

|                 |                                     | lr      | ER          | 85          |       |   |   |   |   |   | 3              | 3               |

|                 |                                     | R       | IRR         | 86          | -     |   |   |   |   |   | 3              | 4               |

|                 |                                     | IR      | IRR         | 87          |       |   |   |   |   |   | 3              | 5               |

|                 |                                     | r       | X(rr)       | 88          |       |   |   |   |   |   | 3              | 4               |

|                 |                                     | X(rr)   | r           | 89          |       |   |   |   |   |   | 3              | 4               |

|                 |                                     | ER      | r           | 94          |       |   |   |   |   |   | 3              | 2               |

|                 |                                     | ER      | lr          | 95          |       |   |   |   |   |   | 3              | 3               |

|                 |                                     | IRR     | R           | 96          |       |   |   |   |   |   | 3              | 4               |

|                 |                                     | IRR     | IR          | 97          | -     |   |   |   |   |   | 3              | 5               |

|                 |                                     | ER      | ER          | E8          | -     |   |   |   |   |   | 4              | 2               |

|                 |                                     | ER      | IM          | E9          | -     |   |   |   |   |   | 4              | 2               |

| LEA dst, X(src) | $dst \gets src + X$                 | r       | X(r)        | 98          | _     | - | _ | - | - | _ | 3              | 3               |

|                 |                                     | rr      | X(rr)       | 99          |       |   |   |   |   |   | 3              | 5               |

| MULT dst        | dst[15:0] ←<br>dst[15:8] * dst[7:0] | RR      |             | F4          | _     | - | _ | - | - | _ | 2              | 8               |

| NOP             | No operation                        |         |             | 0F          | -     | - | - | - | - | - | 1              | 2               |

| OR dst, src     | $dst \gets dst  OR  src$            | r       | r           | 42          | _     | * | * | 0 | _ | _ | 2              | 3               |

|                 |                                     | r       | lr          | 43          |       |   |   |   |   |   | 2              | 4               |

|                 |                                     | R       | R           | 44          |       |   |   |   |   |   | 3              | 3               |

|                 |                                     | R       | IR          | 45          |       |   |   |   |   |   | 3              | 4               |

|                 |                                     | R       | IM          | 46          | -     |   |   |   |   |   | 3              | 3               |

|                 |                                     | IR      | IM          | 47          | -     |   |   |   |   |   | 3              | 4               |

### Table 128. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation: \* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 =Set to 1.

Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

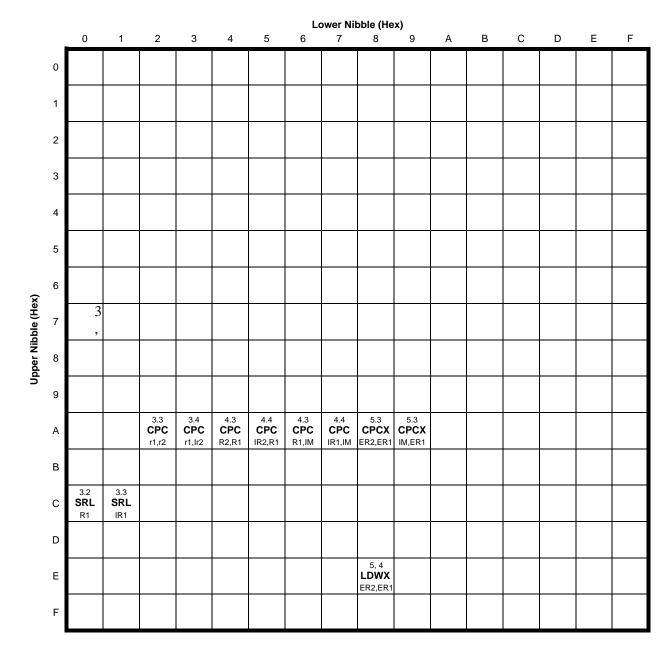

Figure 32. Second Opcode Map after 1FH

|                   |                                       |                 | -40°C to +<br>otherwise s |            |       |                                                                                       |  |  |

|-------------------|---------------------------------------|-----------------|---------------------------|------------|-------|---------------------------------------------------------------------------------------|--|--|

| Symbol            | Parameter                             | Minimum Typical |                           | Maximum    | Units | Conditions                                                                            |  |  |

| V <sub>OH1</sub>  | High Level Output<br>Voltage          | 2.4             | -                         | -          | V     | I <sub>OH</sub> = -2 mA; V <sub>DD</sub> = 3.0 V<br>High Output Drive disabled.       |  |  |

| V <sub>OL2</sub>  | Low Level Output<br>Voltage           | _               | -                         | 0.6        | V     | $I_{OL}$ = 20 mA; $V_{DD}$ = 3.3V<br>High Output Drive enabled.                       |  |  |

| V <sub>OH2</sub>  | High Level Output<br>Voltage          | 2.4             | _                         | _          | V     | I <sub>OH</sub> = -20 mA; V <sub>DD</sub> = 3.3V<br>High Output Drive enabled.        |  |  |

| I <sub>IH</sub>   | Input Leakage Cur-<br>rent            | _               | <u>+</u> 0.002            | <u>+</u> 5 | μA    | $V_{IN} = V_{DD}$<br>$V_{DD} = 3.3 V;$                                                |  |  |

| I <sub>IL</sub>   | Input Leakage Cur-<br>rent            | -               | <u>+</u> 0.007            | <u>+</u> 5 | μA    | $V_{IN} = V_{SS}$<br>$V_{DD} = 3.3V;$                                                 |  |  |

| I <sub>TL</sub>   | Tristate Leakage<br>Current           | -               | -                         | <u>+</u> 5 | μA    |                                                                                       |  |  |

| I <sub>LED</sub>  | Controlled Current<br>Drive           | 1.8             | 3                         | 4.5        | mA    | $\{AFS2, AFS1\} = \{0, 0\}$                                                           |  |  |

|                   |                                       | 2.8             | 7                         | 10.5       | mA    | $\{AFS2, AFS1\} = \{0, 1\}$                                                           |  |  |

|                   |                                       | 7.8             | 13                        | 19.5       | mA    | ${AFS2,AFS1} = {1,0}$                                                                 |  |  |

|                   |                                       | 12              | 20                        | 30         | mA    | ${AFS2,AFS1} = {1,1}$                                                                 |  |  |

| C <sub>PAD</sub>  | GPIO Port Pad<br>Capacitance          | -               | 8.0 <sup>2</sup>          | -          | pF    |                                                                                       |  |  |

| C <sub>XIN</sub>  | XIN Pad Capaci-<br>tance              | -               | 8.0 <sup>2</sup>          | _          | pF    |                                                                                       |  |  |

| C <sub>XOUT</sub> | X <sub>OUT</sub> Pad Capaci-<br>tance | -               | 9.5 <sup>2</sup>          | _          | pF    |                                                                                       |  |  |

| I <sub>PU</sub>   | Weak Pull-up Cur-<br>rent             | 30              | 100                       | 350        | μA    | V <sub>DD</sub> = 3.0 V–3.6 V                                                         |  |  |

| V <sub>RAM</sub>  | RAM Data Reten-<br>tion Voltage       | TBD             |                           |            | V     | Voltage at which RAM retains<br>static values; no reading or writ-<br>ing is allowed. |  |  |

### Table 131. DC Characteristics (Continued)

Notes:

1. This condition excludes all pins that have on-chip pull-ups, when driven Low.

2. These values are provided for design guidance only and are not tested in production.

# **On-Chip Peripheral AC and DC Electrical Characteristics**

Table 135 tabulates the electrical characteristics of the POR and VBO blocks.

#### Table 135. Power-On Reset and Voltage Brown-Out Electrical Characteristics and Timing

|                  |                                                                  | T <sub>A</sub> = | –40°C to +′          |         |       |                                                                                                             |  |

|------------------|------------------------------------------------------------------|------------------|----------------------|---------|-------|-------------------------------------------------------------------------------------------------------------|--|

| Symbol           | Parameter                                                        | Minimum          | Typical <sup>1</sup> | Maximum | Units | Conditions                                                                                                  |  |

| V <sub>POR</sub> | Power-On Reset Voltage Thresh-<br>old                            | 2.20             | 2.45                 | 2.70    | V     | $V_{DD} = V_{POR}$                                                                                          |  |

| V <sub>VBO</sub> | Voltage Brown-Out Reset Voltage<br>Threshold                     | 2.15             | 2.40                 | 2.65    | V     | $V_{DD} = V_{VBO}$                                                                                          |  |

|                  | V <sub>POR</sub> to V <sub>VBO</sub> hysteresis                  |                  | 50                   | 75      | mV    |                                                                                                             |  |

|                  | Starting V <sub>DD</sub> voltage to ensure valid Power-On Reset. | -                | $V_{SS}$             | -       | V     |                                                                                                             |  |

| T <sub>ANA</sub> | Power-On Reset Analog Delay                                      | -                | 70                   | -       | μs    | V <sub>DD</sub> > V <sub>POR</sub> ;<br>T <sub>POR</sub> Digital<br>Reset delay<br>follows T <sub>ANA</sub> |  |

| T <sub>POR</sub> | Power-On Reset Digital Delay                                     |                  | 16                   |         | μs    | 66 Internal<br>Precision<br>Oscillator<br>cycles + IPO<br>startup time<br>(T <sub>IPOST</sub> )             |  |

| T <sub>POR</sub> | Power-On Reset Digital Delay                                     |                  | 1                    |         | ms    | 5000 Internal<br>Precision<br>Oscillator<br>cycles                                                          |  |

| T <sub>SMR</sub> | Stop Mode Recovery with crystal oscillator disabled              |                  | 16                   |         | μs    | 66 Internal<br>Precision<br>Oscillator<br>cycles                                                            |  |

| T <sub>SMR</sub> | Stop Mode Recovery with crystal oscillator enabled               |                  | 1                    |         | ms    | 5000 Internal<br>Precision<br>Oscillator<br>cycles                                                          |  |

| T <sub>VBO</sub> | Voltage Brown-Out Pulse Rejec-<br>tion Period                    | _                | 10                   | _       | μs    | Period of time<br>in which $V_{DD} < V_{VBO}$ without<br>generating a<br>Reset.                             |  |

Note: Data in the typical column is from characterization at 3.3 V and 30°C. These values are provided for design guidance only and are not tested in production.

| Z8 Encore! XP F082A               | Lash<br>Series | Wey<br>with 2 | SO<br>AN<br>KB Flas | b. 10 Lines | Hiterrupts | and the second sec | 10-Bit A/D Channels | UART with IrDA | E Comparator | Temperature Sensor | Description         |

|-----------------------------------|----------------|---------------|---------------------|-------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------|--------------|--------------------|---------------------|

| Standard Temperature: 0°C to 70°C |                |               |                     |             |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                     |                |              |                    |                     |

| Z8F022APB020SG                    | 2 KB           | 512 B         | 64 B                | 6           | 14         | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4                   | 1              | 1            | 1                  | PDIP 8-pin package  |

| Z8F022AQB020SG                    | 2 KB           | 512 B         | 64 B                | 6           | 14         | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4                   | 1              | 1            | 1                  | QFN 8-pin package   |

| Z8F022ASB020SG                    | 2 KB           | 512 B         | 64 B                | 6           | 14         | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4                   | 1              | 1            | 1                  | SOIC 8-pin package  |

| Z8F022ASH020SG                    | 2 KB           | 512 B         | 64 B                | 17          | 20         | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7                   | 1              | 1            | 1                  | SOIC 20-pin package |