Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betans                     |                                                           |  |

|----------------------------|-----------------------------------------------------------|--|

| Product Status             | Active                                                    |  |

| Core Processor             | eZ8                                                       |  |

| Core Size                  | 8-Bit                                                     |  |

| Speed                      | 20MHz                                                     |  |

| Connectivity               | IrDA, UART/USART                                          |  |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT           |  |

| Number of I/O              | 6                                                         |  |

| Program Memory Size        | 2KB (2K x 8)                                              |  |

| Program Memory Type        | FLASH                                                     |  |

| EEPROM Size                | 64 x 8                                                    |  |

| RAM Size                   | 512 x 8                                                   |  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |  |

| Data Converters            | -                                                         |  |

| Oscillator Type            | Internal                                                  |  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |  |

| Mounting Type              | Surface Mount                                             |  |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                             |  |

| Supplier Device Package    | -                                                         |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f021asb020eg |  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Universal Asynchronous Receiver/Transmitter           | . 99 |

|-------------------------------------------------------|------|

| Architecture                                          | . 99 |

| Operation                                             | 100  |

| Transmitting Data using the Polled Method             | 101  |

| Transmitting Data using the Interrupt-Driven Method   | 102  |

| Receiving Data using the Polled Method                | 103  |

| Receiving Data using the Interrupt-Driven Method      | 104  |

| Clear To Send (CTS) Operation                         | 105  |

| MULTIPROCESSOR (9-bit) Mode                           |      |

| External Driver Enable                                | 107  |

| UART Interrupts                                       |      |

| UART Baud Rate Generator                              |      |

| UART Control Register Definitions                     | 110  |

| UART Control 0 and Control 1 Registers                | 110  |

| UART Status 0 Register                                |      |

| UART Status 1 Register                                |      |

| UART Transmit Data Register                           | 115  |

| UART Receive Data Register                            |      |

| UART Address Compare Register                         |      |

| UART Baud Rate High and Low Byte Registers            | 117  |

| Infrared Encoder/Decoder                              | 120  |

| Architecture                                          | 120  |

| Operation                                             | 120  |

| Transmitting IrDA Data                                | 121  |

| Receiving IrDA Data                                   | 122  |

| Infrared Encoder/Decoder Control Register Definitions | 123  |

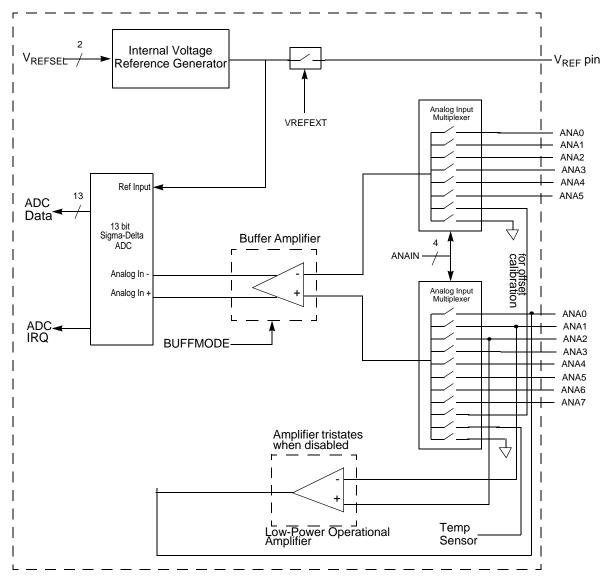

| Analog-to-Digital Converter                           | 124  |

| Architecture                                          |      |

| Operation                                             |      |

| Hardware Overflow                                     |      |

| Automatic Powerdown                                   | 126  |

| Single-Shot Conversion                                |      |

| Continuous Conversion                                 |      |

| Interrupts                                            |      |

| Calibration and Compensation                          |      |

| ADC Compensation Details                              | 130  |

| Input Buffer Stage                                    |      |

| ADC Control Register Definitions                      |      |

| ADC Control Register 0                                | 134  |

| ADC Control/Status Register 1                         |      |

operate in ONE-SHOT, CONTINUOUS, GATED, CAPTURE, CAPTURE RESTART, COMPARE, CAPTURE and COMPARE, PWM SINGLE OUTPUT and PWM DUAL OUTPUT modes.

### **General-Purpose Input/Output**

The Product Line MCUs feature 6 to 25 port pins (Ports A–D) for general- purpose input/ output (GPIO). The number of GPIO pins available is a function of package and each pin is individually programmable. 5 V tolerant input pins are available on all I/Os on 8-pin devices and most I/Os on other package types.

### **Direct LED Drive**

The 20- and 28-pin devices support controlled current sinking output pins capable of driving LEDs without the need for a current limiting resistor. These LED drivers are independently programmable to four different intensity levels.

### **Flash Controller**

The Flash Controller programs and erases Flash memory. The Flash Controller supports several protection mechanisms against accidental program and erasure, plus factory serialization and read protection.

### Non-Volatile Data Storage

The nonvolatile data storage (NVDS) uses a hybrid hardware/software scheme to implement a byte programmable data memory and is capable of over 100,000 write cycles.

**Note:** Devices with 8KB of Flash memory do not include the NVDS feature.

### Interrupt Controller

The Z8 Encore! XP F082A Series products support up to 20 interrupts. These interrupts consist of 8 internal peripheral interrupts and 12 general-purpose I/O pin interrupt sources. The interrupts have three levels of programmable interrupt priority.

### **Reset Controller**

The Z8 Encore! XP F082A Series products can be reset using the RESET pin, Power-On Reset, Watchdog Timer (WDT) time-out, STOP Mode exit, or Voltage Brown-Out (VBO)

| Signal Mnemonic     | I/O     | Description                                                                                                                                                                                                                                                                 |

|---------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog              |         |                                                                                                                                                                                                                                                                             |

| ANA[7:0]            | I       | Analog Port. These signals are used as inputs to the analog-to-digital converter (ADC).                                                                                                                                                                                     |

| VREF                | I/O     | Analog-to-digital converter reference voltage input, or buffered output for internal reference.                                                                                                                                                                             |

| Low-Power Operation | onal Ar | nplifier (LPO)                                                                                                                                                                                                                                                              |

| AMPINP/AMPINN       | I       | LPO inputs. If enabled, these pins drive the positive and negative amplifier inputs respectively.                                                                                                                                                                           |

| AMPOUT              | 0       | LPO output. If enabled, this pin is driven by the on-chip LPO.                                                                                                                                                                                                              |

| Oscillators         |         |                                                                                                                                                                                                                                                                             |

| XIN                 | I       | External Crystal Input. This is the input pin to the crystal oscillator. A crystal can be connected between it and the $X_{OUT}$ pin to form the oscillator. In addition, this pin is used with external RC networks or external clock drivers to provide the system clock. |

| X <sub>OUT</sub>    | 0       | External Crystal Output. This pin is the output of the crystal oscillator. A crystal can be connected between it and the <b>XIN</b> pin to form the oscillator.                                                                                                             |

| Clock Input         |         |                                                                                                                                                                                                                                                                             |

| CLKIN               | I       | Clock Input Signal. This pin may be used to input a TTL-level signal to be used as the system clock.                                                                                                                                                                        |

| LED Drivers         |         |                                                                                                                                                                                                                                                                             |

| LED                 | 0       | Direct LED drive capability. All port C pins have the capability to drive an LED without any other external components. These pins have programma ble drive strengths set by the GPIO block.                                                                                |

| On-Chip Debugger    |         |                                                                                                                                                                                                                                                                             |

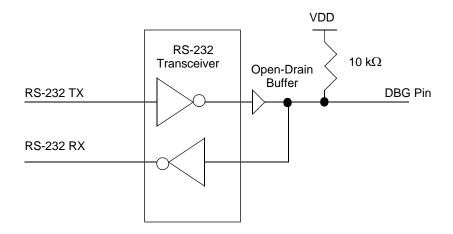

| DBG                 | I/O     | Debug. This signal is the control and data input and output to and from the On-Chip Debugger.                                                                                                                                                                               |

|                     |         | <b>Caution:</b> The DBG pin is open-drain and requires a pull-up resistor to ensure proper operation.                                                                                                                                                                       |

#### **Table 2. Signal Descriptions (Continued)**

replaced by  $AV_{DD}$  and  $AV_{SS}$ . 2. The  $AV_{DD}$  and  $AV_{SS}$  signals are available only in 28-pin packages with ADC. They are replaced by PB6 and PB7 on 28-pin packages without ADC.

| Symbol<br>Mnemonic | Direction | Reset<br>Direction            | Active<br>Low<br>or<br>Active<br>High | Tristate<br>Output   | Internal<br>Pull-up or<br>Pull-down                           | Schmitt-<br>Trigger<br>Input | Open Drain<br>Output                                 | 5 V<br>Tolerance                          |

|--------------------|-----------|-------------------------------|---------------------------------------|----------------------|---------------------------------------------------------------|------------------------------|------------------------------------------------------|-------------------------------------------|

| AVDD               | N/A       | N/A                           | N/A                                   | N/A                  | N/A                                                           | N/A                          | N/A                                                  | N/A                                       |

| AVSS               | N/A       | N/A                           | N/A                                   | N/A                  | N/A                                                           | N/A                          | N/A                                                  | NA                                        |

| DBG                | I/O       | I                             | N/A                                   | Yes                  | Yes                                                           | Yes                          | Yes                                                  | No                                        |

| PA[7:0]            | I/O       | I                             | N/A                                   | Yes                  | Programma-<br>ble<br>Pull-up                                  | Yes                          | Yes,<br>Programma-<br>ble                            | PA[7:2]<br>unless pul-<br>lups<br>enabled |

| PB[7:0]            | I/O       | I                             | N/A                                   | Yes                  | Programma-<br>ble<br>Pull-up                                  | Yes                          | Yes,<br>Programma-<br>ble                            | PB[7:6]<br>unless pul-<br>lups<br>enabled |

| PC[7:0]            | I/O       | I                             | N/A                                   | Yes                  | Programma-<br>ble<br>Pull-up                                  | Yes                          | Yes,<br>Programma-<br>ble                            | PC[7:3]<br>unless pul-<br>lups<br>enabled |

| RESET/<br>PD0      | I/O       | I/O<br>(defaults to<br>RESET) | Low (in<br>Reset<br>mode)             | Yes<br>(PD0<br>only) | Programma-<br>ble for PD0;<br>alw <u>ays on f</u> or<br>RESET | Yes                          | Programma-<br>ble for PD0;<br>always on for<br>RESET | Yes,<br>unless pul-<br>lups<br>enabled    |

| VDD                | N/A       | N/A                           | N/A                                   | N/A                  |                                                               |                              | N/A                                                  | N/A                                       |

| VSS                | N/A       | N/A                           | N/A                                   | N/A                  |                                                               |                              | N/A                                                  | N/A                                       |

### Table 3. Pin Characteristics (20- and 28-pin Devices)

**Note:** PB6 and PB7 are available only in those devices without ADC.

|                                                       | Reset Characteristics and Latency                      |            |                                                               |  |  |

|-------------------------------------------------------|--------------------------------------------------------|------------|---------------------------------------------------------------|--|--|

| Reset Type                                            | Control Registers                                      | eZ8<br>CPU | Reset Latency (Delay)                                         |  |  |

| System Reset                                          | Reset (as applicable)                                  | Reset      | 66 Internal Precision Oscillator Cycles                       |  |  |

| System Reset with Crystal Oscillator Enabled          | Reset (as applicable)                                  | Reset      | 5000 Internal Precision Oscillator Cycles                     |  |  |

| Stop Mode Recovery                                    | Unaffected, except<br>WDT_CTL and<br>OSC_CTL registers | Reset      | 66 Internal Precision Oscillator Cycles<br>+ IPO startup time |  |  |

| Stop Mode Recovery with<br>Crystal Oscillator Enabled | Unaffected, except<br>WDT_CTL and<br>OSC_CTL registers | Reset      | 5000 Internal Precision Oscillator Cycles                     |  |  |

#### Table 8. Reset and Stop Mode Recovery Characteristics and Latency

During a System Reset or Stop Mode Recovery, the Internal Precision Oscillator requires 4  $\mu$ s to start up. Then the Z8 Encore! XP F082A Series device is held in Reset for 66 cycles of the Internal Precision Oscillator. If the crystal oscillator is enabled in the Flash option bits, this reset period is increased to 5000 IPO cycles. When a reset occurs because of a low voltage condition or Power-On Reset (POR), this delay is measured from the time that the supply voltage first exceeds the POR level. If the external pin reset remains asserted at the end of the reset period, the device remains in reset until the pin is deasserted.

At the beginning of Reset, all GPIO pins are configured as inputs with pull-up resistor disabled, except PD0 (or PA2 on 8-pin devices) which is shared with the reset pin. On reset, the PD0 is configured as a bidirectional open-drain reset. The pin is internally driven low during port reset, after which the user code may reconfigure this pin as a general purpose output.

During Reset, the eZ8 CPU and on-chip peripherals are idle; however, the on-chip crystal oscillator and Watchdog Timer oscillator continue to run.

Upon Reset, control registers within the Register File that have a defined Reset value are loaded with their reset values. Other control registers (including the Stack Pointer, Register Pointer and Flags) and general-purpose RAM are undefined following Reset. The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset vector address.

As the control registers are reinitialized by a system reset, the system clock after reset is always the IPO. The software must reconfigure the oscillator control block, such that the correct system clock source is enabled and selected.

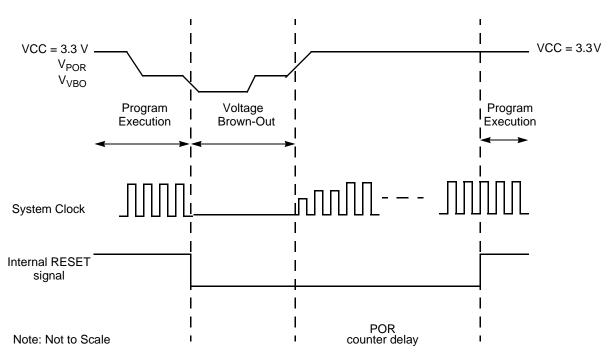

Figure 6. Voltage Brown-Out Reset Operation

The POR level is greater than the VBO level by the specified hysteresis value. This ensures that the device undergoes a Power-On Reset after recovering from a VBO condition.

## Watchdog Timer Reset

If the device is operating in NORMAL or HALT Mode, the Watchdog Timer can initiate a System Reset at time-out if the WDT\_RES Flash option bit is programmed to 1, i.e., the unprogrammed state of the WDT\_RES Flash option bit. If the bit is programmed to 0, it configures the Watchdog Timer to cause an interrupt, not a System Reset, at time-out.

The WDT bit in the Reset Status (RSTSTAT) Register is set to signify that the reset was initiated by the Watchdog Timer.

## **External Reset Input**

The  $\overline{\text{RESET}}$  pin has a Schmitt-Triggered input and an internal pull-up resistor. Once the  $\overline{\text{RESET}}$  pin is asserted for a minimum of four system clock cycles, the device progresses through the System Reset sequence. Because of the possible asynchronicity of the system clock and reset signals, the required reset duration may be as short as three clock periods

PA0 and PA6 contain two different timer functions, a timer input and a complementary timer output. Both of these functions require the same GPIO configuration, the selection between the two is based on the timer mode. See **the** <u>Timers</u> **chapter on page 70** for more details.

**Caution:** For pins with multiple alternate functions, Zilog recommends writing to the AFS1 and AFS2 subregisters before enabling the alternate function via the AF subregister. As a result, spurious transitions through unwanted alternate function modes will be prevented.

# **Direct LED Drive**

The Port C pins provide a current sinked output capable of driving an LED without requiring an external resistor. The output sinks current at programmable levels of 3 mA, 7 mA, 13 mA and 20 mA. This mode is enabled through the LED control registers. The LED Drive Enable (LEDEN) Register turns on the drivers. The LED Drive Level (LEDLVLH and LEDLVLL) registers select the sink current.

For correct function, the LED anode must be connected to  $V_{DD}$  and the cathode to the GPIO pin. Using all Port C pins in LED drive mode with maximum current may result in excessive total current. See **the** <u>Electrical Characteristics</u> chapter on page 226 for the maximum total current for the applicable package.

# **Shared Reset Pin**

On the 20- and 28-pin devices, the PD0 pin shares function with a bidirectional reset pin. Unlike all other I/O pins, this pin does not default to GPIO function on power-up. This pin acts as a bidirectional input/open-drain output reset until the software reconfigures it. The PD0 pin is an output-only open drain when in GPIO mode. There are no pull-up, High Drive, or Stop Mode Recovery source features associated with the PD0 pin.

On the 8-pin product versions, the reset pin is shared with PA2, but the pin is not limited to output-only when in GPIO mode.

**Caution:** If PA2 on the 8-pin product is reconfigured as an input, ensure that no external stimulus drives the pin low during any reset sequence. Since PA2 returns to its **RESET** alternate function during system resets, driving it Low holds the chip in a reset state until the pin is released.

| Port   | Pin | Mnemonic                      | Alternate Function<br>Description         | Alternate<br>Function Select<br>Register AFS1 | Alternate<br>Function<br>Select<br>Register<br>AFS2 |

|--------|-----|-------------------------------|-------------------------------------------|-----------------------------------------------|-----------------------------------------------------|

| Port A | PA0 | TOIN                          | Timer 0 Input                             | AFS1[0]: 0                                    | AFS2[0]: 0                                          |

|        |     | Reserved                      |                                           | AFS1[0]: 0                                    | AFS2[0]: 1                                          |

|        |     | Reserved                      |                                           | AFS1[0]: 1                                    | AFS2[0]: 0                                          |

|        |     | TOOUT                         | Timer 0 Output Complement                 | AFS1[0]: 1                                    | AFS2[0]: 1                                          |

|        | PA1 | TOOUT                         | Timer 0 Output                            | AFS1[1]: 0                                    | AFS2[1]: 0                                          |

|        |     | Reserved                      |                                           | AFS1[1]: 0                                    | AFS2[1]: 1                                          |

|        |     | CLKIN                         | External Clock Input                      | AFS1[1]: 1                                    | AFS2[1]: 0                                          |

|        |     | Analog Functions <sup>1</sup> | ADC Analog Input/V <sub>REF</sub>         | AFS1[1]: 1                                    | AFS2[1]: 1                                          |

|        | PA2 | DE0                           | UART 0 Driver Enable                      | AFS1[2]: 0                                    | AFS2[2]: 0                                          |

|        |     | RESET                         | External Reset                            | AFS1[2]: 0                                    | AFS2[2]: 1                                          |

|        |     | T1OUT                         | Timer 1 Output                            | AFS1[2]: 1                                    | AFS2[2]: 0                                          |

|        |     | Reserved                      |                                           | AFS1[2]: 1                                    | AFS2[2]: 1                                          |

|        | PA3 | CTS0                          | UART 0 Clear to Send                      | AFS1[3]: 0                                    | AFS2[3]: 0                                          |

|        |     | COUT                          | Comparator Output                         | AFS1[3]: 0                                    | AFS2[3]: 1                                          |

|        |     | T1IN                          | Timer 1 Input                             | AFS1[3]: 1                                    | AFS2[3]: 0                                          |

|        |     | Analog Functions <sup>2</sup> | ADC Analog Input/LPO Input (P)            | AFS1[3]: 1                                    | AFS2[3]: 1                                          |

|        | PA4 | RXD0                          | UART 0 Receive Data                       | AFS1[4]: 0                                    | AFS2[4]: 0                                          |

|        |     | Reserved                      |                                           | AFS1[4]: 0                                    | AFS2[4]: 1                                          |

|        |     | Reserved                      |                                           | AFS1[4]: 1                                    | AFS2[4]: 0                                          |

|        |     | Analog Functions <sup>2</sup> | ADC/Comparator Input (N)/LPO<br>Input (N) | AFS1[4]: 1                                    | AFS2[4]: 1                                          |

|        | PA5 | TXD0                          | UART 0 Transmit Data                      | AFS1[5]: 0                                    | AFS2[5]: 0                                          |

|        |     | T1OUT                         | Timer 1 Output Complement                 | AFS1[5]: 0                                    | AFS2[5]: 1                                          |

|        |     | Reserved                      |                                           | AFS1[5]: 1                                    | AFS2[5]: 0                                          |

|        |     | Analog Functions <sup>2</sup> | ADC/Comparator Input (P) LPO<br>Output    | AFS1[5]: 1                                    | AFS2[5]: 1                                          |

### Table 16. Port Alternate Function Mapping (8-Pin Parts)

Notes:

1. Analog functions include ADC inputs, ADC reference, comparator inputs and LPO ports.

2. The alternate function selection must be enabled; see the Port A–D Alternate Function Subregisters (PxAF) section on page 47 for details.

# LED Drive Level Low Register

The LED Drive Level registers contain two control bits for each Port C pin (Table 33). These two bits select between four programmable drive levels. Each pin is individually programmable.

| Bit     | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6    | 5 | 4 | 3 | 2 | 1   | 0 |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---|---|---|---|-----|---|

| Field   | LEDLVLL[7:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |   |   |   |   |     |   |

| RESET   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0    | 0 | 0 | 0 | 0 | 0   | 0 |

| R/W     | R/W         R/W <th>R/W</th> |      |   |   |   |   | R/W |   |

| Address |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | F84H |   |   |   |   |     |   |

### Table 33. LED Drive Level Low Register (LEDLVLL)

| Bit           | Description                                                                             |

|---------------|-----------------------------------------------------------------------------------------|

| [7:0]         | LED Level Low Bit                                                                       |

| LEDLVLLx      | {LEDLVLH, LEDLVLL} select one of four programmable current drive levels for each Port C |

|               | pin.                                                                                    |

|               | 00 = 3mA                                                                                |

|               | 01 = 7 mA                                                                               |

|               | 10 = 13mA                                                                               |

|               | 11 = 20mA                                                                               |

| Note: x indic | cates the specific GPIO port pin number (7–0).                                          |

# Universal Asynchronous Receiver/ Transmitter

The universal asynchronous receiver/transmitter (UART) is a full-duplex communication channel capable of handling asynchronous data transfers. The UART uses a single 8-bit data mode with selectable parity. Features of the UART include:

- 8-bit asynchronous data transfer

- Selectable even- and odd-parity generation and checking

- Option of one or two STOP bits

- Separate transmit and receive interrupts

- Framing, parity, overrun and break detection

- Separate transmit and receive enables

- 16-bit baud rate generator (BRG)

- Selectable MULTIPROCESSOR (9-bit) Mode with three configurable interrupt schemes

- Baud rate generator (BRG) can be configured and used as a basic 16-bit timer

- Driver enable (DE) output for external bus transceivers

# Architecture

The UART consists of three primary functional blocks: transmitter, receiver and baud rate generator. The UART's transmitter and receiver function independently, but employ the same baud rate and data format. Figure 10 displays the UART architecture.

The UART is now configured for interrupt-driven data reception. When the UART Receiver interrupt is detected, the associated interrupt service routine (ISR) performs the following:

- 1. Checks the UART Status 0 Register to determine the source of the interrupt error, break, or received data.

- 2. Reads the data from the UART Receive Data Register if the interrupt was because of data available. If operating in MULTIPROCESSOR (9-bit) Mode, further actions may be required depending on the MULTIPROCESSOR Mode bits MPMD[1:0].

- 3. Clears the UART Receiver interrupt in the applicable Interrupt Request Register.

- 4. Executes the IRET instruction to return from the interrupt-service routine and await more data.

# Clear To Send (CTS) Operation

The CTS pin, if enabled by the CTSE bit of the UART Control 0 Register, performs flow control on the outgoing transmit datastream. The Clear To Send ( $\overline{\text{CTS}}$ ) input pin is sampled one system clock before beginning any new character transmission. To delay transmission of the next data character, an external receiver must deassert  $\overline{\text{CTS}}$  at least one system clock cycle before a new data transmission begins. For multiple character transmissions, this action is typically performed during Stop Bit transmission. If  $\overline{\text{CTS}}$  deasserts in the middle of a character transmission, the current character is sent completely.

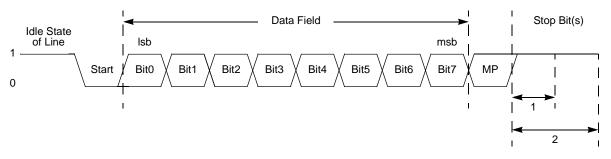

# MULTIPROCESSOR (9-bit) Mode

The UART features a MULTIPROCESSOR (9-bit) Mode that uses an extra (9th) bit for selective communication when a number of processors share a common UART bus. In MULTIPROCESSOR Mode (also referred to as *9-bit Mode*), the multiprocessor bit (MP) is transmitted immediately following the 8-bits of data and immediately preceding the Stop bit(s) as displayed in Figure 13. The character format is:

Figure 13. UART Asynchronous MULTIPROCESSOR Mode Data Format

Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

125

Figure 19. Analog-to-Digital Converter Block Diagram

# Operation

In both SINGLE-ENDED and DIFFERENTIAL modes, the effective output of the ADC is an 11-bit, signed, two's complement digital value. In DIFFERENTIAL Mode, the ADC can output values across the entire 11-bit range, from -1024 to +1023. In SINGLE-ENDED Mode, the output generally ranges from 0 to +1023, but offset errors can cause small negative values. **Caution:** The byte at each address of the Flash memory cannot be programmed (any bits written to 0) more than twice before an erase cycle occurs. Doing so may result in corrupted data at the target byte.

### **Page Erase**

The Flash memory can be erased one page (512 bytes) at a time. Page Erasing the Flash memory sets all bytes in that page to the value FFH. The Flash Page Select Register identifies the page to be erased. Only a page residing in an unprotected sector can be erased. With the Flash Controller unlocked and the active page set, writing the value 95h to the Flash Control Register initiates the Page Erase operation. While the Flash Controller executes the Page Erase operation, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. The eZ8 CPU resumes operation after the Page Erase operation completes. If the Page Erase operation is performed using the On-Chip Debugger, poll the Flash Status Register to determine when the Page Erase operation is complete. When the Page Erase is complete, the Flash Controller returns to its locked state.

### **Mass Erase**

The Flash memory can also be Mass Erased using the Flash Controller, but only by using the On-Chip Debugger. Mass Erasing the Flash memory sets all bytes to the value FFH. With the Flash Controller unlocked and the Mass Erase successfully enabled, writing the value 63H to the Flash Control Register initiates the Mass Erase operation. While the Flash Controller executes the Mass Erase operation, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. Using the On-Chip Debugger, poll the Flash Status Register to determine when the Mass Erase operation is complete. When the Mass Erase is complete, the Flash Controller returns to its locked state.

## **Flash Controller Bypass**

The Flash Controller can be bypassed and the control signals for the Flash memory brought out to the GPIO pins. Bypassing the Flash Controller allows faster Row Programming algorithms by controlling the Flash programming signals directly.

Row programming is recommended for gang programming applications and large volume customers who do not require in-circuit initial programming of the Flash memory. Page Erase operations are also supported when the Flash Controller is bypassed.

For more information about bypassing the Flash Controller, refer to the <u>Third-Party Flash</u> <u>Programming Support for Z8 Encore! MCUs Application Note (AN0117)</u>, which is available for download on <u>www.zilog.com</u>.

Figure 25. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface; #2 of 2

# **DEBUG Mode**

The operating characteristics of the devices in DEBUG Mode are:

- The eZ8 CPU fetch unit stops, idling the eZ8 CPU, unless directed by the OCD to execute specific instructions

- The system clock operates unless in STOP Mode

- All enabled on-chip peripherals operate unless in STOP Mode

- Automatically exits HALT Mode

- Constantly refreshes the Watchdog Timer, if enabled

### **Entering DEBUG Mode**

The operating characteristics of the devices entering DEBUG Mode are:

- The device enters DEBUG Mode after the eZ8 CPU executes a BRK (Breakpoint) instruction

- If the DBG pin is held Low during the final clock cycle of system reset, the part enters DEBUG Mode immediately (20-/28-pin products only)

**Note:** Holding the DBG pin Low for an additional 5000 (minimum) clock cycles after reset (making sure to account for any specified frequency error if using an internal oscillator) prevents a false interpretation of an Autobaud sequence (see the <u>OCD Auto-Baud Detector/Generator</u> section on page 183).

| Mnemonic | Operands    | Instruction                                             |

|----------|-------------|---------------------------------------------------------|

| BCLR     | bit, dst    | Bit Clear                                               |

| BIT      | p, bit, dst | Bit Set or Clear                                        |

| BSET     | bit, dst    | Bit Set                                                 |

| BSWAP    | dst         | Bit Swap                                                |

| CCF      | —           | Complement Carry Flag                                   |

| RCF      | —           | Reset Carry Flag                                        |

| SCF      | —           | Set Carry Flag                                          |

| ТСМ      | dst, src    | Test Complement Under Mask                              |

| ТСМХ     | dst, src    | Test Complement Under Mask using Extended<br>Addressing |

| ТМ       | dst, src    | Test Under Mask                                         |

| TMX      | dst, src    | Test Under Mask using Extended Addressing               |

#### Table 121. Bit Manipulation Instructions

#### Table 122. Block Transfer Instructions

| Mnemonic | Operands | Instruction                                                             |

|----------|----------|-------------------------------------------------------------------------|

| LDCI     | dst, src | Load Constant to/from Program Memory and Auto-<br>Increment Addresses   |

| LDEI     | dst, src | Load External Data to/from Data Memory and Auto-<br>Increment Addresses |

#### Table 123. CPU Control Instructions

| Mnemonic | Operands | Instruction           |

|----------|----------|-----------------------|

| ATM      |          | Atomic Execution      |

| CCF      | —        | Complement Carry Flag |

| DI       | —        | Disable Interrupts    |

| EI       | —        | Enable Interrupts     |

| HALT     | —        | Halt Mode             |

| NOP      | —        | No Operation          |

| Assembly        | Symbolic Operation                  | Address<br>Mode |       | _ Opcode(s) | Flags |   |   |   |   | Fetch<br>Cycle | Instr. |            |

|-----------------|-------------------------------------|-----------------|-------|-------------|-------|---|---|---|---|----------------|--------|------------|

| Mnemonic        |                                     | dst             | src   | (Hex)       | С     | Ζ | S | v | D | н              | S      | Cycle<br>s |

| LDX dst, src    | $dst \leftarrow src$                | r               | ER    | 84          | -     | - | - | - | _ | -              | 3      | 2          |

|                 |                                     | lr              | ER    | 85          |       |   |   |   |   |                | 3      | 3          |

|                 |                                     | R               | IRR   | 86          | -     |   |   |   |   |                | 3      | 4          |

|                 |                                     | IR              | IRR   | 87          |       |   |   |   |   |                | 3      | 5          |

|                 |                                     | r               | X(rr) | 88          |       |   |   |   |   |                | 3      | 4          |

|                 |                                     | X(rr)           | r     | 89          |       |   |   |   |   |                | 3      | 4          |

|                 |                                     | ER              | r     | 94          |       |   |   |   |   |                | 3      | 2          |

|                 |                                     | ER              | lr    | 95          |       |   |   |   |   |                | 3      | 3          |

|                 |                                     | IRR             | R     | 96          |       |   |   |   |   |                | 3      | 4          |

|                 |                                     | IRR             | IR    | 97          | -     |   |   |   |   |                | 3      | 5          |

|                 |                                     | ER              | ER    | E8          | -     |   |   |   |   |                | 4      | 2          |

|                 |                                     | ER              | IM    | E9          | -     |   |   |   |   |                | 4      | 2          |

| LEA dst, X(src) | $dst \gets src + X$                 | r               | X(r)  | 98          | _     | - | _ | - | - | _              | 3      | 3          |

|                 |                                     | rr              | X(rr) | 99          |       |   |   |   |   |                | 3      | 5          |

| MULT dst        | dst[15:0] ←<br>dst[15:8] * dst[7:0] | RR              |       | F4          | _     | - | _ | - | - | _              | 2      | 8          |

| NOP             | No operation                        |                 |       | 0F          | -     | - | - | - | - | -              | 1      | 2          |

| OR dst, src     | $dst \gets dst  OR  src$            | r               | r     | 42          | _     | * | * | 0 | _ | _              | 2      | 3          |

|                 |                                     | r               | lr    | 43          |       |   |   |   |   |                | 2      | 4          |

|                 |                                     | R               | R     | 44          |       |   |   |   |   |                | 3      | 3          |

|                 |                                     | R               | IR    | 45          |       |   |   |   |   |                | 3      | 4          |

|                 |                                     | R               | IM    | 46          | -     |   |   |   |   |                | 3      | 3          |

|                 |                                     | IR              | IM    | 47          | -     |   |   |   |   |                | 3      | 4          |

### Table 128. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation: \* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 =Set to 1.

|                   |                                       |         | -40°C to +<br>otherwise s |            |       |                                                                                       |  |  |

|-------------------|---------------------------------------|---------|---------------------------|------------|-------|---------------------------------------------------------------------------------------|--|--|

| Symbol            | Parameter                             | Minimum | Typical                   | Maximum    | Units | Conditions                                                                            |  |  |

| V <sub>OH1</sub>  | High Level Output<br>Voltage          | 2.4     | -                         | -          | V     | I <sub>OH</sub> = -2 mA; V <sub>DD</sub> = 3.0 V<br>High Output Drive disabled.       |  |  |

| V <sub>OL2</sub>  | Low Level Output<br>Voltage           | _       | -                         | 0.6        | V     | I <sub>OL</sub> = 20 mA; V <sub>DD</sub> = 3.3V<br>High Output Drive enabled.         |  |  |

| V <sub>OH2</sub>  | High Level Output<br>Voltage          | 2.4     | _                         | _          | V     | I <sub>OH</sub> = -20 mA; V <sub>DD</sub> = 3.3V<br>High Output Drive enabled.        |  |  |

| I <sub>IH</sub>   | Input Leakage Cur-<br>rent            | _       | <u>+</u> 0.002            | <u>+</u> 5 | μA    | $V_{IN} = V_{DD}$<br>$V_{DD} = 3.3 V;$                                                |  |  |

| I <sub>IL</sub>   | Input Leakage Cur-<br>rent            | -       | <u>+</u> 0.007            | <u>+</u> 5 | μA    | $V_{IN} = V_{SS}$<br>$V_{DD} = 3.3V;$                                                 |  |  |

| I <sub>TL</sub>   | Tristate Leakage<br>Current           | -       | -                         | <u>+</u> 5 | μA    |                                                                                       |  |  |

| I <sub>LED</sub>  | Controlled Current<br>Drive           | 1.8     | 3                         | 4.5        | mA    | $\{AFS2, AFS1\} = \{0, 0\}$                                                           |  |  |

|                   |                                       | 2.8     | 7                         | 10.5       | mA    | $\{AFS2, AFS1\} = \{0, 1\}$                                                           |  |  |

|                   |                                       | 7.8     | 13                        | 19.5       | mA    | ${AFS2,AFS1} = {1,0}$                                                                 |  |  |

|                   |                                       | 12      | 20                        | 30         | mA    | ${AFS2,AFS1} = {1,1}$                                                                 |  |  |

| C <sub>PAD</sub>  | GPIO Port Pad<br>Capacitance          | -       | 8.0 <sup>2</sup>          | -          | pF    |                                                                                       |  |  |

| C <sub>XIN</sub>  | XIN Pad Capaci-<br>tance              | -       | 8.0 <sup>2</sup>          | _          | pF    |                                                                                       |  |  |

| C <sub>XOUT</sub> | X <sub>OUT</sub> Pad Capaci-<br>tance | -       | 9.5 <sup>2</sup>          | _          | pF    |                                                                                       |  |  |

| I <sub>PU</sub>   | Weak Pull-up Cur-<br>rent             | 30      | 100                       | 350        | μA    | V <sub>DD</sub> = 3.0 V–3.6 V                                                         |  |  |

| V <sub>RAM</sub>  | RAM Data Reten-<br>tion Voltage       | TBD     |                           |            | V     | Voltage at which RAM retains<br>static values; no reading or writ-<br>ing is allowed. |  |  |

### Table 131. DC Characteristics (Continued)

Notes:

1. This condition excludes all pins that have on-chip pull-ups, when driven Low.

2. These values are provided for design guidance only and are not tested in production.

# **On-Chip Peripheral AC and DC Electrical Characteristics**

Table 135 tabulates the electrical characteristics of the POR and VBO blocks.

#### Table 135. Power-On Reset and Voltage Brown-Out Electrical Characteristics and Timing

|                  |                                                                  | T <sub>A</sub> = | –40°C to +′          |         |       |                                                                                                             |

|------------------|------------------------------------------------------------------|------------------|----------------------|---------|-------|-------------------------------------------------------------------------------------------------------------|

| Symbol           | Parameter                                                        | Minimum          | Typical <sup>1</sup> | Maximum | Units | Conditions                                                                                                  |

| V <sub>POR</sub> | Power-On Reset Voltage Thresh-<br>old                            | 2.20             | 2.45                 | 2.70    | V     | $V_{DD} = V_{POR}$                                                                                          |

| $V_{VBO}$        | Voltage Brown-Out Reset Voltage<br>Threshold                     | 2.15             | 2.40                 | 2.65    | V     | $V_{DD} = V_{VBO}$                                                                                          |

|                  | V <sub>POR</sub> to V <sub>VBO</sub> hysteresis                  |                  | 50                   | 75      | mV    |                                                                                                             |

|                  | Starting V <sub>DD</sub> voltage to ensure valid Power-On Reset. | -                | $V_{SS}$             | -       | V     |                                                                                                             |

| T <sub>ANA</sub> | Power-On Reset Analog Delay                                      | -                | 70                   | -       | μs    | V <sub>DD</sub> > V <sub>POR</sub> ;<br>T <sub>POR</sub> Digital<br>Reset delay<br>follows T <sub>ANA</sub> |

| T <sub>POR</sub> | Power-On Reset Digital Delay                                     |                  | 16                   |         | μs    | 66 Internal<br>Precision<br>Oscillator<br>cycles + IPO<br>startup time<br>(T <sub>IPOST</sub> )             |

| T <sub>POR</sub> | Power-On Reset Digital Delay                                     |                  | 1                    |         | ms    | 5000 Internal<br>Precision<br>Oscillator<br>cycles                                                          |

| T <sub>SMR</sub> | Stop Mode Recovery with crystal oscillator disabled              |                  | 16                   |         | μs    | 66 Internal<br>Precision<br>Oscillator<br>cycles                                                            |

| T <sub>SMR</sub> | Stop Mode Recovery with crystal oscillator enabled               |                  | 1                    |         | ms    | 5000 Internal<br>Precision<br>Oscillator<br>cycles                                                          |

| T <sub>VBO</sub> | Voltage Brown-Out Pulse Rejec-<br>tion Period                    | _                | 10                   | _       | μs    | Period of time<br>in which $V_{DD} < V_{VBO}$ without<br>generating a<br>Reset.                             |

Note: Data in the typical column is from characterization at 3.3 V and 30°C. These values are provided for design guidance only and are not tested in production.

|                   |                   | V <sub>DD</sub> | = 2.7 V to   |            |       |                                                                             |  |

|-------------------|-------------------|-----------------|--------------|------------|-------|-----------------------------------------------------------------------------|--|

| Symbol            | Parameter         | Minimum         | Typical      | Maximum    | Units | Conditions                                                                  |  |

| T <sub>AERR</sub> | Temperature Error |                 | <u>+</u> 0.5 | <u>+</u> 2 | °C    | Over the range +20°C<br>to +30°C (as mea-<br>sured by ADC). <sup>1</sup>    |  |

|                   |                   |                 | <u>+</u> 1   | <u>+</u> 5 | °C    | Over the range +0°C<br>to +70°C (as mea-<br>sured by ADC).                  |  |

|                   |                   |                 | <u>+</u> 2   | <u>+</u> 7 | °C    | Over the range +0°C<br>to +105°C (as mea-<br>sured by ADC).                 |  |

|                   |                   |                 | <u>+</u> 7   |            | °C    | Over the range –40°C<br>to +105°C (as mea-<br>sured by ADC).                |  |

| t <sub>WAKE</sub> | Wakeup Time       |                 | 80           | 100        | μs    | Time required for Tem<br>perature Sensor to<br>stabilize after<br>enabling. |  |

#### Table 142. Temperature Sensor Electrical Characteristics

Note: Devices are factory calibrated at for maximal accuracy between +20°C and +30°C, so the sensor is maximally accurate in that range. User recalibration for a different temperature range is possible and increases accuracy near the new calibration point.

LD 210 LDC 210 LDCI 209, 210 LDE 210 **LDEI 209** LDX 210 LEA 210 logical 210 **MULT 208 NOP 209** OR 210 **ORX 210 POP 210** POPX 210 program control 211 **PUSH 210** PUSHX 210 RCF 209, 210 **RET 211** RL 211 **RLC 211** rotate and shift 211 RR 211 **RRC 211 SBC 208** SCF 209, 210 SRA 211 SRL 211 **SRP 210 STOP 210 SUB 208 SUBX 208 SWAP 211 TCM 209 TCMX 209** TM 209 TMX 209 **TRAP 211** Watchdog Timer refresh 210 **XOR 210 XORX 210** instructions, eZ8 classes of 207 interrupt control register 69 interrupt controller 55

architecture 55 interrupt assertion types 58 interrupt vectors and priority 58 operation 57 register definitions 60 software interrupt assertion 59 interrupt edge select register 67 interrupt request 0 register 60 interrupt request 1 register 61 interrupt request 2 register 62 interrupt return 211 interrupt vector listing 55 interrupts **UART 108** IR 206 Ir 206 IrDA architecture 120 block diagram 120 control register definitions 123 operation 120 receiving data 122 transmitting data 121 **IRET 211** IRQ0 enable high and low bit registers 62 IRQ1 enable high and low bit registers 64 IRQ2 enable high and low bit registers 65 **IRR 206** Irr 206

# J

JP 211 jump, conditional, relative, and relative conditional 211

# L

LD 210 LDC 210 LDCI 209, 210 LDE 210 LDEI 209, 210 LDX 210 259