Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT           |

| Number of I/O              | 25                                                        |

| Program Memory Size        | 2KB (2K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | 64 x 8                                                    |

| RAM Size                   | 512 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f021asj020sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| Revision History                                                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| List of Figures                                                                                                                                                                                        |

| List of Tables                                                                                                                                                                                         |

| Overview1Features1Part Selection Guide2Block Diagram3CPU and Peripheral Overview410-Bit Analog-to-Digital Converter4Low-Power Operational Amplifier4Internal Precision Oscillator5Temperature Sensor5  |

| Analog Comparator5External Crystal Oscillator5Low Voltage Detector5On-Chip Debugger5Universal Asynchronous Receiver/Transmitter5Timers5General-Purpose Input/Output6Direct LED Drive6Flash Controller6 |

| Non-Volatile Data Storage       6         Interrupt Controller       6         Reset Controller       6                                                                                                |

| Pin Description8Available Packages8Pin Configurations8Signal Descriptions10Pin Characteristics12                                                                                                       |

| Address Space15Register File15Program Memory15Data Memory17Flash Information Area17                                                                                                                    |

| Register Map                                                                                                                                                                                           |

| Address (Hex)    | Register Description                 | Mnemonic      | Reset (Hex) | Page       |

|------------------|--------------------------------------|---------------|-------------|------------|

| Timer 1          |                                      |               |             |            |

| F08              | Timer 1 High Byte                    | T1H           | 00          | <u>90</u>  |

| F09              | Timer 1 Low Byte                     | T1L           | 01          | <u>90</u>  |

| F0A              | Timer 1 Reload High Byte             | T1RH          | FF          | <u>91</u>  |

| Timer 1 (cont'd) |                                      |               |             |            |

| F0B              | Timer 1 Reload Low Byte              | T1RL          | FF          | <u>91</u>  |

| F0C              | Timer 1 PWM High Byte                | T1PWMH        | 00          | <u>92</u>  |

| F0D              | Timer 1 PWM Low Byte                 | T1PWML        | 00          | <u>92</u>  |

| F0E              | Timer 1 Control 0                    | T1CTL0        | 00          | <u>85</u>  |

| F0F              | Timer 1 Control 1                    | T1CTL1        | 00          | <u>86</u>  |

| F10–F6F          | Reserved                             | —             | XX          |            |

| UART             |                                      |               |             |            |

| F40              | UART Transmit/Receive Data registers | TXD, RXD      | XX          | <u>115</u> |

| F41              | UART Status 0 Register               | U0STAT0       | 00          | <u>114</u> |

| F42              | UART Control 0 Register              | U0CTL0        | 00          | <u>110</u> |

| F43              | UART Control 1 Register              | U0CTL1        | 00          | <u>110</u> |

| F44              | UART Status 1 Register               | U0STAT1       | 00          | <u>115</u> |

| F45              | UART Address Compare Register        | <b>U0ADDR</b> | 00          | <u>116</u> |

| F46              | UART Baud Rate High Byte Register    | U0BRH         | FF          | <u>117</u> |

| F47              | UART Baud Rate Low Byte Register     | U0BRL         | FF          | <u>117</u> |

| Analog-to-Digita | al Converter (ADC)                   |               |             |            |

| F70              | ADC Control 0                        | ADCCTL0       | 00          | <u>134</u> |

| F71              | ADC Control 1                        | ADCCTL1       | 80          | <u>136</u> |

| F72              | ADC Data High Byte                   | ADCD_H        | XX          | <u>137</u> |

| F73              | ADC Data Low Byte                    | ADCD_L        | XX          | 137        |

| F74–F7F          | Reserved                             |               | XX          |            |

| Low Power Con    | trol                                 |               |             |            |

| F80              | Power Control 0                      | PWRCTL0       | 80          | <u>34</u>  |

| F81              | Reserved                             | —             | XX          |            |

| LED Controller   |                                      |               |             |            |

| F82              | LED Drive Enable                     | LEDEN         | 00          | <u>53</u>  |

| F83              | LED Drive Level High Byte            | LEDLVLH       | 00          | <u>53</u>  |

| F84              | LED Drive Level Low Byte             | LEDLVLL       | 00          | <u>54</u>  |

### Table 7. Register File Address Map (Continued)

1. XX = Undefined.

2. Refer to the eZ8 CPU Core User Manual (UM0128).

| Address (Hex)           | Register Description    | Mnemonic | Reset (Hex) | Page       |

|-------------------------|-------------------------|----------|-------------|------------|

| F85                     | Reserved                | —        | XX          |            |

| <b>Oscillator Contr</b> | ol                      |          |             |            |

| F86                     | Oscillator Control      | OSCCTL   | A0          | <u>196</u> |

| F87–F8F                 | Reserved                | _        | XX          |            |

| Comparator 0            |                         |          |             |            |

| F90                     | Comparator 0 Control    | CMP0     | 14          | <u>141</u> |

| F91–FBF                 | Reserved                | —        | XX          |            |

| Interrupt Contro        | oller                   |          |             |            |

| FC0                     | Interrupt Request 0     | IRQ0     | 00          | <u>60</u>  |

| FC1                     | IRQ0 Enable High Bit    | IRQ0ENH  | 00          | <u>63</u>  |

| FC2                     | IRQ0 Enable Low Bit     | IRQ0ENL  | 00          | <u>63</u>  |

| FC3                     | Interrupt Request 1     | IRQ1     | 00          | <u>61</u>  |

| FC4                     | IRQ1 Enable High Bit    | IRQ1ENH  | 00          | <u>65</u>  |

| FC5                     | IRQ1 Enable Low Bit     | IRQ1ENL  | 00          | <u>65</u>  |

| FC6                     | Interrupt Request 2     | IRQ2     | 00          | <u>62</u>  |

| FC7                     | IRQ2 Enable High Bit    | IRQ2ENH  | 00          | <u>66</u>  |

| FC8                     | IRQ2 Enable Low Bit     | IRQ2ENL  | 00          | <u>67</u>  |

| FC9–FCC                 | Reserved                | —        | XX          |            |

| FCD                     | Interrupt Edge Select   | IRQES    | 00          | <u>68</u>  |

| FCE                     | Shared Interrupt Select | IRQSS    | 00          | <u>68</u>  |

| FCF                     | Interrupt Control       | IRQCTL   | 00          | <u>69</u>  |

| GPIO Port A             |                         |          |             |            |

| FD0                     | Port A Address          | PAADDR   | 00          | <u>44</u>  |

| FD1                     | Port A Control          | PACTL    | 00          | <u>46</u>  |

| FD2                     | Port A Input Data       | PAIN     | XX          | <u>46</u>  |

| FD3                     | Port A Output Data      | PAOUT    | 00          | <u>46</u>  |

| GPIO Port B             |                         |          |             |            |

| FD4                     | Port B Address          | PBADDR   | 00          | <u>44</u>  |

| FD5                     | Port B Control          | PBCTL    | 00          | <u>46</u>  |

| FD6                     | Port B Input Data       | PBIN     | XX          | <u>46</u>  |

| FD7                     | Port B Output Data      | PBOUT    | 00          | <u>46</u>  |

| GPIO Port C             |                         |          |             |            |

| FD8                     | Port C Address          | PCADDR   | 00          | 44         |

### Table 7. Register File Address Map (Continued)

1. XX = Undefined.

2. Refer to the eZ8 CPU Core User Manual (UM0128).

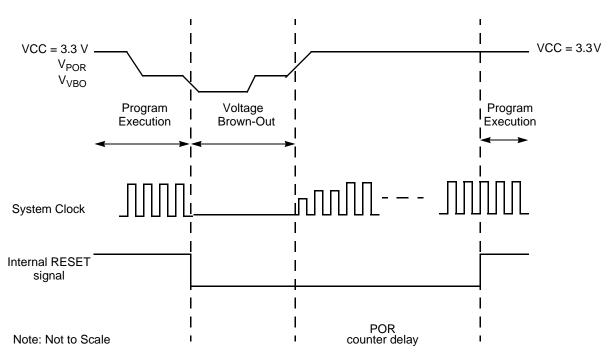

Figure 6. Voltage Brown-Out Reset Operation

The POR level is greater than the VBO level by the specified hysteresis value. This ensures that the device undergoes a Power-On Reset after recovering from a VBO condition.

### Watchdog Timer Reset

If the device is operating in NORMAL or HALT Mode, the Watchdog Timer can initiate a System Reset at time-out if the WDT\_RES Flash option bit is programmed to 1, i.e., the unprogrammed state of the WDT\_RES Flash option bit. If the bit is programmed to 0, it configures the Watchdog Timer to cause an interrupt, not a System Reset, at time-out.

The WDT bit in the Reset Status (RSTSTAT) Register is set to signify that the reset was initiated by the Watchdog Timer.

### **External Reset Input**

The  $\overline{\text{RESET}}$  pin has a Schmitt-Triggered input and an internal pull-up resistor. Once the  $\overline{\text{RESET}}$  pin is asserted for a minimum of four system clock cycles, the device progresses through the System Reset sequence. Because of the possible asynchronicity of the system clock and reset signals, the required reset duration may be as short as three clock periods

without initiating an interrupt (if enabled for that pin).

### Stop Mode Recovery Using the External RESET Pin

When the Z8 Encore! XP F082A Series device is in STOP Mode and the external **RESET** pin is driven Low, a system reset occurs. Because of a glitch filter operating on the **RESET** pin, the Low pulse must be greater than the minimum width specified, or it is ignored. See the <u>Electrical Characteristics</u> chapter on page 226 for details.

### Low Voltage Detection

In addition to the Voltage Brown-Out (VBO) Reset described above, it is also possible to generate an interrupt when the supply voltage drops below a user-selected value. For details about configuring the Low Voltage Detection (LVD) and the threshold levels available, see the <u>Trim Option Bits at Address 0003H (TLVD) Register</u> on page 166. The LVD function is available on the 8-pin product versions only.

When the supply voltage drops below the LVD threshold, the LVD bit of the Reset Status (RSTSTAT) Register is set to one. This bit remains one until the low-voltage condition goes away. Reading or writing this bit does not clear it. The LVD circuit can also generate an interrupt when so enabled, see the <u>GPIO Mode Interrupt Controller</u> chapter on page 55. The LVD bit is not latched; therefore, enabling the interrupt is the only way to guarantee detection of a transient low voltage event.

The LVD functionality depends on circuitry shared with the VBO block; therefore, disabling the VBO also disables the LVD.

### **Reset Register Definitions**

The following sections define the Reset registers.

#### **Reset Status Register**

The read-only Reset Status (RSTSTAT) Register, shown in Table 11, indicates the source of the most recent Reset event, indicates a Stop Mode Recovery event and indicates a Watchdog Timer time-out. Reading this register resets the upper four bits to 0. This register shares its address with the write-only Watchdog Timer Control Register.

Table 12 lists the bit settings for Reset and Stop Mode Recovery events.

PA0 and PA6 contain two different timer functions, a timer input and a complementary timer output. Both of these functions require the same GPIO configuration, the selection between the two is based on the timer mode. See **the** <u>Timers</u> **chapter on page 70** for more details.

**Caution:** For pins with multiple alternate functions, Zilog recommends writing to the AFS1 and AFS2 subregisters before enabling the alternate function via the AF subregister. As a result, spurious transitions through unwanted alternate function modes will be prevented.

### **Direct LED Drive**

The Port C pins provide a current sinked output capable of driving an LED without requiring an external resistor. The output sinks current at programmable levels of 3 mA, 7 mA, 13 mA and 20 mA. This mode is enabled through the LED control registers. The LED Drive Enable (LEDEN) Register turns on the drivers. The LED Drive Level (LEDLVLH and LEDLVLL) registers select the sink current.

For correct function, the LED anode must be connected to  $V_{DD}$  and the cathode to the GPIO pin. Using all Port C pins in LED drive mode with maximum current may result in excessive total current. See **the** <u>Electrical Characteristics</u> chapter on page 226 for the maximum total current for the applicable package.

### **Shared Reset Pin**

On the 20- and 28-pin devices, the PD0 pin shares function with a bidirectional reset pin. Unlike all other I/O pins, this pin does not default to GPIO function on power-up. This pin acts as a bidirectional input/open-drain output reset until the software reconfigures it. The PD0 pin is an output-only open drain when in GPIO mode. There are no pull-up, High Drive, or Stop Mode Recovery source features associated with the PD0 pin.

On the 8-pin product versions, the reset pin is shared with PA2, but the pin is not limited to output-only when in GPIO mode.

**Caution:** If PA2 on the 8-pin product is reconfigured as an input, ensure that no external stimulus drives the pin low during any reset sequence. Since PA2 returns to its **RESET** alternate function during system resets, driving it Low holds the chip in a reset state until the pin is released.

| Bit          | Description (Continued)                                                                                  |  |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| [4]<br>U0RXI | <b>UART 0 Receiver Interrupt Request</b><br>0 = No interrupt request is pending for the UART 0 receiver. |  |  |  |  |  |

|              | 1 = An interrupt request from the UART 0 receiver is awaiting service.                                   |  |  |  |  |  |

| [3]          | UART 0 Transmitter Interrupt Request                                                                     |  |  |  |  |  |

| U0TXI        | 0 = No interrupt request is pending for the UART 0 transmitter.                                          |  |  |  |  |  |

|              | 1 = An interrupt request from the UART 0 transmitter is awaiting service.                                |  |  |  |  |  |

| [2:1]        | Reserved                                                                                                 |  |  |  |  |  |

|              | These bits are reserved and must be programmed to 00.                                                    |  |  |  |  |  |

| [0]          | ADC Interrupt Request                                                                                    |  |  |  |  |  |

0 = No interrupt request is pending for the analog-to-digital Converter.

1 = An interrupt request from the Analog-to-Digital Converter is awaiting service.

### **Interrupt Request 1 Register**

The Interrupt Request 1 (IRQ1) Register, shown in Table 36, stores interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ1 Register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 1 Register to determine if any interrupt requests are pending.

| Bit     | 7     | 6     | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|-------|-------|------|------|------|------|------|------|

| Field   | PA7VI | PA6CI | PA5I | PA4I | PA3I | PA2I | PA1I | PA0I |

| RESET   | 0     | 0     | 0    | 0    | 0    | 0    | 0    | 0    |

| R/W     | R/W   | R/W   | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| Address | FC3H  |       |      |      |      |      |      |      |

Table 36. Interrupt Request 1 Register (IRQ1)

| Bit           | Description                                                                                                                                                                                          |  |  |  |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| [7]<br>PA7VI  | <b>Port A Pin 7 or LVD Interrupt Request</b><br>0 = No interrupt request is pending for GPIO Port A or LVD.                                                                                          |  |  |  |  |  |

|               | 1 = An interrupt request from GPIO Port A or LVD.                                                                                                                                                    |  |  |  |  |  |

| [6]<br>PA6CI  | Port A Pin 6 or Comparator Interrupt Request<br>0 = No interrupt request is pending for GPIO Port A or Comparator.<br>1 = An interrupt request from GPIO Port A or Comparator.                       |  |  |  |  |  |

| [5:0]<br>PA5I | <ul> <li>Port A Pin x Interrupt Request</li> <li>0 = No interrupt request is pending for GPIO Port A pin x.</li> <li>1 = An interrupt request from GPIO Port A pin x is awaiting service.</li> </ul> |  |  |  |  |  |

| Note: x ir    | Note: x indicates the specific GPIO port pin number (0–5).                                                                                                                                           |  |  |  |  |  |

ADCI

#### Table 39. IRQ0 Enable High Bit Register (IRQ0ENH)

| Bit          | 7                                                                    | 6          | 5           | 4             | 3             | 2        | 1        | 0      |  |

|--------------|----------------------------------------------------------------------|------------|-------------|---------------|---------------|----------|----------|--------|--|

| Field        | Reserved                                                             | T1ENH      | T0ENH       | <b>U0RENH</b> | <b>U0TENH</b> | Reserved | Reserved | ADCENH |  |

| RESET        | 0                                                                    | 0          | 0           | 0             | 0             | 0        | 0        | 0      |  |

| R/W          | R/W                                                                  | R/W        | R/W         | R/W           | R/W           | R/W      | R/W      | R/W    |  |

| Address      | FC1H                                                                 |            |             |               |               |          |          |        |  |

|              |                                                                      |            |             |               |               |          |          |        |  |

| Bit          | Description                                                          |            |             |               |               |          |          |        |  |

| [7]          | <b>Reserved</b><br>This bit is reserved and must be programmed to 0. |            |             |               |               |          |          |        |  |

| [6]<br>T1ENH | Timer 1 Int                                                          | errupt Req | uest Enable | e High Bit    |               |          |          |        |  |

| [5]<br>T0ENH | Timer 0 Interrupt Request Enable High Bit                            |            |             |               |               |          |          |        |  |

|              | UART 0 Receive Interrupt Request Enable High Bit                     |            |             |               |               |          |          |        |  |

| <b>U0RENH</b> |                                                                   |

|---------------|-------------------------------------------------------------------|

| [3]<br>UOTENH | UART 0 Transmit Interrupt Request Enable High Bit                 |

| [2:1]         | Reserved<br>These bits are reserved and must be programmed to 00. |

| [0]<br>ADCENH | ADC Interrupt Request Enable High Bit                             |

| Bit     | 7        | 6     | 5            | 4             | 3             | 2        | 1        | 0      |

|---------|----------|-------|--------------|---------------|---------------|----------|----------|--------|

| Field   | Reserved | T1ENL | <b>T0ENL</b> | <b>U0RENL</b> | <b>U0TENL</b> | Reserved | Reserved | ADCENL |

| RESET   | 0        | 0     | 0            | 0             | 0             | 0        | 0        | 0      |

| R/W     | R        | R/W   | R/W          | R/W           | R/W           | R        | R        | R/W    |

| Address | FC2H     |       |              |               |               |          |          |        |

#### Table 40. IRQ0 Enable Low Bit Register (IRQ0ENL)

| Bit          | Description                                                   |

|--------------|---------------------------------------------------------------|

| [7]          | Reserved<br>This bit is reserved and must be programmed to 0. |

| [6]<br>T1ENL | Timer 1 Interrupt Request Enable Low Bit                      |

| [5]<br>T0ENL | Timer 0 Interrupt Request Enable Low Bit                      |

The UART is now configured for interrupt-driven data reception. When the UART Receiver interrupt is detected, the associated interrupt service routine (ISR) performs the following:

- 1. Checks the UART Status 0 Register to determine the source of the interrupt error, break, or received data.

- 2. Reads the data from the UART Receive Data Register if the interrupt was because of data available. If operating in MULTIPROCESSOR (9-bit) Mode, further actions may be required depending on the MULTIPROCESSOR Mode bits MPMD[1:0].

- 3. Clears the UART Receiver interrupt in the applicable Interrupt Request Register.

- 4. Executes the IRET instruction to return from the interrupt-service routine and await more data.

### Clear To Send (CTS) Operation

The CTS pin, if enabled by the CTSE bit of the UART Control 0 Register, performs flow control on the outgoing transmit datastream. The Clear To Send ( $\overline{\text{CTS}}$ ) input pin is sampled one system clock before beginning any new character transmission. To delay transmission of the next data character, an external receiver must deassert  $\overline{\text{CTS}}$  at least one system clock cycle before a new data transmission begins. For multiple character transmissions, this action is typically performed during Stop Bit transmission. If  $\overline{\text{CTS}}$  deasserts in the middle of a character transmission, the current character is sent completely.

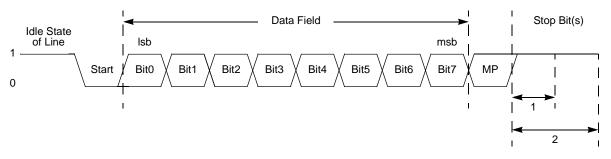

### MULTIPROCESSOR (9-bit) Mode

The UART features a MULTIPROCESSOR (9-bit) Mode that uses an extra (9th) bit for selective communication when a number of processors share a common UART bus. In MULTIPROCESSOR Mode (also referred to as *9-bit Mode*), the multiprocessor bit (MP) is transmitted immediately following the 8-bits of data and immediately preceding the Stop bit(s) as displayed in Figure 13. The character format is:

Figure 13. UART Asynchronous MULTIPROCESSOR Mode Data Format

Z8 Encore! XP<sup>®</sup> F082A Series **Product Specification**

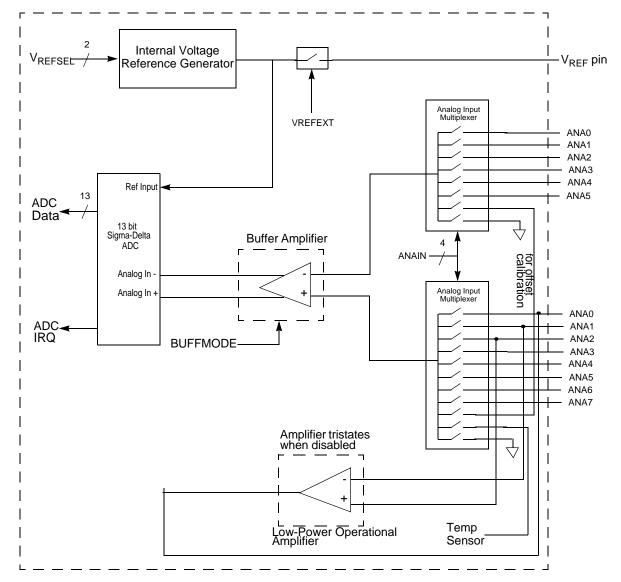

Figure 19. Analog-to-Digital Converter Block Diagram

## Operation

In both SINGLE-ENDED and DIFFERENTIAL modes, the effective output of the ADC is an 11-bit, signed, two's complement digital value. In DIFFERENTIAL Mode, the ADC can output values across the entire 11-bit range, from -1024 to +1023. In SINGLE-ENDED Mode, the output generally ranges from 0 to +1023, but offset errors can cause small negative values.

#### Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

#### **Compensation Steps:**

1. Correct for Offset:

| ADC MSB    | ADC LSB    |

|------------|------------|

| _          |            |

| Offset MSB | Offset LSB |

| =          |            |

| #1 MSB     | #1 LSB     |

|            |            |

2. Compute the absolute value of the offset-corrected ADC value *if negative*; the gain correction factor is computed assuming positive numbers, with sign restoration afterward.

| #2 MSB | #2 LSB |

|--------|--------|

|--------|--------|

Also compute the absolute value of the gain correction word, if negative.

| AGain MSB | AGain LSB |

|-----------|-----------|

|-----------|-----------|

3. Multiply by the Gain Correction Word. If operating in DIFFERENTIAL Mode, there are two gain correction values: one for positive ADC values, another for negative ADC values. Use the appropriate Gain Correction Word based on the sign computed by byte #2.

| #2 MSB | #2 LSB |

|--------|--------|

|        |        |

| AGain MSB | AGain LSB |

|-----------|-----------|

| -         |           |

=

| Bit              | 7                                           | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5    | 4     | 3  | 2         | 1  | 0 |

|------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|----|-----------|----|---|

| Field            | REFSELH                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Rese | erved | В  | UFMODE[2: | 0] |   |

| RESET            | 1                                           | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0    | 0     | 0  | 0         | 0  | 0 |

| R/W              | R/W                                         | /W R/W R/W R/W R/W R/W R/W R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |       |    |           |    |   |

| Address          |                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      | F7    | 1H |           | •  |   |

| Bit              | Dese                                        | cription                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |       |    |           |    |   |

| [7]<br>REFSELH   | In co<br>the le<br>REF<br>00=<br>01=<br>10= | <ul> <li>Voltage Reference Level Select High Bit</li> <li>In conjunction with the Low bit (REFSELL) in ADC Control Register 0, this determines the level of the internal voltage reference; the following details the effects of {REFSELH REFSELL}; this reference is independent of the Comparator reference.</li> <li>00= Internal Reference Disabled, reference comes from external pin.</li> <li>01= Internal Reference set to 1.0V.</li> <li>10= Internal Reference set to 2.0V (default).</li> <li>11= Reserved.</li> </ul> |      |       |    |           |    |   |

| [6:3]            |                                             | <b>Reserved</b> These bits are reserved and must be programmed to 0000.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |       |    |           |    |   |

| [2:0]<br>BUFMODI | E[2:0] 000<br>001<br>010                    | Input Buffer Mode Select<br>[2:0] 000 = Single-ended, unbuffered input.<br>001 = Single-ended, buffered input with unity gain.<br>010 = Reserved.<br>011 = Reserved.                                                                                                                                                                                                                                                                                                                                                              |      |       |    |           |    |   |

#### Table 74. ADC Control/Status Register 1 (ADCCTL1)

100 = Differential, unbuffered input.101 = Differential, buffered input with unity gain.

110 = Reserved. 111 = Reserved.

### ADC Data High Byte Register

The ADC Data High Byte (ADCD\_H) Register contains the upper eight bits of the ADC output. The output is an 13-bit two's complement value. During a single-shot conversion, this value is invalid. Access to the ADC Data High Byte Register is read-only. Reading the ADC Data High Byte Register latches data in the ADC Low Bits Register.

| Bit   | Description (Continued)                                                                        |

|-------|------------------------------------------------------------------------------------------------|

| [1:0] | For 8-pin devices, the following voltages can be configured; for 20- and 28-pin devices, these |

|       | bits are reserved.                                                                             |

|       | 000000 = 0.00 V                                                                                |

|       | 000001 = 0.05 V                                                                                |

|       | 000010 = 0.10 V                                                                                |

|       | 000011 = 0.15 V                                                                                |

|       | 000100 = 0.20 V                                                                                |

|       | 000101 = 0.25 V                                                                                |

|       | 000110 = 0.30 V                                                                                |

|       | 000111 = 0.35 V                                                                                |

|       | 001000 = 0.40  V                                                                               |

|       | 001001 = 0.45 V                                                                                |

|       | 001010 = 0.50  V                                                                               |

|       | 001011 = 0.55 V                                                                                |

|       | 001100 = 0.60  V                                                                               |

|       | 001101 = 0.65 V                                                                                |

|       | 001110 = 0.70 V                                                                                |

|       | 001111 = 0.75 V                                                                                |

|       | 010000 = 0.80  V                                                                               |

|       | 010001 = 0.85  V                                                                               |

|       | 010010 = 0.90  V                                                                               |

|       | 010011 = 0.95  V                                                                               |

|       | 010100 = 1.00  V (Default)                                                                     |

|       | 010101 = 1.05  V                                                                               |

|       | 010110 = 1.10 V<br>010111 = 1.15 V                                                             |

|       | 01000 = 1.20  V                                                                                |

|       | 011001 = 1.25 V                                                                                |

|       | 011010 = 1.30  V                                                                               |

|       | 011011 = 1.35 V                                                                                |

|       | 011100 = 1.40  V                                                                               |

|       | 011101 = 1.45 V                                                                                |

|       | 011110 = 1.50 V                                                                                |

|       | 011111 = 1.55 V                                                                                |

|       | 100000 = 1.60  V                                                                               |

|       | 100001 = 1.65  V                                                                               |

|       | 100010 = 1.70  V                                                                               |

|       | 100011 = 1.75 V                                                                                |

|       | 100100 = 1.80  V                                                                               |

### Flash Controller Behavior in DEBUG Mode

The following changes in behavior of the Flash Controller occur when the Flash Controller is accessed using the On-Chip Debugger:

- The Flash Write Protect option bit is ignored.

- The Flash Sector Protect Register is ignored for programming and erase operations.

- Programming operations are not limited to the page selected in the Page Select Register.

- Bits in the Flash Sector Protect Register can be written to one or zero.

- The second write of the Page Select Register to unlock the Flash Controller is not necessary.

- The Page Select Register can be written when the Flash Controller is unlocked.

- The Mass Erase command is enabled through the Flash Control Register.

**Caution:** For security reasons, the Flash controller allows only a single page to be opened for write/ erase. When writing multiple Flash pages, the flash controller must go through the unlock sequence again to select another page.

### **Flash Control Register Definitions**

This section defines the features of the following Flash Control registers.

Flash Control Register: see page 153

Flash Status Register: see page 155

Flash Page Select Register: see page 156

Flash Sector Protect Register: see page 157

Flash Frequency High and Low Byte Registers: see page 157

### **Flash Control Register**

The Flash Controller must be unlocked using the Flash Control (FCTL) Register before programming or erasing the Flash memory. Writing the sequence 73H 8CH, sequentially, to the Flash Control Register unlocks the Flash Controller. When the Flash Controller is unlocked, the Flash memory can be enabled for Mass Erase or Page Erase by writing the appropriate enable command to the FCTL. Page Erase applies only to the active page selected in Flash Page Select Register. Mass Erase is enabled only through the On-Chip

### **ADC Calibration Data**

#### Table 96. ADC Calibration Bits

| Bit        | 7                                   | 6           | 5             | 4      | 3    | 2   | 1   | 0   |

|------------|-------------------------------------|-------------|---------------|--------|------|-----|-----|-----|

| Field      |                                     |             |               | ADC    | _CAL |     |     |     |

| RESET      | U                                   | U           | U             | U      | U    | U   | U   | U   |

| R/W        | R/W                                 | R/W         | R/W           | R/W    | R/W  | R/W | R/W | R/W |

| Address    | Information Page Memory 0060H–007DH |             |               |        |      |     |     |     |

| Noto: II - | I Inchanged h                       | W Reset R/M | / - Road/Writ | ۰<br>۵ |      |     |     |     |

Note: U = Unchanged by Reset. R/W = Read/Write.

### Bit Description

[7:0] Analog-to-Digital Converter Calibration Values

ADC\_CAL Contains factory-calibrated values for ADC gain and offset compensation. Each of the ten supported modes has one byte of offset calibration and two bytes of gain calibration. These values are read by the software to compensate ADC measurements as described in the Software Compensation Procedure Using Factory Calibration Data section on page 129. The location of each calibration byte is provided in Table 97.

| Info Page | Memory  |                    |                          |                |

|-----------|---------|--------------------|--------------------------|----------------|

| Address   | Address | Compensation Usage | ADC Mode                 | Reference Type |

| 60        | FE60    | Offset             | Single-Ended Unbuffered  | Internal 2.0 V |

| 08        | FE08    | Gain High Byte     | Single-Ended Unbuffered  | Internal 2.0 V |

| 09        | FE09    | Gain Low Byte      | Single-Ended Unbuffered  | Internal 2.0 V |

| 63        | FE63    | Offset             | Single-Ended Unbuffered  | Internal 1.0 V |

| 0A        | FE0A    | Gain High Byte     | Single-Ended Unbuffered  | Internal 1.0 V |

| 0B        | FE0B    | Gain Low Byte      | Single-Ended Unbuffered  | Internal 1.0 V |

| 66        | FE66    | Offset             | Single-Ended Unbuffered  | External 2.0 V |

| 0C        | FE0C    | Gain High Byte     | Single-Ended Unbuffered  | External 2.0 V |

| 0D        | FE0D    | Gain Low Byte      | Single-Ended Unbuffered  | External 2.0 V |

| 69        | FE69    | Offset             | Single-Ended 1x Buffered | Internal 2.0 V |

| 0E        | FE0E    | Gain High Byte     | Single-Ended 1x Buffered | Internal 2.0 V |

| 0F        | FE0F    | Gain Low Byte      | Single-Ended 1x Buffered | Internal 2.0 V |

| 6C        | FE6C    | Offset             | Single-Ended 1x Buffered | External 2.0 V |

| 10        | FE10    | Gain High Byte     | Single-Ended 1x Buffered | External 2.0 V |

| 11        | FE11    | Gain Low Byte      | Single-Ended 1x Buffered | External 2.0 V |

| 6F        | FE6F    | Offset             | Differential Unbuffered  | Internal 2.0 V |

#### Table 97. ADC Calibration Data Location

### **Temperature Sensor Calibration Data**

#### Table 98. Temperature Sensor Calibration High Byte at 003A (TSCALH)

| Bit       | 7           | 6             | 5             | 4           | 3          | 2   | 1   | 0   |

|-----------|-------------|---------------|---------------|-------------|------------|-----|-----|-----|

| Field     |             |               |               | TSC         | ALH        |     |     |     |

| RESET     | U           | U             | U             | U           | U          | U   | U   | U   |

| R/W       | R/W         | R/W           | R/W           | R/W         | R/W        | R/W | R/W | R/W |

| Address   |             |               | Info          | rmation Pag | e Memory 0 | 03A |     |     |

| Note: U = | Unchanged b | by Reset. R/W | / = Read/Writ | e.          |            |     |     |     |

#### Bit Description [7:0] **Temperature Sensor Calibration High Byte** TSCALH The TSCALH and TSCALL bytes combine to form the 12-bit temperature sensor offset calibra-

tion value. For more details, see Temperature Sensor Operation on page 139.

#### Table 99. Temperature Sensor Calibration Low Byte at 003B (TSCALL)

| Bit       | 7                            | 6            | 5             | 4   | 3   | 2   | 1   | 0   |

|-----------|------------------------------|--------------|---------------|-----|-----|-----|-----|-----|

| Field     |                              | TSCALL       |               |     |     |     |     |     |

| RESET     | U                            | U            | U             | U   | U   | U   | U   | U   |

| R/W       | R/W                          | R/W          | R/W           | R/W | R/W | R/W | R/W | R/W |

| Address   | Information Page Memory 003B |              |               |     |     |     |     |     |

| Note: U = | Unchanged b                  | y Reset. R/W | / = Read/Writ | e.  |     |     |     |     |

#### Bit Description

| [7:0]  | Temperature Sensor Calibration Low Byte                                                   |

|--------|-------------------------------------------------------------------------------------------|

| TSCALL | The TSCALH and TSCALL bytes combine to form the 12-bit temperature sensor offset calibra- |

|        | tion value. For usage details, see the Temperature Sensor Operation section on page 144.  |

Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

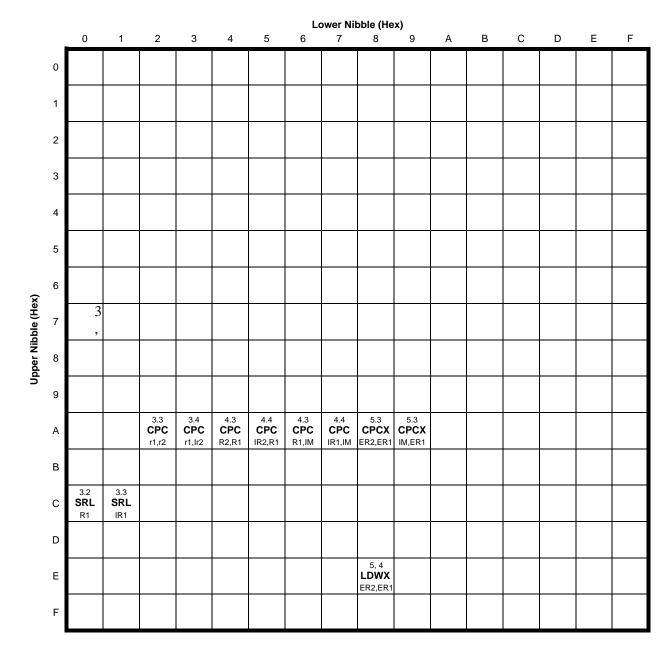

Figure 32. Second Opcode Map after 1FH

| ning (Continued) |  |

|------------------|--|

|                  |  |

#### Table 139. Analog-to-Digital Converter Electrical Characteristics and Timing (Continued)

#### $V_{DD}$ = 3.0 V to 3.6 V T<sub>A</sub> = 0°C to +70°C (unless otherwise stated)

| Symbol         | Parameter                               | Minimum | Typical | Maximum              | Units                          | Conditions                                                                                                                                                                                                                                |

|----------------|-----------------------------------------|---------|---------|----------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | Continuous Conversion<br>Time           | -       | 256     | _                    | Sys-<br>tem<br>clock<br>cycles | All measurements but temperature sensor                                                                                                                                                                                                   |

|                |                                         |         | 512     |                      |                                | Temperature sensor measurement                                                                                                                                                                                                            |

|                | Signal Input Bandwidth                  | -       | 10      |                      | kHz                            | As defined by -3 dB point                                                                                                                                                                                                                 |

| R <sub>S</sub> | Analog Source<br>Impedance <sup>4</sup> | -       | _       | 10                   | kΩ                             | In unbuffered mode                                                                                                                                                                                                                        |

|                |                                         |         |         | 500                  | kΩ                             | In buffered modes                                                                                                                                                                                                                         |

| Zin            | Input Impedance                         | -       | 150     |                      | kΩ                             | In unbuffered mode at 20MHz <sup>5</sup>                                                                                                                                                                                                  |

|                |                                         | 10      | _       |                      | MΩ                             | In buffered modes                                                                                                                                                                                                                         |

| Vin            | Input Voltage Range                     | 0       |         | V <sub>DD</sub>      | V                              | Unbuffered Mode                                                                                                                                                                                                                           |

|                |                                         | 0.3     |         | V <sub>DD</sub> -1.1 | V                              | Buffered Modes<br>These values define<br>the range over which<br>the ADC performs<br>within spec; exceeding<br>these values does not<br>cause damage or insta-<br>bility; see DC Charac-<br>teristics for absolute<br>pin voltage limits. |

Notes:

1. Analog source impedance affects the ADC offset voltage (because of pin leakage) and input settling time.

2. Devices are factory calibrated at  $V_{DD}$  = 3.3 V and  $T_A$  = +30°C, so the ADC is maximally accurate under these conditions.

3. LSBs are defined assuming 10-bit resolution.

- 4. This is the maximum recommended resistance seen by the ADC input pin.

- 5. The input impedance is inversely proportional to the system clock frequency.

#### 240

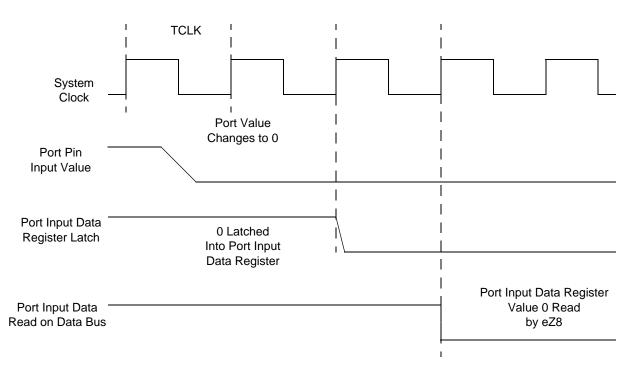

### General Purpose I/O Port Input Data Sample Timing

Figure 34 displays timing of the GPIO Port input sampling. The input value on a GPIO port pin is sampled on the rising edge of the system clock. The Port value is available to the eZ8 CPU on the second rising clock edge following the change of the Port value.

#### Figure 34. Port Input Sample Timing

#### Table 143. GPIO Port Input Timing

|                     |                                                                                                    | Delay (ns) |         |

|---------------------|----------------------------------------------------------------------------------------------------|------------|---------|

| Parameter           | Abbreviation                                                                                       | Minimum    | Maximum |

| T <sub>S_PORT</sub> | Port Input Transition to X <sub>IN</sub> Rise Setup Time (not pictured)                            | 5          | -       |

| T <sub>H_PORT</sub> | X <sub>IN</sub> Rise to Port Input Transition Hold Time (not pictured)                             | 0          | -       |

| T <sub>SMR</sub>    | GPIO Port Pin Pulse Width to ensure Stop Mode Recovery (for GPIO port pins enabled as SMR sources) | 1 μs       |         |

# Packaging

Zilog's Product Line of MCUs includes the Z8F011A, Z8F012A, Z8F021A, Z8F022A, Z8F041A, Z8F042A, Z8F081A and Z8F082A devices, which are available in the following packages:

- 8-pin Plastic Dual-Inline Package (PDIP)

- 8-Pin Quad Flat No-Lead Package (QFN)/MLF-S<sup>1</sup>

- 8-pin Small Outline Integrated Circuit Package (SOIC)

- 20-pin Small Outline Integrated Circuit Package (SOIC)

- 20-pin Small Shrink Outline Package (SSOP)

- 20-pin Plastic Dual-Inline Package (PDIP)

- 28-pin Small Outline Integrated Circuit Package (SOIC)

- 28-pin Small Shrink Outline Package (SSOP)

- 28-pin Plastic Dual-Inline Package (PDIP)

Current diagrams for each of these packages are published in Zilog's <u>Packaging Product</u> <u>Specification (PS0072)</u>, which is available free for download from the Zilog website.

<sup>1.</sup> The footprint of the QFN)/MLF-S package is identical to that of the 8-pin SOIC package, but with a lower profile.