# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 17                                                           |

| Program Memory Size        | 2KB (2K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 64 x 8                                                       |

| RAM Size                   | 512 x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 7x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 105°C (TA)                                           |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                               |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f022ahh020eg    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Register Map**

Table 7 provides the address map for the Register File of the Z8 Encore! XP F082A Series devices. Not all devices and package styles in the Z8 Encore! XP F082A Series support the ADC, or all of the GPIO Ports. Consider registers for unimplemented peripherals as Reserved.

| Address (Hex)  | Register Description              | Mnemonic | Reset (Hex) | Page      |

|----------------|-----------------------------------|----------|-------------|-----------|

| General-Purpos | e RAM                             |          |             |           |

| Z8F082A/Z8F08  | 1A Devices                        |          |             |           |

| 000–3FF        | General-Purpose Register File RAM | —        | XX          |           |

| 400–EFF        | Reserved                          | —        | XX          |           |

| Z8F042A/Z8F04  | 1A Devices                        |          |             |           |

| 000–3FF        | General-Purpose Register File RAM | —        | XX          |           |

| 400–EFF        | Reserved                          | —        | XX          |           |

| Z8F022A/Z8F02  | 1A Devices                        |          |             |           |

| 000–1FF        | General-Purpose Register File RAM | _        | XX          |           |

| 200–EFF        | Reserved                          | —        | XX          |           |

| Z8F012A/Z8F01  | 1A Devices                        |          |             |           |

| 000–0FF        | General-Purpose Register File RAM | _        | XX          |           |

| 100-EFF        | Reserved                          | —        | XX          |           |

| Timer 0        |                                   |          |             |           |

| F00            | Timer 0 High Byte                 | T0H      | 00          | <u>90</u> |

| F01            | Timer 0 Low Byte                  | TOL      | 01          | <u>90</u> |

| F02            | Timer 0 Reload High Byte          | TORH     | FF          | <u>91</u> |

| F03            | Timer 0 Reload Low Byte           | TORL     | FF          | <u>91</u> |

| F04            | Timer 0 PWM High Byte             | TOPWMH   | 00          | <u>92</u> |

| F05            | Timer 0 PWM Low Byte              | TOPWML   | 00          | <u>92</u> |

| F06            | Timer 0 Control 0                 | TOCTLO   | 00          | <u>85</u> |

| F07            | Timer 0 Control 1                 | T0CTL1   | 00          | <u>86</u> |

#### Table 7. Register File Address Map

Notes: 1. XX = Undefined.

2. Refer to the <u>eZ8</u> CPU <u>Core User Manual (UM0128)</u>.

# General-Purpose Input/Output

The Z8 Encore! XP F082A Series products support a maximum of 25 port pins (Ports A–D) for general-purpose input/output (GPIO) operations. Each port contains control and data registers. The GPIO control registers determine data direction, open-drain, output drive current, programmable pull-ups, Stop Mode Recovery functionality and alternate pin functions. Each port pin is individually programmable. In addition, the Port C pins are capable of direct LED drive at programmable drive strengths.

# **GPIO Port Availability By Device**

Table 14 lists the port pins available with each device and package type.

| Devices                                                                                                                                  | Package | ADC | Port A | Port B | Port C | Port D | Total I/O |

|------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|--------|--------|--------|--------|-----------|

| Z8F082ASB, Z8F082APB, Z8F082AQB<br>Z8F042ASB, Z8F042APB, Z8F042AQB<br>Z8F022ASB, Z8F022APB, Z8F022AQB<br>Z8F012ASB, Z8F012APB, Z8F012AQB | 8-pin   | Yes | [5:0]  | No     | No     | No     | 6         |

| Z8F081ASB, Z8F081APB, Z8F081AQB<br>Z8F041ASB, Z8F041APB, Z8F041AQB<br>Z8F021ASB, Z8F021APB, Z8F021AQB<br>Z8F011ASB, Z8F011APB, Z8F011AQB | 8-pin   | No  | [5:0]  | No     | No     | No     | 6         |

| Z8F082APH, Z8F082AHH, Z8F082ASH<br>Z8F042APH, Z8F042AHH, Z8F042ASH<br>Z8F022APH, Z8F022AHH, Z8F022ASH<br>Z8F012APH, Z8F012AHH, Z8F012ASH | 20-pin  | Yes | [7:0]  | [3:0]  | [3:0]  | [0]    | 17        |

| Z8F081APH, Z8F081AHH, Z8F081ASH<br>Z8F041APH, Z8F041AHH, Z8F041ASH<br>Z8F021APH, Z8F021AHH, Z8F021ASH<br>Z8F011APH, Z8F011AHH, Z8F011ASH | 20-pin  | No  | [7:0]  | [3:0]  | [3:0]  | [0]    | 17        |

| Z8F082APJ, Z8F082ASJ, Z8F082AHJ<br>Z8F042APJ, Z8F042ASJ, Z8F042AHJ<br>Z8F022APJ, Z8F022ASJ, Z8F022AHJ<br>Z8F012APJ, Z8F012ASJ, Z8F012AHJ | 28-pin  | Yes | [7:0]  | [5:0]  | [7:0]  | [0]    | 23        |

| Z8F081APJ, Z8F081ASJ, Z8F081AHJ<br>Z8F041APJ, Z8F041ASJ, Z8F041AHJ<br>Z8F021APJ, Z8F021ASJ, Z8F021AHJ<br>Z8F011APJ, Z8F011ASJ, Z8F011AHJ | 28-pin  | No  | [7:0]  | [7:0]  | [7:0]  | [0]    | 25        |

Table 14. Port Availability by Device and Package Type

| Port   | Pin | Mnemonic                      | Alternate Function<br>Description         | Alternate<br>Function Select<br>Register AFS1 | Alternate<br>Function<br>Select<br>Register<br>AFS2 |

|--------|-----|-------------------------------|-------------------------------------------|-----------------------------------------------|-----------------------------------------------------|

| Port A | PA0 | TOIN                          | Timer 0 Input                             | AFS1[0]: 0                                    | AFS2[0]: 0                                          |

|        |     | Reserved                      |                                           | AFS1[0]: 0                                    | AFS2[0]: 1                                          |

|        |     | Reserved                      |                                           | AFS1[0]: 1                                    | AFS2[0]: 0                                          |

|        |     | TOOUT                         | Timer 0 Output Complement                 | AFS1[0]: 1                                    | AFS2[0]: 1                                          |

|        | PA1 | TOOUT                         | Timer 0 Output                            | AFS1[1]: 0                                    | AFS2[1]: 0                                          |

|        |     | Reserved                      |                                           | AFS1[1]: 0                                    | AFS2[1]: 1                                          |

|        |     | CLKIN                         | External Clock Input                      | AFS1[1]: 1                                    | AFS2[1]: 0                                          |

|        |     | Analog Functions <sup>1</sup> | ADC Analog Input/V <sub>REF</sub>         | AFS1[1]: 1                                    | AFS2[1]: 1                                          |

|        | PA2 | DE0                           | UART 0 Driver Enable                      | AFS1[2]: 0                                    | AFS2[2]: 0                                          |

|        |     | RESET                         | External Reset                            | AFS1[2]: 0                                    | AFS2[2]: 1                                          |

|        |     | T1OUT                         | Timer 1 Output                            | AFS1[2]: 1                                    | AFS2[2]: 0                                          |

|        |     | Reserved                      |                                           | AFS1[2]: 1                                    | AFS2[2]: 1                                          |

|        | PA3 | CTS0                          | UART 0 Clear to Send                      | AFS1[3]: 0                                    | AFS2[3]: 0                                          |

|        |     | COUT                          | Comparator Output                         | AFS1[3]: 0                                    | AFS2[3]: 1                                          |

|        |     | T1IN                          | Timer 1 Input                             | AFS1[3]: 1                                    | AFS2[3]: 0                                          |

|        |     | Analog Functions <sup>2</sup> | ADC Analog Input/LPO Input (P)            | AFS1[3]: 1                                    | AFS2[3]: 1                                          |

|        | PA4 | RXD0                          | UART 0 Receive Data                       | AFS1[4]: 0                                    | AFS2[4]: 0                                          |

|        |     | Reserved                      |                                           | AFS1[4]: 0                                    | AFS2[4]: 1                                          |

|        |     | Reserved                      |                                           | AFS1[4]: 1                                    | AFS2[4]: 0                                          |

|        |     | Analog Functions <sup>2</sup> | ADC/Comparator Input (N)/LPO<br>Input (N) | AFS1[4]: 1                                    | AFS2[4]: 1                                          |

|        | PA5 | TXD0                          | UART 0 Transmit Data                      | AFS1[5]: 0                                    | AFS2[5]: 0                                          |

|        |     | T1OUT                         | Timer 1 Output Complement                 | AFS1[5]: 0                                    | AFS2[5]: 1                                          |

|        |     | Reserved                      |                                           | AFS1[5]: 1                                    | AFS2[5]: 0                                          |

|        |     | Analog Functions <sup>2</sup> | ADC/Comparator Input (P) LPO<br>Output    | AFS1[5]: 1                                    | AFS2[5]: 1                                          |

### Table 16. Port Alternate Function Mapping (8-Pin Parts)

Notes:

1. Analog functions include ADC inputs, ADC reference, comparator inputs and LPO ports.

2. The alternate function selection must be enabled; see the Port A–D Alternate Function Subregisters (PxAF) section on page 47 for details.

**Example 1.** A poor coding style that can result in lost interrupt requests:

LDX r0, IRQ0 AND r0, MASK LDX IRQ0, r0

To avoid missing interrupts, use the coding style in Example 2 to clear bits in the Interrupt Request 0 Register:

**Example 2.** A good coding style that avoids lost interrupt requests:

ANDX IRQ0, MASK

### **Software Interrupt Assertion**

Program code can generate interrupts directly. Writing a 1 to the correct bit in the Interrupt Request Register triggers an interrupt (assuming that interrupt is enabled). When the interrupt request is acknowledged by the eZ8 CPU, the bit in the Interrupt Request Register is automatically cleared to 0.

**Caution:** Zilog recommends not using a coding style to generate software interrupts by setting bits in the Interrupt Request registers. All incoming interrupts received between execution of the first LDX command and the final LDX command are lost. See Example 3, which follows.

**Example 3.** A poor coding style that can result in lost interrupt requests:

```

LDX r0, IRQ0

OR r0, MASK

LDX IRQ0, r0

```

To avoid missing interrupts, use the coding style in Example 4 to set bits in the Interrupt Request registers:

**Example 4.** A good coding style that avoids lost interrupt requests:

ORX IRQ0, MASK

### Watchdog Timer Interrupt Assertion

The Watchdog Timer interrupt behavior is different from interrupts generated by other sources. The Watchdog Timer continues to assert an interrupt as long as the time-out condition continues. As it operates on a different (and usually slower) clock domain than the rest of the device, the Watchdog Timer continues to assert this interrupt for many system clocks until the counter rolls over.

- Configure the timer for GATED Mode

- Set the prescale value

- 2. Write to the Timer High and Low Byte registers to set the starting count value. Writing these registers only affects the first pass in GATED Mode. After the first timer reset in GATED Mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. Enable the timer interrupt, if appropriate and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input deassertion and reload events. If appropriate, configure the timer interrupt to be generated only at the input deassertion event or the reload event by setting TICONFIG field of the TxCTL0 Register.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control Register to enable the timer.

- 7. Assert the Timer Input signal to initiate the counting.

### CAPTURE/COMPARE Mode

In CAPTURE/COMPARE Mode, the timer begins counting on the first external Timer Input transition. The acceptable transition (rising edge or falling edge) is set by the TPOL bit in the Timer Control Register. The timer input is the system clock.

Every subsequent acceptable transition (after the first) of the Timer Input signal captures the current count value. The Capture value is written to the Timer PWM High and Low Byte registers. When the Capture event occurs, an interrupt is generated, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL0 Register is set to indicate the timer interrupt is caused by an input capture event.

If no Capture event occurs, the timer counts up to the 16-bit Compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the Compare value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL0 Register is cleared to indicate the timer interrupt is not because of an input capture event.

Observe the following steps for configuring a timer for CAPTURE/COMPARE Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE/COMPARE Mode

- Set the prescale value

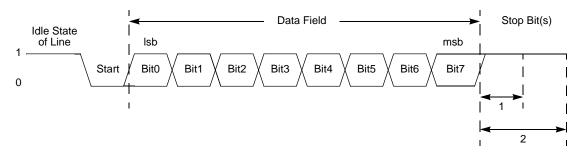

Figure 11. UART Asynchronous Data Format without Parity

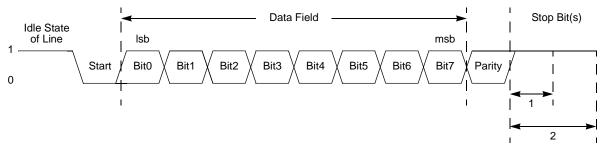

Figure 12. UART Asynchronous Data Format with Parity

# **Transmitting Data using the Polled Method**

Observe the following steps to transmit data using the polled method of operation:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the required baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Write to the UART Control 1 Register, if MULTIPROCESSOR Mode is appropriate, to enable MULTIPROCESSOR (9-bit) Mode functions.

- 4. Set the Multiprocessor Mode Select (MPEN) bit to enable MULTIPROCESSOR Mode.

- 5. Write to the UART Control 0 Register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission

- Set the parity enable bit (PEN), if parity is appropriate and MULTIPROCESSOR Mode is not enabled and select either even or odd parity (PSEL)

# **UART Interrupts**

The UART features separate interrupts for the transmitter and the receiver. In addition, when the UART primary functionality is disabled, the Baud Rate Generator can also function as a basic timer with interrupt capability.

### **Transmitter Interrupts**

The transmitter generates a single interrupt when the Transmit Data Register Empty bit (TDRE) is set to 1. This indicates that the transmitter is ready to accept new data for transmission. The TDRE interrupt occurs after the Transmit Shift Register has shifted the first bit of data out. The Transmit Data Register can now be written with the next character to send. This action provides 7 bit periods of latency to load the Transmit Data Register before the Transmit Shift Register completes shifting the current character. Writing to the UART Transmit Data Register clears the TDRE bit to 0.

### **Receiver Interrupts**

The receiver generates an interrupt when any of the following actions occur:

• A data byte is received and is available in the UART Receive Data Register. This interrupt can be disabled independently of the other receiver interrupt sources. The received data interrupt occurs after the receive character has been received and placed in the Receive Data Register. To avoid an overrun error, software must respond to this received data available condition before the next character is completely received.

**Note:** In MULTIPROCESSOR Mode (MPEN=1), the receive data interrupts are dependent on the multiprocessor configuration and the most recent address byte.

- A break is received.

- An overrun is detected.

- A data framing error is detected.

### **UART Overrun Errors**

When an overrun error condition occurs the UART prevents overwriting of the valid data currently in the Receive Data Register. The Break Detect and Overrun status bits are not displayed until after the valid data has been read.

After the valid data has been read, the UART Status 0 Register is updated to indicate the overrun condition (and Break Detect, if applicable). The RDA bit is set to 1 to indicate that the Receive Data Register contains a data byte. However, because the overrun error occurred, this byte may not contain valid data and must be ignored. The BRKD bit indicates if the overrun was caused by a break condition on the line. After reading the status

| Bit          | 7                                                                                                                                                                                                                                                                                                          | 6                                                                                                                                                                                                                   | 5       | 4    | 3     | 2      | 1      | 0    |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|--------|--------|------|--|

| Field        | MPMD[1]                                                                                                                                                                                                                                                                                                    | MPEN                                                                                                                                                                                                                | MPMD[0] | MPBT | DEPOL | BRGCTL | RDAIRQ | IREN |  |

| RESET        | 0                                                                                                                                                                                                                                                                                                          | 0                                                                                                                                                                                                                   | 0       | 0    | 0     | 0      | 0      | 0    |  |

| R/W          | R/W                                                                                                                                                                                                                                                                                                        | R/W                                                                                                                                                                                                                 | R/W     | R/W  | R/W   | R/W    | R/W    | R/W  |  |

| Address      |                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                     |         | F4   | 3H    |        |        |      |  |

| Bit          | Descript                                                                                                                                                                                                                                                                                                   | tion                                                                                                                                                                                                                |         |      |       |        |        |      |  |

| [6]<br>MPEN  |                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                     |         |      |       |        |        |      |  |

| [4]<br>MPBT  | <ul> <li>MPBT This bit is applicable only when MULTIPROCESSOR (9-bit) Mode is enabled. The 9th bit is used by the receiving device to determine if the data byte contains address or data information.</li> <li>0 = Send a 0 in the multiprocessor bit location of the data stream (data byte).</li> </ul> |                                                                                                                                                                                                                     |         |      |       |        |        |      |  |

| [3]<br>DEPOL | <b>Driver E</b><br>0 = DE s                                                                                                                                                                                                                                                                                | <ul> <li>1 = Send a 1 in the multiprocessor bit location of the data stream (address byte).</li> <li>Driver Enable Polarity</li> <li>0 = DE signal is Active High.</li> <li>1 = DE signal is Active Low.</li> </ul> |         |      |       |        |        |      |  |

### Table 64. UART Control 1 Register (U0CTL1)

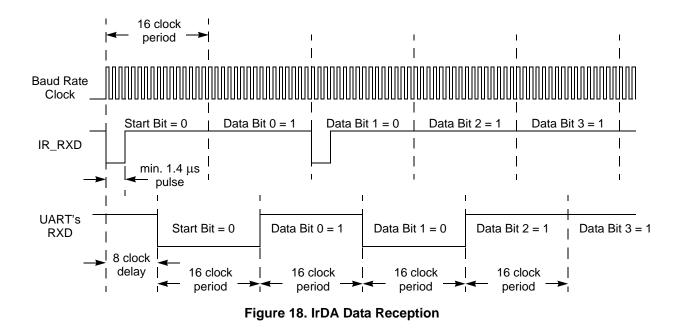

## **Receiving IrDA Data**

Data received from the infrared transceiver using the IR\_RXD signal through the RXD pin is decoded by the infrared endec and passed to the UART. The UART's baud rate clock is used by the infrared endec to generate the demodulated signal (RXD) that drives the UART. Each UART/Infrared data bit is 16-clocks wide. Figure 18 displays data reception. When the infrared endec is enabled, the UART's RXD signal is internal to the Z8 Encore! XP F082A Series products while the IR\_RXD signal is received through the RXD pin.

### **Infrared Data Reception**

**Caution:** The system clock frequency must be at least 1.0MHz to ensure proper reception of the 1.4µs minimum width pulses allowed by the IrDA standard.

### **Endec Receiver Synchronization**

The IrDA receiver uses a local baud rate clock counter (0 to 15 clock periods) to generate an input stream for the UART and to create a sampling window for detection of incoming pulses. The generated UART input (UART RXD) is delayed by 8 baud rate clock periods with respect to the incoming IrDA data stream. When a falling edge in the input data stream is detected, the Endec counter is reset. When the count reaches a value of 8, the UART RXD value is updated to reflect the value of the decoded data. When the count reaches 12 baud clock periods, the sampling window for the next incoming pulse opens.

| Bit    | Description (Continued)                                                                     |

|--------|---------------------------------------------------------------------------------------------|

| [5:2]  | Internal Reference Voltage Level                                                            |

| REFLVL | This reference is independent of the ADC voltage reference. Note: 8-pin devices contain two |

|        | additional LSBs for increased resolution.                                                   |

|        | For 20-/28-pin devices:                                                                     |

|        | 0000 = 0.0 V                                                                                |

|        | 0001 = 0.2 V                                                                                |

|        | 0010 = 0.4 V                                                                                |

|        | 0011 = 0.6 V                                                                                |

|        | 0100 = 0.8 V                                                                                |

|        | 0101 = 1.0 V (Default)                                                                      |

|        | 0110 = 1.2 V                                                                                |

|        | 0111 = 1.4 V                                                                                |

|        | 1000 = 1.6 V                                                                                |

|        | 1001 = 1.8 V                                                                                |

|        | 1010–1111 = Reserved                                                                        |

# **Trim Bit Address Space**

All available Trim bit addresses and their functions are listed in Table 90 through Table 95.

# Trim Bit Address 0000H

| Bit       | 7                                               | 6        | 5     | 4           | 3           | 2    | 1   | 0   |  |  |

|-----------|-------------------------------------------------|----------|-------|-------------|-------------|------|-----|-----|--|--|

| Field     |                                                 | Reserved |       |             |             |      |     |     |  |  |

| RESET     | U                                               | U        | U     | U           | U           | U    | U   | U   |  |  |

| R/W       | R/W                                             | R/W      | R/W   | R/W         | R/W         | R/W  | R/W | R/W |  |  |

| Address   |                                                 |          | Infor | mation Page | e Memory 00 | 020H |     |     |  |  |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |          |       |             |             |      |     |     |  |  |

| Bit       | Description                                     |          |       |             |             |      |     |     |  |  |

| [7:0]     | Reserved                                        | leserved |       |             |             |      |     |     |  |  |

#### Table 90. Trim Options Bits at Address 0000H

These bits are reserved; altering this register may result in incorrect device operation.

# Trim Bit Address 0001H

#### Table 91. Trim Option Bits at 0001H

| Bit                                             | 7                             | 6        | 5   | 4   | 3   | 2   | 1   | 0   |  |

|-------------------------------------------------|-------------------------------|----------|-----|-----|-----|-----|-----|-----|--|

| Field                                           |                               | Reserved |     |     |     |     |     |     |  |

| RESET                                           | U                             | U        | U   | U   | U   | U   | U   | U   |  |

| R/W                                             | R/W                           | R/W      | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address                                         | Information Page Memory 0021H |          |     |     |     |     |     |     |  |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                               |          |     |     |     |     |     |     |  |

# Bit Description [7:0] Reserved These bits are reserved; altering this register may result in incorrect device operation.

| LVD_TRIM | LVD Threshold (V)<br>Typical | Description             |

|----------|------------------------------|-------------------------|

| 00000    | 3.60                         | Maximum LVD threshold   |

| 00001    | 3.55                         |                         |

| 00010    | 3.50                         |                         |

| 00010    | 3.45                         |                         |

| 00100    | 3.40                         |                         |

| 00100    | 3.35                         |                         |

| 00101    | 3.30                         |                         |

| 00110    | 3.25                         |                         |

| 01000    | 3.20                         |                         |

|          |                              |                         |

| 01001    | 3.15                         |                         |

| 01010    | 3.10                         | Default on Reset        |

| 01011    | 3.05                         |                         |

| 01100    | 3.00                         |                         |

| 01101    | 2.95                         |                         |

| 01110    | 2.90                         |                         |

| 01111    | 2.85                         |                         |

| 10000    | 2.80                         |                         |

| 10001    | 2.75                         |                         |

| 10010    | 2.70                         |                         |

| 10011    | 2.70                         |                         |

| to       | to                           | Minimum LVD there shall |

| 11111    | 1.65                         | Minimum LVD threshold   |

### Table 94. LVD Trim Values

## **Byte Write**

To write a byte to the NVDS array, the user code must first push the address, then the data byte onto the stack. The user code issues a CALL instruction to the address of the byte-write routine (0x10B3). At the return from the sub-routine, the write status byte resides in working register R0. The bit fields of this status byte are defined in Table 106. The contents of the status byte are undefined for write operations to illegal addresses. Also, user code must pop the address and data bytes off the stack.

The write routine uses 13 bytes of stack space in addition to the two bytes of address and data pushed by the user. Sufficient memory must be available for this stack usage.

Because of the Flash memory architecture, NVDS writes exhibit a nonuniform execution time. In general, a write takes  $251 \mu s$  (assuming a 20MHz system clock). Every 400 to 500 writes, however, a maintenance operation is necessary. In this rare occurrence, the write takes up to 61 ms to complete. Slower system clock speeds result in proportionally higher execution times.

NVDS byte writes to invalid addresses (those exceeding the NVDS array size) have no effect. Illegal write operations have a  $2\mu s$  execution time.

| Bit              | 7 | 6    | 5     | 4 | 3    | 2  | 1   | 0   |

|------------------|---|------|-------|---|------|----|-----|-----|

| Field            |   | Rese | erved |   | RCPY | PF | AWE | DWE |

| Default<br>Value | 0 | 0    | 0     | 0 | 0    | 0  | 0   | 0   |

#### Table 106. Write Status Byte

| Bit   | Description                                                                                                 |

|-------|-------------------------------------------------------------------------------------------------------------|

| [7:4] | Reserved<br>These bits are reserved and must be programmed to 0000.                                         |

| [3]   | <b>Recopy Subroutine Executed</b>                                                                           |

| RCPY  | A recopy subroutine was executed. These operations take significantly longer than a normal write operation. |

| [2]   | <b>Power Failure Indicator</b>                                                                              |

| PF    | A power failure or system reset occurred during the most recent attempted write to the NVDS array.          |

| [1]   | Address Write Error                                                                                         |

| AWE   | An address byte failure occurred during the most recent attempted write to the NVDS array.                  |

| [0]   | Data Write Error                                                                                            |

| DWE   | A data byte failure occurred during the most recent attempted write to the NVDS array.                      |

host is the character 80H. The character 80H has eight continuous bits Low (one Start bit plus 7 data bits), framed between High bits. The Auto-Baud Detector measures this period and sets the OCD Baud Rate Generator accordingly.

The Auto-Baud Detector/Generator is clocked by the system clock. The minimum baud rate is the system clock frequency divided by 512. For optimal operation with asynchronous datastreams, the maximum recommended baud rate is the system clock frequency divided by 8. The maximum possible baud rate for asynchronous datastreams is the system clock frequency divided by 4, but this theoretical maximum is possible only for low noise designs with clean signals. Table 108 lists minimum and recommended maximum baud rates for sample crystal frequencies.

| System Clock<br>Frequency (MHz) | Recommended Maximum<br>Baud Rate (Kbps) | Recommended<br>Standard PC Baud<br>Rate (bps) | Minimum Baud<br>Rate (Kbps) |

|---------------------------------|-----------------------------------------|-----------------------------------------------|-----------------------------|

| 20.0                            | 2500.0                                  | 1,843,200                                     | 39                          |

| 1.0                             | 125.0                                   | 115,200                                       | 1.95                        |

| 0.032768 (32kHz)                | 4.096                                   | 2,400                                         | 0.064                       |

#### Table 108. OCD Baud-Rate Limits

If the OCD receives a Serial Break (nine or more continuous bits Low) the Auto-Baud Detector/Generator resets. Reconfigure the Auto-Baud Detector/Generator by sending 80H.

### **OCD Serial Errors**

The On-Chip Debugger can detect any of the following error conditions on the DBG pin:

- Serial Break (a minimum of nine continuous bits Low)

- Framing Error (received Stop bit is Low)

- Transmit Collision (OCD and host simultaneous transmission detected by the OCD)

When the OCD detects one of these errors, it aborts any command currently in progress, transmits a four character long Serial Break back to the host and resets the Auto-Baud Detector/Generator. A Framing Error or Transmit Collision may be caused by the host sending a Serial Break to the OCD. Because of the open-drain nature of the interface, returning a Serial Break break back to the host only extends the length of the Serial Break if the host releases the Serial Break early.

The host transmits a Serial Break on the DBG pin when first connecting to the Z8 Encore! XP F082A Series devices or when recovering from an error. A Serial Break from the host resets the Auto-Baud Generator/Detector but does not reset the OCD Control Register. A

| Mnemonic | Operands        | Instruction                   |

|----------|-----------------|-------------------------------|

| BRK      | _               | On-Chip Debugger Break        |

| BTJ      | p, bit, src, DA | Bit Test and Jump             |

| BTJNZ    | bit, src, DA    | Bit Test and Jump if Non-Zero |

| BTJZ     | bit, src, DA    | Bit Test and Jump if Zero     |

| CALL     | dst             | Call Procedure                |

| DJNZ     | dst, src, RA    | Decrement and Jump Non-Zero   |

| IRET     | _               | Interrupt Return              |

| JP       | dst             | Jump                          |

| JP cc    | dst             | Jump Conditional              |

| JR       | DA              | Jump Relative                 |

| JR cc    | DA              | Jump Relative Conditional     |

| RET      | _               | Return                        |

| TRAP     | vector          | Software Trap                 |

### Table 126. Program Control Instructions

#### Table 127. Rotate and Shift Instructions

| MnemonicOperandsInstructionBSWAPdstBit SwapRLdstRotate Left |

|-------------------------------------------------------------|

|                                                             |

|                                                             |

| RLC dst Rotate Left through Carry                           |

| RR dst Rotate Right                                         |

| RRC dst Rotate Right through Ca                             |

| SRA dst Shift Right Arithmetic                              |

| SRL dst Shift Right Logical                                 |

| SWAP dst Swap Nibbles                                       |

|               |                                         |         |              | •           |   |   |       |   |   |   |                |                 |

|---------------|-----------------------------------------|---------|--------------|-------------|---|---|-------|---|---|---|----------------|-----------------|

| Assembly      |                                         |         | lress<br>ode | _ Opcode(s) |   |   | Flags |   |   |   | Fetch<br>Cycle | Instr.<br>Cycle |

| Mnemonic      | Symbolic Operation                      | dst src |              | (Hex)       |   | Ζ | S     | V | D | Н | s              | s               |

| JR dst        | $PC \gets PC + X$                       | DA      |              | 8B          | _ | _ | _     | _ | _ | _ | 2              | 2               |

| JR cc, dst    | if cc is true<br>PC $\leftarrow$ PC + X | DA      |              | 0B-FB       | _ | - | -     | - | - | _ | 2              | 2               |

| LD dst, rc    | dst $\leftarrow$ src                    | r       | IM           | 0C-FC       | _ | _ | _     | _ | _ | _ | 2              | 2               |

|               |                                         | r       | X(r)         | C7          | - |   |       |   |   |   | 3              | 3               |

|               |                                         | X(r)    | r            | D7          | - |   |       |   |   |   | 3              | 4               |

|               |                                         | r       | lr           | E3          | - |   |       |   |   |   | 2              | 3               |

|               |                                         | R       | R            | E4          | - |   |       |   |   |   | 3              | 2               |

|               |                                         | R       | IR           | E5          | - |   |       |   |   |   | 3              | 4               |

|               |                                         | R       | IM           | E6          | _ |   |       |   |   |   | 3              | 2               |

|               |                                         | IR      | IM           | E7          | - |   |       |   |   |   | 3              | 3               |

|               |                                         | lr      | r            | F3          | _ |   |       |   |   |   | 2              | 3               |

|               |                                         | IR      | R            | F5          | _ |   |       |   |   |   | 3              | 3               |

| LDC dst, src  | dst $\leftarrow$ src                    | r       | Irr          | C2          | _ | _ | _     | _ | _ | _ | 2              | 5               |

|               |                                         | lr      | Irr          | C5          | _ |   |       |   |   |   | 2              | 9               |

|               |                                         | Irr     | r            | D2          | _ |   |       |   |   |   | 2              | 5               |

| LDCI dst, src | dst ← src                               | lr      | Irr          | C3          | _ | _ | _     | _ | _ | _ | 2              | 9               |

|               | r ← r + 1<br>rr ← rr + 1                | Irr     | lr           | D3          | _ |   |       |   |   |   | 2              | 9               |

| LDE dst, src  | dst ← src                               | r       | Irr          | 82          | _ | _ | _     | _ | _ | _ | 2              | 5               |

|               |                                         | Irr     | r            | 92          | - |   |       |   |   |   | 2              | 5               |

| LDEI dst, src | dst $\leftarrow$ src                    | lr      | Irr          | 83          | _ | - | _     | _ | _ | - | 2              | 9               |

|               | r ← r + 1<br>rr ← rr + 1                | Irr     | lr           | 93          | - |   |       |   |   |   | 2              | 9               |

| LDWX dst, src | dst ← src                               | ER      | ER           | 1FE8        | _ | _ | _     | _ | _ | _ | 5              | 4               |

### Table 128. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 =Set to 1.

### Z8 Encore! XP<sup>®</sup> F082A Series **Product Specification**

|   |             |             |                     |                  |                     |                | Lo                                      | ower Nil                                                           | ble (He         | x)               |              |            |             |             |           |             |

|---|-------------|-------------|---------------------|------------------|---------------------|----------------|-----------------------------------------|--------------------------------------------------------------------|-----------------|------------------|--------------|------------|-------------|-------------|-----------|-------------|

|   | 0           | 1           | 2                   | 3                | 4                   | 5              | 6                                       | 7                                                                  | 8               | 9                | А            | В          | С           | D           | Е         | F           |

|   | 1.1         | 2.2         | 2.3                 | 2.4              | 3.3                 | 3.4            | 3.3                                     | 3.4                                                                | 4.3             | 4.3              | 2.3          | 2.2        | 2.2         | 3.2         | 1.2       | 1.2         |

| 0 | BRK         | SRP<br>IM   | <b>ADD</b><br>r1,r2 | ADD<br>r1,lr2    | <b>ADD</b><br>R2,R1 | ADD<br>IR2,R1  | ADD<br>R1,IM                            | ADD<br>IR1,IM                                                      | ADDX<br>ER2,ER1 | ADDX<br>IM,ER1   | DJNZ<br>r1,X | JR<br>cc,X | LD<br>r1,IM | JP<br>cc,DA | INC<br>r1 | NOP         |

|   | 2.2         | 2.3         | 2.3                 | 2.4              | 3.3                 | 3.4            | 3.3                                     | 3.4                                                                | 4.3             | 4.3              | 11,∧         |            | 11,111      | CC,DA       |           | See 2nd     |

| 1 | RLC         | RLC         | ADC                 | ADC              | ADC                 | ADC            | ADC                                     | ADC                                                                | ADCX            |                  |              |            |             |             |           | Opcode      |

|   | R1          | IR1         | r1,r2               | r1,lr2           | R2,R1               | IR2,R1         | R1,IM                                   | IR1,IM                                                             | ER2,ER1         | IM,ER1           |              |            |             |             |           | Мар         |

| - | 2.2         | 2.3         | 2.3                 | 2.4              | 3.3                 | 3.4            | 3.3                                     | 3.4                                                                | 4.3             | 4.3              |              |            |             |             |           | 1           |

| 2 | INC<br>R1   | INC<br>IR1  | SUB<br>r1,r2        | SUB<br>r1,lr2    | <b>SUB</b><br>R2,R1 | SUB<br>IR2,R1  | SUB<br>R1,IM                            | SUB<br>IR1,IM                                                      | SUBX<br>ER2,ER1 | SUBX<br>IM,ER1   |              |            |             |             |           | _           |

|   | 2.2         | 2.3         | 2.3                 | 2.4              | 3.3                 | 3.4            | 3.3                                     | 3.4                                                                | 4.3             | 4.3              |              |            |             |             |           |             |

| 3 | DEC         | DEC         | SBC                 | SBC              | SBC                 | SBC            | SBC                                     | SBC                                                                | SBCX            | SBCX             |              |            |             |             |           |             |

|   | R1          | IR1         | r1,r2               | r1,lr2           | R2,R1               | IR2,R1         | R1,IM                                   | IR1,IM                                                             | ER2,ER1         | IM,ER1           |              |            |             |             |           |             |

|   | 2.2         | 2.3         | 2.3                 | 2.4              | 3.3                 | 3.4            | 3.3                                     | 3.4                                                                | 4.3             | 4.3              |              |            |             |             |           |             |

| 4 | DA<br>R1    | DA<br>IR1   | OR<br>r1,r2         | OR<br>r1,lr2     | <b>OR</b><br>R2,R1  | OR<br>IR2,R1   | OR<br>R1,IM                             | OR<br>IR1,IM                                                       | ORX<br>ER2,ER1  | ORX<br>IM,ER1    |              |            |             |             |           |             |

|   | 2.2         | 2.3         | 2.3                 | 2.4              | 3.3                 | 3.4            | 3.3                                     | 3.4                                                                | 4.3             | 4.3              |              |            |             |             |           | 1.2         |

| 5 | POP         | POP         | AND                 | AND              | AND                 | AND            | AND                                     | AND                                                                | ANDX            | ANDX             |              |            |             |             |           | WDT         |

|   | R1          | IR1         | r1,r2               | r1,lr2           | R2,R1               | IR2,R1         | R1,IM                                   | IR1,IM                                                             | ER2,ER1         |                  |              |            |             |             |           |             |

| 6 | 2.2<br>COM  | 2.3<br>COM  | 2.3<br>TCM          | 2.4<br>TCM       | 3.3<br>TCM          | 3.4<br>TCM     | 3.3<br>TCM                              | 3.4<br>TCM                                                         | 4.3<br>TCMX     | 4.3<br>TCMX      |              |            |             |             |           | 1.2<br>STOP |

| 0 | R1          | IR1         | r1,r2               | r1,lr2           | R2,R1               | IR2,R1         | R1,IM                                   | IR1,IM                                                             | ER2,ER1         | IM,ER1           |              |            |             |             |           | 3105        |

|   | 2.2         | 2.3         | 2.3                 | 2.4              | 3.3                 | 3.4            | 3.3                                     | 3.4                                                                | 4.3             | 4.3              |              |            |             |             |           | 1.2         |

| 7 | PUSH        | PUSH        | тм                  | тм               | тм                  | тм             | тм                                      | тм                                                                 | тмх             | тмх              |              |            |             |             |           | HALT        |

|   | R2          | IR2         | r1,r2               | r1,lr2           | R2,R1               | IR2,R1         | R1,IM                                   | IR1,IM                                                             | ER2,ER1         | IM,ER1           |              |            |             |             |           |             |

| 8 | 2.5<br>DECW | 2.6<br>DECW | 2.5<br>LDE          | 2.9<br>LDEI      | 3.2<br>LDX          | 3.3<br>LDX     | 3.4<br>LDX                              | 3.5<br><b>LDX</b>                                                  | 3.4<br>LDX      | 3.4<br>LDX       |              |            |             |             |           | 1.2<br>DI   |

| 0 | RR1         | IRR1        | r1,Irr2             | lr1,lrr2         | r1,ER2              | Ir1,ER2        | IRR2,R1                                 | IRR2,IR1                                                           | r1,rr2,X        | rr1,r2,X         |              |            |             |             |           | 5.          |

|   | 2.2         | 2.3         | 2.5                 | 2.9              | 3.2                 | 3.3            | 3.4                                     | 3.5                                                                | 3.3             | 3.5              |              |            |             |             |           | 1.2         |

| 9 | RL          | RL          | LDE                 | LDEI             | LDX                 | LDX            | LDX                                     | LDX                                                                | LEA             | LEA              |              |            |             |             |           | EI          |

|   | R1<br>2.5   | IR1<br>2.6  | r2,Irr1<br>2.3      | lr2,Irr1<br>2.4  | r2,ER1<br>3.3       | Ir2,ER1<br>3.4 | R2,IRR1<br>3.3                          | IR2,IRR1<br>3.4                                                    | r1,r2,X<br>4.3  | rr1,rr2,X<br>4.3 |              |            |             |             |           | 1.4         |

| А | INCW        | INCW        | CP                  | CP               | CP                  | 3.4<br>CP      | CP                                      | 3.4<br>CP                                                          | CPX             | CPX              |              |            |             |             |           | RET         |

|   | RR1         | IRR1        | r1,r2               | r1,lr2           | R2,R1               | IR2,R1         | R1,IM                                   | IR1,IM                                                             | ER2,ER1         | IM,ER1           |              |            |             |             |           |             |

| _ | 2.2         | 2.3         | 2.3                 | 2.4              | 3.3                 | 3.4            | 3.3                                     | 3.4                                                                | 4.3             | 4.3              |              |            |             |             |           | 1.5         |

| В | CLR<br>R1   | IR1         | XOR<br>r1,r2        | XOR              | <b>XOR</b><br>R2,R1 | XOR<br>IR2,R1  | XOR<br>R1,IM                            | XOR<br>IR1,IM                                                      | XORX<br>ER2,ER1 | XORX<br>IM,ER1   |              |            |             |             |           | IRET        |

|   | 2.2         | 2.3         | 2.5                 | r1,lr2<br>2.9    | 2.3                 | 2.9            | K I,IIVI                                | 3.4                                                                | 3.2             | IIVI,EKI         |              |            |             |             |           | 1.2         |

| С | RRC         | RRC         | LDC                 | LDCI             | JP                  | LDC            |                                         | LD                                                                 | PUSHX           |                  |              |            |             |             |           | RCF         |

|   | R1          | IR1         | r1,Irr2             | lr1,lrr2         | IRR1                | lr1,lrr2       |                                         | r1,r2,X                                                            | ER2             |                  |              |            |             |             |           |             |

| - | 2.2         | 2.3         | 2.5                 | 2.9              | 2.6                 | 2.2            | 3.3                                     | 3.4                                                                | 3.2             |                  |              |            |             |             |           | 1.2         |

| D | SRA<br>R1   | SRA<br>IR1  | LDC<br>r2,Irr1      | LDCI<br>Ir2,Irr1 | CALL<br>IRR1        | BSWAP<br>R1    | DA                                      | LD<br>r2,r1,X                                                      | POPX<br>ER1     |                  |              |            |             |             |           | SCF         |

|   | 2.2         | 2.3         | 2.2                 | 2.3              | 3.2                 | 3.3            | 3.2                                     | 3.3                                                                | 4.2             | 4.2              |              |            |             |             |           | 1.2         |

| Е | RR          | RR          | BIT                 | LD               | LD                  | LD             | LD                                      | LD                                                                 | LDX             | LDX              |              |            |             |             | i I       | CCF         |

|   | R1          | IR1         | p,b,r1              | r1,lr2           | R2,R1               | IR2,R1         | R1,IM                                   |                                                                    | ER2,ER1         | IM,ER1           |              | 1          |             |             |           |             |

| F | 2.2<br>SWAP | 2.3<br>SWAP | 2.6<br><b>TRAP</b>  | 2.3<br>LD        | 2.8<br>MULT         | 3.3<br>LD      | 3.3<br><b>BTJ</b>                       | 3.4<br><b>BTJ</b>                                                  |                 |                  |              |            |             |             |           |             |

| г | R1          | IR1         | Vector              | Ir1,r2           | RR1                 | R2,IR1         | <b>р,b,r1,X</b>                         |                                                                    |                 |                  | V            | V          |             |             |           |             |

|   |             |             |                     | ,                |                     |                | , . , . , . , . , . , . , . , . , . , . | , , <b>.</b> . |                 |                  |              |            |             |             |           |             |

Lower Nibble (Hex)

Figure 31. First Opcode Map

| Part Number         | Flash    | RAM     | SDVN  | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |

|---------------------|----------|---------|-------|-----------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|

| Z8 Encore! XP F082A |          |         |       |           |            |                     |                     |                |            |                    |                     |

| Standard Temperatu  |          |         |       |           |            |                     |                     |                |            |                    |                     |

| Z8F041APB020SG      | 4 KB     | 1KB     | 128 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 8-pin package  |

| Z8F041AQB020SG      | 4 KB     | 1KB     | 128 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | QFN 8-pin package   |

| Z8F041ASB020SG      | 4 KB     | 1KB     | 128 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 8-pin package  |

| Z8F041ASH020SG      | 4 KB     | 1KB     | 128 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 20-pin package |

| Z8F041AHH020SG      | 4 KB     | 1KB     | 128 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 20-pin package |

| Z8F041APH020SG      | 4 KB     | 1KB     | 128 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 20-pin package |

| Z8F041ASJ020SG      | 4 KB     | 1KB     | 128 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 28-pin package |

| Z8F041AHJ020SG      | 4 KB     | 1KB     | 128 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 28-pin package |

| Z8F041APJ020SG      | 4 KB     | 1KB     | 128 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 28-pin package |

| Extended Temperatu  | re: –40° | C to 10 | )5°C  |           |            |                     |                     |                |            |                    |                     |

| Z8F041APB020EG      | 4 KB     | 1KB     | 128 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 8-pin package  |

| Z8F041AQB020EG      | 4 KB     | 1KB     | 128 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | QFN 8-pin package   |

| Z8F041ASB020EG      | 4 KB     | 1KB     | 128 B | 6         | 13         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 8-pin package  |

| Z8F041ASH020EG      | 4 KB     | 1KB     | 128 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 20-pin package |

| Z8F041AHH020EG      | 4 KB     | 1KB     | 128 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 20-pin package |

| Z8F041APH020EG      | 4 KB     | 1KB     | 128 B | 17        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 20-pin package |

| Z8F041ASJ020EG      | 4 KB     | 1KB     | 128 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SOIC 28-pin package |

| Z8F041AHJ020EG      | 4 KB     | 1KB     | 128 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | SSOP 28-pin package |

| Z8F041APJ020EG      | 4 KB     | 1KB     | 128 B | 25        | 19         | 2                   | 0                   | 1              | 1          | 0                  | PDIP 28-pin package |

### Table 148. Z8 Encore! XP F082A Series Ordering Matrix

254

|                        | Flash | RAM     | NVDS    | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description |

|------------------------|-------|---------|---------|-----------|------------|---------------------|---------------------|----------------|------------|--------------------|-------------|

| Z8 Encore! XP F082A Se | eries | Develo  | pment   | Kit       |            |                     |                     |                |            |                    |             |

| Z8F08A28100KITG        |       | Z8 Enco | ore! XP | F082/     | A Ser      | ies 2               | 8-Pin               | Dev            | elopn      | nent K             | it          |

| Z8F04A28100KITG        |       | Z8 Enco | ore! XP | F042/     | A Ser      | ies 2               | 8-Pin               | Dev            | elopn      | nent K             | it          |

| Z8F04A08100KITG        |       | Z8 Enco | ore! XP | F042/     | A Ser      | ies 8               | -Pin l              | Deve           | opme       | ent Kit            |             |

| ZUSBSC00100ZACG        |       | USB Sn  | nart Ca | ble Ac    | cess       | ory K               | it                  |                |            |                    |             |

| ZUSBOPTSC01ZACG        |       | USB Op  | to-Isol | ated S    | mart       | Cabl                | e Aco               | cesso          | ry Kit     |                    |             |

| ZENETSC0100ZACG        |       | Etherne | t Smar  | t Cable   | e Acc      | esso                | ry Kit              |                |            |                    |             |

### Table 148. Z8 Encore! XP F082A Series Ordering Matrix

Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

UARTx control 1 (UxCTL1) 112 UARTx receive data (UxRXD) 116 UARTx status 0 (UxSTAT0) 114 UARTx status 1 (UxSTAT1) 115 UARTx transmit data (UxTXD) 116 Watchdog Timer control (WDTCTL) 30, 96, 141, 196 Watchdog Timer reload high byte (WDTH) 97 Watchdog Timer reload low byte (WDTL) 98 Watchdog Timer reload upper byte (WDTU) 97 register file 15 register pair 206 register pointer 207 reset and stop mode characteristics 23 and Stop Mode Recovery 22 carry flag 209 sources 24 **RET 211** return 211 RL 211 **RLC 211** rotate and shift instuctions 211 rotate left 211 rotate left through carry 211 rotate right 211 rotate right through carry 211 **RP 207** RR 206, 211

rr 206 RRC 211

# S

SBC 208 SCF 209, 210 second opcode map after 1FH 225 set carry flag 209, 210 set register pointer 210 shift right arithmatic 211 shift right logical 211 signal descriptions 10 single-shot conversion (ADC) 126 software trap 211 source operand 207 SP 207 SRA 211 src 207 SRL 211 **SRP 210** stack pointer 207 **STOP 210** STOP mode 32 stop mode 210 Stop Mode Recovery sources 27 using a GPIO port pin transition 28 using Watchdog Timer time-out 28 stop mode recovery sources 29 using a GPIO port pin transition 29 **SUB 208** subtract 208 subtract - extended addressing 208 subtract with carry 208 subtract with carry - extended addressing 208 **SUBX 208 SWAP 211** swap nibbles 211 symbols, additional 207

# Т

PRELIMINARY

TCM 209 TCMX 209 test complement under mask 209 test complement under mask - extended addressing 209 test under mask 209 test under mask - extended addressing 209 timer signals 10 timers 70 architecture 70 block diagram 71 CAPTURE mode 79, 80, 87, 88 CAPTURE/COMPARE mode 83, 88 COMPARE mode 81, 87