Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 23                                                           |

| Program Memory Size        | 2KB (2K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 64 x 8                                                       |

| RAM Size                   | 512 x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 8x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 105°C (TA)                                           |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 28-SSOP (0.173", 4.40mm Width)                               |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f022ahj020eg    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Operating Modes<br>Crystal Oscillator Operation<br>Oscillator Operation with an External RC Network                                                                                             | . 198                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| Internal Precision Oscillator                                                                                                                                                                   |                                                             |

| eZ8 CPU Instruction Set<br>Assembly Language Programming Introduction<br>Assembly Language Syntax<br>eZ8 CPU Instruction Notation<br>eZ8 CPU Instruction Classes<br>eZ8 CPU Instruction Summary | . 204<br>. 205<br>. 206<br>. 207                            |

| Opcode Maps                                                                                                                                                                                     | . 222                                                       |

| Electrical Characteristics                                                                                                                                                                      | . 226<br>. 227<br>. 232<br>. 233<br>. 240<br>. 241<br>. 242 |

| Packaging                                                                                                                                                                                       | . 245                                                       |

| Ordering Information<br>Part Number Suffix Designations                                                                                                                                         |                                                             |

| Index                                                                                                                                                                                           | . 256                                                       |

| Customer Support                                                                                                                                                                                | . 265                                                       |

# List of Tables

| Table 1.  | Z8 Encore! XP F082A Series Family Part Selection Guide 2           |

|-----------|--------------------------------------------------------------------|

| Table 2.  | Signal Descriptions                                                |

| Table 3.  | Pin Characteristics (20- and 28-pin Devices) 13                    |

| Table 4.  | Pin Characteristics (8-Pin Devices) 14                             |

| Table 5.  | Z8 Encore! XP F082A Series Program Memory Maps 16                  |

| Table 6.  | Z8 Encore! XP F082A Series Flash Memory Information Area Map 17    |

| Table 7.  | Register File Address Map 18                                       |

| Table 8.  | Reset and Stop Mode Recovery Characteristics and Latency 23        |

| Table 9.  | Reset Sources and Resulting Reset Type 24                          |

| Table 10. | Stop Mode Recovery Sources and Resulting Action                    |

| Table 11. | Reset Status Register (RSTSTAT)                                    |

| Table 12. | Reset and Stop Mode Recovery Bit Descriptions                      |

| Table 13. | Power Control Register 0 (PWRCTL0)                                 |

| Table 14. | Port Availability by Device and Package Type                       |

| Table 15. | Port Alternate Function Mapping (Non 8-Pin Parts) 40               |

| Table 16. | Port Alternate Function Mapping (8-Pin Parts)                      |

| Table 17. | GPIO Port Registers and Subregisters                               |

| Table 18. | Port A–D GPIO Address Registers (PxADDR)                           |

| Table 19. | Port A–D GPIO Address Registers by Bit Description                 |

| Table 20. | Port A–D Control Registers (PxCTL)                                 |

| Table 21. | Port A–D Data Direction Subregisters (PxDD) 46                     |

| Table 22. | Port A–D Alternate Function Subregisters (PxAF)                    |

| Table 23. | Port A–D Output Control Subregisters (PxOC)                        |

| Table 24. | Port A–D High Drive Enable Subregisters (PxHDE)                    |

| Table 25. | Port A–D Stop Mode Recovery Source Enable Subregisters (PxSMRE) 49 |

| Table 26. | Port A–D Pull-Up Enable Subregisters (PxPUE)                       |

| Table 27. | Port A–D Alternate Function Set 2 Subregisters (PxAFS2) 51         |

| Table 28. | Port A–D Alternate Function Set 1 Subregisters (PxAFS1) 51         |

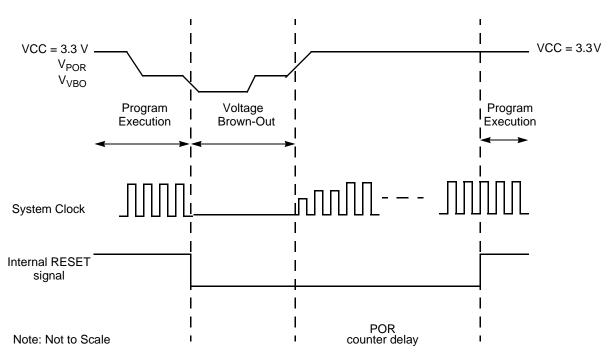

Figure 6. Voltage Brown-Out Reset Operation

The POR level is greater than the VBO level by the specified hysteresis value. This ensures that the device undergoes a Power-On Reset after recovering from a VBO condition.

### Watchdog Timer Reset

If the device is operating in NORMAL or HALT Mode, the Watchdog Timer can initiate a System Reset at time-out if the WDT\_RES Flash option bit is programmed to 1, i.e., the unprogrammed state of the WDT\_RES Flash option bit. If the bit is programmed to 0, it configures the Watchdog Timer to cause an interrupt, not a System Reset, at time-out.

The WDT bit in the Reset Status (RSTSTAT) Register is set to signify that the reset was initiated by the Watchdog Timer.

### **External Reset Input**

The  $\overline{\text{RESET}}$  pin has a Schmitt-Triggered input and an internal pull-up resistor. Once the  $\overline{\text{RESET}}$  pin is asserted for a minimum of four system clock cycles, the device progresses through the System Reset sequence. Because of the possible asynchronicity of the system clock and reset signals, the required reset duration may be as short as three clock periods

| Port                | Pin | Mnemonic                           | Alternate Function Description            | Alternate Function<br>Set Register AFS1 |

|---------------------|-----|------------------------------------|-------------------------------------------|-----------------------------------------|

| Port C <sup>5</sup> | PC0 | Reserved                           |                                           | AFS1[0]: 0                              |

|                     |     | ANA4/CINP                          | ADC or Comparator Input                   | AFS1[0]: 1                              |

|                     | PC1 | Reserved                           |                                           | AFS1[1]: 0                              |

|                     |     | ANA5/CINN                          | ADC or Comparator Input                   | AFS1[1]: 1                              |

|                     | PC2 | Reserved                           |                                           | AFS1[2]: 0                              |

|                     |     | ANA6/V <sub>REF</sub> <sup>4</sup> | ADC Analog Input or ADC Voltage Reference | AFS1[2]: 1                              |

|                     | PC3 | COUT                               | Comparator Output                         | AFS1[3]: 0                              |

|                     |     | Reserved                           |                                           | AFS1[3]: 1                              |

|                     | PC4 | Reserved                           |                                           | AFS1[4]: 0                              |

|                     |     |                                    |                                           | AFS1[4]: 1                              |

|                     | PC5 | Reserved                           |                                           | AFS1[5]: 0                              |

|                     |     |                                    |                                           | AFS1[5]: 1                              |

|                     | PC6 | Reserved                           |                                           | AFS1[6]: 0                              |

|                     |     |                                    |                                           | AFS1[6]: 1                              |

|                     | PC7 | Reserved                           |                                           | AFS1[7]: 0                              |

|                     |     |                                    |                                           | AFS1[7]: 1                              |

| Port D <sup>6</sup> | PD0 | RESET                              | External Reset                            | N/A                                     |

#### Table 15. Port Alternate Function Mapping (Non 8-Pin Parts) (Continued)

Notes:

2. Whether PA0/PA6 takes on the timer input or timer output complement function depends on the timer configuration. See the <u>Timer Pin Signal Operation</u> section on page 84 for details.

Because there are at most two choices of alternate function for any pin of Port B, the Alternate Function Set Register AFS2 is not used to select the function. Alternate function selection must also be enabled. See the <u>Port</u> <u>A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

4. V<sub>REF</sub> is available on PB5 in 28-pin products and on PC2 in 20-pin parts.

Because there are at most two choices of alternate function for any pin of Port C, the Alternate Function Set Register AFS2 is not used to select the function. Alternate function selection must also be enabled. See the <u>Port</u> <u>A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

6. Because there is only a single alternate function for the Port PD0 pin, the Alternate Function Set registers are not implemented for Port D. Enabling alternate function selections automatically enables the associated alternate function. See the Port A–D Alternate Function Subregisters (PxAF) section on page 47 for details.

Because there is only a single alternate function for each Port A pin, the Alternate Function Set registers are not implemented for Port A. Enabling alternate function selections automatically enables the associated alternate function. See the <u>Port A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

# **GPIO Interrupts**

Many of the GPIO port pins can be used as interrupt sources. Some port pins can be configured to generate an interrupt request on either the rising edge or falling edge of the pin input signal. Other port pin interrupt sources generate an interrupt when any edge occurs (both rising and falling). See the <u>GPIO Mode Interrupt Controller</u> chapter on page 55 for more information about interrupts using the GPIO pins.

# **GPIO Control Register Definitions**

Four registers for each port provide access to GPIO control, input data and output data. Table 17 lists these port registers. Use the Port A–D Address and Control registers together to provide access to subregisters for port configuration and control.

| Port Register Mnemonic    | Port Register Name                                          |

|---------------------------|-------------------------------------------------------------|

| P <i>x</i> ADDR           | Port A–D Address Register; selects subregisters.            |

| P <i>x</i> CTL            | Port A–D Control Register; provides access to subregisters. |

| PxIN                      | Port A–D Input Data Register.                               |

| P <i>x</i> OUT            | Port A–D Output Data Register.                              |

| Port Subregister Mnemonic | Port Register Name                                          |

| P <i>x</i> DD             | Data Direction.                                             |

| P <i>x</i> AF             | Alternate Function.                                         |

| P <i>x</i> OC             | Output Control (Open-Drain).                                |

| P <i>x</i> HDE            | High Drive Enable.                                          |

| P <i>x</i> SMRE           | Stop Mode Recovery Source Enable.                           |

| P <i>x</i> PUE            | Pull-up Enable.                                             |

| PxAFS1                    | Alternate Function Set 1.                                   |

| PxAFS2                    | Alternate Function Set 2.                                   |

Table 17. GPIO Port Registers and Subregisters

## **Port A–D Control Registers**

The Port A–D Control registers set the GPIO port operation. The value in the corresponding Port A–D Address Register determines which subregister is read from or written to by a Port A–D Control Register transaction; see Table 20.

| Bit     | 7                      | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|------------------------|-----------------------------|---|---|---|---|---|---|

| Field   |                        | PCTL                        |   |   |   |   |   |   |

| RESET   | 00H                    |                             |   |   |   |   |   |   |

| R/W     | R/W                    | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |

| Address | FD1H, FD5H, FD9H, FDDH |                             |   |   |   |   |   |   |

#### Table 20. Port A–D Control Registers (PxCTL)

| Bit   | Description                                                                                              |

|-------|----------------------------------------------------------------------------------------------------------|

| [7:0] | Port Control                                                                                             |

| PCTLx | The Port Control Register provides access to all subregisters that configure the GPIO port<br>operation. |

|       |                                                                                                          |

Note: x indicates the specific GPIO port pin number (7–0).

## Port A–D Data Direction Subregisters

The Port A–D Data Direction subregister is accessed through the Port A–D Control Register by writing 01H to the Port A–D Address Register; see Table 21.

| Bit     | 7         | 6                                                                                     | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----------|---------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|

| Field   | DD7       | DD6                                                                                   | DD5 | DD4 | DD3 | DD2 | DD1 | DD0 |

| RESET   | 1         | 1                                                                                     | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W     | R/W       | R/W                                                                                   | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | If 01H ir | If 01H in Port A–D Address Register, accessible through the Port A–D Control Register |     |     |     |     |     |     |

Table 21. Port A–D Data Direction Subregisters (PxDD)

| Bit   | Description                                                                                                                                                  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0] | Data Direction                                                                                                                                               |

| DDx   | These bits control the direction of the associated port pin. Port Alternate Function operation<br>overrides the Data Direction Register setting.             |

|       | 0 = Output. Data in the Port A–D Output Data Register is driven onto the port pin.                                                                           |

|       | <ul> <li>1 = Input. The port pin is sampled and the value written into the Port A–D Input Data Register.</li> <li>The output driver is tristated.</li> </ul> |

| Note: | x indicates the specific GPIO port pin number (7–0).                                                                                                         |

The window remains open until the count again reaches 8 (that is, 24 baud clock periods since the previous pulse was detected), giving the Endec a sampling window of minus four baud rate clocks to plus eight baud rate clocks around the expected time of an incoming pulse. If an incoming pulse is detected inside this window this process is repeated. If the incoming data is a logical 1 (no pulse), the Endec returns to the initial state and waits for the next falling edge. As each falling edge is detected, the Endec clock counter is reset, resynchronizing the Endec to the incoming signal, allowing the Endec to tolerate jitter and baud rate errors in the incoming datastream. Resynchronizing the Endec does not alter the operation of the UART, which ultimately receives the data. The UART is only synchronized to the incoming data stream when a Start bit is received.

# Infrared Encoder/Decoder Control Register Definitions

All infrared endec configuration and status information is set by the UART Control registers as defined in the <u>Universal Asynchronous Receiver/Transmitter</u> section on page 99.

**Caution:** To prevent spurious signals during IrDA data transmission, set the IREN bit in the UART Control 1 Register to 1 to enable the Infrared Encoder/Decoder before enabling the GPIO Port alternate function for the corresponding pin.

### Flash Operation Timing Using the Flash Frequency Registers

Before performing either a program or erase operation on Flash memory, you must first configure the Flash Frequency High and Low Byte registers. The Flash Frequency registers allow programming and erasing of the Flash with system clock frequencies ranging from 32kHz (32768Hz) through 20MHz.

The Flash Frequency High and Low Byte registers combine to form a 16-bit value, FFREQ, to control timing for Flash program and erase operations. The 16-bit binary Flash Frequency value must contain the system clock frequency (in kHz). This value is calculated using the following equation:

$FFREQ[15:0] = \frac{System Clock Frequency (Hz)}{1000}$

**Caution:** Flash programming and erasure are not supported for system clock frequencies below 32kHz (32768Hz) or above 20MHz. The Flash Frequency High and Low Byte registers must be loaded with the correct value to ensure operation of the Z8 Encore! XP F082A Series devices.

### Flash Code Protection Against External Access

The user code contained within the Flash memory can be protected against external access by the on-chip debugger. Programming the FRP Flash option bit prevents reading of the user code with the On-Chip Debugger. See the <u>Flash Option Bits</u> chapter on page 159 and the <u>On-Chip Debugger</u> chapter on page 180 for more information.

# Flash Code Protection Against Accidental Program and Erasure

The Z8 Encore! XP F082A Series provides several levels of protection against accidental program and erasure of the Flash memory contents. This protection is provided by a combination of the Flash option bits, the register locking mechanism, the page select redundancy and the sector level protection control of the Flash Controller.

#### Flash Code Protection Using the Flash Option Bits

The FRP and FWP Flash option bits combine to provide three levels of Flash Program Memory protection, as shown in Table 79. See the <u>Flash Option Bits</u> chapter on page 159 for more information.

| Bit                   | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [5:4]<br>OSC_SEL[1:0] | <ul> <li>Oscillator Mode Selection</li> <li>00 = On-chip oscillator configured for use with external RC networks (&lt;4MHz).</li> <li>01 = Minimum power for use with very low frequency crystals (32kHz to 1.0MHz).</li> <li>10 = Medium power for use with medium frequency crystals or ceramic resonators (0.5MHz to 5.0MHz).</li> <li>11 = Maximum power for use with high frequency crystals (5.0MHz to 20.0MHz). This setting is the default for unprogrammed (erased) Flash.</li> </ul> |

| [3]<br>VBO_AO         | <ul> <li>Voltage Brown-Out Protection Always On</li> <li>0 = Voltage Brown-Out Protection can be disabled in STOP Mode to reduce total power consumption. For the block to be disabled, the power control register bit must also be written (see the <u>Power Control Register Definitions</u> section on page 33).</li> <li>1 = Voltage Brown-Out Protection is always enabled including during STOP Mode. This setting is the default for unprogrammed (erased) Flash.</li> </ul>            |

| [2]<br>FRP            | <ul> <li>Flash Read Protect</li> <li>0 = User program code is inaccessible. Limited control features are available through the On-Chip Debugger.</li> <li>1 = User program code is accessible. All On-Chip Debugger commands are enabled. This setting is the default for unprogrammed (erased) Flash.</li> </ul>                                                                                                                                                                              |

| [1]                   | Reserved<br>This bit is reserved and must be programmed to 1.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| [0]<br>FWP            | <ul> <li>Flash Write Protect</li> <li>This Option Bit provides Flash Program Memory protection:</li> <li>0 = Programming and erasure disabled for all of Flash Program Memory. Programming,<br/>Page Erase and Mass Erase through User Code is disabled. Mass Erase is available<br/>using the On-Chip Debugger.</li> <li>1 = Programming, Page Erase and Mass Erase are enabled for all of Flash program<br/>memory.</li> </ul>                                                               |

163

### Flash Program Memory Address 0001H

#### Table 89. Flash Options Bits at Program Memory Address 0001H

| Bit     | 7                    | 6   | 5   | 4      | 3        | 2   | 1   | 0   |

|---------|----------------------|-----|-----|--------|----------|-----|-----|-----|

| Field   | Reserved             |     |     | XTLDIS | Reserved |     |     |     |

| RESET   | U                    | U   | U   | U      | U        | U   | U   | U   |

| R/W     | R/W                  | R/W | R/W | R/W    | R/W      | R/W | R/W | R/W |

| Address | Program Memory 0001H |     |     |        |          |     |     |     |

Note: U = Unchanged by Reset. R/W = Read/Write.

| Bit    | Description                                                                                                                                                                                                                                                                                                                                  |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:5]  | Reserved                                                                                                                                                                                                                                                                                                                                     |

|        | These bits are reserved and must be programmed to 111.                                                                                                                                                                                                                                                                                       |

| [4]    | State of the Crystal Oscillator at Reset                                                                                                                                                                                                                                                                                                     |

| XTLDIS | This bit only enables the crystal oscillator. Its selection as a system clock must be performed manually.                                                                                                                                                                                                                                    |

|        | 0 = Crystal oscillator is enabled during reset, resulting in longer reset timing.                                                                                                                                                                                                                                                            |

|        | 1 = Crystal oscillator is disabled during reset, resulting in shorter reset timing.                                                                                                                                                                                                                                                          |

|        | <b>Caution:</b> Programming the XTLDIS bit to zero on 8-pin versions of this device prevents any further communication via the debug pin due to the fact that the XIN and DBG functions are shared on pin 2 of this package. Do not program this bit to zero on 8-pin devices unless further debugging or Flash programming is not required. |

| [3:0]  | Reserved                                                                                                                                                                                                                                                                                                                                     |

These bits are reserved and must be programmed to 1111.

# **Trim Bit Address Space**

All available Trim bit addresses and their functions are listed in Table 90 through Table 95.

# Trim Bit Address 0000H

| Bit       | 7           | 6             | 5             | 4           | 3           | 2    | 1   | 0   |  |  |

|-----------|-------------|---------------|---------------|-------------|-------------|------|-----|-----|--|--|

| Field     |             | Reserved      |               |             |             |      |     |     |  |  |

| RESET     | U           | U             | U             | U           | U           | U    | U   | U   |  |  |

| R/W       | R/W         | R/W           | R/W           | R/W         | R/W         | R/W  | R/W | R/W |  |  |

| Address   |             |               | Infor         | mation Page | e Memory 00 | 020H |     |     |  |  |

| Note: U = | Unchanged b | by Reset. R/W | / = Read/Writ | e.          |             |      |     |     |  |  |

| Bit       | Description |               |               |             |             |      |     |     |  |  |

| [7:0]     | Reserved    |               |               |             |             |      |     |     |  |  |

#### Table 90. Trim Options Bits at Address 0000H

These bits are reserved; altering this register may result in incorrect device operation.

## Trim Bit Address 0001H

#### Table 91. Trim Option Bits at 0001H

| Bit                                             | 7                             | 6 | 5 | 4 | 3 | 2  | 1 | 0 |  |  |

|-------------------------------------------------|-------------------------------|---|---|---|---|----|---|---|--|--|

| Field                                           | Reserved                      |   |   |   |   |    |   |   |  |  |

| RESET                                           | U                             | U | U | U | U | UU |   |   |  |  |

| R/W                                             | R/W R/W R/W R/W R/W R/W R/W   |   |   |   |   |    |   |   |  |  |

| Address                                         | Information Page Memory 0021H |   |   |   |   |    |   |   |  |  |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                               |   |   |   |   |    |   |   |  |  |

# Bit Description [7:0] Reserved These bits are reserved; altering this register may result in incorrect device operation.

# Trim Bit Address 0004H

#### Table 95. Trim Option Bits at 0004H

| Bit                                             | 7                             | 6   | 5   | 4   | 3   | 2           | 1 | 0 |  |  |  |

|-------------------------------------------------|-------------------------------|-----|-----|-----|-----|-------------|---|---|--|--|--|

| Field                                           | Reserved                      |     |     |     |     |             |   |   |  |  |  |

| RESET                                           | U                             | U   | U   | U   | U   | U U U       |   |   |  |  |  |

| R/W                                             | R/W                           | R/W | R/W | R/W | R/W | R/W R/W R/W |   |   |  |  |  |

| Address                                         | Information Page Memory 0024H |     |     |     |     |             |   |   |  |  |  |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                               |     |     |     |     |             |   |   |  |  |  |

#### Bit Description

#### [7:0] Reserved

These bits are reserved; altering this register may result in incorrect device operation.

# **Zilog Calibration Data**

This section briefly describes the features of the following Flash option bit calibration registers.

ADC Calibration Data: see page 169

Temperature Sensor Calibration Data: see page 171

Watchdog Timer Calibration Data: see page 172

Serialization Data: see page 173

Randomized Lot Identifier: see page 174

| Debug Command           | Command<br>Byte | Enabled when<br>Not in DEBUG<br>Mode? | Disabled by Flash Read Protect<br>Option Bit                                                                                                                              |

|-------------------------|-----------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Write Program Counter   | 06H             | _                                     | Disabled.                                                                                                                                                                 |

| Read Program Counter    | 07H             | -                                     | Disabled.                                                                                                                                                                 |

| Write Register          | 08H             | -                                     | Only writes of the Flash Memory Control<br>registers are allowed. Additionally, only<br>the Mass Erase command is allowed to<br>be written to the Flash Control Register. |

| Read Register           | 09H             | _                                     | Disabled.                                                                                                                                                                 |

| Write Program Memory    | 0AH             | -                                     | Disabled.                                                                                                                                                                 |

| Read Program Memory     | 0BH             | -                                     | Disabled.                                                                                                                                                                 |

| Write Data Memory       | 0CH             | -                                     | Yes.                                                                                                                                                                      |

| Read Data Memory        | 0DH             | _                                     | -                                                                                                                                                                         |

| Read Program Memory CRC | 0EH             | _                                     | -                                                                                                                                                                         |

| Reserved                | 0FH             | -                                     | _                                                                                                                                                                         |

| Step Instruction        | 10H             | _                                     | Disabled.                                                                                                                                                                 |

| Stuff Instruction       | 11H             | _                                     | Disabled.                                                                                                                                                                 |

| Execute Instruction     | 12H             | _                                     | Disabled.                                                                                                                                                                 |

| Reserved                | 13H–FFH         | _                                     | -                                                                                                                                                                         |

#### Table 109. Debug Command Enable/Disable (Continued)

In the list of OCD commands that follows, data and commands sent from the host to the On-Chip Debugger are identified by DBG  $\leftarrow$  Command/Data. Data sent from the On-Chip Debugger back to the host is identified by DBG  $\rightarrow$  Data.

**Read OCD Revision (00H).** The Read OCD Revision command determines the version of the On-Chip Debugger. If OCD commands are added, removed, or changed, this revision number changes.

```

DBG \leftarrow 00H

DBG \rightarrow OCDRev[15:8] (Major revision number)

DBG \rightarrow OCDRev[7:0] (Minor revision number)

```

**Read OCD Status Register (02H).** The Read OCD Status Register command reads the OCDSTAT Register.

DBG  $\leftarrow$  02H DBG  $\rightarrow$  OCDSTAT[7:0]

**Read Runtime Counter (03H).** The Runtime Counter counts system clock cycles in between Breakpoints. The 16-bit Runtime Counter counts up from 0000H and stops at the maximum count of FFFFH. The Runtime Counter is overwritten during the Write Memory,

## **OCD Status Register**

The OCD Status Register reports status information about the current state of the debugger and the system.

#### Table 111. OCD Status Register (OCDSTAT)

| Bit   | 7   | 6    | 5      | 4        | 3 | 2     | 1 | 0 |  |  |

|-------|-----|------|--------|----------|---|-------|---|---|--|--|

| Field | DBG | HALT | FRPENB | Reserved |   |       |   |   |  |  |

| RESET | 0   | 0    | 0      | 0        | 0 | 0 0 0 |   |   |  |  |

| R/W   | R   | R    | R      | R        | R | R     | R | R |  |  |

| Bit           | Description                                                                                                                            |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>DBG    | Debug Status<br>0 = NORMAL Mode.<br>1 = DEBUG Mode.                                                                                    |

| [6]<br>HALT   | HALT Mode<br>0 = Not in HALT Mode.<br>1 = In HALT Mode.                                                                                |

| [5]<br>FRPENB | Flash Read Protect Option Bit Enable<br>0 = FRP bit enabled, that allows disabling of many OCD commands.<br>1 = FRP bit has no effect. |

| [4:0]         | Reserved<br>These bits are reserved and must be programmed to 00000.                                                                   |

# **Oscillator Control**

The Z8 Encore! XP F082A Series devices uses five possible clocking schemes, each user-selectable:

- Internal precision trimmed RC oscillator (IPO)

- On-chip oscillator using off-chip crystal or resonator

- On-chip oscillator using external RC network

- External clock drive

- On-chip low power Watchdog Timer oscillator

- Clock failure detection circuitry

In addition, Z8 Encore! XP F082A Series devices contain clock failure detection and recovery circuitry, allowing continued operation despite a failure of the system clock oscillator.

# Operation

This chapter discusses the logic used to select the system clock and handle primary oscillator failures.

# **System Clock Selection**

The oscillator control block selects from the available clocks. Table 112 details each clock source and its usage.

**Note:** The stabilization time varies depending on the crystal, resonator or feedback network used. See Table 115 for transconductance values to compute oscillator stabilization times.

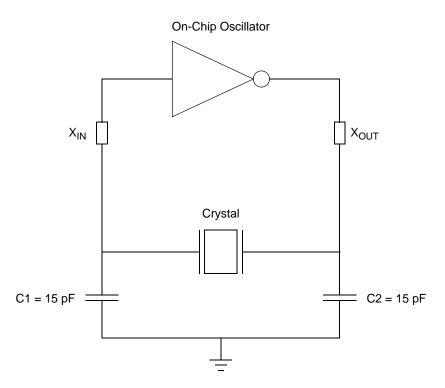

Figure 27 displays a recommended configuration for connection with an external fundamental-mode, parallel-resonant crystal operating at 20MHz. Recommended 20MHz crystal specifications are provided in Table 114. Printed circuit board layouts must add no more than 4pF of stray capacitance to either the  $X_{IN}$  or  $X_{OUT}$  pins. If oscillation does not occur, reduce the values of capacitors C1 and C2 to decrease loading.

Figure 27. Recommended 20 MHz Crystal Oscillator Configuration

# **Internal Precision Oscillator**

The internal precision oscillator (IPO) is designed for use without external components. You can either manually trim the oscillator for a nonstandard frequency or use the automatic factory-trimmed version to achieve a 5.53MHz frequency. IPO features include:

- On-chip RC oscillator that does not require external components

- Output frequency of either 5.53 MHz or 32.8 kHz (contains both a fast and a slow mode)

- Trimmed through Flash option bits with user override

- Elimination of crystals or ceramic resonators in applications where very high timing accuracy is not required

# Operation

An 8-bit trimming register, incorporated into the design, compensates for absolute variation of oscillator frequency. Once trimmed the oscillator frequency is stable and does not require subsequent calibration. Trimming is performed during manufacturing and is not necessary for you to repeat unless a frequency other than 5.53 MHz (fast mode) or 32.8 kHz (slow mode) is required. This trimming is done at +30°C and a supply voltage of 3.3 V, so accuracy of this operating point is optimal.

If not used, the IPO can be disabled by the Oscillator Control Register (see the <u>Oscillator</u> <u>Control Register Definitions section on page 196</u>).

By default, the oscillator frequency is set by the factory trim value stored in the write-protected Flash information page. However, the user code can override these trim values as described in the <u>Trim Bit Address Space</u> section on page 165.

Select one of two frequencies for the oscillator (5.53MHz and 32.8kHz) using the OSC-SEL bits in the the <u>Oscillator Control</u> chapter on page 193.

| Mnemonic | Operands        | Instruction                   |

|----------|-----------------|-------------------------------|

| BRK      | _               | On-Chip Debugger Break        |

| BTJ      | p, bit, src, DA | Bit Test and Jump             |

| BTJNZ    | bit, src, DA    | Bit Test and Jump if Non-Zero |

| BTJZ     | bit, src, DA    | Bit Test and Jump if Zero     |

| CALL     | dst             | Call Procedure                |

| DJNZ     | dst, src, RA    | Decrement and Jump Non-Zero   |

| IRET     | _               | Interrupt Return              |

| JP       | dst             | Jump                          |

| JP cc    | dst             | Jump Conditional              |

| JR       | DA              | Jump Relative                 |

| JR cc    | DA              | Jump Relative Conditional     |

| RET      | _               | Return                        |

| TRAP     | vector          | Software Trap                 |

#### Table 126. Program Control Instructions

#### Table 127. Rotate and Shift Instructions

| MnemonicOperandsInstructionBSWAPdstBit SwapRLdstRotate LeftRLCdstRotate Left through CarryRRdstRotate RightRRCdstRotate Right through CarrySRAdstShift Right Arithmetic |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RLC     dst     Rotate Left through Carry       RR     dst     Rotate Right       RRC     dst     Rotate Right through Carry                                            |

| RR     dst     Rotate Right       RRC     dst     Rotate Right through Cart                                                                                             |

| RRC   dst   Rotate Right through Carr                                                                                                                                   |

|                                                                                                                                                                         |

| SRA dst Shift Right Arithmetic                                                                                                                                          |

|                                                                                                                                                                         |

| SRL dst Shift Right Logical                                                                                                                                             |

| SWAP dst Swap Nibbles                                                                                                                                                   |

221

| Assembly      |                                                                                                                        |     | dress<br>ode | Opcode(s) |   |   | Fla | ags |   |   | Fetch<br>Cycle | Instr.<br>Cycle |

|---------------|------------------------------------------------------------------------------------------------------------------------|-----|--------------|-----------|---|---|-----|-----|---|---|----------------|-----------------|

| Mnemonic      | Symbolic Operation                                                                                                     | dst | src          | (Hex)     | С | Ζ | S   | V   | D | Н | S              | S               |

| TMX dst, src  | dst AND src                                                                                                            | ER  | ER           | 78        | - | * | *   | 0   | - | - | 4              | 3               |

|               |                                                                                                                        | ER  | IM           | 79        |   |   |     |     |   |   | 4              | 3               |

| TRAP Vector   | $SP \leftarrow SP - 2$<br>@SP \leftarrow PC<br>$SP \leftarrow SP - 1$<br>@SP \leftarrow FLAGS<br>PC \leftarrow @Vector |     | Vector       | F2        | _ | - | _   | _   | - | - | 2              | 6               |

| WDT           |                                                                                                                        |     |              | 5F        | _ | _ | _   | _   | _ | _ | 1              | 2               |

| XOR dst, src  | $dst \gets dst \ XOR \ src$                                                                                            | r   | r            | B2        | _ | * | *   | 0   | _ | _ | 2              | 3               |

|               |                                                                                                                        | r   | lr           | B3        | - |   |     |     |   |   | 2              | 4               |

|               |                                                                                                                        | R   | R            | B4        |   |   |     |     |   |   | 3              | 3               |

|               |                                                                                                                        | R   | IR           | B5        | - |   |     |     |   |   | 3              | 4               |

|               |                                                                                                                        | R   | IM           | B6        | - |   |     |     |   |   | 3              | 3               |

|               |                                                                                                                        | IR  | IM           | B7        |   |   |     |     |   |   | 3              | 4               |

| XORX dst, src | $dst \gets dst \ XOR \ src$                                                                                            | ER  | ER           | B8        | _ | * | *   | 0   | _ | _ | 4              | 3               |

|               |                                                                                                                        | ER  | IM           | B9        |   |   |     |     |   |   | 4              | 3               |

#### Table 128. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

– = Unaffected.

X = Undefined.

0 = Reset to 0.

1 =Set to 1.

## **UART** Timing

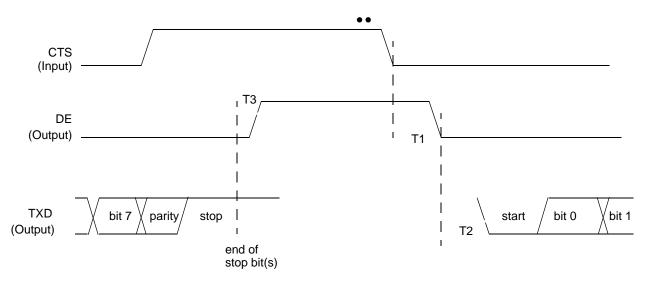

Figure 37 and Table 146 provide timing information for UART pins for the case where CTS is used for flow control. The CTS to DE assertion delay (T1) assumes the Transmit Data Register has been loaded with data prior to CTS assertion.

| Figure 37. U | ART Timing | With CTS |

|--------------|------------|----------|

|--------------|------------|----------|

|                |                                                    | Delay (ns)                 |                                            |  |  |  |

|----------------|----------------------------------------------------|----------------------------|--------------------------------------------|--|--|--|

| Parameter      | Abbreviation                                       | Minimum                    | Maximum                                    |  |  |  |

| UART           |                                                    |                            |                                            |  |  |  |

| T <sub>1</sub> | CTS Fall to DE output delay                        | 2 * X <sub>IN</sub> period | 2 * X <sub>IN</sub> period +<br>1 bit time |  |  |  |

| T <sub>2</sub> | DE assertion to TXD falling edge (start bit) delay | ± 5                        |                                            |  |  |  |

| T <sub>3</sub> | End of Stop Bit(s) to DE deassertion delay         | ±                          | : 5                                        |  |  |  |

| Table 14 |         | T Timin | a With  | CTS |

|----------|---------|---------|---------|-----|

|          | 10. UAR |         | ig with | 613 |