Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                       |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 6                                                            |

| Program Memory Size        | 2KB (2K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 64 x 8                                                       |

| RAM Size                   | 512 x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 4x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 105°C (TA)                                           |

| Mounting Type              | Through Hole                                                 |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                       |

| Supplier Device Package    | · · · · · · · · · · · · · · · · · · ·                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f022apb020eg    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Program Memory Address (Hex)                                        | Function                     |  |  |  |  |

|---------------------------------------------------------------------|------------------------------|--|--|--|--|

| 0002–0003                                                           | Reset Vector                 |  |  |  |  |

| 0004–0005                                                           | WDT Interrupt Vector         |  |  |  |  |

| 0006–0007                                                           | Illegal Instruction Trap     |  |  |  |  |

| 0008–0037                                                           | Interrupt Vectors*           |  |  |  |  |

| 0038–0039                                                           | Reserved                     |  |  |  |  |

| 003A-003D                                                           | Oscillator Fail Trap Vectors |  |  |  |  |

| 003E-03FF                                                           | Program Memory               |  |  |  |  |

| Note: *See Table 32 on page 56 for a list of the interrupt vectors. |                              |  |  |  |  |

| Table 5. Z8 Encore! XP F082A Series P | Program Memory Maps (Continued) |

|---------------------------------------|---------------------------------|

|---------------------------------------|---------------------------------|

# **Data Memory**

The Z8 Encore! XP F082A Series does not use the eZ8 CPU's 64 KB Data Memory address space.

# **Flash Information Area**

Table 6 describes the Z8 Encore! XP F082A Series Flash Information Area. This 128B Information Area is accessed by setting bit 7 of the Flash Page Select Register to 1. When access is enabled, the Flash Information Area is mapped into the Program Memory and overlays the 128 bytes at addresses FE00H to FF7FH. When the Information Area access is enabled, all reads from these Program Memory addresses return the Information Area data rather than the Program Memory data. Access to the Flash Information Area is read-only.

Table 6. Z8 Encore! XP F082A Series Flash Memory Information Area Map

| Program Memory |                                                                                           |

|----------------|-------------------------------------------------------------------------------------------|

| Address (Hex)  | Function                                                                                  |

| FE00–FE3F      | Zilog Option Bits/Calibration Data                                                        |

| FE40-FE53      | Part Number<br>20-character ASCII alphanumeric code<br>Left-justified and filled with FFH |

| FE54–FE5F      | Reserved                                                                                  |

| FE60–FE7F      | Zilog Calibration Data                                                                    |

| FE80–FFFF      | Reserved                                                                                  |

| Port                  | Pin | Mnemonic   | Alternate Function Description          | Alternate Function<br>Set Register AFS1 |

|-----------------------|-----|------------|-----------------------------------------|-----------------------------------------|

| Port A <sup>1,2</sup> | PA0 | T0IN/T0OUT | Timer 0 Input/Timer 0 Output Complement | N/A                                     |

|                       |     | Reserved   |                                         | -                                       |

|                       | PA1 | TOOUT      | Timer 0 Output                          | -                                       |

|                       |     | Reserved   |                                         | -                                       |

|                       | PA2 | DE0        | UART 0 Driver Enable                    | -                                       |

|                       |     | Reserved   |                                         | -                                       |

|                       | PA3 | CTS0       | UART 0 Clear to Send                    | -                                       |

|                       |     | Reserved   |                                         | -                                       |

|                       | PA4 | RXD0/IRRX0 | UART 0/IrDA 0 Receive Data              | -                                       |

|                       |     | Reserved   |                                         | -                                       |

|                       | PA5 | TXD0/IRTX0 | UART 0/IrDA 0 Transmit Data             | -                                       |

|                       |     | Reserved   |                                         | -                                       |

|                       | PA6 | T1IN/T1OUT | Timer 1 Input/Timer 1 Output Complement | -                                       |

|                       |     | Reserved   |                                         | -                                       |

|                       | PA7 | T1OUT      | Timer 1 Output                          | -                                       |

|                       |     | Reserved   |                                         | -                                       |

### Table 15. Port Alternate Function Mapping (Non 8-Pin Parts)

Notes:

- Because there is only a single alternate function for each Port A pin, the Alternate Function Set registers are not implemented for Port A. Enabling alternate function selections automatically enables the associated alternate function. See the <u>Port A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

- 2. Whether PA0/PA6 takes on the timer input or timer output complement function depends on the timer configuration. See the <u>Timer Pin Signal Operation</u> section on page 84 for details.

- Because there are at most two choices of alternate function for any pin of Port B, the Alternate Function Set Register AFS2 is not used to select the function. Alternate function selection must also be enabled. See the <u>Port</u> <u>A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

- 4. V<sub>REF</sub> is available on PB5 in 28-pin products and on PC2 in 20-pin parts.

- Because there are at most two choices of alternate function for any pin of Port C, the Alternate Function Set Register AFS2 is not used to select the function. Alternate function selection must also be enabled. See the Port <u>A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

- Because there is only a single alternate function for the Port PD0 pin, the Alternate Function Set registers are not implemented for Port D. Enabling alternate function selections automatically enables the associated alternate function. See the <u>Port A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

| Bit     | 7                                                                                     | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|---------------------------------------------------------------------------------------|------|------|------|------|------|------|------|

| Field   | POC7                                                                                  | POC6 | POC5 | POC4 | POC3 | POC2 | POC1 | POC0 |

| RESET   | 00H (Ports A-C); 01H (Port D)                                                         |      |      |      |      |      |      |      |

| R/W     | R/W                                                                                   | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| Address | If 03H in Port A–D Address Register, accessible through the Port A–D Control Register |      |      |      |      |      |      |      |

| D:4     | Decertation                                                                           |      |      |      |      |      |      |      |

### Table 23. Port A–D Output Control Subregisters (PxOC)

| Bit   | Description                                                                                                                |

|-------|----------------------------------------------------------------------------------------------------------------------------|

| [7:0] | Port Output Control                                                                                                        |

| POCx  | These bits function independently of the alternate function bit and always disable the drains if set to 1.                 |

|       | 0 = The source current is enabled for any output mode unless overridden by the alternate func-<br>tion (push-pull output). |

|       | 1 = The source current for the associated pin is disabled (open-drain mode).                                               |

### Port A–D High Drive Enable Subregisters

The Port A–D High Drive Enable Subregister, shown in Table 24, is accessed through the port A–D Control Register by writing 04H to the Port A–D Address Register. Setting the bits in the Port A–D High Drive Enable subregisters to 1 configures the specified port pins for high current output drive operation. The Port A–D High Drive Enable subregister affects the pins directly and, as a result, alternate functions are also affected.

| Bit     | 7                                                                                     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|---------|---------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|

| Field   | PHDE7                                                                                 | PHDE6 | PHDE5 | PHDE4 | PHDE3 | PHDE2 | PHDE1 | PHDE0 |

| RESET   | 0                                                                                     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| R/W     | R/W                                                                                   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

| Address | If 04H in Port A–D Address Register, accessible through the Port A–D Control Register |       |       |       |       |       |       |       |

Table 24. Port A–D High Drive Enable Subregisters (PxHDE)

| Bit                                                        | Description                                                       |  |  |  |  |

|------------------------------------------------------------|-------------------------------------------------------------------|--|--|--|--|

| [7:0]                                                      | Port High Drive Enabled                                           |  |  |  |  |

| PHDEx                                                      | 0 = The port pin is configured for standard output current drive. |  |  |  |  |

|                                                            | 1 = The port pin is configured for high output current drive.     |  |  |  |  |

| Note: x indicates the specific GPIO port pin number (7–0). |                                                                   |  |  |  |  |

|          | Program        |                                                                                                                        |

|----------|----------------|------------------------------------------------------------------------------------------------------------------------|

|          | Memory         |                                                                                                                        |

| Priority | Vector Address |                                                                                                                        |

| Highest  | 0002H          | Reset (not an interrupt)                                                                                               |

|          | 0004H          | Watchdog Timer (see Watchdog Timer)                                                                                    |

|          | 003AH          | Primary Oscillator Fail Trap (not an interrupt)                                                                        |

|          | 003CH          | Watchdog Oscillator Fail Trap (not an interrupt)                                                                       |

|          | 0006H          | Illegal Instruction Trap (not an interrupt)                                                                            |

| _        | 0008H          | Reserved                                                                                                               |

|          | 000AH          | Timer 1                                                                                                                |

|          | 000CH          | Timer 0                                                                                                                |

|          | 000EH          | UART 0 receiver                                                                                                        |

|          | 0010H          | UART 0 transmitter                                                                                                     |

|          | 0012H          | Reserved                                                                                                               |

|          | 0014H          | Reserved                                                                                                               |

|          | 0016H          | ADC                                                                                                                    |

|          | 0018H          | Port A Pin 7, selectable rising or falling input edge or LVD (see Reset, Stop Mode Recovery and Low Voltage Detection) |

|          | 001AH          | Port A Pin 6, selectable rising or falling input edge or Comparator Output                                             |

|          | 001CH          | Port A Pin 5, selectable rising or falling input edge                                                                  |

|          | 001EH          | Port A Pin 4, selectable rising or falling input edge                                                                  |

|          | 0020H          | Port A Pin 3, selectable rising or falling input edge                                                                  |

|          | 0022H          | Port A Pin 2, selectable rising or falling input edge                                                                  |

|          | 0024H          | Port A Pin 1, selectable rising or falling input edge                                                                  |

|          | 0026H          | Port A Pin 0, selectable rising or falling input edge                                                                  |

|          | 0028H          | Reserved                                                                                                               |

|          | 002AH          | Reserved                                                                                                               |

|          | 002CH          | Reserved                                                                                                               |

|          | 002EH          | Reserved                                                                                                               |

|          | 0030H          | Port C Pin 3, both input edges                                                                                         |

|          | 0032H          | Port C Pin 2, both input edges                                                                                         |

|          | 0034H          | Port C Pin 1, both input edges                                                                                         |

| Lowest   | 0036H          | Port C Pin 0, both input edges                                                                                         |

|          | 0038H          | Reserved                                                                                                               |

|          |                |                                                                                                                        |

### Table 34. Trap and Interrupt Vectors in Order of Priority

| Bit     | 7       | 6       | 5      | 4      | 3             | 2      | 1      | 0      |  |

|---------|---------|---------|--------|--------|---------------|--------|--------|--------|--|

| Field   | PA7VENH | PA6CENH | PA5ENH | PA4ENH | <b>PA3ENH</b> | PA2ENH | PA1ENH | PA0ENH |  |

| RESET   | 0       | 0       | 0      | 0      | 0             | 0      | 0      | 0      |  |

| R/W     | R/W     | R/W     | R/W    | R/W    | R/W           | R/W    | R/W    | R/W    |  |

| Address |         | FC4H    |        |        |               |        |        |        |  |

| Bit             | Description                                                   |

|-----------------|---------------------------------------------------------------|

| [7]<br>PA7VENH  | Port A Bit[7] or LVD Interrupt Request Enable High Bit        |

| [6]<br>PA6CENH  | Port A Bit[7] or Comparator Interrupt Request Enable High Bit |

| [5:0]<br>PAxENH | Port A Bit[ <i>x</i> ] Interrupt Request Enable High Bit      |

See the <u>Shared Interrupt Select Register (IRQSS) Register</u> on page 68 for selection of either the LVD or the comparator as the interrupt source.

| Bit     | 7       | 6       | 5      | 4      | 3             | 2      | 1      | 0      |

|---------|---------|---------|--------|--------|---------------|--------|--------|--------|

| Field   | PA7VENL | PA6CENL | PA5ENL | PA4ENL | <b>PA3ENL</b> | PA2ENL | PA1ENL | PA0ENL |

| RESET   | 0       | 0       | 0      | 0      | 0             | 0      | 0      | 0      |

| R/W     | R/W     | R/W     | R/W    | R/W    | R/W           | R/W    | R/W    | R/W    |

| Address |         | FC5H    |        |        |               |        |        |        |

| Bit             | Description                                                  |

|-----------------|--------------------------------------------------------------|

| [7]<br>PA7VENL  | Port A Bit[7] or LVD Interrupt Request Enable Low Bit        |

| [6]<br>PA6CENL  | Port A Bit[6] or Comparator Interrupt Request Enable Low Bit |

| [5:0]<br>PAxENL | Port A Bit[x] Interrupt Request Enable Low Bit               |

## **IRQ2 Enable High and Low Bit Registers**

Table 44 describes the priority control for IRQ2. The IRQ2 Enable High and Low Bit registers, shown in Tables 44 and 45, form a priority-encoded enabling for interrupts in the Interrupt Request 2 Register.

66

| IRQ2ENH[ <i>x</i> ] | IRQ2ENL[x] | Priority | Description |

|---------------------|------------|----------|-------------|

| 0                   | 0          | Disabled | Disabled    |

| 0                   | 1          | Level 1  | Low         |

| 1                   | 0          | Level 2  | Medium      |

| 1                   | 1          | Level 3  | High        |

### Table 44. IRQ2 Enable and Priority Encoding

### Table 45. IRQ2 Enable High Bit Register (IRQ2ENH)

| Bit     | 7        | 6    | 5   | 4   | 3     | 2     | 1     | 0     |  |

|---------|----------|------|-----|-----|-------|-------|-------|-------|--|

| Field   | Reserved |      |     |     | C3ENH | C2ENH | C1ENH | C0ENH |  |

| RESET   | 0        | 0    | 0   | 0   | 0     | 0     | 0     | 0     |  |

| R/W     | R/W      | R/W  | R/W | R/W | R/W   | R/W   | R/W   | R/W   |  |

| Address |          | FC7H |     |     |       |       |       |       |  |

| Bit          | Description                                                                |

|--------------|----------------------------------------------------------------------------|

| [7:4]        | <b>Reserved</b><br>These bits are reserved and must be programmed to 0000. |

| [3]<br>C3ENH | Port C3 Interrupt Request Enable High Bit                                  |

| [2]<br>C2ENH | Port C2 Interrupt Request Enable High Bit                                  |

| [1]<br>C1ENH | Port C1 Interrupt Request Enable High Bit                                  |

| [0]<br>C0ENH | Port C0 Interrupt Request Enable High Bit                                  |

The timer input can be used as a selectable counting source. It shares the same pin as the complementary timer output. When selected by the GPIO Alternate Function registers, this pin functions as a timer input in all modes except for the DUAL PWM OUTPUT mode. For this mode, there is no timer input available.

# **Timer Control Register Definitions**

This section defines the features of the following Timer Control registers.

<u>Timer 0–1 Control Registers</u>: see page 85

<u>Timer 0–1 High and Low Byte Registers</u>: see page 89

Timer Reload High and Low Byte Registers: see page 91

Timer 0-1 PWM High and Low Byte Registers: see page 92

# Timer 0–1 Control Registers

The Timer Control registers are 8-bit read/write registers that control the operation of their associated counter/timers.

### Time 0–1 Control Register 0

The Timer Control Register 0 (TxCTL0) and Timer Control Register 1 (TxCTL1), shown in Table 50, determine the timer operating mode. These registers each include a programmable PWM deadband delay, two bits to configure timer interrupt definition and a status bit to identify if the most recent timer interrupt is caused by an input capture event.

| Bit            | 7                       | 6           | 5    | 4        | 3   | 2    | 1   | 0      |  |

|----------------|-------------------------|-------------|------|----------|-----|------|-----|--------|--|

| Field          | TMODEHI                 | TICO        | NFIG | Reserved |     | PWMD |     | INPCAP |  |

| RESET          | 0                       | 0           | 0    | 0        | 0   | 0    | 0   | 0      |  |

| R/W            | R/W                     | R/W         | R/W  | R/W      | R/W | R/W  | R/W | R      |  |

| Address        |                         | F06H, F0EH  |      |          |     |      |     |        |  |

| Bit            | Descript                | Description |      |          |     |      |     |        |  |

| [7]<br>TMODEHI | [7] Timer Mode High Bit |             |      |          |     |      |     |        |  |

Table 50. Timer 0–1 Control Register 0 (TxCTL0)

| Bit                  | 7   | 6 | 5 | 4  | 3  | 2 | 1 | 0 |

|----------------------|-----|---|---|----|----|---|---|---|

| Field                | TXD |   |   |    |    |   |   |   |

| RESET                | Х   | Х | Х | Х  | Х  | Х | Х | Х |

| R/W                  | W   | W | W | W  | W  | W | W | W |

| Address              | 1   |   |   | F4 | OH | I | I |   |

| Note: X = Undefined. |     |   |   |    |    |   |   |   |

### Table 67. UART Transmit Data Register (U0TXD)

| Bit   | Description                                                        |

|-------|--------------------------------------------------------------------|

| [7:0] | Transmit Data                                                      |

| TXD   | UART transmitter data byte to be shifted out through the TXDx pin. |

## **UART Receive Data Register**

Data bytes received through the RXDx pin are stored in the UART Receive Data (UxRXD) Register, shown in Table 68. The read-only UART Receive Data Register shares a Register File address with the Write-only UART Transmit Data Register.

| Table 68 | . UART | Receive | Data | Register | (U0RXD) |

|----------|--------|---------|------|----------|---------|

|----------|--------|---------|------|----------|---------|

| Bit                  | 7          | 6 | 5 | 4  | 3  | 2 | 1 | 0 |  |

|----------------------|------------|---|---|----|----|---|---|---|--|

| Field                | RXD        |   |   |    |    |   |   |   |  |

| RESET                | Х          | Х | Х | Х  | Х  | Х | Х | Х |  |

| R/W                  | R          | R | R | R  | R  | R | R | R |  |

| Address              |            |   |   | F4 | 0H |   |   |   |  |

| Note: X = Undefined. |            |   |   |    |    |   |   |   |  |

| Bit                  | Descriptio | n |   |    |    |   |   |   |  |

| Dit   | Description                                |

|-------|--------------------------------------------|

| [7:0] | Receive Data                               |

| RXD   | UART receiver data byte from the RXDx pin. |

## **UART Address Compare Register**

The UART Address Compare (UxADDR) Register stores the multi-node network address of the UART (see Table 69). When the MPMD[1] bit of UART Control Register 0 is set, all incoming address bytes are compared to the value stored in the Address Compare Register. Receive interrupts and RDA assertions only occur in the event of a match.

# **ADC Control Register 0**

The ADC Control Register 0 (ADCCTL0) selects the analog input channel and initiates the analog-to-digital conversion. It also selects the voltage reference configuration.

| <b>,</b> ,          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                        |                                            |                                              |              |                           |        |     |  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|----------------------------------------------|--------------|---------------------------|--------|-----|--|

| Bit                 | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6                                                                                                                                                                                                                                                                                                                                                                                      | 5                                          | 4                                            | 3            | 2                         | 1      | 0   |  |

| Field               | CEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | REFSELL                                                                                                                                                                                                                                                                                                                                                                                | REFOUT                                     | CONT                                         |              | ANAI                      | N[3:0] |     |  |

| RESET               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0                                                                                                                                                                                                                                                                                                                                                                                      | 0                                          | 0                                            | 0            | 0                         | 0      | 0   |  |

| R/W                 | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W                                                                                                                                                                                                                                                                                                                                                                                    | R/W                                        | R/W                                          | R/W          | R/W                       | R/W    | R/W |  |

| Address             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                        |                                            | F7                                           | 0H           |                           |        |     |  |

| Bit                 | Descrip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | tion                                                                                                                                                                                                                                                                                                                                                                                   |                                            |                                              |              |                           |        |     |  |

| [7]<br>CEN          | 0 = Conv<br>this I<br>1 = Begi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <ul> <li>Conversion Enable</li> <li>0 = Conversion is complete. Writing a 0 produces no effect. The ADC automatically clears this bit to 0 when a conversion is complete.</li> <li>1 = Begin conversion. Writing a 1 to this bit starts a conversion. If a conversion is already in progress, the conversion restarts. This bit remains 1 until the conversion is complete.</li> </ul> |                                            |                                              |              |                           |        |     |  |

| [6]<br>REFSELL      | <ul> <li>Voltage Reference Level Select Low Bit</li> <li>In conjunction with the High bit (REFSELH) in ADC Control/Status Register 1, this determines the level of the internal voltage reference; the following details the effects of {REF-SELH, REFSELL}; note that this reference is independent of the Comparator reference.</li> <li>00 = Internal Reference Disabled, reference comes from external pin.</li> <li>01 = Internal Reference set to 1.0 V.</li> <li>10 = Internal Reference set to 2.0 V (default).</li> <li>11 = Reserved.</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                        |                                            |                                              |              |                           |        |     |  |

| [5]<br>REFOUT       | 0 = Refe<br>1 = The i<br><b>Caution</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Reference<br>rence buffer<br>internal ADC<br>: When the<br>OUT bit mus                                                                                                                                                                                                                                                                                                                 | is disabled;<br>reference i<br>ADC is used | Vref pin is a<br>s buffered a<br>with an ext | nd driven ou | ut to the V <sub>RE</sub> | F pin. |     |  |

| [4]<br>CONT         | <ul> <li>Conversion</li> <li>0 = Single-shot conversion. ADC data is output once at completion of the 5129 system clock cycles (measurements of the internal temperature sensor take twice as long).</li> <li>1 = Continuous conversion. ADC data updated every 256 system clock cycles after an initial 5129 clock conversion (measurements of the internal temperature sensor take twice as</li> </ul>                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                        |                                            |                                              |              |                           |        |     |  |

| [3:0]<br>ANAIN[3:0] | long).<br>Analog Input Select<br>These bits select the analog input for conversion. Not all Port pins in this list are available in<br>all packages for the Z8 Encore! XP F082A Series. For information about port pins available<br>with each package style, see the <u>Pin Description</u> chapter on page 8. Do not enable unavail-<br>able analog inputs. Usage of these bits changes depending on the buffer mode selected in<br>ADC Control/Status Register 1.                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                        |                                            |                                              |              |                           |        |     |  |

Table 73. ADC Control Register 0 (ADCCTL0)

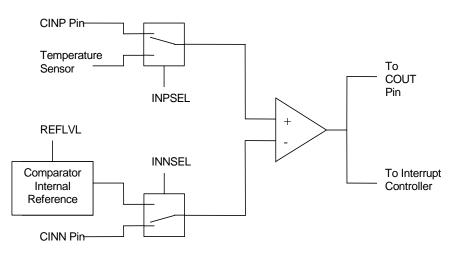

# **Comparator**

The Z8 Encore! XP F082A Series devices feature a general purpose comparator that compares two analog input signals. These analog signals may be external stimulus from a pin (CINP and/or CINN) or internally generated signals. Both a programmable voltage reference and the temperature sensor output voltage are available internally. The output is available as an interrupt source or can be routed to an external pin.

Figure 20. Comparator Block Diagram

# Operation

When the positive comparator input exceeds the negative input by more than the specified hysteresis, the output is a logic High. When the negative input exceeds the positive by more than the hysteresis, the output is a logic Low. Otherwise, the comparator output retains its present value. See <u>Table 141</u> on page 238 for details.

The comparator may be powered down to reduce supply current. See the <u>Power Control</u> <u>Register 0</u> section on page 33 for details.

**Caution:** Because of the propagation delay of the comparator, Zilog does not recommend enabling or reconfiguring the comparator without first disabling the interrupts and waiting for the comparator output to settle. Doing so can result in spurious interrupts.

The following code example illustrates how to safely enable the comparator:

```

di

ld cmp0, r0 ; load some new configuration

nop

nop         ; wait for output to settle

clr irq0 ; clear any spurious interrupts pending

ei

```

# **Comparator Control Register Definition**

The Comparator Control Register (CMP0) configures the comparator inputs and sets the value of the internal voltage reference.

| Bit     | 7      | 6      | 5   | 4   | 3                                       | 2   | 1   | 0   |

|---------|--------|--------|-----|-----|-----------------------------------------|-----|-----|-----|

| Field   | INPSEL | INNSEL |     | REF | Reserved (20-/28-pin)<br>REFLVL (8-pin) |     |     |     |

| RESET   | 0      | 0      | 0   | 1   | 0                                       | 1   | 0   | 0   |

| R/W     | R/W    | R/W    | R/W | R/W | R/W                                     | R/W | R/W | R/W |

| Address | F90H   |        |     |     |                                         |     |     |     |

Table 77. Comparator Control Register (CMP0)

| Bit    | Description                                                                                                                                                            |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]    | Signal Select for Positive Input                                                                                                                                       |

| INPSEL | 0 = GPIO pin used as positive comparator input.                                                                                                                        |

|        | <ol> <li>Temperature sensor used as positive comparator input.</li> </ol>                                                                                              |

| [6]    | Signal Select for Negative Input                                                                                                                                       |

| INNSEL | <ul> <li>0 = Internal reference disabled, GPIO pin used as negative comparator input.</li> <li>1 = Internal reference enabled as negative comparator input.</li> </ul> |

| Bit   | Description (Continued)                                                                        |

|-------|------------------------------------------------------------------------------------------------|

| [1:0] | For 8-pin devices, the following voltages can be configured; for 20- and 28-pin devices, these |

|       | bits are reserved.                                                                             |

|       | 000000 = 0.00 V                                                                                |

|       | 000001 = 0.05 V                                                                                |

|       | 000010 = 0.10 V                                                                                |

|       | 000011 = 0.15 V                                                                                |

|       | 000100 = 0.20 V                                                                                |

|       | 000101 = 0.25 V                                                                                |

|       | 000110 = 0.30 V                                                                                |

|       | 000111 = 0.35 V                                                                                |

|       | 001000 = 0.40  V                                                                               |

|       | 001001 = 0.45 V                                                                                |

|       | 001010 = 0.50  V                                                                               |

|       | 001011 = 0.55 V                                                                                |

|       | 001100 = 0.60  V                                                                               |

|       | 001101 = 0.65 V                                                                                |

|       | 001110 = 0.70 V                                                                                |

|       | 001111 = 0.75 V                                                                                |

|       | 010000 = 0.80  V                                                                               |

|       | 010001 = 0.85  V                                                                               |

|       | 010010 = 0.90  V                                                                               |

|       | 010011 = 0.95  V                                                                               |

|       | 010100 = 1.00  V (Default)                                                                     |

|       | 010101 = 1.05  V                                                                               |

|       | 010110 = 1.10 V<br>010111 = 1.15 V                                                             |

|       | 01000 = 1.20  V                                                                                |

|       | 011000 = 1.25  V<br>011001 = 1.25  V                                                           |

|       | 011010 = 1.30  V                                                                               |

|       | 011011 = 1.35 V                                                                                |

|       | 011100 = 1.40  V                                                                               |

|       | 011101 = 1.45 V                                                                                |

|       | 011110 = 1.50 V                                                                                |

|       | 011111 = 1.55 V                                                                                |

|       | 100000 = 1.60  V                                                                               |

|       | 100001 = 1.65  V                                                                               |

|       | 100010 = 1.70  V                                                                               |

|       | 100011 = 1.75 V                                                                                |

|       | 100100 = 1.80  V                                                                               |

# **Temperature Sensor**

The on-chip Temperature Sensor allows you to measure temperature on the die with either the on-board ADC or on-board comparator. This block is factory calibrated for in-circuit software correction. Uncalibrated accuracy is significantly worse, therefore the temperature sensor is not recommended for uncalibrated use.

# **Temperature Sensor Operation**

The on-chip temperature sensor is a Proportional to Absolute Temperature (PTAT) topology. A pair of Flash option bytes contain the calibration data. The temperature sensor can be disabled by a bit in the <u>Power Control Register 0</u> section on page 33 to reduce power consumption.

The temperature sensor can be directly read by the ADC to determine the absolute value of its output. The temperature sensor output is also available as an input to the comparator for threshold type measurement determination. The accuracy of the sensor when used with the comparator is substantially less than when measured by the ADC.

If the temperature sensor is routed to the ADC, the ADC must be configured in unity-gain buffered mode (for details, see the <u>Input Buffer Stage</u> section on page 133). The value read back from the ADC is a signed number, although it is always positive.

The sensor is factory-trimmed through the ADC using the external 2.0 V reference. Unless the sensor is retrimmed for use with a different reference, it is most accurate when used with the external 2.0 V reference.

Because this sensor is an on-chip sensor, Zilog recommends that the user account for the difference between ambient and die temperature when inferring ambient temperature conditions.

During normal operation, the die undergoes heating that causes a mismatch between the ambient temperature and that measured by the sensor. For best results, the Z8 Encore! XP device must be placed into STOP Mode for sufficient time such that the die and ambient temperatures converge (this time is dependent on the thermal design of the system). The temperature sensor measurement must then be made immediately after recovery from STOP Mode.

The following equation defines the transfer function between the temperature sensor output voltage and the die temperature. This is needed for comparator threshold measurements.

$V = 0.01 \times T + 0.65$

**Caution:** The Flash Frequency High and Low Byte registers must be loaded with the correct value to ensure proper operation of the device. Also, Flash programming and erasure is not supported for system clock frequencies below 20kHz or above 20MHz.

| Table 84. | . Flash Frequency | v High Byte | Register ( | (FFREQH) |

|-----------|-------------------|-------------|------------|----------|

|           |                   |             |            |          |

| Bit     | 7   | 6      | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|---------|-----|--------|-----|-----|-----|-----|-----|-----|--|--|

| Field   |     | FFREQH |     |     |     |     |     |     |  |  |

| RESET   | 0   | 0      | 0   | 0   | 0   | 0   | 0   | 0   |  |  |

| R/W     | R/W | R/W    | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Address |     | FFAH   |     |     |     |     |     |     |  |  |

| Bit    | Description                                    |

|--------|------------------------------------------------|

| [7:0]  | Flash Frequency High Byte                      |

| FFREQH | High byte of the 16-bit Flash Frequency value. |

### Table 85. Flash Frequency Low Byte Register (FFREQL)

| Bit     | 7 | 6      | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |

|---------|---|--------|---|----|----|---|---|---|--|--|--|

| Field   |   | FFREQL |   |    |    |   |   |   |  |  |  |

| RESET   |   |        |   | (  | )  |   |   |   |  |  |  |

| R/W     |   | R/W    |   |    |    |   |   |   |  |  |  |

| Address |   |        |   | FF | BH |   |   |   |  |  |  |

| Bit    | Description                                   |

|--------|-----------------------------------------------|

| [7:0]  | Flash Frequency Low Byte                      |

| FFREQL | Low byte of the 16-bit Flash Frequency value. |

## **Temperature Sensor Calibration Data**

### Table 98. Temperature Sensor Calibration High Byte at 003A (TSCALH)

| Bit       | 7                                               | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|-----------|-------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|--|--|

| Field     | TSCALH                                          |     |     |     |     |     |     |     |  |  |

| RESET     | U                                               | U   | U   | U   | U   | U   | U   | U   |  |  |

| R/W       | R/W                                             | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Address   | Information Page Memory 003A                    |     |     |     |     |     |     |     |  |  |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |     |     |     |     |     |     |     |  |  |

#### Bit Description [7:0] **Temperature Sensor Calibration High Byte** TSCALH The TSCALH and TSCALL bytes combine to form the 12-bit temperature sensor offset calibra-

tion value. For more details, see Temperature Sensor Operation on page 139.

### Table 99. Temperature Sensor Calibration Low Byte at 003B (TSCALL)

| Bit       | 7                                               | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|-----------|-------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|--|--|

| Field     | TSCALL                                          |     |     |     |     |     |     |     |  |  |

| RESET     | U                                               | U   | U   | U   | U   | U   | U   | U   |  |  |

| R/W       | R/W                                             | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Address   | ss Information Page Memory 003B                 |     |     |     |     |     |     |     |  |  |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |     |     |     |     |     |     |     |  |  |

#### Bit Description

| [7:0]  | Temperature Sensor Calibration Low Byte                                                   |

|--------|-------------------------------------------------------------------------------------------|

| TSCALL | The TSCALH and TSCALL bytes combine to form the 12-bit temperature sensor offset calibra- |

|        | tion value. For usage details, see the Temperature Sensor Operation section on page 144.  |

# Watchdog Timer Calibration Data

### Table 100. Watchdog Calibration High Byte at 007EH (WDTCALH)

| Bit       | 7                             | 6           | 5             | 4  | 3 | 2 | 1 | 0 |  |  |

|-----------|-------------------------------|-------------|---------------|----|---|---|---|---|--|--|

| Field     | WDTCALH                       |             |               |    |   |   |   |   |  |  |

| RESET     | U                             |             |               |    |   |   |   |   |  |  |

| R/W       | R/W R/W R/W R/W R/W R/W R/W   |             |               |    |   |   |   |   |  |  |

| Address   | Information Page Memory 007EH |             |               |    |   |   |   |   |  |  |

| Note: U = | Unchanged h                   | w Reset R/M | / = Read/Writ | e. |   |   |   |   |  |  |

Note: U = Unchanged by Reset. R/W = Read/Write.

### Bit Description

[7:0] Watchdog Timer Calibration High Byte

WDTCALH

The WDTCALH and WDTCALL bytes, when loaded into the Watchdog Timer reload registers result in a one second time-out at room temperature and 3.3V supply voltage. To use the Watchdog Timer calibration, user code must load WDTU with 0x00, WDTH with WDT-CALH and WDTL with WDTCALL.

|                   |                                                                                  | T <sub>A</sub> = - | –40°C to +′          |         |       |                                                                                      |

|-------------------|----------------------------------------------------------------------------------|--------------------|----------------------|---------|-------|--------------------------------------------------------------------------------------|

| Symbol            | Parameter                                                                        | Minimum            | Typical <sup>1</sup> | Maximum | Units | Conditions                                                                           |

| T <sub>RAMP</sub> | Time for $V_{DD}$ to transition from $V_{SS}$ to $V_{POR}$ to ensure valid Reset | 0.10               | -                    | 100     | ms    |                                                                                      |

| T <sub>SMP</sub>  | Stop Mode Recovery pin pulse rejection period                                    |                    | 20                   |         | ns    | For any SMR<br>pin or for the<br>Reset pin<br>when it is<br>asserted in<br>STOP Mode |

### Table 135. Power-On Reset and Voltage Brown-Out Electrical Characteristics and Timing

| Table 136. Flash Memory Ele | ctrical Characteristics and Timing |

|-----------------------------|------------------------------------|

|-----------------------------|------------------------------------|

|                                               | $T_A = -$ | = 2.7 V to<br>-40°C to +<br>otherwise | 105°C   |        |                                                                                                                                                                   |  |  |

|-----------------------------------------------|-----------|---------------------------------------|---------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Parameter                                     | Minimum   | Typical                               | Maximum | Units  | Notes                                                                                                                                                             |  |  |

| Flash Byte Read Time                          | 100       | _                                     | _       | ns     |                                                                                                                                                                   |  |  |

| Flash Byte Program Time                       | 20        | _                                     | 40      | μs     |                                                                                                                                                                   |  |  |

| Flash Page Erase Time                         | 10        | _                                     | _       | ms     |                                                                                                                                                                   |  |  |

| Flash Mass Erase Time                         | 200       | _                                     | _       | ms     |                                                                                                                                                                   |  |  |

| Writes to Single Address<br>Before Next Erase | -         | -                                     | 2       |        |                                                                                                                                                                   |  |  |

| Flash Row Program Time                        | -         | -                                     | 8       | ms     | Cumulative program time for<br>single row cannot exceed limit<br>before next erase. This<br>parameter is only an issue<br>when bypassing the Flash<br>Controller. |  |  |

| Data Retention                                | 100       | _                                     | _       | years  | 25°C                                                                                                                                                              |  |  |

| Endurance                                     | 10,000    | _                                     | _       | cycles | Program/erase cycles                                                                                                                                              |  |  |

|                     |                          | T <sub>A</sub> = - | = 2.7 V to<br>-40°C to +<br>otherwise | -105°C      |       |                                                                                            |  |

|---------------------|--------------------------|--------------------|---------------------------------------|-------------|-------|--------------------------------------------------------------------------------------------|--|

| Symbol              | Symbol Parameter         |                    | Minimum Typical Maximum               |             | Units | Conditions                                                                                 |  |

| F <sub>WDT</sub>    | WDT Oscillator Frequency |                    | 10                                    |             | kHz   |                                                                                            |  |

| F <sub>WDT</sub>    | WDT Oscillator Error     |                    |                                       | <u>+</u> 50 | %     |                                                                                            |  |

| T <sub>WDTCAL</sub> | WDT Calibrated Time-out  | 0.98               | 1                                     | 1.02        | S     | V <sub>DD</sub> = 3.3V;<br>T <sub>A</sub> = 30°C                                           |  |

|                     |                          | 0.70               | 1                                     | 1.30        | S     | $V_{DD} = 2.7 V \text{ to } 3.6 V$<br>$T_A = 0^{\circ}C \text{ to } 70^{\circ}C$           |  |

|                     |                          | 0.50               | 1                                     | 1.50        | S     | $V_{DD} = 2.7 V \text{ to } 3.6 V$<br>$T_A = -40^{\circ}\text{C to } +105^{\circ}\text{C}$ |  |

### Table 137. Watchdog Timer Electrical Characteristics and Timing

### Table 138. Non-Volatile Data Storage

|                        |         | = 2.7 V to<br>-40°C to + |         |        |                                           |

|------------------------|---------|--------------------------|---------|--------|-------------------------------------------|

| Parameter              | Minimum | Typical                  | Maximum | Units  | Notes                                     |

| NVDS Byte Read Time    | 34      | _                        | 519     | μs     | With system clock at 20MHz                |

| NVDS Byte Program Time | 0.171   | _                        | 39.7    | ms     | With system clock at 20MHz                |

| Data Retention         | 100     | _                        | -       | years  | 25°C                                      |

| Endurance              | 160,000 | _                        | _       | cycles | Cumulative write cycles for entire memory |

| Jaquin<br>Munu<br>Lue<br>Z8 Encore! XP F082A | Lash<br>E<br>Series | W<br>V<br>With 11 | SO<br>N<br>(B Flas | y<br>1/0 Lines | Hit Interrupts | e 16-Bit Timers w/PWM | 6<br>4<br>10-Bit A/D Channels | ici<br>UART with IrDA | comparator | Temperature Sensor | Description         |

|----------------------------------------------|---------------------|-------------------|--------------------|----------------|----------------|-----------------------|-------------------------------|-----------------------|------------|--------------------|---------------------|

| Standard Temperatu                           |                     |                   |                    | -              |                |                       | -                             | •                     |            |                    |                     |

| Z8F012APB020SG                               | 1KB                 | 256 B             | 16 B               | 6              | 14             | 2                     | 4                             | 1                     | 1          | 1                  | PDIP 8-pin package  |

| Z8F012AQB020SG                               | 1KB                 | 256 B             | 16 B               | 6              | 14             | 2                     | 4                             | 1                     | 1          | 1                  | QFN 8-pin package   |

| Z8F012ASB020SG                               | 1KB                 | 256 B             | 16 B               | 6              | 14             | 2                     | 4                             | 1                     | 1          | 1                  | SOIC 8-pin package  |

| Z8F012ASH020SG                               | 1KB                 | 256 B             | 16 B               | 17             | 20             | 2                     | 7                             | 1                     | 1          | 1                  | SOIC 20-pin package |

| Z8F012AHH020SG                               | 1KB                 | 256 B             | 16 B               | 17             | 20             | 2                     | 7                             | 1                     | 1          | 1                  | SSOP 20-pin package |

| Z8F012APH020SG                               | 1KB                 | 256 B             | 16 B               | 17             | 20             | 2                     | 7                             | 1                     | 1          | 1                  | PDIP 20-pin package |

| Z8F012ASJ020SG                               | 1KB                 | 256 B             | 16 B               | 23             | 20             | 2                     | 8                             | 1                     | 1          | 1                  | SOIC 28-pin package |

| Z8F012AHJ020SG                               | 1KB                 | 256 B             | 16 B               | 23             | 20             | 2                     | 8                             | 1                     | 1          | 1                  | SSOP 28-pin package |

| Z8F012APJ020SG                               | 1KB                 | 256 B             | 16 B               | 23             | 20             | 2                     | 8                             | 1                     | 1          | 1                  | PDIP 28-pin package |

| Extended Temperatu                           | re: –40'            | °C to 10          | 5°C                |                |                |                       |                               |                       |            |                    |                     |

| Z8F012APB020EG                               | 1KB                 | 256 B             | 16 B               | 6              | 14             | 2                     | 4                             | 1                     | 1          | 1                  | PDIP 8-pin package  |

| Z8F012AQB020EG                               | 1KB                 | 256 B             | 16 B               | 6              | 14             | 2                     | 4                             | 1                     | 1          | 1                  | QFN 8-pin package   |

| Z8F012ASB020EG                               | 1KB                 | 256 B             | 16 B               | 6              | 14             | 2                     | 4                             | 1                     | 1          | 1                  | SOIC 8-pin package  |

| Z8F012ASH020EG                               | 1KB                 | 256 B             | 16 B               | 17             | 20             | 2                     | 7                             | 1                     | 1          | 1                  | SOIC 20-pin package |

| Z8F012AHH020EG                               | 1KB                 | 256 B             | 16 B               | 17             | 20             | 2                     | 7                             | 1                     | 1          | 1                  | SSOP 20-pin package |

| Z8F012APH020EG                               | 1KB                 | 256 B             | 16 B               | 17             | 20             | 2                     | 7                             | 1                     | 1          | 1                  | PDIP 20-pin package |

| Z8F012ASJ020EG                               | 1KB                 | 256 B             | 16 B               | 23             | 20             | 2                     | 8                             | 1                     | 1          | 1                  | SOIC 28-pin package |

| Z8F012AHJ020EG                               | 1KB                 | 256 B             | 16 B               | 23             | 20             | 2                     | 8                             | 1                     | 1          | 1                  | SSOP 28-pin package |

| Z8F012APJ020EG                               | 1KB                 | 256 B             | 16 B               | 23             | 20             | 2                     | 8                             | 1                     | 1          | 1                  | PDIP 28-pin package |

### Table 148. Z8 Encore! XP F082A Series Ordering Matrix

LD 210 LDC 210 LDCI 209, 210 LDE 210 **LDEI 209** LDX 210 LEA 210 logical 210 **MULT 208 NOP 209** OR 210 **ORX 210 POP 210** POPX 210 program control 211 **PUSH 210** PUSHX 210 RCF 209, 210 **RET 211** RL 211 **RLC 211** rotate and shift 211 RR 211 **RRC 211 SBC 208** SCF 209, 210 SRA 211 SRL 211 **SRP 210 STOP 210 SUB 208 SUBX 208 SWAP 211 TCM 209 TCMX 209** TM 209 TMX 209 **TRAP 211** Watchdog Timer refresh 210 **XOR 210 XORX 210** instructions, eZ8 classes of 207 interrupt control register 69 interrupt controller 55

architecture 55 interrupt assertion types 58 interrupt vectors and priority 58 operation 57 register definitions 60 software interrupt assertion 59 interrupt edge select register 67 interrupt request 0 register 60 interrupt request 1 register 61 interrupt request 2 register 62 interrupt return 211 interrupt vector listing 55 interrupts **UART 108** IR 206 Ir 206 IrDA architecture 120 block diagram 120 control register definitions 123 operation 120 receiving data 122 transmitting data 121 **IRET 211** IRQ0 enable high and low bit registers 62 IRQ1 enable high and low bit registers 64 IRQ2 enable high and low bit registers 65 **IRR 206** Irr 206

# J

JP 211 jump, conditional, relative, and relative conditional 211

# L

LD 210 LDC 210 LDCI 209, 210 LDE 210 LDEI 209, 210 LDX 210 259