Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 17                                                           |

| Program Memory Size        | 2KB (2K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 64 x 8                                                       |

| RAM Size                   | 512 x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 7x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 105°C (TA)                                           |

| Mounting Type              | Through Hole                                                 |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                      |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f022aph020eg    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Reset, Stop Mode Recovery and Low Voltage Detection | 22 |

|-----------------------------------------------------|----|

| Reset Types                                         | 22 |

| Reset Sources                                       | 24 |

| Power-On Reset                                      | 24 |

| Voltage Brown-Out Reset                             | 25 |

| Watchdog Timer Reset                                | 26 |

| External Reset Input                                | 26 |

| External Reset Indicator                            | 27 |

| On-Chip Debugger Initiated Reset                    | 27 |

| Stop Mode Recovery                                  | 27 |

| Stop Mode Recovery Using Watchdog Timer Time-Out    | 28 |

| Stop Mode Recovery Using a GPIO Port Pin Transition | 28 |

| Stop Mode Recovery Using the External RESET Pin     | 29 |

| Low Voltage Detection                               | 29 |

| Reset Register Definitions                          | 29 |

| Low-Power Modes                                     | 32 |

| STOP Mode                                           |    |

| HALT Mode                                           |    |

| Peripheral-Level Power Control                      |    |

| Power Control Register Definitions                  |    |

| -                                                   |    |

| General-Purpose Input/Output                        |    |

| GPIO Port Availability By Device                    |    |

| GPIO Alternate Functions                            |    |

| Direct LED Drive                                    |    |

| Shared Reset Pin                                    |    |

| Shared Debug Pin                                    |    |

| Crystal Oscillator Override                         |    |

| 5V Tolerance                                        |    |

| External Clock Setup                                |    |

| GPIO Interrupts                                     |    |

| GPIO Control Register Definitions                   |    |

| Port A–D Address Registers                          |    |

| Port A–D Control Registers                          |    |

| Port A–D Data Direction Subregisters                |    |

| Port A–D Alternate Function Subregisters            |    |

| Port A–C Input Data Registers                       |    |

| Port A–D Output Data Register                       |    |

| LED Drive Enable Register                           |    |

| LED Drive Enable Register                           |    |

|                                                     | 55 |

### V

| Address (Hex)           | Register Description    | Mnemonic | Reset (Hex) | Page       |  |

|-------------------------|-------------------------|----------|-------------|------------|--|

| F85                     | Reserved                | —        | XX          |            |  |

| <b>Oscillator Contr</b> | ol                      |          |             |            |  |

| F86                     | Oscillator Control      | OSCCTL   | A0          | <u>196</u> |  |

| F87–F8F                 | Reserved                | _        | XX          |            |  |

| Comparator 0            |                         |          |             |            |  |

| F90                     | Comparator 0 Control    | CMP0     | 14          | <u>141</u> |  |

| F91–FBF                 | Reserved                | _        | XX          |            |  |

| Interrupt Contro        | oller                   |          |             |            |  |

| FC0                     | Interrupt Request 0     | IRQ0     | 00          | <u>60</u>  |  |

| FC1                     | IRQ0 Enable High Bit    | IRQ0ENH  | 00          | <u>63</u>  |  |

| FC2                     | IRQ0 Enable Low Bit     | IRQ0ENL  | 00          | <u>63</u>  |  |

| FC3                     | Interrupt Request 1     | IRQ1     | 00          | <u>61</u>  |  |

| FC4                     | IRQ1 Enable High Bit    | IRQ1ENH  | 00          | <u>65</u>  |  |

| FC5                     | IRQ1 Enable Low Bit     | IRQ1ENL  | 00          | <u>65</u>  |  |

| FC6                     | Interrupt Request 2     | IRQ2     | 00          | <u>62</u>  |  |

| FC7                     | IRQ2 Enable High Bit    | IRQ2ENH  | 00          | <u>66</u>  |  |

| FC8                     | IRQ2 Enable Low Bit     | IRQ2ENL  | 00          | <u>67</u>  |  |

| FC9–FCC                 | Reserved                | —        | XX          |            |  |

| FCD                     | Interrupt Edge Select   | IRQES    | 00          | <u>68</u>  |  |

| FCE                     | Shared Interrupt Select | IRQSS    | 00          | <u>68</u>  |  |

| FCF                     | Interrupt Control       | IRQCTL   | 00          | <u>69</u>  |  |

| GPIO Port A             |                         |          |             |            |  |

| FD0                     | Port A Address          | PAADDR   | 00          | <u>44</u>  |  |

| FD1                     | Port A Control          | PACTL    | 00          | <u>46</u>  |  |

| FD2                     | Port A Input Data       | PAIN     | XX          | <u>46</u>  |  |

| FD3                     | Port A Output Data      | PAOUT    | 00          | <u>46</u>  |  |

| GPIO Port B             |                         |          |             |            |  |

| FD4                     | Port B Address          | PBADDR   | 00          | <u>44</u>  |  |

| FD5                     | Port B Control          | PBCTL    | 00          | <u>46</u>  |  |

| FD6                     | Port B Input Data       | PBIN     | XX          | <u>46</u>  |  |

| FD7                     | Port B Output Data      | PBOUT    | 00          | <u>46</u>  |  |

| GPIO Port C             |                         |          |             |            |  |

| FD8                     | Port C Address          | PCADDR   | 00          | 44         |  |

### Table 7. Register File Address Map (Continued)

1. XX = Undefined.

2. Refer to the eZ8 CPU Core User Manual (UM0128).

| Port                | Pin | Mnemonic                           | Alternate Function Description            | Alternate Function<br>Set Register AFS1 |

|---------------------|-----|------------------------------------|-------------------------------------------|-----------------------------------------|

| Port C <sup>5</sup> | PC0 | Reserved                           |                                           | AFS1[0]: 0                              |

|                     |     | ANA4/CINP                          | ADC or Comparator Input                   | AFS1[0]: 1                              |

|                     | PC1 | Reserved                           |                                           | AFS1[1]: 0                              |

|                     |     | ANA5/CINN                          | ADC or Comparator Input                   | AFS1[1]: 1                              |

|                     | PC2 | Reserved                           |                                           | AFS1[2]: 0                              |

|                     |     | ANA6/V <sub>REF</sub> <sup>4</sup> | ADC Analog Input or ADC Voltage Reference | AFS1[2]: 1                              |

|                     | PC3 | COUT                               | Comparator Output                         | AFS1[3]: 0                              |

|                     |     | Reserved                           |                                           | AFS1[3]: 1                              |

|                     | PC4 | Reserved                           |                                           | AFS1[4]: 0                              |

|                     |     |                                    |                                           | AFS1[4]: 1                              |

|                     | PC5 | Reserved                           |                                           | AFS1[5]: 0                              |

|                     |     |                                    |                                           | AFS1[5]: 1                              |

|                     | PC6 | Reserved                           |                                           | AFS1[6]: 0                              |

|                     |     |                                    |                                           | AFS1[6]: 1                              |

|                     | PC7 | Reserved                           |                                           | AFS1[7]: 0                              |

|                     |     |                                    |                                           | AFS1[7]: 1                              |

| Port D <sup>6</sup> | PD0 | RESET                              | External Reset                            | N/A                                     |

### Table 15. Port Alternate Function Mapping (Non 8-Pin Parts) (Continued)

Notes:

2. Whether PA0/PA6 takes on the timer input or timer output complement function depends on the timer configuration. See the <u>Timer Pin Signal Operation</u> section on page 84 for details.

Because there are at most two choices of alternate function for any pin of Port B, the Alternate Function Set Register AFS2 is not used to select the function. Alternate function selection must also be enabled. See the <u>Port</u> <u>A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

4. V<sub>REF</sub> is available on PB5 in 28-pin products and on PC2 in 20-pin parts.

Because there are at most two choices of alternate function for any pin of Port C, the Alternate Function Set Register AFS2 is not used to select the function. Alternate function selection must also be enabled. See the <u>Port</u> <u>A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

6. Because there is only a single alternate function for the Port PD0 pin, the Alternate Function Set registers are not implemented for Port D. Enabling alternate function selections automatically enables the associated alternate function. See the Port A–D Alternate Function Subregisters (PxAF) section on page 47 for details.

Because there is only a single alternate function for each Port A pin, the Alternate Function Set registers are not implemented for Port A. Enabling alternate function selections automatically enables the associated alternate function. See the <u>Port A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

### 49

### Port A–D Stop Mode Recovery Source Enable Subregisters

The Port A–D Stop Mode Recovery Source Enable Subregister, shown in Table 25, is accessed through the Port A–D Control Register by writing 05H to the Port A–D Address Register. Setting the bits in the Port A–D Stop Mode Recovery Source Enable subregisters to 1 configures the specified port pins as a Stop Mode Recovery source. During STOP Mode, any logic transition on a port pin enabled as a Stop Mode Recovery source initiates Stop Mode Recovery.

### Table 25. Port A–D Stop Mode Recovery Source Enable Subregisters (PxSMRE)

| Bit     | 7         | 6                                                                                     | 5      | 4      | 3      | 2      | 1      | 0      |  |  |

|---------|-----------|---------------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--|--|

| Field   | PSMRE7    | PSMRE6                                                                                | PSMRE5 | PSMRE4 | PSMRE3 | PSMRE2 | PSMRE1 | PSMRE0 |  |  |

| RESET   | 0         | 0                                                                                     | 0      | 0      | 0      | 0      | 0      | 0      |  |  |

| R/W     | R/W       | R/W                                                                                   | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |  |  |

| Address | If 05H ir | If 05H in Port A–D Address Register, accessible through the Port A–D Control Register |        |        |        |        |        |        |  |  |

### Bit Description

[7:0] **Port Stop Mode Recovery Source Enabled**

PSMREx 0 = The port pin is not configured as a Stop Mode Recovery source. Transitions on this pin during STOP Mode do not initiate Stop Mode Recovery.

1 = The port pin is configured as a Stop Mode Recovery source. Any logic transition on this pin during STOP Mode initiates Stop Mode Recovery.

Note: x indicates the specific GPIO port pin number (7-0).

| Bit     | 7           | 6                                                                                     | 5        | 4      | 3      | 2      | 1      | 0      |  |

|---------|-------------|---------------------------------------------------------------------------------------|----------|--------|--------|--------|--------|--------|--|

| Field   | PAFS17      | PAFS16                                                                                | PAFS15   | PAFS14 | PAFS13 | PAFS12 | PAFS11 | PAFS10 |  |

| RESET   | 0           | 0                                                                                     | 0        | 0      | 0      | 0      | 0      | 0      |  |

| R/W     | R/W         | R/W                                                                                   | R/W      | R/W    | R/W    | R/W    | R/W    | R/W    |  |

| Address | If 07H in   | If 07H in Port A–D Address Register, accessible through the Port A–D Control Register |          |        |        |        |        |        |  |

| Bit     | Description |                                                                                       |          |        |        |        |        |        |  |

| [7:0]   | •           | ate Functio                                                                           | on Set 1 |        |        |        |        |        |  |

| Table 27. Port A–D Alternate Function Set | 1 Subregisters (PxAFS1) |

|-------------------------------------------|-------------------------|

|                                           |                         |

| Bit   | Description                                                                      |

|-------|----------------------------------------------------------------------------------|

| [7:0] | Port Alternate Function Set 1                                                    |

| PAFSx | 0 = Port Alternate Function selected, as defined in Tables 15 and 16 on page 43. |

|       | 1 = Port Alternate Function selected, as defined in Tables 15 and 16 on page 43. |

Note: x indicates the specific GPIO port pin number (7–0).

### Port A–D Alternate Function Set 2 Subregisters

The Port A–D Alternate Function Set 2 Subregister, shown in Table 28, is accessed through the Port A–D Control Register by writing 08H to the Port A–D Address Register. The Alternate Function Set 2 subregisters selects the alternate function available at a port pin. Alternate Functions selected by setting or clearing bits of this register is defined in Table 16 on page 43.

Note: Alternate function selection on the port pins must also be enabled. See the Port A–D Alternate Function Subregisters section on page 47 for details.

| Bit     | 7         | 6                                                                                     | 5      | 4      | 3      | 2      | 1      | 0      |  |  |  |

|---------|-----------|---------------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--|--|--|

| Field   | PAFS27    | PAFS26                                                                                | PAFS25 | PAFS24 | PAFS23 | PAFS22 | PAFS21 | PAFS20 |  |  |  |

| RESET   |           | 00H (all ports of 20/28 pin devices); 04H (Port A of 8-pin device)                    |        |        |        |        |        |        |  |  |  |

| R/W     | R/W       | R/W                                                                                   | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |  |  |  |

| Address | If 08H ir | If 08H in Port A–D Address Register, accessible through the Port A–D Control Register |        |        |        |        |        |        |  |  |  |

#### Bit Description

#### [7] **Port Alternate Function Set 2**

- PAFS2x 0 = Port Alternate Function selected, as defined in Table 16.

- 1 = Port Alternate Function selected, as defined in Table 16.

Note: x indicates the specific GPIO port pin number (7-0).

51

**Example 1.** A poor coding style that can result in lost interrupt requests:

LDX r0, IRQ0 AND r0, MASK LDX IRQ0, r0

To avoid missing interrupts, use the coding style in Example 2 to clear bits in the Interrupt Request 0 Register:

**Example 2.** A good coding style that avoids lost interrupt requests:

ANDX IRQ0, MASK

### **Software Interrupt Assertion**

Program code can generate interrupts directly. Writing a 1 to the correct bit in the Interrupt Request Register triggers an interrupt (assuming that interrupt is enabled). When the interrupt request is acknowledged by the eZ8 CPU, the bit in the Interrupt Request Register is automatically cleared to 0.

**Caution:** Zilog recommends not using a coding style to generate software interrupts by setting bits in the Interrupt Request registers. All incoming interrupts received between execution of the first LDX command and the final LDX command are lost. See Example 3, which follows.

**Example 3.** A poor coding style that can result in lost interrupt requests:

```

LDX r0, IRQ0

OR r0, MASK

LDX IRQ0, r0

```

To avoid missing interrupts, use the coding style in Example 4 to set bits in the Interrupt Request registers:

**Example 4.** A good coding style that avoids lost interrupt requests:

ORX IRQ0, MASK

### Watchdog Timer Interrupt Assertion

The Watchdog Timer interrupt behavior is different from interrupts generated by other sources. The Watchdog Timer continues to assert an interrupt as long as the time-out condition continues. As it operates on a different (and usually slower) clock domain than the rest of the device, the Watchdog Timer continues to assert this interrupt for many system clocks until the counter rolls over.

enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer Reload.

Observe the following steps for configuring a timer for COUNTER Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer.

- Configure the timer for COUNTER Mode.

- Select either the rising edge or falling edge of the Timer Input signal for the count. This selection also sets the initial logic level (High or Low) for the Timer Output alternate function. However, the Timer Output function is not required to be enabled.

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This only affects the first pass in COUNTER Mode. After the first timer Reload in COUNTER Mode, counting always begins at the reset value of 0001H. In COUNTER Mode the Timer High and Low Byte registers must be written with the value 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 7. Write to the Timer Control Register to enable the timer.

In COUNTER Mode, the number of Timer Input transitions since the timer start is computed via the following equation:

COUNTER Mode Timer Input Transitions = Current Count Value-Start Value

### **COMPARATOR COUNTER Mode**

In COMPARATOR COUNTER Mode, the timer counts input transitions from the analog comparator output. The TPOL bit in the Timer Control Register selects whether the count occurs on the rising edge or the falling edge of the comparator output signal. In COMPAR-ATOR COUNTER Mode, the prescaler is disabled.

| Bit              | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6                       | 5                            | 4           | 3           | 2       | 1         | 0   |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------------|-------------|-------------|---------|-----------|-----|--|--|

| Field            | REFSELH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Reserved                |                              |             |             | В       | UFMODE[2: | 0]  |  |  |

| RESET            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0                       | 0                            | 0           | 0           | 0       | 0         | 0   |  |  |

| R/W              | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W                     | R/W                          | R/W         | R/W         | R/W     | R/W       | R/W |  |  |

| Address          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                         |                              | F7          | 1H          |         | •         |     |  |  |

| Bit              | Dese                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Description             |                              |             |             |         |           |     |  |  |

|                  | <ul> <li>[7] Voltage Reference Level Select High Bit</li> <li>REFSELH In conjunction with the Low bit (REFSELL) in ADC Control Register 0, this determin<br/>the level of the internal voltage reference; the following details the effects of {REFSE<br/>REFSELL}; this reference is independent of the Comparator reference.<br/>00= Internal Reference Disabled, reference comes from external pin.<br/>01= Internal Reference set to 1.0V.<br/>10= Internal Reference set to 2.0V (default).<br/>11= Reserved.</li> </ul> |                         |                              |             |             |         |           |     |  |  |

| [6:3]            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | erved<br>se bits are re | eserved and                  | must be pro | ogrammed to | o 0000. |           |     |  |  |

| [2:0]<br>BUFMODI | E[2:0] 000<br>001<br>010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | •                       | ded, unbuffe<br>ded, buffere | •           | unity gain. |         |           |     |  |  |

### Table 74. ADC Control/Status Register 1 (ADCCTL1)

100 = Differential, unbuffered input.101 = Differential, buffered input with unity gain.

110 = Reserved. 111 = Reserved.

### ADC Data High Byte Register

The ADC Data High Byte (ADCD\_H) Register contains the upper eight bits of the ADC output. The output is an 13-bit two's complement value. During a single-shot conversion, this value is invalid. Access to the ADC Data High Byte Register is read-only. Reading the ADC Data High Byte Register latches data in the ADC Low Bits Register.

| Bit            | 7    | 6     | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|----------------|------|-------|---|---|---|---|---|---|--|--|

| Field          |      | ADCDH |   |   |   |   |   |   |  |  |

| RESET          | Х    | Х     | Х | Х | Х | Х | Х | Х |  |  |

| R/W            | R    | R     | R | R | R | R | R | R |  |  |

| Address        | F72H |       |   |   |   |   |   |   |  |  |

| X = Undefined. |      |       |   |   |   |   |   |   |  |  |

|                |      |       |   |   |   |   |   |   |  |  |

### Table 75. ADC Data High Byte Register (ADCD\_H)

# Bit Description [7:0] ADC Data High Byte ADCDH This byte contains the upper eight bits of the ADC output. These bits are not valid during a single-shot conversion. During a continuous conversion, the most recent conversion output is held in this register. These bits are undefined after a Reset.

### ADC Data Low Byte Register

The ADC Data Low Byte (ADCD\_L) Register contains the lower bits of the ADC output plus an overflow status bit. The output is a 13-bit two's complement value. During a single-shot conversion, this value is invalid. Access to the ADC Data Low Byte Register is read-only. Reading the ADC Data High Byte Register latches data in the ADC Low Bits Register.

| Bit            | 7    | 6 | 5     | 4    | 3   | 2 | 1 | 0 |  |  |  |

|----------------|------|---|-------|------|-----|---|---|---|--|--|--|

| Field          |      |   | ADCDL | Rese | OVF |   |   |   |  |  |  |

| RESET          | Х    | Х | Х     | Х    | Х   | Х | Х |   |  |  |  |

| R/W            | R    | R | R     | R    | R   | R | R | R |  |  |  |

| Address        | F73H |   |       |      |     |   |   |   |  |  |  |

| X = Undefined. |      |   |       |      |     |   |   |   |  |  |  |

Table 76. ADC Data Low Byte Register (ADCD\_L)

| Bit Description                                                           |                                                                             |

|---------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| [7:3] ADC Data Low Bit<br>ADCDL These bits are the<br>undefined after a R | east significant five bits of the 13-bits of the ADC output. These bits are |

In the above equation, T is the temperature in °C; V is the sensor output in volts.

Assuming a compensated ADC measurement, the following equation defines the relationship between the ADC reading and the die temperature:

$T = (25/128) \times (ADC - TSCAL[11:2]) + 30$

In the above equation, T is the temperature in C; ADC is the 10-bit compensated ADC value; and TSCAL is the temperature sensor calibration value, ignoring the two least significant bits of the 12-bit value.

See the <u>Temperature Sensor Calibration Data</u> section on page 171 for the location of TSCAL.

### Calibration

The temperature sensor undergoes calibration during the manufacturing process and is maximally accurate at 30°C. Accuracy decreases as measured temperatures move further from the calibration point.

### Flash Operation Timing Using the Flash Frequency Registers

Before performing either a program or erase operation on Flash memory, you must first configure the Flash Frequency High and Low Byte registers. The Flash Frequency registers allow programming and erasing of the Flash with system clock frequencies ranging from 32kHz (32768Hz) through 20MHz.

The Flash Frequency High and Low Byte registers combine to form a 16-bit value, FFREQ, to control timing for Flash program and erase operations. The 16-bit binary Flash Frequency value must contain the system clock frequency (in kHz). This value is calculated using the following equation:

$FFREQ[15:0] = \frac{System Clock Frequency (Hz)}{1000}$

**Caution:** Flash programming and erasure are not supported for system clock frequencies below 32kHz (32768Hz) or above 20MHz. The Flash Frequency High and Low Byte registers must be loaded with the correct value to ensure operation of the Z8 Encore! XP F082A Series devices.

### Flash Code Protection Against External Access

The user code contained within the Flash memory can be protected against external access by the on-chip debugger. Programming the FRP Flash option bit prevents reading of the user code with the On-Chip Debugger. See the <u>Flash Option Bits</u> chapter on page 159 and the <u>On-Chip Debugger</u> chapter on page 180 for more information.

# Flash Code Protection Against Accidental Program and Erasure

The Z8 Encore! XP F082A Series provides several levels of protection against accidental program and erasure of the Flash memory contents. This protection is provided by a combination of the Flash option bits, the register locking mechanism, the page select redundancy and the sector level protection control of the Flash Controller.

### Flash Code Protection Using the Flash Option Bits

The FRP and FWP Flash option bits combine to provide three levels of Flash Program Memory protection, as shown in Table 79. See the <u>Flash Option Bits</u> chapter on page 159 for more information.

### **Flash Page Select Register**

The Flash Page Select (FPS) Register shares address space with the Flash Sector Protect Register. Unless the Flash controller is unlocked and written with 5EH, writes to this address target the Flash Page Select Register.

The register is used to select one of the available Flash memory pages to be programmed or erased. Each Flash Page contains 512 bytes of Flash memory. During a Page Erase operation, all Flash memory having addresses with the most significant 7 bits given by FPS[6:0] are chosen for program/erase operation.

| Bit     | 7       | 6    | 5                   | 4 | 3 | 2 | 1 | 0 |  |  |  |

|---------|---------|------|---------------------|---|---|---|---|---|--|--|--|

| Field   | INFO_EN |      | PAGE                |   |   |   |   |   |  |  |  |

| RESET   | 0       | 0    | 0                   | 0 | 0 | 0 | 0 |   |  |  |  |

| R/W     | R/W     | R/W  | R/W R/W R/W R/W R/W |   |   |   |   |   |  |  |  |

| Address |         | FF9H |                     |   |   |   |   |   |  |  |  |

### Table 82. Flash Page Select Register (FPS)

### Bit Description

### [7] Information Area Enable

INFO\_EN 0 = Information Area us not selected.

1 = Information Area is selected. The Information Area is mapped into the Program Memory address space at addresses FE00H through FFFFH.

### [6:0] Page Select

PAGE This 7-bit field identifies the Flash memory page for Page Erase and page unlocking. Program Memory Address[15:9] = PAGE[6:0]. For the Z8F08xx devices, the upper 3 bits must be zero. For the Z8F04xx devices, the upper 4 bits must be zero. For Z8F02xx devices, the upper 5 bits must always be 0. For the Z8F01xx devices, the upper 6 bits must always be 0.

If the PA2/RESET pin is held Low while a 32-bit key sequence is issued to the PA0/ DBG pin, the DBG feature is unlocked. After releasing PA2/RESET, it is pulled High. At this point, the PA0/DBG pin may be used to autobaud and cause the device to enter DEBUG Mode. See the <u>OCD Unlock Sequence (8-Pin Devices Only) section on</u> page 185.

### **Exiting DEBUG Mode**

The device exits DEBUG Mode following any of these operations:

- Clearing the DBGMODE bit in the OCD Control Register to 0

- Power-On Reset

- Voltage Brown-Out reset

- Watchdog Timer reset

- Asserting the RESET pin Low to initiate a Reset

- Driving the DBG pin Low while the device is in STOP Mode initiates a System Reset

### OCD Data Format

The OCD interface uses the asynchronous data format defined for RS-232. Each character transmitted and received by the OCD consists of 1 Start bit, 8 data bits (least-significant bit first) and 1 Stop bit as displayed in Figure 26.

| <br>START | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | STOP |

|-----------|----|----|----|----|----|----|----|----|------|

|           |    |    |    |    |    |    |    |    | 1    |

Figure 26. OCD Data Format

**Note:** When responding to a request for data, the OCD may commence transmitting immediately after receiving the stop bit of an incoming frame. Therefore, when sending the stop bit, the host must not actively drive the DBG pin High for more than 0.5 bit times. Zilog recommends that, if possible, the host drives the DBG pin using an open drain output to avoid this issue.

### **OCD Auto-Baud Detector/Generator**

To run over a range of baud rates (data bits per second) with various system clock frequencies, the On-Chip Debugger contains an Auto-Baud Detector/Generator. After a reset, the OCD is idle until it receives data. The OCD requires that the first character sent from the

### **Internal Precision Oscillator**

The internal precision oscillator (IPO) is designed for use without external components. You can either manually trim the oscillator for a nonstandard frequency or use the automatic factory-trimmed version to achieve a 5.53MHz frequency. IPO features include:

- On-chip RC oscillator that does not require external components

- Output frequency of either 5.53 MHz or 32.8 kHz (contains both a fast and a slow mode)

- Trimmed through Flash option bits with user override

- Elimination of crystals or ceramic resonators in applications where very high timing accuracy is not required

### Operation

An 8-bit trimming register, incorporated into the design, compensates for absolute variation of oscillator frequency. Once trimmed the oscillator frequency is stable and does not require subsequent calibration. Trimming is performed during manufacturing and is not necessary for you to repeat unless a frequency other than 5.53 MHz (fast mode) or 32.8 kHz (slow mode) is required. This trimming is done at +30°C and a supply voltage of 3.3 V, so accuracy of this operating point is optimal.

If not used, the IPO can be disabled by the Oscillator Control Register (see the <u>Oscillator</u> <u>Control Register Definitions section on page 196</u>).

By default, the oscillator frequency is set by the factory trim value stored in the write-protected Flash information page. However, the user code can override these trim values as described in the <u>Trim Bit Address Space</u> section on page 165.

Select one of two frequencies for the oscillator (5.53MHz and 32.8kHz) using the OSC-SEL bits in the the <u>Oscillator Control</u> chapter on page 193.

| Mnemonic | Operands    | Instruction                                             |

|----------|-------------|---------------------------------------------------------|

| BCLR     | bit, dst    | Bit Clear                                               |

| BIT      | p, bit, dst | Bit Set or Clear                                        |

| BSET     | bit, dst    | Bit Set                                                 |

| BSWAP    | dst         | Bit Swap                                                |

| CCF      | —           | Complement Carry Flag                                   |

| RCF      | —           | Reset Carry Flag                                        |

| SCF      | —           | Set Carry Flag                                          |

| ТСМ      | dst, src    | Test Complement Under Mask                              |

| ТСМХ     | dst, src    | Test Complement Under Mask using Extended<br>Addressing |

| ТМ       | dst, src    | Test Under Mask                                         |

| ТМХ      | dst, src    | Test Under Mask using Extended Addressing               |

### Table 121. Bit Manipulation Instructions

### Table 122. Block Transfer Instructions

| Mnemonic | Operands | Instruction                                                             |

|----------|----------|-------------------------------------------------------------------------|

| LDCI     | dst, src | Load Constant to/from Program Memory and Auto-<br>Increment Addresses   |

| LDEI     | dst, src | Load External Data to/from Data Memory and Auto-<br>Increment Addresses |

### Table 123. CPU Control Instructions

| Mnemonic | Operands | Instruction           |

|----------|----------|-----------------------|

| ATM      | _        | Atomic Execution      |

| CCF      | —        | Complement Carry Flag |

| DI       | —        | Disable Interrupts    |

| EI       | —        | Enable Interrupts     |

| HALT     | —        | Halt Mode             |

| NOP      | —        | No Operation          |

|               |                                         |      |              | •           |   |   |     | '   |   |   |                |                 |

|---------------|-----------------------------------------|------|--------------|-------------|---|---|-----|-----|---|---|----------------|-----------------|

| Assembly      |                                         |      | lress<br>ode | _ Opcode(s) |   |   | Fla | ags |   |   | Fetch<br>Cycle | Instr.<br>Cycle |

| Mnemonic      | Symbolic Operation                      | dst  | src          | (Hex)       |   | Ζ | S   | V   | D | Н | S              | s               |

| JR dst        | $PC \gets PC + X$                       | DA   |              | 8B          | _ | _ | _   | _   | _ | _ | 2              | 2               |

| JR cc, dst    | if cc is true<br>PC $\leftarrow$ PC + X | DA   |              | 0B-FB       | _ | - | -   | _   | - | _ | 2              | 2               |

| LD dst, rc    | dst $\leftarrow$ src                    | r    | IM           | 0C-FC       | _ | _ | _   | _   | _ | _ | 2              | 2               |

|               |                                         | r    | X(r)         | C7          | - |   |     |     |   |   | 3              | 3               |

|               |                                         | X(r) | r            | D7          | - |   |     |     |   |   | 3              | 4               |

|               |                                         | r    | lr           | E3          | - |   |     |     |   |   | 2              | 3               |

|               |                                         | R    | R            | E4          | - |   |     |     |   |   | 3              | 2               |

|               |                                         | R    | IR           | E5          | - |   |     |     |   |   | 3              | 4               |

|               |                                         | R    | IM           | E6          | _ |   |     |     |   |   | 3              | 2               |

|               |                                         | IR   | IM           | E7          | _ |   |     |     |   |   | 3              | 3               |

|               |                                         | lr   | r            | F3          | _ |   |     |     |   |   | 2              | 3               |

|               |                                         | IR   | R            | F5          | _ |   |     |     |   |   | 3              | 3               |

| LDC dst, src  | dst $\leftarrow$ src                    | r    | Irr          | C2          | _ | _ | _   | _   | _ | _ | 2              | 5               |

|               |                                         | lr   | Irr          | C5          | _ |   |     |     |   |   | 2              | 9               |

|               |                                         | Irr  | r            | D2          | _ |   |     |     |   |   | 2              | 5               |

| LDCI dst, src | dst ← src                               | lr   | Irr          | C3          | _ | _ | _   | _   | _ | _ | 2              | 9               |

|               | r ← r + 1<br>rr ← rr + 1                | Irr  | lr           | D3          | _ |   |     |     |   |   | 2              | 9               |

| LDE dst, src  | dst ← src                               | r    | Irr          | 82          | _ | _ | _   | _   | _ | _ | 2              | 5               |

|               |                                         | Irr  | r            | 92          | - |   |     |     |   |   | 2              | 5               |

| LDEI dst, src | dst $\leftarrow$ src                    | lr   | Irr          | 83          | _ | - | _   | _   | _ | - | 2              | 9               |

|               | r ← r + 1<br>rr ← rr + 1                | Irr  | lr           | 93          | - |   |     |     |   |   | 2              | 9               |

| LDWX dst, src | dst ← src                               | ER   | ER           | 1FE8        | _ | _ | _   | -   | _ | _ | 5              | 4               |

### Table 128. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 =Set to 1.

### **Opcode Maps**

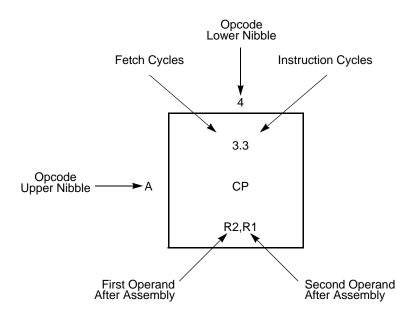

A description of the opcode map data and the abbreviations are provided in Figure 30. Figures 31 and 32 display the eZ8 CPU instructions. Table 129 lists Opcode Map abbreviations.

Figure 30. Opcode Map Cell Description

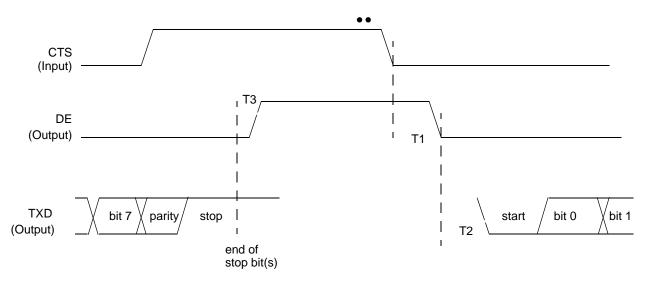

### **UART** Timing

Figure 37 and Table 146 provide timing information for UART pins for the case where CTS is used for flow control. The CTS to DE assertion delay (T1) assumes the Transmit Data Register has been loaded with data prior to CTS assertion.

| Figure 37. | UART | Timing | With C | ٢S |

|------------|------|--------|--------|----|

|------------|------|--------|--------|----|

|                |                                                    | Delay (ns)                 |                                            |  |  |  |

|----------------|----------------------------------------------------|----------------------------|--------------------------------------------|--|--|--|

| Parameter      | Abbreviation                                       | Minimum                    | Maximum                                    |  |  |  |

| UART           |                                                    |                            |                                            |  |  |  |

| T <sub>1</sub> | CTS Fall to DE output delay                        | 2 * X <sub>IN</sub> period | 2 * X <sub>IN</sub> period +<br>1 bit time |  |  |  |

| T <sub>2</sub> | DE assertion to TXD falling edge (start bit) delay | Ŧ                          | - 5                                        |  |  |  |

| T <sub>3</sub> | End of Stop Bit(s) to DE deassertion delay         | ±                          | : 5                                        |  |  |  |

| Table 146. | IIART | Timina | With   | <b>CTS</b> |

|------------|-------|--------|--------|------------|

| Table 140. |       | runng  | VVILII | 613        |

### Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

### Ζ

Z8 Encore! block diagram 3 features 1 part selection guide 2

## **Customer Support**

To share comments, get your technical questions answered, or report issues you may be experiencing with our products, please visit Zilog's Technical Support page at <u>http://support.zilog.com</u>.

To learn more about this product, find additional documentation, or to discover other facets about Zilog product offerings, please visit the Zilog Knowledge Base at <u>http://</u><u>zilog.com/kb</u> or consider participating in the Zilog Forum at <u>http://zilog.com/forum</u>.

This publication is subject to replacement by a later edition. To determine whether a later edition exists, please visit the Zilog website at <u>http://www.zilog.com</u>.