Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 23                                                           |

| Program Memory Size        | 2KB (2K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 64 x 8                                                       |

| RAM Size                   | 512 x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 8x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 105°C (TA)                                           |

| Mounting Type              | Through Hole                                                 |

| Package / Case             | 28-DIP (0.600", 15.24mm)                                     |

| Supplier Device Package    |                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f022apj020eg    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

| Table 89.  | Flash Options Bits at Program Memory Address 0001H 164                   |

|------------|--------------------------------------------------------------------------|

| Table 90.  | Trim Options Bits at Address 0000H 165                                   |

| Table 91.  | Trim Option Bits at 0001H 165                                            |

| Table 92.  | Trim Option Bits at 0002H (TIPO) 166                                     |

| Table 93.  | Trim Option Bits at Address 0003H (TLVD) 166                             |

| Table 94.  | LVD Trim Values                                                          |

| Table 95.  | Trim Option Bits at 0004H 168                                            |

| Table 96.  | ADC Calibration Bits                                                     |

| Table 97.  | ADC Calibration Data Location                                            |

| Table 98.  | Temperature Sensor Calibration High Byte at 003A (TSCALH) 171            |

| Table 99.  | Temperature Sensor Calibration Low Byte at 003B (TSCALL) 171             |

| Table 100. | Watchdog Calibration High Byte at 007EH (WDTCALH) 172                    |

| Table 101. | Serial Number at 001C - 001F (S_NUM) 173                                 |

| Table 102. | Serialization Data Locations                                             |

| Table 103. | Watchdog Calibration Low Byte at 007FH (WDTCALL) 173                     |

| Table 104. | Lot Identification Number (RAND_LOT)                                     |

| Table 105. | Randomized Lot ID Locations                                              |

| Table 106. | Write Status Byte 177                                                    |

| Table 107. | NVDS Read Time                                                           |

| Table 108. | OCD Baud-Rate Limits                                                     |

| Table 109. | Debug Command Enable/Disable 186                                         |

| Table 110. | OCD Control Register (OCDCTL) 191                                        |

| Table 111. | OCD Status Register (OCDSTAT) 192                                        |

| Table 112. | Oscillator Configuration and Selection                                   |

| Table 113. | Oscillator Control Register (OSCCTL)                                     |

| Table 114. | Recommended Crystal Oscillator Specifications                            |

| Table 115. | Transconductance Values for Low, Medium and High Gain Operating<br>Modes |

| Table 116. | Assembly Language Syntax Example 1                                       |

| Table 117. | Assembly Language Syntax Example 2                                       |

| Table 118. | Notational Shorthand                                                     |

# **CPU and Peripheral Overview**

The eZ8 CPU, Zilog's latest 8-bit Central Processing Unit (CPU), meets the continuing demand for faster and more code-efficient microcontrollers. The eZ8 CPU executes a superset of the original Z8 instruction set. The features of eZ8 CPU include:

- Direct register-to-register architecture allows each register to function as an accumulator, improving execution time and decreasing the required program memory

- Software stack allows much greater depth in subroutine calls and interrupts than hardware stacks

- Compatible with existing Z8 code

- Expanded internal Register File allows access of up to 4 KB

- New instructions improve execution efficiency for code developed using higherlevel programming languages, including C

- Pipelined instruction fetch and execution

- New instructions for improved performance including BIT, BSWAP, BTJ, CPC, LDC, LDCI, LEA, MULT and SRL

- New instructions support 12-bit linear addressing of the Register File

- Up to 10 MIPS operation

- C-Compiler friendly

- 2 to 9 clock cycles per instruction

For more information about eZ8 CPU, refer to the <u>eZ8 CPU Core User Manual</u> (<u>UM0128</u>), which is available for download on <u>www.zilog.com</u>.

#### **10-Bit Analog-to-Digital Converter**

The optional analog-to-digital converter (ADC) converts an analog input signal to a 10-bit binary number. The ADC accepts inputs from eight different analog input pins in both single-ended and differential modes. The ADC also features a unity gain buffer when high input impedance is required.

#### **Low-Power Operational Amplifier**

The optional low-power operational amplifier (LPO) is a general-purpose amplifier primarily targeted for current sense applications. The LPO output may be routed internally to the ADC or externally to a pin.

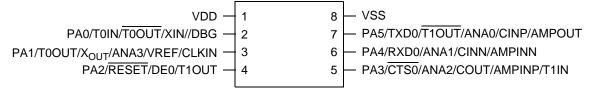

Figure 2. Z8F08xA, Z8F04xA, Z8F02xA and Z8F01xA in 8-Pin SOIC, QFN/MLF-S, or PDIP Package

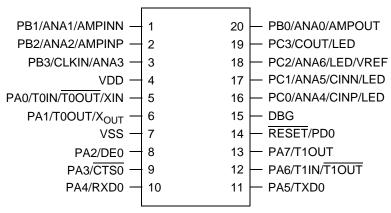

Figure 3. Z8F08xA, Z8F04xA, Z8F02xA and Z8F01xA in 20-Pin SOIC, SSOP or PDIP Package

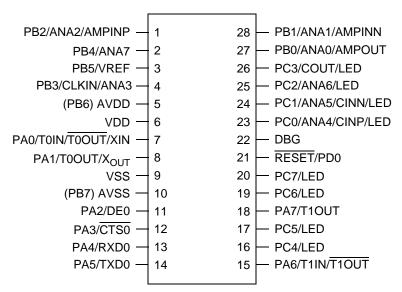

Figure 4. Z8F08xA, Z8F04xA, Z8F02xA and Z8F01xA in 28-Pin SOIC, SSOP or PDIP Package

| FDAFFDBFGPIO Port DFDCFFDDF   | Port C Control<br>Port C Input Data<br>Port C Output Data<br>Port D Address<br>Port D Control | PCCTL<br>PCIN<br>PCOUT<br>PDADDR | 00<br>XX<br>00 | <u>46</u><br><u>46</u><br><u>46</u> |

|-------------------------------|-----------------------------------------------------------------------------------------------|----------------------------------|----------------|-------------------------------------|

| FDBFGPIO Port DFDCFFDDF       | Port C Output Data Port D Address                                                             | PCOUT                            | 00             |                                     |

| GPIO Port D<br>FDC F<br>FDD F | Port D Address                                                                                |                                  |                | <u>46</u>                           |

| FDC F<br>FDD F                |                                                                                               | PDADDR                           |                |                                     |

| FDD F                         |                                                                                               | PDADDR                           |                |                                     |

|                               | Port D Control                                                                                |                                  | 00             | <u>44</u>                           |

| FDE F                         |                                                                                               | PDCTL                            | 00             | <u>46</u>                           |

|                               | Reserved                                                                                      | —                                | XX             |                                     |

| FDF F                         | Port D Output Data                                                                            | PDOUT                            | 00             | <u>46</u>                           |

| FE0-FEF F                     | Reserved                                                                                      | _                                | XX             |                                     |

| Watchdog Timer (              | WDT)                                                                                          |                                  |                |                                     |

| FF0 F                         | Reset Status (Read-only)                                                                      | RSTSTAT                          | X0             | <u>29</u>                           |

| Ī                             | Watchdog Timer Control (Write-only)                                                           | WDTCTL                           | N/A            | <u>96</u>                           |

| FF1 V                         | Watchdog Timer Reload Upper Byte                                                              | WDTU                             | 00             | <u>97</u>                           |

| FF2 V                         | Watchdog Timer Reload High Byte                                                               | WDTH                             | 04             | <u>97</u>                           |

| FF3 V                         | Watchdog Timer Reload Low Byte                                                                | WDTL                             | 00             | <u>98</u>                           |

| FF4–FF5 F                     | Reserved                                                                                      | _                                | XX             |                                     |

| Trim Bit Control              |                                                                                               |                                  |                |                                     |

| FF6 1                         | Trim Bit Address                                                                              | TRMADR                           | 00             | <u>161</u>                          |

| FF7 1                         | Trim Bit Data                                                                                 | TRMDR                            | 00             | <u>162</u>                          |

| Flash Memory Cor              | ntroller                                                                                      |                                  |                |                                     |

| FF8 F                         | Flash Control                                                                                 | FCTL                             | 00             | <u>155</u>                          |

| FF8 F                         | Flash Status                                                                                  | FSTAT                            | 00             | <u>155</u>                          |

| FF9 F                         | Flash Page Select                                                                             | FPS                              | 00             | <u>156</u>                          |

| F                             | Flash Sector Protect                                                                          | FPROT                            | 00             | <u>157</u>                          |

| FFA F                         | Flash Programming Frequency High Byte                                                         | FFREQH                           | 00             | <u>158</u>                          |

| FFB F                         | Flash Programming Frequency Low Byte                                                          | FFREQL                           | 00             | <u>158</u>                          |

| eZ8 CPU                       |                                                                                               |                                  |                |                                     |

| FFC F                         | Flags                                                                                         | _                                | XX             | See                                 |

| FFD F                         | Register Pointer                                                                              | RP                               | XX             | foot-                               |

| FFE S                         | Stack Pointer High Byte                                                                       | SPH                              | XX             | -note 2                             |

| FFF S                         | Stack Pointer Low Byte                                                                        | SPL                              | XX             |                                     |

| Notes:                        |                                                                                               |                                  |                |                                     |

#### Table 7. Register File Address Map (Continued)

1. XX = Undefined.

2. Refer to the <u>eZ8</u> CPU Core User Manual (UM0128).

|                                                       | Reset Characteristics and Latency                      |            |                                                               |  |  |  |

|-------------------------------------------------------|--------------------------------------------------------|------------|---------------------------------------------------------------|--|--|--|

| Reset Type                                            | Control Registers                                      | eZ8<br>CPU | Reset Latency (Delay)                                         |  |  |  |

| System Reset                                          | Reset (as applicable)                                  | Reset      | 66 Internal Precision Oscillator Cycles                       |  |  |  |

| System Reset with Crystal Oscillator Enabled          | Reset (as applicable)                                  | Reset      | 5000 Internal Precision Oscillator Cycles                     |  |  |  |

| Stop Mode Recovery                                    | Unaffected, except<br>WDT_CTL and<br>OSC_CTL registers | Reset      | 66 Internal Precision Oscillator Cycles<br>+ IPO startup time |  |  |  |

| Stop Mode Recovery with<br>Crystal Oscillator Enabled | Unaffected, except<br>WDT_CTL and<br>OSC_CTL registers | Reset      | 5000 Internal Precision Oscillator Cycles                     |  |  |  |

#### Table 8. Reset and Stop Mode Recovery Characteristics and Latency

During a System Reset or Stop Mode Recovery, the Internal Precision Oscillator requires 4  $\mu$ s to start up. Then the Z8 Encore! XP F082A Series device is held in Reset for 66 cycles of the Internal Precision Oscillator. If the crystal oscillator is enabled in the Flash option bits, this reset period is increased to 5000 IPO cycles. When a reset occurs because of a low voltage condition or Power-On Reset (POR), this delay is measured from the time that the supply voltage first exceeds the POR level. If the external pin reset remains asserted at the end of the reset period, the device remains in reset until the pin is deasserted.

At the beginning of Reset, all GPIO pins are configured as inputs with pull-up resistor disabled, except PD0 (or PA2 on 8-pin devices) which is shared with the reset pin. On reset, the PD0 is configured as a bidirectional open-drain reset. The pin is internally driven low during port reset, after which the user code may reconfigure this pin as a general purpose output.

During Reset, the eZ8 CPU and on-chip peripherals are idle; however, the on-chip crystal oscillator and Watchdog Timer oscillator continue to run.

Upon Reset, control registers within the Register File that have a defined Reset value are loaded with their reset values. Other control registers (including the Stack Pointer, Register Pointer and Flags) and general-purpose RAM are undefined following Reset. The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset vector address.

As the control registers are reinitialized by a system reset, the system clock after reset is always the IPO. The software must reconfigure the oscillator control block, such that the correct system clock source is enabled and selected.

| Bit         | 7                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6                                                                                                                                                                                                                           | 5            | 4           | 3           | 2        | 1 | 0   |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------|-------------|----------|---|-----|--|--|

| Field       | POR                                                                                                                                                                                                                                                                                                                                                                                                                                             | STOP                                                                                                                                                                                                                        | WDT          | EXT         |             | Reserved |   | LVD |  |  |

| RESET       | See descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                             | below        | 0           | 0           | 0        | 0 | 0   |  |  |

| R/W         | R                                                                                                                                                                                                                                                                                                                                                                                                                                               | R                                                                                                                                                                                                                           | R            | R           | R           | R        | R | R   |  |  |

| Address     |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                             |              | FF          | ЮH          |          |   |     |  |  |

| Bit         | Descriptio                                                                                                                                                                                                                                                                                                                                                                                                                                      | Description                                                                                                                                                                                                                 |              |             |             |          |   |     |  |  |

| [7]<br>POR  | If this bit is                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>Power-On Reset Indicator</b><br>If this bit is set to 1, a Power-On Reset event occurs. This bit is reset to 0 if a WDT time-out or<br>Stop Mode Recovery occurs. This bit is also reset to 0 when the register is read. |              |             |             |          |   |     |  |  |

| [6]<br>STOP | <b>Stop Mode Recovery Indicator</b><br>If this bit is set to 1, a Stop Mode Recovery occurs. If the STOP and WDT bits are both set to 1, the Stop Mode Recovery occurs because of a WDT time-out. If the STOP bit is 1 and the WDT bit is 0, the Stop Mode Recovery was not caused by a WDT time-out. This bit is reset by a Power-On Reset or a WDT time-out that occurred while not in STOP Mode. Reading this register also resets this bit. |                                                                                                                                                                                                                             |              |             |             |          |   |     |  |  |

| [5]<br>WDT  | Watchdog Timer Time-Out Indicator         If this bit is set to 1, a WDT time-out occurs. A POR resets this pin. A Stop Mode Recovery         from a change in an input pin also resets this bit. Reading this register resets this bit. This read         must occur before clearing the WDT interrupt.                                                                                                                                        |                                                                                                                                                                                                                             |              |             |             |          |   |     |  |  |

| [4]<br>EXT  | <b>External Reset Indicator</b><br>If this bit is set to 1, a Reset initiated by the external RESET pin occurs. A Power-On Reset or<br>a Stop Mode Recovery from a change in an input pin resets this bit. Reading this register<br>resets this bit.                                                                                                                                                                                            |                                                                                                                                                                                                                             |              |             |             |          |   |     |  |  |

| [3:1]       | Reserved<br>These bits                                                                                                                                                                                                                                                                                                                                                                                                                          | are reserved                                                                                                                                                                                                                | d and must b | be programn | ned to 000. |          |   |     |  |  |

| [0]<br>LVD  | <b>Low Voltage Detection Indicator</b><br>If this bit is set to 1 the current state of the supply voltage is below the low voltage detection threshold. This value is not latched but is a real-time indicator of the supply voltage level.                                                                                                                                                                                                     |                                                                                                                                                                                                                             |              |             |             |          |   |     |  |  |

### Table 11. Reset Status Register (RSTSTAT)

operational amplifier (LPO) is OFF. To use the LPO, clear the LPO bit, turning it ON. Clearing this bit might interfere with normal ADC measurements on ANA0 (the LPO output). This bit enables the amplifier even in STOP Mode. If the amplifier is not required in STOP Mode, disable it. Failure to perform this results in STOP Mode currents greater than specified.

**Note:** This register is only reset during a POR sequence. Other system reset events do not affect it.

| Bit         | 7                                                                                                                                                                          | 6                                                    | 5            | 4          | 3    | 2   | 1    | 0        |  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--------------|------------|------|-----|------|----------|--|

| Field       | LPO                                                                                                                                                                        | Rese                                                 | erved        | VBO        | TEMP | ADC | COMP | Reserved |  |

| RESET       | 1                                                                                                                                                                          | 0                                                    | 0            | 0          | 0    | 0   | 0    | 0        |  |

| R/W         | R/W                                                                                                                                                                        | R/W                                                  | R/W          | R/W        | R/W  | R/W | R/W  | R/W      |  |

| Address     | F80H                                                                                                                                                                       |                                                      |              |            |      |     |      |          |  |

| Bit         | Description                                                                                                                                                                |                                                      |              |            |      |     |      |          |  |

| [7]<br>LPO  | <b>Low-Power Operational Amplifier Disable</b><br>0 = LPO is enabled (this applies even in STOP Mode).<br>1 = LPO is disabled.                                             |                                                      |              |            |      |     |      |          |  |

| [6:5]       | <b>Reserved</b><br>These bits are reserved and must be programmed to 00.                                                                                                   |                                                      |              |            |      |     |      |          |  |

| [4]<br>VBO  | Voltage Brown-Out Detector Disable<br>This bit and the VBO_AO Flash option bit must both enable the VBO for the VBO to be active.<br>0 = VBO enabled.<br>1 = VBO disabled. |                                                      |              |            |      |     |      |          |  |

| [3]<br>TEMP | 0 = Temper                                                                                                                                                                 | ature Sensor I<br>ature Senso<br>ature Senso         | r enabled.   |            |      |     |      |          |  |

| [2]<br>ADC  | 0 = Analog-                                                                                                                                                                | <b>Digital Con</b><br>to-Digital Co<br>to-Digital Co | onverter ena | abled.     |      |     |      |          |  |

| [1]<br>COMP | Comparator Disable<br>0 = Comparator is enabled.<br>1 = Comparator is disabled.                                                                                            |                                                      |              |            |      |     |      |          |  |

| [0]         | Reserved<br>This bit is re                                                                                                                                                 | eserved and                                          | must be pr   | ogrammed t | o 0. |     |      |          |  |

#### Table 13. Power Control Register 0 (PWRCTL0)

| Port                | Pin | Mnemonic                      | Alternate Function Description | Alternate Function<br>Set Register AFS1 |

|---------------------|-----|-------------------------------|--------------------------------|-----------------------------------------|

| Port B <sup>3</sup> | PB0 | Reserved                      |                                | AFS1[0]: 0                              |

|                     |     | ANA0/AMPOUT                   | ADC Analog Input/LPO Output    | AFS1[0]: 1                              |

|                     | PB1 | Reserved                      |                                | AFS1[1]: 0                              |

|                     |     | ANA1/AMPINN                   | ADC Analog Input/LPO Input (N) | AFS1[1]: 1                              |

|                     | PB2 | Reserved                      |                                | AFS1[2]: 0                              |

|                     |     | ANA2/AMPINP                   | ADC Analog Input/LPO Input (P) | AFS1[2]: 1                              |

|                     | PB3 | CLKIN                         | External Clock Input           | AFS1[3]: 0                              |

|                     |     | ANA3                          | ADC Analog Input               | AFS1[3]: 1                              |

|                     | PB4 | Reserved                      |                                | AFS1[4]: 0                              |

|                     |     | ANA7                          | ADC Analog Input               | AFS1[4]: 1                              |

|                     | PB5 | Reserved                      |                                | AFS1[5]: 0                              |

|                     |     | V <sub>REF</sub> <sup>4</sup> | ADC Voltage Reference          | AFS1[5]: 1                              |

|                     | PB6 | Reserved                      |                                | AFS1[6]: 0                              |

|                     |     | Reserved                      |                                | AFS1[6]: 1                              |

|                     | PB7 | Reserved                      |                                | AFS1[7]: 0                              |

|                     |     | Reserved                      |                                | AFS1[7]: 1                              |

#### Table 15. Port Alternate Function Mapping (Non 8-Pin Parts) (Continued)

Notes:

- Because there is only a single alternate function for each Port A pin, the Alternate Function Set registers are not implemented for Port A. Enabling alternate function selections automatically enables the associated alternate function. See the <u>Port A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

- 2. Whether PA0/PA6 takes on the timer input or timer output complement function depends on the timer configuration. See the <u>Timer Pin Signal Operation</u> section on page 84 for details.

- Because there are at most two choices of alternate function for any pin of Port B, the Alternate Function Set Register AFS2 is not used to select the function. Alternate function selection must also be enabled. See the <u>Port</u> <u>A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

- 4. V<sub>RFF</sub> is available on PB5 in 28-pin products and on PC2 in 20-pin parts.

- Because there are at most two choices of alternate function for any pin of Port C, the Alternate Function Set Register AFS2 is not used to select the function. Alternate function selection must also be enabled. See the <u>Port</u> <u>A–D Alternate Function Subregisters (PxAF)</u> section on page 47 for details.

- 6. Because there is only a single alternate function for the Port PD0 pin, the Alternate Function Set registers are not implemented for Port D. Enabling alternate function selections automatically enables the associated alternate function. See the Port A–D Alternate Function Subregisters (PxAF) section on page 47 for details.

| Bit          | Description (Continued)                                                                                  |

|--------------|----------------------------------------------------------------------------------------------------------|

| [4]<br>U0RXI | <b>UART 0 Receiver Interrupt Request</b><br>0 = No interrupt request is pending for the UART 0 receiver. |

|              | 1 = An interrupt request from the UART 0 receiver is awaiting service.                                   |

| [3]          | UART 0 Transmitter Interrupt Request                                                                     |

| U0TXI        | 0 = No interrupt request is pending for the UART 0 transmitter.                                          |

|              | 1 = An interrupt request from the UART 0 transmitter is awaiting service.                                |

| [2:1]        | Reserved                                                                                                 |

|              | These bits are reserved and must be programmed to 00.                                                    |

| [0]          | ADC Interrupt Request                                                                                    |

0 = No interrupt request is pending for the analog-to-digital Converter.

1 = An interrupt request from the Analog-to-Digital Converter is awaiting service.

# **Interrupt Request 1 Register**

The Interrupt Request 1 (IRQ1) Register, shown in Table 36, stores interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ1 Register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 1 Register to determine if any interrupt requests are pending.

| Bit     | 7     | 6     | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|-------|-------|------|------|------|------|------|------|

| Field   | PA7VI | PA6CI | PA5I | PA4I | PA3I | PA2I | PA1I | PA0I |

| RESET   | 0     | 0     | 0    | 0    | 0    | 0    | 0    | 0    |

| R/W     | R/W   | R/W   | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| Address |       | FC3H  |      |      |      |      |      |      |

Table 36. Interrupt Request 1 Register (IRQ1)

| Bit           | Description                                                                                                                                                                                          |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>PA7VI  | <b>Port A Pin 7 or LVD Interrupt Request</b><br>0 = No interrupt request is pending for GPIO Port A or LVD.                                                                                          |

|               | 1 = An interrupt request from GPIO Port A or LVD.                                                                                                                                                    |

| [6]<br>PA6CI  | Port A Pin 6 or Comparator Interrupt Request<br>0 = No interrupt request is pending for GPIO Port A or Comparator.<br>1 = An interrupt request from GPIO Port A or Comparator.                       |

| [5:0]<br>PA5I | <ul> <li>Port A Pin x Interrupt Request</li> <li>0 = No interrupt request is pending for GPIO Port A pin x.</li> <li>1 = An interrupt request from GPIO Port A pin x is awaiting service.</li> </ul> |

| Note: x ir    | dicates the specific GPIO port pin number (0–5).                                                                                                                                                     |

ADCI

- Set the prescale value

- If using the Timer Output alternate function, set the initial output level (High or Low)

- 2. Write to the Timer High and Low Byte registers to set the starting count value (usually 0001H). This action only affects the first pass in CONTINUOUS Mode. After the first timer Reload in CONTINUOUS Mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. Enable the timer interrupt (if appropriate) and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin (if using the Timer Output function) for the Timer Output alternate function.

- 6. Write to the Timer Control Register to enable the timer and initiate counting.

In CONTINUOUS Mode, the system clock always provides the timer input. The timer period is computed via the following equation:

CONTINUOUS Mode Time-Out Period (s) =  $\frac{\text{Reload Value } \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, use the ONE-SHOT Mode equation to determine the first time-out period.

#### **COUNTER Mode**

In COUNTER Mode, the timer counts input transitions from a GPIO port pin. The timer input is taken from the GPIO port pin Timer Input alternate function. The TPOL bit in the Timer Control Register selects whether the count occurs on the rising edge or the falling edge of the Timer Input signal. In COUNTER Mode, the prescaler is disabled.

**Caution:** The input frequency of the Timer Input signal must not exceed one-fourth the system clock frequency. Further, the high or low state of the input signal pulse must be no less than twice the system clock period. A shorter pulse may not be captured.

Upon reaching the reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is

The PWM period is represented by the following equation:

$PWM Period (s) = \frac{Reload Value \times Prescale}{System Clock Frequency (Hz)}$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, use the ONE-SHOT Mode equation to determine the first PWM time-out period.

If TPOL is set to 0, the ratio of the PWM output High time to the total period is represented by:

PWM Output High Time Ratio (%) =  $\frac{\text{Reload Value} - \text{PWM Value}}{\text{Reload Value}} \times 100$

If TPOL is set to 1, the ratio of the PWM output High time to the total period is represented by:

PWM Output High Time Ratio (%) =  $\frac{PWM Value}{Reload Value} \times 100$

#### **PWM DUAL OUTPUT Mode**

In PWM DUAL OUTPUT Mode, the timer outputs a Pulse-Width Modulated (PWM) output signal pair (basic PWM signal and its complement) through two GPIO port pins. The timer input is the system clock. The timer first counts up to the 16-bit PWM match value stored in the Timer PWM High and Low Byte registers. When the timer count value matches the PWM value, the Timer Output toggles. The timer continues counting until it reaches the reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

If the TPOL bit in the Timer Control Register is set to 1, the Timer Output signal begins as a High (1) and transitions to a Low (0) when the timer value matches the PWM value. The Timer Output signal returns to a High (1) after the timer reaches the reload value and is reset to 0001H.

If the TPOL bit in the Timer Control Register is set to 0, the Timer Output signal begins as a Low (0) and transitions to a High (1) when the timer value matches the PWM value. The Timer Output signal returns to a Low (0) after the timer reaches the reload value and is reset to 0001H.

The timer also generates a second PWM output signal Timer Output Complement. The Timer Output Complement is the complement of the Timer Output PWM signal. A programmable deadband delay can be configured to time delay (0 to 128 system clock cycles) PWM output transitions on these two pins from a low to a high (inactive to active). This

| Table 67. UART Transmit Data Register (U0TXD) |  |

|-----------------------------------------------|--|

| Bit                  | 7    | 6 | 5 | 4  | 3  | 2 | 1 | 0 |  |

|----------------------|------|---|---|----|----|---|---|---|--|

| Field                |      |   |   | Tک | (D |   |   |   |  |

| RESET                | Х    | Х | Х | Х  | Х  | Х | Х | Х |  |

| R/W                  | W    | W | W | W  | W  | W | W | W |  |

| Address              | F40H |   |   |    |    |   |   |   |  |

| Note: X = Undefined. |      |   |   |    |    |   |   |   |  |

| Bit   | Description                                                        |

|-------|--------------------------------------------------------------------|

| [7:0] | Transmit Data                                                      |

| TXD   | UART transmitter data byte to be shifted out through the TXDx pin. |

# **UART Receive Data Register**

Data bytes received through the RXDx pin are stored in the UART Receive Data (UxRXD) Register, shown in Table 68. The read-only UART Receive Data Register shares a Register File address with the Write-only UART Transmit Data Register.

| Table 68. UART Receive | Data Register | (U0RXD) |

|------------------------|---------------|---------|

|------------------------|---------------|---------|

| Bit       | 7                    | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------|----------------------|---|---|---|---|---|---|---|

| Field     | RXD                  |   |   |   |   |   |   |   |

| RESET     | Х                    | Х | Х | Х | Х | Х | Х | Х |

| R/W       | R                    | R | R | R | R | R | R | R |

| Address   | F40H                 |   |   |   |   |   |   |   |

| Note: X = | Note: X = Undefined. |   |   |   |   |   |   |   |

| Bit       | Descriptio           | n |   |   |   |   |   |   |

| [7:0] | Receive Data                               |

|-------|--------------------------------------------|

| RXD   | UART receiver data byte from the RXDx pin. |

# **UART Address Compare Register**

The UART Address Compare (UxADDR) Register stores the multi-node network address of the UART (see Table 69). When the MPMD[1] bit of UART Control Register 0 is set, all incoming address bytes are compared to the value stored in the Address Compare Register. Receive interrupts and RDA assertions only occur in the event of a match.

| #3 | #3 | #3 | #3 |

|----|----|----|----|

4. Round the result and discard the least significant two bytes (equivalent to dividing by  $2^{16}$ ).

| #3     | #3     | #3   | #3   |

|--------|--------|------|------|

| _      |        |      |      |

| 0x00   | 0x00   | 0x80 | 0x00 |

| _      |        |      |      |

|        |        |      |      |

| #4 MSB | #4 LSB |      |      |

5. Determine the sign of the gain correction factor using the sign bits from <u>Step 2</u>. If the offset-corrected ADC value *and* the gain correction word both have the same sign, then the factor is positive and remains unchanged. If they have differing signs, then the factor is negative and must be multiplied by -1.

| #5 MSB | #5 LSB |

|--------|--------|

|--------|--------|

6. Add the gain correction factor to the original offset corrected value.

| #5 MSB | #5 LSB |

|--------|--------|

|        |        |

| +      |        |

| #1 MSB | #1 LSB |

|        |        |

| =      |        |

| #6 MSB | #6 LSB |

| L      |        |

7. Shift the result to the right, using the sign bit determined in <u>Step 1</u>, to allow for the detection of computational overflow.

| $S \rightarrow \#6 MSB \#6 LSB$ |

|---------------------------------|

|---------------------------------|

132

**Caution:** The byte at each address of the Flash memory cannot be programmed (any bits written to 0) more than twice before an erase cycle occurs. Doing so may result in corrupted data at the target byte.

## **Page Erase**

The Flash memory can be erased one page (512 bytes) at a time. Page Erasing the Flash memory sets all bytes in that page to the value FFH. The Flash Page Select Register identifies the page to be erased. Only a page residing in an unprotected sector can be erased. With the Flash Controller unlocked and the active page set, writing the value 95h to the Flash Control Register initiates the Page Erase operation. While the Flash Controller executes the Page Erase operation, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. The eZ8 CPU resumes operation after the Page Erase operation completes. If the Page Erase operation is performed using the On-Chip Debugger, poll the Flash Status Register to determine when the Page Erase operation is complete. When the Page Erase is complete, the Flash Controller returns to its locked state.

#### **Mass Erase**

The Flash memory can also be Mass Erased using the Flash Controller, but only by using the On-Chip Debugger. Mass Erasing the Flash memory sets all bytes to the value FFH. With the Flash Controller unlocked and the Mass Erase successfully enabled, writing the value 63H to the Flash Control Register initiates the Mass Erase operation. While the Flash Controller executes the Mass Erase operation, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. Using the On-Chip Debugger, poll the Flash Status Register to determine when the Mass Erase operation is complete. When the Mass Erase is complete, the Flash Controller returns to its locked state.

# **Flash Controller Bypass**

The Flash Controller can be bypassed and the control signals for the Flash memory brought out to the GPIO pins. Bypassing the Flash Controller allows faster Row Programming algorithms by controlling the Flash programming signals directly.

Row programming is recommended for gang programming applications and large volume customers who do not require in-circuit initial programming of the Flash memory. Page Erase operations are also supported when the Flash Controller is bypassed.

For more information about bypassing the Flash Controller, refer to the <u>Third-Party Flash</u> <u>Programming Support for Z8 Encore! MCUs Application Note (AN0117)</u>, which is available for download on <u>www.zilog.com</u>. Debugger. Writing an invalid value or an invalid sequence returns the Flash Controller to its locked state. The Write-only Flash Control Register shares its Register File address with the read-only Flash Status Register.

# Flash Program Memory Address 0001H

#### Table 89. Flash Options Bits at Program Memory Address 0001H

| Bit     | 7        | 6                    | 5   | 4      | 3        | 2   | 1   | 0   |

|---------|----------|----------------------|-----|--------|----------|-----|-----|-----|

| Field   | Reserved |                      |     | XTLDIS | Reserved |     |     |     |

| RESET   | U        | U                    | U   | U      | U        | U   | U   | U   |

| R/W     | R/W      | R/W                  | R/W | R/W    | R/W      | R/W | R/W | R/W |

| Address |          | Program Memory 0001H |     |        |          |     |     |     |

Note: U = Unchanged by Reset. R/W = Read/Write.

| Bit    | Description                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| [7:5]  | Reserved                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|        | These bits are reserved and must be programmed to 111.                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| [4]    | State of the Crystal Oscillator at Reset                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| XTLDIS | This bit only enables the crystal oscillator. Its selection as a system clock must be performed manually.                                                                                                                                                                                                                                    |  |  |  |  |  |

|        | 0 = Crystal oscillator is enabled during reset, resulting in longer reset timing.                                                                                                                                                                                                                                                            |  |  |  |  |  |

|        | 1 = Crystal oscillator is disabled during reset, resulting in shorter reset timing.                                                                                                                                                                                                                                                          |  |  |  |  |  |

|        | <b>Caution:</b> Programming the XTLDIS bit to zero on 8-pin versions of this device prevents any further communication via the debug pin due to the fact that the XIN and DBG functions are shared on pin 2 of this package. Do not program this bit to zero on 8-pin devices unless further debugging or Flash programming is not required. |  |  |  |  |  |

| [3:0]  | Reserved                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|        | These bits are reserved and must be programmed to 1111.                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

# **Byte Write**

To write a byte to the NVDS array, the user code must first push the address, then the data byte onto the stack. The user code issues a CALL instruction to the address of the byte-write routine (0x10B3). At the return from the sub-routine, the write status byte resides in working register R0. The bit fields of this status byte are defined in Table 106. The contents of the status byte are undefined for write operations to illegal addresses. Also, user code must pop the address and data bytes off the stack.

The write routine uses 13 bytes of stack space in addition to the two bytes of address and data pushed by the user. Sufficient memory must be available for this stack usage.

Because of the Flash memory architecture, NVDS writes exhibit a nonuniform execution time. In general, a write takes  $251 \mu s$  (assuming a 20MHz system clock). Every 400 to 500 writes, however, a maintenance operation is necessary. In this rare occurrence, the write takes up to 61 ms to complete. Slower system clock speeds result in proportionally higher execution times.

NVDS byte writes to invalid addresses (those exceeding the NVDS array size) have no effect. Illegal write operations have a  $2\mu s$  execution time.

| Bit              | 7        | 6 | 5 | 4 | 3    | 2  | 1   | 0   |

|------------------|----------|---|---|---|------|----|-----|-----|

| Field            | Reserved |   |   |   | RCPY | PF | AWE | DWE |

| Default<br>Value | 0        | 0 | 0 | 0 | 0    | 0  | 0   | 0   |

#### Table 106. Write Status Byte

| Bit   | Description                                                                                                 |

|-------|-------------------------------------------------------------------------------------------------------------|

| [7:4] | Reserved<br>These bits are reserved and must be programmed to 0000.                                         |

| [3]   | <b>Recopy Subroutine Executed</b>                                                                           |

| RCPY  | A recopy subroutine was executed. These operations take significantly longer than a normal write operation. |

| [2]   | <b>Power Failure Indicator</b>                                                                              |

| PF    | A power failure or system reset occurred during the most recent attempted write to the NVDS array.          |

| [1]   | Address Write Error                                                                                         |

| AWE   | An address byte failure occurred during the most recent attempted write to the NVDS array.                  |

| [0]   | Data Write Error                                                                                            |

| DWE   | A data byte failure occurred during the most recent attempted write to the NVDS array.                      |

# **Opcode Maps**

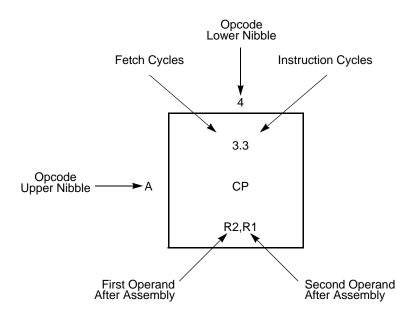

A description of the opcode map data and the abbreviations are provided in Figure 30. Figures 31 and 32 display the eZ8 CPU instructions. Table 129 lists Opcode Map abbreviations.

Figure 30. Opcode Map Cell Description

| Lart Number                                                                                                         | Elash | RAM | SQ N<br>N<br>KB Elas | // I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | UART with IrDA | Comparator | Temperature Sensor | Description         |  |  |

|---------------------------------------------------------------------------------------------------------------------|-------|-----|----------------------|--------------|------------|---------------------|---------------------|----------------|------------|--------------------|---------------------|--|--|

| Z8 Encore! XP F082A Series with 4 KB Flash, 10-Bit Analog-to-Digital Converter<br>Standard Temperature: 0°C to 70°C |       |     |                      |              |            |                     |                     |                |            |                    |                     |  |  |

| Z8F042APB020SG                                                                                                      | 4 KB  | 1KB | ,<br>128 B           | 6            | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |  |  |

| Z8F042AQB020SG                                                                                                      | 4 KB  | 1KB | 128 B                | 6            | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |  |  |

| Z8F042ASB020SG                                                                                                      | 4 KB  | 1KB | 128 B                | 6            | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |  |  |

| Z8F042ASH020SG                                                                                                      | 4 KB  | 1KB | 128 B                | 17           | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |  |  |

| Z8F042AHH020SG                                                                                                      | 4 KB  | 1KB | 128 B                | 17           | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |  |  |

| Z8F042APH020SG                                                                                                      | 4 KB  | 1KB | 128 B                | 17           | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |  |  |

| Z8F042ASJ020SG                                                                                                      | 4 KB  | 1KB | 128 B                | 23           | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |  |  |

| Z8F042AHJ020SG                                                                                                      | 4 KB  | 1KB | 128 B                | 23           | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |  |  |

| Z8F042APJ020SG                                                                                                      | 4 KB  | 1KB | 128 B                | 23           | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |  |  |

| Extended Temperature: –40°C to 105°C                                                                                |       |     |                      |              |            |                     |                     |                |            |                    |                     |  |  |

| Z8F042APB020EG                                                                                                      | 4 KB  | 1KB | 128 B                | 6            | 14         | 2                   | 4                   | 1              | 1          | 1                  | PDIP 8-pin package  |  |  |

| Z8F042AQB020EG                                                                                                      | 4 KB  | 1KB | 128 B                | 6            | 14         | 2                   | 4                   | 1              | 1          | 1                  | QFN 8-pin package   |  |  |

| Z8F042ASB020EG                                                                                                      | 4 KB  | 1KB | 128 B                | 6            | 14         | 2                   | 4                   | 1              | 1          | 1                  | SOIC 8-pin package  |  |  |

| Z8F042ASH020EG                                                                                                      | 4 KB  | 1KB | 128 B                | 17           | 20         | 2                   | 7                   | 1              | 1          | 1                  | SOIC 20-pin package |  |  |

| Z8F042AHH020EG                                                                                                      | 4 KB  | 1KB | 128 B                | 17           | 20         | 2                   | 7                   | 1              | 1          | 1                  | SSOP 20-pin package |  |  |

| Z8F042APH020EG                                                                                                      | 4 KB  | 1KB | 128 B                | 17           | 20         | 2                   | 7                   | 1              | 1          | 1                  | PDIP 20-pin package |  |  |

| Z8F042ASJ020EG                                                                                                      | 4 KB  | 1KB | 128 B                | 23           | 20         | 2                   | 8                   | 1              | 1          | 1                  | SOIC 28-pin package |  |  |

| Z8F042AHJ020EG                                                                                                      | 4 KB  | 1KB | 128 B                | 23           | 20         | 2                   | 8                   | 1              | 1          | 1                  | SSOP 28-pin package |  |  |

| Z8F042APJ020EG                                                                                                      | 4 KB  | 1KB | 128 B                | 23           | 20         | 2                   | 8                   | 1              | 1          | 1                  | PDIP 28-pin package |  |  |

### Table 148. Z8 Encore! XP F082A Series Ordering Matrix

PS022827-1212