#### Zilog - Z8F022AQB020SG Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                       |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 6                                                            |

| Program Memory Size        | 2KB (2K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 64 x 8                                                       |

| RAM Size                   | 512 x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 4x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | 0°C ~ 70°C (TA)                                              |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 8-VDFN Exposed Pad                                           |

| Supplier Device Package    | 8-QFN (5x6)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f022aqb020sg    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| LED Drive Level Low Register 54                          |

|----------------------------------------------------------|

| GPIO Mode Interrupt Controller                           |

| Interrupt Vector Listing                                 |

| Architecture                                             |

| Operation                                                |

| Master Interrupt Enable                                  |

| Interrupt Vectors and Priority 58                        |

| Interrupt Assertion                                      |

| Software Interrupt Assertion 59                          |

| Watchdog Timer Interrupt Assertion 59                    |

| Interrupt Control Register Definitions                   |

| Interrupt Request 0 Register 60                          |

| Interrupt Request 1 Register                             |

| Interrupt Request 2 Register                             |

| IRQ0 Enable High and Low Bit Registers                   |

| IRQ1 Enable High and Low Bit Registers64                 |

| IRQ2 Enable High and Low Bit Registers                   |

| Interrupt Edge Select Register 67                        |

| Shared Interrupt Select Register 68                      |

| Interrupt Control Register 69                            |

| Timers                                                   |

| Architecture                                             |

| Operation                                                |

| Timer Operating Modes                                    |

| Reading the Timer Count Values                           |

| Timer Pin Signal Operation                               |

| Timer Control Register Definitions                       |

| Timer 0–1 Control Registers                              |

| Timer 0–1 High and Low Byte Registers                    |

| Timer Reload High and Low Byte Registers                 |

| Timer 0–1 PWM High and Low Byte Registers                |

| Watchdog Timer                                           |

| Operation                                                |

| Watchdog Timer Refresh                                   |

| Watchdog Timer Time-Out Response                         |

| Watchdog Timer Reload Unlock Sequence                    |

| Watchdog Timer Calibration                               |

| Watchdog Timer Control Register Definitions              |

| Watchdog Timer Control Register                          |

| Watchdog Timer Reload Upper, High and Low Byte Registers |

|                                                          |

### vi

| Table 4. Pin Characteristics (8-Pin Devices) |           |                                                                         |                                       |                    |                                                      |                              |                                                      |                                       |

|----------------------------------------------|-----------|-------------------------------------------------------------------------|---------------------------------------|--------------------|------------------------------------------------------|------------------------------|------------------------------------------------------|---------------------------------------|

| Symbol<br>Mnemonic                           | Direction | Reset<br>Direction                                                      | Active<br>Low<br>or<br>Active<br>High | Tristate<br>Output | Internal<br>Pull-up or<br>Pull-down                  | Schmitt-<br>Trigger<br>Input | Open Drain<br>Output                                 | 5V<br>Tolerance                       |

| PA0/DBG                                      | I/O       | I (but can<br>change<br>during<br>reset if key<br>sequence<br>detected) | N/A                                   | Yes                | Programma-<br>ble<br>Pull-up                         | Yes                          | Yes,<br>Programma-<br>ble                            | Yes,<br>unless<br>pull-ups<br>enabled |

| PA1                                          | I/O       | I                                                                       | N/A                                   | Yes                | Programma-<br>ble<br>Pull-up                         | Yes                          | Yes,<br>Programma-<br>ble                            | Yes,<br>unless<br>pull-ups<br>enabled |

| RESET/<br>PA2                                | I/O       | I/O<br>(defaults<br>to RESET)                                           | Low (in<br>Reset<br>mode)             | Yes                | Programma-<br>ble for PA2;<br>always on for<br>RESET | Yes                          | Programma-<br>ble for PA2;<br>always on for<br>RESET | Yes,<br>unless<br>pull-ups<br>enabled |

| PA[5:3]                                      | I/O       | I                                                                       | N/A                                   | Yes                | Programma-<br>ble<br>Pull-up                         | Yes                          | Yes,<br>Programma-<br>ble                            | Yes,<br>unless<br>pull-ups<br>enabled |

| $V_{DD}$                                     | N/A       | N/A                                                                     | N/A                                   | N/A                | N/A                                                  | N/A                          | N/A                                                  | N/A                                   |

| V <sub>SS</sub>                              | N/A       | N/A                                                                     | N/A                                   | N/A                | N/A                                                  | N/A                          | N/A                                                  | N/A                                   |

### **Port A–D Control Registers**

The Port A–D Control registers set the GPIO port operation. The value in the corresponding Port A–D Address Register determines which subregister is read from or written to by a Port A–D Control Register transaction; see Table 20.

| Bit     | 7                           | 6 | 5 | 4  | 3  | 2 | 1 | 0 |

|---------|-----------------------------|---|---|----|----|---|---|---|

| Field   | PCTL                        |   |   |    |    |   |   |   |

| RESET   |                             |   |   | 00 | )H |   |   |   |

| R/W     | R/W R/W R/W R/W R/W R/W R/W |   |   |    |    |   |   |   |

| Address | FD1H, FD5H, FD9H, FDDH      |   |   |    |    |   |   |   |

#### Table 20. Port A–D Control Registers (PxCTL)

| Bit   | Description                                                                                              |

|-------|----------------------------------------------------------------------------------------------------------|

| [7:0] | Port Control                                                                                             |

| PCTLx | The Port Control Register provides access to all subregisters that configure the GPIO port<br>operation. |

|       |                                                                                                          |

Note: x indicates the specific GPIO port pin number (7–0).

### Port A–D Data Direction Subregisters

The Port A–D Data Direction subregister is accessed through the Port A–D Control Register by writing 01H to the Port A–D Address Register; see Table 21.

| Bit     | 7                                                                                     | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|---------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|

| Field   | DD7                                                                                   | DD6 | DD5 | DD4 | DD3 | DD2 | DD1 | DD0 |

| RESET   | 1                                                                                     | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W     | R/W                                                                                   | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | If 01H in Port A–D Address Register, accessible through the Port A–D Control Register |     |     |     |     |     |     |     |

Table 21. Port A–D Data Direction Subregisters (PxDD)

| Bit   | Description                                                                                                                                                  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0] | Data Direction                                                                                                                                               |

| DDx   | These bits control the direction of the associated port pin. Port Alternate Function operation<br>overrides the Data Direction Register setting.             |

|       | 0 = Output. Data in the Port A–D Output Data Register is driven onto the port pin.                                                                           |

|       | <ul> <li>1 = Input. The port pin is sampled and the value written into the Port A–D Input Data Register.</li> <li>The output driver is tristated.</li> </ul> |

| Note: | x indicates the specific GPIO port pin number (7–0).                                                                                                         |

### Port A–D Alternate Function Subregisters

The Port A–D Alternate Function Subregister, shown in Table 22, is accessed through the Port A–D Control Register by writing 02H to the Port A–D Address Register. The Port A–D Alternate Function subregisters enable the alternate function selection on pins. If disabled, pins functions as GPIO. If enabled, select one of four alternate functions using alternate function set subregisters 1 and 2 as described in the the Port A–D Alternate Functions section on page 37 and the Port A–D Alternate Function Set 2 Subregisters section on page 51. See the <u>GPIO Alternate Functions</u> section on page 37 to determine the alternate function associated with each port pin.

**Caution:** Do not enable alternate functions for GPIO port pins for which there is no associated alternate function. Failure to follow this guideline can result in unpredictable operation.

| Bit     | 7                                                                                     | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|---------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|

| Field   | AF7                                                                                   | AF6 | AF5 | AF4 | AF3 | AF2 | AF1 | AF0 |

| RESET   | 00H (Ports A–C); 01H (Port D); 04H (Port A of 8-pin device)                           |     |     |     |     |     |     |     |

| R/W     | R/W                                                                                   |     |     |     |     |     |     |     |

| Address | If 02H in Port A–D Address Register, accessible through the Port A–D Control Register |     |     |     |     |     |     |     |

| Bit   | Description                                                                                                                                                |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0] | Port Alternate Function Enabled                                                                                                                            |

| AFx   | 0 = The port pin is in normal mode and the DDx bit in the Port A–D Data Direction subregister determines the direction of the pin.                         |

|       | 1 = The alternate function selected through Alternate Function Set subregisters is enabled.<br>Port pin operation is controlled by the alternate function. |

Note: x indicates the specific GPIO port pin number (7-0).

### Port A–D Output Control Subregisters

The Port A–D Output Control Subregister, shown in Table 23, is accessed through the Port A–D Control Register by writing 03H to the Port A–D Address Register. Setting the bits in the Port A–D Output Control subregisters to 1 configures the specified port pins for opendrain operation. These subregisters affect the pins directly and, as a result, alternate functions are also affected.

| Bit     | 7                                                                                     | 6           | 5        | 4      | 3      | 2      | 1      | 0      |

|---------|---------------------------------------------------------------------------------------|-------------|----------|--------|--------|--------|--------|--------|

| Field   | PAFS17                                                                                | PAFS16      | PAFS15   | PAFS14 | PAFS13 | PAFS12 | PAFS11 | PAFS10 |

| RESET   | 0                                                                                     | 0           | 0        | 0      | 0      | 0      | 0      | 0      |

| R/W     | R/W                                                                                   | R/W         | R/W      | R/W    | R/W    | R/W    | R/W    | R/W    |

| Address | If 07H in Port A–D Address Register, accessible through the Port A–D Control Register |             |          |        |        |        |        |        |

| Bit     | Description                                                                           |             |          |        |        |        |        |        |

| [7:0]   | •                                                                                     | ate Functio | on Set 1 |        |        |        |        |        |

| Table 27. Port A–D Alternate Function Set | 1 Subregisters (PxAFS1) |

|-------------------------------------------|-------------------------|

|                                           |                         |

| Bit   | Description                                                                      |

|-------|----------------------------------------------------------------------------------|

| [7:0] | Port Alternate Function Set 1                                                    |

| PAFSx | 0 = Port Alternate Function selected, as defined in Tables 15 and 16 on page 43. |

|       | 1 = Port Alternate Function selected, as defined in Tables 15 and 16 on page 43. |

Note: x indicates the specific GPIO port pin number (7–0).

### Port A–D Alternate Function Set 2 Subregisters

The Port A–D Alternate Function Set 2 Subregister, shown in Table 28, is accessed through the Port A–D Control Register by writing 08H to the Port A–D Address Register. The Alternate Function Set 2 subregisters selects the alternate function available at a port pin. Alternate Functions selected by setting or clearing bits of this register is defined in Table 16 on page 43.

Note: Alternate function selection on the port pins must also be enabled. See the Port A–D Alternate Function Subregisters section on page 47 for details.

| Bit     | 7                                                                  | 6                                                                                     | 5      | 4      | 3      | 2      | 1      | 0      |  |

|---------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--|

| Field   | PAFS27                                                             | PAFS26                                                                                | PAFS25 | PAFS24 | PAFS23 | PAFS22 | PAFS21 | PAFS20 |  |

| RESET   | 00H (all ports of 20/28 pin devices); 04H (Port A of 8-pin device) |                                                                                       |        |        |        |        |        |        |  |

| R/W     | R/W                                                                | R/W                                                                                   | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |  |

| Address | If 08H ir                                                          | If 08H in Port A–D Address Register, accessible through the Port A–D Control Register |        |        |        |        |        |        |  |

#### Bit Description

#### [7] **Port Alternate Function Set 2**

- PAFS2x 0 = Port Alternate Function selected, as defined in Table 16.

- 1 = Port Alternate Function selected, as defined in Table 16.

Note: x indicates the specific GPIO port pin number (7-0).

51

## Architecture

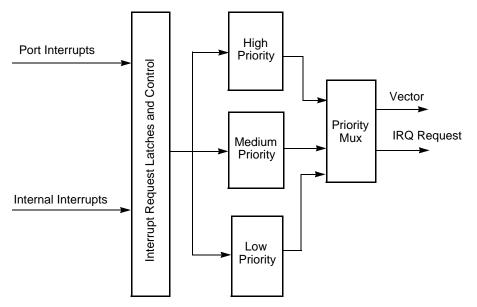

Figure 8 displays the interrupt controller block diagram.

Figure 8. Interrupt Controller Block Diagram

## Operation

This section describes the operational aspects of the following functions.

Master Interrupt Enable: see page 57

Interrupt Vectors and Priority: see page 58

Interrupt Assertion: see page 58

Software Interrupt Assertion: see page 59

Watchdog Timer Interrupt Assertion: see page 59

## Master Interrupt Enable

The master interrupt enable bit (IRQE) in the Interrupt Control Register globally enables and disables interrupts. Interrupts are globally enabled by any of the following actions:

- Execution of an EI (Enable Interrupt) instruction

- Execution of an IRET (Return from Interrupt) instruction

# **Timers**

These Z8 Encore! XP F082A Series products contain two 16-bit reloadable timers that can be used for timing, event counting, or generation of pulse-width modulated (PWM) signals. The timers' feature include:

- 16-bit reload counter

- Programmable prescaler with prescale values from 1 to 128

- PWM output generation

- Capture and compare capability

- External input pin for timer input, clock gating, or capture signal. External input pin signal frequency is limited to a maximum of one-fourth the system clock frequency

- Timer output pin

- Timer interrupt

In addition to the timers described in this chapter, the Baud Rate Generator of the UART (if unused) may also provide basic timing functionality. For information about using the Baud Rate Generator as an additional timer, see the <u>Universal Asynchronous Receiver/</u> <u>Transmitter</u> chapter on page 99.

## Architecture

Figure 9 displays the architecture of the timers.

enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer Reload.

Observe the following steps for configuring a timer for COUNTER Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer.

- Configure the timer for COUNTER Mode.

- Select either the rising edge or falling edge of the Timer Input signal for the count. This selection also sets the initial logic level (High or Low) for the Timer Output alternate function. However, the Timer Output function is not required to be enabled.

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This only affects the first pass in COUNTER Mode. After the first timer Reload in COUNTER Mode, counting always begins at the reset value of 0001H. In COUNTER Mode the Timer High and Low Byte registers must be written with the value 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 7. Write to the Timer Control Register to enable the timer.

In COUNTER Mode, the number of Timer Input transitions since the timer start is computed via the following equation:

COUNTER Mode Timer Input Transitions = Current Count Value-Start Value

### **COMPARATOR COUNTER Mode**

In COMPARATOR COUNTER Mode, the timer counts input transitions from the analog comparator output. The TPOL bit in the Timer Control Register selects whether the count occurs on the rising edge or the falling edge of the comparator output signal. In COMPAR-ATOR COUNTER Mode, the prescaler is disabled.

### **Timer Reload High and Low Byte Registers**

The Timer 0–1 Reload High and Low Byte (TxRH and TxRL) registers, shown in Tables 54 and 55, store a 16-bit reload value, {TRH[7:0], TRL[7:0]}. Values written to the Timer Reload High Byte Register are stored in a temporary holding register. When a write to the Timer Reload Low Byte Register occurs, the temporary holding register value is written to the Timer High Byte Register. This operation allows simultaneous updates of the 16-bit Timer reload value.

In COMPARE Mode, the Timer Reload High and Low Byte registers store the 16-bit Compare value.

| Bit     | 7          | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|---------|------------|-----|-----|-----|-----|-----|-----|-----|--|--|

| Field   | TRH        |     |     |     |     |     |     |     |  |  |

| RESET   | 1          | 1   | 1   | 1   | 1   | 1   | 1   | 1   |  |  |

| R/W     | R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Address | F02H, F0AH |     |     |     |     |     |     |     |  |  |

#### Table 54. Timer 0–1 Reload High Byte Register (TxRH)

| Bit     | 7          | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|---------|------------|-----|-----|-----|-----|-----|-----|-----|--|--|

| Field   | TRL        |     |     |     |     |     |     |     |  |  |

| RESET   | 1          | 1   | 1   | 1   | 1   | 1   | 1   | 1   |  |  |

| R/W     | R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Address | F03H, F0BH |     |     |     |     |     |     |     |  |  |

| Bit      | Description                                                                                                                                                                                                                  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]    | Timer Reload Register High and Low                                                                                                                                                                                           |

| TRH, TRL | These two bytes form the 16-bit reload value, {TRH[7:0], TRL[7:0]}. This value sets the max-<br>imum count value which initiates a timer reload to 0001H. In COMPARE Mode, these two<br>bytes form the 16-bit Compare value. |

into the Watchdog Timer Reload registers results in a one-second time-out at room temperature and 3.3V supply voltage. Time-outs other than one second may be obtained by scaling the calibration values up or down as required.

**Note:** The Watchdog Timer accuracy still degrades as temperature and supply voltage vary. See <u>Table 137</u> on page 235 for details.

### Watchdog Timer Control Register Definitions

This section defines the features of the following Watchdog Timer Control registers.

Watchdog Timer Control Register (WDTCTL): see page 96

Watchdog Timer Reload Upper Byte Register (WDTU): see page 97

Watchdog Timer Reload High Byte Register (WDTH): see page 97

Watchdog Timer Reload Low Byte Register (WDTL): see page 98

### Watchdog Timer Control Register

The Watchdog Timer Control (WDTCTL) Register is a write-only control register. Writing the 55H, AAH unlock sequence to the WDTCTL Register address unlocks the three Watchdog Timer Reload Byte registers (WDTU, WDTH and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL Register address produce no effect on the bits in the WDTCTL Register. The locking mechanism prevents spurious writes to the reload registers. This register address is shared with the read-only Reset Status Register.

| Bit       | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-----------|------------|---|---|---|---|---|---|---|--|--|

| Field     | WDTUNLK    |   |   |   |   |   |   |   |  |  |

| RESET     | Х          | Х | Х | Х | Х | Х | Х | Х |  |  |

| R/W       | W          | W | W | W | W | W | W | W |  |  |

| Address   | FF0H       |   |   |   |   |   |   |   |  |  |

| Note: X = | Undefined. |   |   |   |   |   |   |   |  |  |

| DIL     | Description                                                                                  |

|---------|----------------------------------------------------------------------------------------------|

| [7:0]   | Watchdog Timer Unlock                                                                        |

| WDTUNLK | The software must write the correct unlocking sequence to this register before it is allowed |

|         | to modify the contents of the Watchdog Timer reload registers.                               |

Description

Dit

| Bit          | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5       | 4    | 3     | 2      | 1      | 0    |  |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|--------|--------|------|--|--|--|

| Field        | MPMD[1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | MPEN                                                                                                                                                                                                                                                                                                                                                                                                                                                          | MPMD[0] | MPBT | DEPOL | BRGCTL | RDAIRQ | IREN |  |  |  |

| RESET        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0       | 0    | 0     | 0      | 0      | 0    |  |  |  |

| R/W          | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W     | R/W  | R/W   | R/W    | R/W    | R/W  |  |  |  |

| Address      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         | F4   | 3H    |        |        |      |  |  |  |

| Bit          | Descript                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |      |       |        |        |      |  |  |  |

| [6]<br>MPEN  | <ul> <li>MD[1,0] If MULTIPROCESSOR (9-bit) Mode is enabled:<br/>00 = The UART generates an interrupt request on all received bytes (data and address).<br/>01 = The UART generates an interrupt request only on received address bytes.<br/>10 = The UART generates an interrupt request when a received address byte matches the value stored in the Address Compare Register and on all successive data bytes until an address mismatch occurs.</li> <li>11 = The UART generates an interrupt request on all received data bytes for which the most recent address byte matched the value in the Address Compare Register.</li> <li>MULTIPROCESSOR (9-bit) Enable</li> <li>This bit is used to enable MULTIPROCESSOR (9-bit) Mode.</li> <li>0 = Disable MULTIPROCESSOR (9-bit) Mode.</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |      |       |        |        |      |  |  |  |

| [4]<br>MPBT  | Multipro<br>This bit is<br>used by<br>tion.<br>0 = Send                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <ul> <li>1 = Enable MULTIPROCESSOR (9-bit) Mode.</li> <li>Multiprocessor Bit Transmit This bit is applicable only when MULTIPROCESSOR (9-bit) Mode is enabled. The 9th bit is used by the receiving device to determine if the data byte contains address or data informa- tion. 0 = Send a 0 in the multiprocessor bit location of the data stream (data byte). 1 = Send a 1 in the multiprocessor bit location of the data stream (address byte).</li></ul> |         |      |       |        |        |      |  |  |  |

| [3]<br>DEPOL | <b>Driver E</b><br>0 = DE s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <ul> <li>1 = Send a 1 in the multiprocessor bit location of the data stream (address byte).</li> <li>Driver Enable Polarity</li> <li>0 = DE signal is Active High.</li> <li>1 = DE signal is Active Low.</li> </ul>                                                                                                                                                                                                                                           |         |      |       |        |        |      |  |  |  |

### Table 64. UART Control 1 Register (U0CTL1)

| Table 67. UART Transmit Data Register (U0TXD) |  |

|-----------------------------------------------|--|

| Bit       | 7          | 6 | 5 | 4  | 3  | 2 | 1 | 0 |

|-----------|------------|---|---|----|----|---|---|---|

| Field     |            |   |   | Tک | (D |   |   |   |

| RESET     | Х          | Х | Х | Х  | Х  | Х | Х | Х |

| R/W       | W          | W | W | W  | W  | W | W | W |

| Address   | F40H       |   |   |    |    |   |   |   |

| Note: X = | Undefined. |   |   |    |    |   |   |   |

| Bit   | Description                                                        |

|-------|--------------------------------------------------------------------|

| [7:0] | Transmit Data                                                      |

| TXD   | UART transmitter data byte to be shifted out through the TXDx pin. |

### **UART Receive Data Register**

Data bytes received through the RXDx pin are stored in the UART Receive Data (UxRXD) Register, shown in Table 68. The read-only UART Receive Data Register shares a Register File address with the Write-only UART Transmit Data Register.

| Table 68. UART Receive | Data Register | (U0RXD) |

|------------------------|---------------|---------|

|------------------------|---------------|---------|

| Bit       | 7          | 6         | 5 | 4  | 3  | 2 | 1 | 0 |

|-----------|------------|-----------|---|----|----|---|---|---|

| Field     |            |           |   | RX | (D |   |   |   |

| RESET     | Х          | Х         | Х | Х  | Х  | Х | Х | Х |

| R/W       | R          | R         | R | R  | R  | R | R | R |

| Address   |            | F40H      |   |    |    |   |   |   |

| Note: X = | Undefined. | ndefined. |   |    |    |   |   |   |

| Bit       | Descriptio | n         |   |    |    |   |   |   |

| [7:0] | Receive Data                               |

|-------|--------------------------------------------|

| RXD   | UART receiver data byte from the RXDx pin. |

### **UART Address Compare Register**

The UART Address Compare (UxADDR) Register stores the multi-node network address of the UART (see Table 69). When the MPMD[1] bit of UART Control Register 0 is set, all incoming address bytes are compared to the value stored in the Address Compare Register. Receive interrupts and RDA assertions only occur in the event of a match.

### Flash Operation Timing Using the Flash Frequency Registers

Before performing either a program or erase operation on Flash memory, you must first configure the Flash Frequency High and Low Byte registers. The Flash Frequency registers allow programming and erasing of the Flash with system clock frequencies ranging from 32kHz (32768Hz) through 20MHz.

The Flash Frequency High and Low Byte registers combine to form a 16-bit value, FFREQ, to control timing for Flash program and erase operations. The 16-bit binary Flash Frequency value must contain the system clock frequency (in kHz). This value is calculated using the following equation:

$FFREQ[15:0] = \frac{System Clock Frequency (Hz)}{1000}$

**Caution:** Flash programming and erasure are not supported for system clock frequencies below 32kHz (32768Hz) or above 20MHz. The Flash Frequency High and Low Byte registers must be loaded with the correct value to ensure operation of the Z8 Encore! XP F082A Series devices.

### Flash Code Protection Against External Access

The user code contained within the Flash memory can be protected against external access by the on-chip debugger. Programming the FRP Flash option bit prevents reading of the user code with the On-Chip Debugger. See the <u>Flash Option Bits</u> chapter on page 159 and the <u>On-Chip Debugger</u> chapter on page 180 for more information.

# Flash Code Protection Against Accidental Program and Erasure

The Z8 Encore! XP F082A Series provides several levels of protection against accidental program and erasure of the Flash memory contents. This protection is provided by a combination of the Flash option bits, the register locking mechanism, the page select redundancy and the sector level protection control of the Flash Controller.

### Flash Code Protection Using the Flash Option Bits

The FRP and FWP Flash option bits combine to provide three levels of Flash Program Memory protection, as shown in Table 79. See the <u>Flash Option Bits</u> chapter on page 159 for more information.

#### 150

#### Table 79. Flash Code Protection Using the Flash Option Bits

| FWP | Flash Code Protection Description                                                                                                                                                                     |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Programming and erasing disabled for all of Flash Program Mem-<br>ory. In user code programming, Page Erase and Mass Erase are all<br>disabled. Mass Erase is available through the On-Chip Debugger. |

| 1   | Programming, Page Erase and Mass Erase are enabled for all of Flash Program Memory.                                                                                                                   |

#### Flash Code Protection Using the Flash Controller

At Reset, the Flash Controller locks to prevent accidental program or erasure of the Flash memory. To program or erase the Flash memory, first write the Page Select Register with the target page. Unlock the Flash Controller by making two consecutive writes to the Flash Control Register with the values 73H and 8CH, sequentially. The Page Select Register must be rewritten with the target page. If the two Page Select writes do not match, the controller reverts to a locked state. If the two writes match, the selected page becomes active. See Figure 22 on page 148 for details.

After unlocking a specific page, you can enable either Page Program or Erase. Writing the value 95H causes a Page Erase only if the active page resides in a sector that is not protected. Any other value written to the Flash Control Register locks the Flash Controller. Mass Erase is not allowed in the user code but only in through the Debug Port.

After unlocking a specific page, you can also write to any byte on that page. After a byte is written, the page remains unlocked, allowing for subsequent writes to other bytes on the same page. Further writes to the Flash Control Register cause the active page to revert to a locked state.

#### **Sector-Based Flash Protection**

The final protection mechanism is implemented on a per-sector basis. The Flash memories of Z8 Encore! XP devices are divided into maximum number of 8 sectors. A sector is 1/8 of the total Flash memory size unless this value is smaller than the page size – in which case, the sector and page sizes are equal. On Z8 Encore! F082A Series devices, the sector size is varied according to the Flash memory configuration shown in <u>Table 78</u> on page 146.

The Flash Sector Protect Register can be configured to prevent sectors from being programmed or erased. After a sector is protected, it cannot be unprotected by user code. The Flash Sector Protect Register is cleared after reset, and any previously-written protection values are lost. User code must write this register in their initialization routine if they prefer to enable sector protection.

The Flash Sector Protect Register shares its Register File address with the Page Select Register. The Flash Sector Protect Register is accessed by writing the Flash Control Regis-

| Info Page | Memory  |                         |                          |                |

|-----------|---------|-------------------------|--------------------------|----------------|

| Address   | Address | Compensation Usage      | ADC Mode                 | Reference Type |

| 12        | FE12    | Positive Gain High Byte | Differential Unbuffered  | Internal 2.0 V |

| 13        | FE13    | Positive Gain Low Byte  | Differential Unbuffered  | Internal 2.0 V |

| 30        | FE30    | Negative Gain High Byte | Differential Unbuffered  | Internal 2.0 V |

| 31        | FE31    | Negative Gain Low Byte  | Differential Unbuffered  | Internal 2.0 V |

| 72        | FE72    | Offset                  | Differential Unbuffered  | Internal 1.0 V |

| 14        | FE14    | Positive Gain High Byte | Differential Unbuffered  | Internal 1.0 V |

| 15        | FE15    | Positive Gain Low Byte  | Differential Unbuffered  | Internal 1.0 V |

| 32        | FE32    | Negative Gain High Byte | Differential Unbuffered  | Internal 1.0 V |

| 33        | FE33    | Negative Gain Low Byte  | Differential Unbuffered  | Internal 1.0 V |

| 75        | FE75    | Offset                  | Differential Unbuffered  | External 2.0 V |

| 16        | FE16    | Positive Gain High Byte | Differential Unbuffered  | External 2.0 V |

| 17        | FE17    | Positive Gain Low Byte  | Differential Unbuffered  | External 2.0 V |

| 34        | FE34    | Negative Gain High Byte | Differential Unbuffered  | External 2.0 V |

| 35        | FE35    | Negative Gain Low Byte  | Differential Unbuffered  | External 2.0 V |

| 78        | FE78    | Offset                  | Differential 1x Buffered | Internal 2.0 V |

| 18        | FE18    | Positive Gain High Byte | Differential 1x Buffered | Internal 2.0 V |

| 19        | FE19    | Positive Gain Low Byte  | Differential 1x Buffered | Internal 2.0 V |

| 36        | FE36    | Negative Gain High Byte | Differential 1x Buffered | Internal 2.0 V |

| 37        | FE37    | Negative Gain Low Byte  | Differential 1x Buffered | Internal 2.0 V |

| 7B        | FE7B    | Offset                  | Differential 1x Buffered | External 2.0 V |

| 1A        | FE1A    | Positive Gain High Byte | Differential 1x Buffered | External 2.0 V |

| 1B        | FE1B    | Positive Gain Low Byte  | Differential 1x Buffered | External 2.0 V |

| 38        | FE38    | Negative Gain High Byte | Differential 1x Buffered | External 2.0 V |

| 39        | FE39    | Negative Gain Low Byte  | Differential 1x Buffered | External 2.0 V |

### Table 97. ADC Calibration Data Location (Continued)

### 173

#### Table 101. Watchdog Calibration Low Byte at 007FH (WDTCALL)

| Bit       | 7           | 6            | 5              | 4           | 3           | 2    | 1   | 0   |

|-----------|-------------|--------------|----------------|-------------|-------------|------|-----|-----|

| Field     |             |              |                | WDT         | CALL        |      |     |     |

| RESET     | U           | U            | U              | U           | U           | U    | U   | U   |

| R/W       | R/W         | R/W          | R/W            | R/W         | R/W         | R/W  | R/W | R/W |

| Address   |             |              | Infor          | mation Page | e Memory 00 | )7FH |     |     |

| Note: U = | Unchanged b | y Reset. R/W | / = Read/Write | Э.          |             |      |     |     |

| Bit     | Description                                                                              |

|---------|------------------------------------------------------------------------------------------|

| [7:0]   | Watchdog Timer Calibration Low Byte                                                      |

| WDTCALL | The WDTCALH and WDTCALL bytes, when loaded into the Watchdog Timer reload regis-         |

|         | ters result in a one second time-out at room temperature and 3.3V supply voltage. To use |

|         | the Watchdog Timer calibration, user code must load WDTU with 0x00, WDTH with WDT-       |

|         | CALH and WDTL with WDTCALL.                                                              |

### **Serialization Data**

#### Table 102. Serial Number at 001C - 001F (S\_NUM)

| Bit       | 7           | 6                                 | 5             | 4   | 3   | 2   | 1   | 0   |

|-----------|-------------|-----------------------------------|---------------|-----|-----|-----|-----|-----|

| Field     |             |                                   |               | S_N | NUM |     |     |     |

| RESET     | U           | U                                 | U             | U   | U   | U   | U   | U   |

| R/W       | R/W         | R/W                               | R/W           | R/W | R/W | R/W | R/W | R/W |

| Address   |             | Information Page Memory 001C-001F |               |     |     |     |     |     |

| Note: U = | Unchanged b | by Reset. R/W                     | / = Read/Writ | e.  |     |     |     |     |

| Bit   | Description                                                          |

|-------|----------------------------------------------------------------------|

| [7:0] | Serial Number Byte                                                   |

| S_NUM | The serial number is a unique four-byte binary value. See Table 103. |

#### Table 103. Serialization Data Locations

| Info Page<br>Address | Memory<br>Address | Usage                                     |

|----------------------|-------------------|-------------------------------------------|

| 1C                   | FE1C              | Serial Number Byte 3 (most significant).  |

| 1D                   | FE1D              | Serial Number Byte 2.                     |

| 1E                   | FE1E              | Serial Number Byte 1.                     |

| 1F                   | FE1F              | Serial Number Byte 0 (least significant). |

### Table 123. CPU Control Instructions (Continued)

| Mnemonic | Operands | Instruction            |  |  |  |  |  |

|----------|----------|------------------------|--|--|--|--|--|

| RCF      | —        | Reset Carry Flag       |  |  |  |  |  |

| SCF      | —        | Set Carry Flag         |  |  |  |  |  |

| SRP      | SIC      | Set Register Pointer   |  |  |  |  |  |

| STOP     | —        | STOP Mode              |  |  |  |  |  |

| WDT      | —        | Watchdog Timer Refresh |  |  |  |  |  |

### Table 124. Load Instructions

| Mnemonic | Operands    | Instruction                                                             |

|----------|-------------|-------------------------------------------------------------------------|

| CLR      | dst         | Clear                                                                   |

| LD       | dst, src    | Load                                                                    |

| LDC      | dst, src    | Load Constant to/from Program Memory                                    |

| LDCI     | dst, src    | Load Constant to/from Program Memory and Auto-<br>Increment Addresses   |

| LDE      | dst, src    | Load External Data to/from Data Memory                                  |

| LDEI     | dst, src    | Load External Data to/from Data Memory and Auto-<br>Increment Addresses |

| LDWX     | dst, src    | Load Word using Extended Addressing                                     |

| LDX      | dst, src    | Load using Extended Addressing                                          |

| LEA      | dst, X(src) | Load Effective Address                                                  |

| POP      | dst         | Рор                                                                     |

| POPX     | dst         | Pop using Extended Addressing                                           |

| PUSH     | src         | Push                                                                    |

| PUSHX    | src         | Push using Extended Addressing                                          |

#### Table 125. Logical Instructions

| Mnemonic | Operands | Instruction                                    |

|----------|----------|------------------------------------------------|

| AND      | dst, src | Logical AND                                    |

| ANDX     | dst, src | Logical AND using Extended Addressing          |

| СОМ      | dst      | Complement                                     |

| OR       | dst, src | Logical OR                                     |

| ORX      | dst, src | Logical OR using Extended Addressing           |

| XOR      | dst, src | Logical Exclusive OR                           |

| XORX     | dst, src | Logical Exclusive OR using Extended Addressing |

221

| Assembly      |                                                                                                                        | Address<br>Mode |        | Opcode(s) | Flags |   |   |     |   |   | Fetch<br>Cycle | Instr.<br>Cycle |

|---------------|------------------------------------------------------------------------------------------------------------------------|-----------------|--------|-----------|-------|---|---|-----|---|---|----------------|-----------------|

| Mnemonic      | Symbolic Operation                                                                                                     | dst src         |        | (Hex)     | С     | Ζ | S | V D |   | Н | S              | S               |

| TMX dst, src  | dst AND src                                                                                                            | ER              | ER     | 78        | -     | * | * | 0   | _ | - | 4              | 3               |

|               |                                                                                                                        | ER              | IM     | 79        |       |   |   |     |   |   | 4              | 3               |

| TRAP Vector   | $SP \leftarrow SP - 2$<br>@SP \leftarrow PC<br>$SP \leftarrow SP - 1$<br>@SP \leftarrow FLAGS<br>PC \leftarrow @Vector |                 | Vector | F2        | _     | - | - | -   | - | _ | 2              | 6               |

| WDT           |                                                                                                                        |                 |        | 5F        | _     | _ | _ | _   | _ | _ | 1              | 2               |

| XOR dst, src  | $dst \gets dst \ XOR \ src$                                                                                            | r               | r      | B2        | _     | * | * | 0   | _ | _ | 2              | 3               |

|               |                                                                                                                        | r               | lr     | B3        | -     |   |   |     |   |   | 2              | 4               |

|               |                                                                                                                        | R               | R      | B4        |       |   |   |     |   |   | 3              | 3               |

|               |                                                                                                                        | R               | IR     | B5        | -     |   |   |     |   |   | 3              | 4               |

|               |                                                                                                                        | R               | IM     | B6        | -     |   |   |     |   |   | 3              | 3               |

|               |                                                                                                                        | IR              | IM     | B7        |       |   |   |     |   |   | 3              | 4               |

| XORX dst, src | $dst \gets dst \ XOR \ src$                                                                                            | ER              | ER     | B8        | _     | * | * | 0   | _ | _ | 4              | 3               |

|               |                                                                                                                        | ER              | IM     | B9        |       |   |   |     |   |   | 4              | 3               |

### Table 128. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

– = Unaffected.

X = Undefined.

0 = Reset to 0.

1 =Set to 1.

# **Electrical Characteristics**

The data in this chapter represents all known data prior to qualification and characterization of the F082A Series of products, and is therefore subject to change. Additional electrical characteristics may be found in the individual chapters of this document.

### **Absolute Maximum Ratings**

Stresses greater than those listed in Table 130 may cause permanent damage to the device. These ratings are stress ratings only. Operation of the device at any condition outside those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. For improved reliability, tie unused inputs to one of the supply voltages ( $V_{DD}$  or  $V_{SS}$ ).

| Parameter                                           | Minimum | Maximum | Units | Notes |

|-----------------------------------------------------|---------|---------|-------|-------|

| Ambient temperature under bias                      | -40     | +105    | °C    |       |

| Storage temperature                                 | -65     | +150    | °C    |       |

| Voltage on any pin with respect to V <sub>SS</sub>  | -0.3    | +5.5    | V     | 1     |

|                                                     | -0.3    | +3.9    | V     | 2     |

| Voltage on $V_{DD}$ pin with respect to $V_{SS}$    | -0.3    | +3.6    | V     |       |

| Maximum current on input and/or inactive output pin | -5      | +5      | μA    |       |

| Maximum output current from active output pin       | -25     | +25     | mA    |       |

| 8-pin Packages Maximum Ratings at 0°C to 70°C       |         |         |       |       |

| Total power dissipation                             |         | 220     | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$    |         | 60      | mA    |       |

| 20-pin Packages Maximum Ratings at 0°C to 70°C      |         |         |       |       |

| Total power dissipation                             |         | 430     | mW    |       |

| Table 130. Absolute Maximum Ratings | Table | 130. | Absolute | Maximum | Ratings |

|-------------------------------------|-------|------|----------|---------|---------|

|-------------------------------------|-------|------|----------|---------|---------|

| Jaquin<br>Munu<br>Lue<br>Z8 Encore! XP F082A | Lash<br>E<br>Series | W<br>V<br>With 11 | SO<br>N<br>(B Flas | y<br>1/0 Lines | Hit Interrupts | e 16-Bit Timers w/PWM | 6<br>4<br>10-Bit A/D Channels | ici<br>UART with IrDA | D Comparator | Temperature Sensor | Description         |

|----------------------------------------------|---------------------|-------------------|--------------------|----------------|----------------|-----------------------|-------------------------------|-----------------------|--------------|--------------------|---------------------|

| Standard Temperatu                           |                     |                   |                    | -              |                |                       | -                             | •                     |              |                    |                     |

| Z8F012APB020SG                               | 1KB                 | 256 B             | 16 B               | 6              | 14             | 2                     | 4                             | 1                     | 1            | 1                  | PDIP 8-pin package  |

| Z8F012AQB020SG                               | 1KB                 | 256 B             | 16 B               | 6              | 14             | 2                     | 4                             | 1                     | 1            | 1                  | QFN 8-pin package   |

| Z8F012ASB020SG                               | 1KB                 | 256 B             | 16 B               | 6              | 14             | 2                     | 4                             | 1                     | 1            | 1                  | SOIC 8-pin package  |

| Z8F012ASH020SG                               | 1KB                 | 256 B             | 16 B               | 17             | 20             | 2                     | 7                             | 1                     | 1            | 1                  | SOIC 20-pin package |

| Z8F012AHH020SG                               | 1KB                 | 256 B             | 16 B               | 17             | 20             | 2                     | 7                             | 1                     | 1            | 1                  | SSOP 20-pin package |

| Z8F012APH020SG                               | 1KB                 | 256 B             | 16 B               | 17             | 20             | 2                     | 7                             | 1                     | 1            | 1                  | PDIP 20-pin package |

| Z8F012ASJ020SG                               | 1KB                 | 256 B             | 16 B               | 23             | 20             | 2                     | 8                             | 1                     | 1            | 1                  | SOIC 28-pin package |

| Z8F012AHJ020SG                               | 1KB                 | 256 B             | 16 B               | 23             | 20             | 2                     | 8                             | 1                     | 1            | 1                  | SSOP 28-pin package |

| Z8F012APJ020SG                               | 1KB                 | 256 B             | 16 B               | 23             | 20             | 2                     | 8                             | 1                     | 1            | 1                  | PDIP 28-pin package |

| Extended Temperatu                           | re: –40'            | °C to 10          | 5°C                |                |                |                       |                               |                       |              |                    |                     |

| Z8F012APB020EG                               | 1KB                 | 256 B             | 16 B               | 6              | 14             | 2                     | 4                             | 1                     | 1            | 1                  | PDIP 8-pin package  |

| Z8F012AQB020EG                               | 1KB                 | 256 B             | 16 B               | 6              | 14             | 2                     | 4                             | 1                     | 1            | 1                  | QFN 8-pin package   |

| Z8F012ASB020EG                               | 1KB                 | 256 B             | 16 B               | 6              | 14             | 2                     | 4                             | 1                     | 1            | 1                  | SOIC 8-pin package  |

| Z8F012ASH020EG                               | 1KB                 | 256 B             | 16 B               | 17             | 20             | 2                     | 7                             | 1                     | 1            | 1                  | SOIC 20-pin package |

| Z8F012AHH020EG                               | 1KB                 | 256 B             | 16 B               | 17             | 20             | 2                     | 7                             | 1                     | 1            | 1                  | SSOP 20-pin package |

| Z8F012APH020EG                               | 1KB                 | 256 B             | 16 B               | 17             | 20             | 2                     | 7                             | 1                     | 1            | 1                  | PDIP 20-pin package |

| Z8F012ASJ020EG                               | 1KB                 | 256 B             | 16 B               | 23             | 20             | 2                     | 8                             | 1                     | 1            | 1                  | SOIC 28-pin package |

| Z8F012AHJ020EG                               | 1KB                 | 256 B             | 16 B               | 23             | 20             | 2                     | 8                             | 1                     | 1            | 1                  | SSOP 28-pin package |

| Z8F012APJ020EG                               | 1KB                 | 256 B             | 16 B               | 23             | 20             | 2                     | 8                             | 1                     | 1            | 1                  | PDIP 28-pin package |

### Table 148. Z8 Encore! XP F082A Series Ordering Matrix