Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                       |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 6                                                            |

| Program Memory Size        | 2KB (2K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 64 x 8                                                       |

| RAM Size                   | 512 x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 4x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | 0°C ~ 70°C (TA)                                              |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f022asb020sg    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **CPU and Peripheral Overview**

The eZ8 CPU, Zilog's latest 8-bit Central Processing Unit (CPU), meets the continuing demand for faster and more code-efficient microcontrollers. The eZ8 CPU executes a superset of the original Z8 instruction set. The features of eZ8 CPU include:

- Direct register-to-register architecture allows each register to function as an accumulator, improving execution time and decreasing the required program memory

- Software stack allows much greater depth in subroutine calls and interrupts than hardware stacks

- Compatible with existing Z8 code

- Expanded internal Register File allows access of up to 4 KB

- New instructions improve execution efficiency for code developed using higherlevel programming languages, including C

- Pipelined instruction fetch and execution

- New instructions for improved performance including BIT, BSWAP, BTJ, CPC, LDC, LDCI, LEA, MULT and SRL

- New instructions support 12-bit linear addressing of the Register File

- Up to 10 MIPS operation

- C-Compiler friendly

- 2 to 9 clock cycles per instruction

For more information about eZ8 CPU, refer to the <u>eZ8 CPU Core User Manual</u> (<u>UM0128</u>), which is available for download on <u>www.zilog.com</u>.

### **10-Bit Analog-to-Digital Converter**

The optional analog-to-digital converter (ADC) converts an analog input signal to a 10-bit binary number. The ADC accepts inputs from eight different analog input pins in both single-ended and differential modes. The ADC also features a unity gain buffer when high input impedance is required.

### **Low-Power Operational Amplifier**

The optional low-power operational amplifier (LPO) is a general-purpose amplifier primarily targeted for current sense applications. The LPO output may be routed internally to the ADC or externally to a pin.

# **Internal Precision Oscillator**

The internal precision oscillator (IPO) is a trimmable clock source that requires no external components.

# **Temperature Sensor**

The optional temperature sensor produces an analog output proportional to the device temperature. This signal can be sent to either the ADC or the analog comparator.

# **Analog Comparator**

The analog comparator compares the signal at an input pin with either an internal programmable voltage reference or a second input pin. The comparator output can be used to drive either an output pin or to generate an interrupt.

# **External Crystal Oscillator**

The crystal oscillator circuit provides highly accurate clock frequencies with the use of an external crystal, ceramic resonator or RC network.

# Low Voltage Detector

The low voltage detector (LVD) is able to generate an interrupt when the supply voltage drops below a user-programmable level. The LVD is available on 8-pin devices only.

# **On-Chip Debugger**

The Z8 Encore! XP F082A Series products feature an integrated on-chip debugger (OCD) accessed via a single-pin interface. The OCD provides a rich-set of debugging capabilities, such as reading and writing registers, programming Flash memory, setting breakpoints and executing code.

# **Universal Asynchronous Receiver/Transmitter**

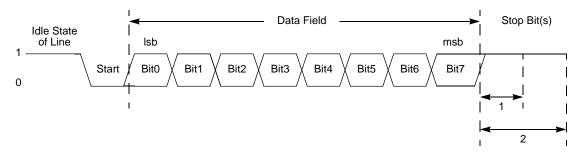

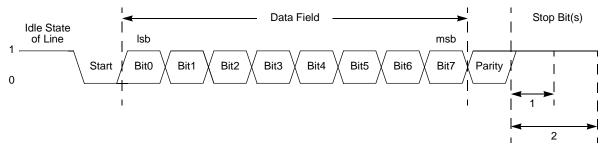

The full-duplex universal asynchronous receiver/transmitter (UART) is included in all Z8 Encore! XP package types. The UART supports 8- and 9-bit data modes and selectable parity. The UART also supports multi-drop address processing in hardware. The UART baud rate generator (BRG) can be configured and used as a basic 16-bit timer.

# Timers

Two enhanced 16-bit reloadable timers can be used for timing/counting events or for motor control operations. These timers provide a 16-bit programmable reload counter and

# **Port A–D Control Registers**

The Port A–D Control registers set the GPIO port operation. The value in the corresponding Port A–D Address Register determines which subregister is read from or written to by a Port A–D Control Register transaction; see Table 20.

| Bit     | 7   | 6                       | 5 | 4  | 3  | 2 | 1 | 0 |

|---------|-----|-------------------------|---|----|----|---|---|---|

| Field   |     | PCTL                    |   |    |    |   |   |   |

| RESET   |     |                         |   | 00 | )H |   |   |   |

| R/W     | R/W | R/W R/W R/W R/W R/W R/W |   |    |    |   |   |   |

| Address |     | FD1H, FD5H, FD9H, FDDH  |   |    |    |   |   |   |

#### Table 20. Port A–D Control Registers (PxCTL)

| Bit   | Description                                                                                              |

|-------|----------------------------------------------------------------------------------------------------------|

| [7:0] | Port Control                                                                                             |

| PCTLx | The Port Control Register provides access to all subregisters that configure the GPIO port<br>operation. |

|       |                                                                                                          |

Note: x indicates the specific GPIO port pin number (7–0).

# Port A–D Data Direction Subregisters

The Port A–D Data Direction subregister is accessed through the Port A–D Control Register by writing 01H to the Port A–D Address Register; see Table 21.

| Bit     | 7         | 6                                                                                     | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----------|---------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|

| Field   | DD7       | DD6                                                                                   | DD5 | DD4 | DD3 | DD2 | DD1 | DD0 |

| RESET   | 1         | 1                                                                                     | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W     | R/W       | R/W                                                                                   | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | If 01H ir | If 01H in Port A–D Address Register, accessible through the Port A–D Control Register |     |     |     |     |     |     |

Table 21. Port A–D Data Direction Subregisters (PxDD)

| Bit   | Description                                                                                                                                                  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0] | Data Direction                                                                                                                                               |

| DDx   | These bits control the direction of the associated port pin. Port Alternate Function operation<br>overrides the Data Direction Register setting.             |

|       | 0 = Output. Data in the Port A–D Output Data Register is driven onto the port pin.                                                                           |

|       | <ul> <li>1 = Input. The port pin is sampled and the value written into the Port A–D Input Data Register.</li> <li>The output driver is tristated.</li> </ul> |

| Note: | x indicates the specific GPIO port pin number (7–0).                                                                                                         |

#### 49

### Port A–D Stop Mode Recovery Source Enable Subregisters

The Port A–D Stop Mode Recovery Source Enable Subregister, shown in Table 25, is accessed through the Port A–D Control Register by writing 05H to the Port A–D Address Register. Setting the bits in the Port A–D Stop Mode Recovery Source Enable subregisters to 1 configures the specified port pins as a Stop Mode Recovery source. During STOP Mode, any logic transition on a port pin enabled as a Stop Mode Recovery source initiates Stop Mode Recovery.

#### Table 25. Port A–D Stop Mode Recovery Source Enable Subregisters (PxSMRE)

| Bit     | 7         | 6            | 5           | 4             | 3            | 2            | 1            | 0        |

|---------|-----------|--------------|-------------|---------------|--------------|--------------|--------------|----------|

| Field   | PSMRE7    | PSMRE6       | PSMRE5      | PSMRE4        | PSMRE3       | PSMRE2       | PSMRE1       | PSMRE0   |

| RESET   | 0         | 0            | 0           | 0             | 0            | 0            | 0            | 0        |

| R/W     | R/W       | R/W          | R/W         | R/W           | R/W          | R/W          | R/W          | R/W      |

| Address | If 05H ir | n Port A–D A | Address Reg | jister, acces | sible throug | h the Port A | –D Control F | Register |

#### Bit Description

[7:0] **Port Stop Mode Recovery Source Enabled**

PSMREx 0 = The port pin is not configured as a Stop Mode Recovery source. Transitions on this pin during STOP Mode do not initiate Stop Mode Recovery.

1 = The port pin is configured as a Stop Mode Recovery source. Any logic transition on this pin during STOP Mode initiates Stop Mode Recovery.

Note: x indicates the specific GPIO port pin number (7-0).

**Example 1.** A poor coding style that can result in lost interrupt requests:

LDX r0, IRQ0 AND r0, MASK LDX IRQ0, r0

To avoid missing interrupts, use the coding style in Example 2 to clear bits in the Interrupt Request 0 Register:

**Example 2.** A good coding style that avoids lost interrupt requests:

ANDX IRQ0, MASK

### **Software Interrupt Assertion**

Program code can generate interrupts directly. Writing a 1 to the correct bit in the Interrupt Request Register triggers an interrupt (assuming that interrupt is enabled). When the interrupt request is acknowledged by the eZ8 CPU, the bit in the Interrupt Request Register is automatically cleared to 0.

**Caution:** Zilog recommends not using a coding style to generate software interrupts by setting bits in the Interrupt Request registers. All incoming interrupts received between execution of the first LDX command and the final LDX command are lost. See Example 3, which follows.

**Example 3.** A poor coding style that can result in lost interrupt requests:

```

LDX r0, IRQ0

OR r0, MASK

LDX IRQ0, r0

```

To avoid missing interrupts, use the coding style in Example 4 to set bits in the Interrupt Request registers:

**Example 4.** A good coding style that avoids lost interrupt requests:

ORX IRQ0, MASK

### Watchdog Timer Interrupt Assertion

The Watchdog Timer interrupt behavior is different from interrupts generated by other sources. The Watchdog Timer continues to assert an interrupt as long as the time-out condition continues. As it operates on a different (and usually slower) clock domain than the rest of the device, the Watchdog Timer continues to assert this interrupt for many system clocks until the counter rolls over.

| Bit           | Description (Continued)                                                  |

|---------------|--------------------------------------------------------------------------|

| [4]<br>U0RENL | UART 0 Receive Interrupt Request Enable Low Bit                          |

| [3]<br>U0TENL | UART 0 Transmit Interrupt Request Enable Low Bit                         |

| [2:1]         | <b>Reserved</b><br>These bits are reserved and must be programmed to 00. |

| [0]<br>ADCENL | ADC Interrupt Request Enable Low Bit                                     |

# **IRQ1 Enable High and Low Bit Registers**

Table 41 describes the priority control for IRQ1. The IRQ1 Enable High and Low Bit registers, shown in Tables 41 and 42, form a priority-encoded enabling for interrupts in the Interrupt Request 1 Register.

| IRQ1ENH[x]        | IRQ1ENL[x]        | Priority | Description |

|-------------------|-------------------|----------|-------------|

| 0                 | 0                 | Disabled | Disabled    |

| 0                 | 1                 | Level 1  | Low         |

| 1                 | 0                 | Level 2  | Medium      |

| 1                 | 1                 | Level 3  | High        |

| Note: x indicates | register bits 0-7 |          |             |

### Table 41. IRQ1 Enable and Priority Encoding

enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer Reload.

Observe the following steps for configuring a timer for COUNTER Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer.

- Configure the timer for COUNTER Mode.

- Select either the rising edge or falling edge of the Timer Input signal for the count. This selection also sets the initial logic level (High or Low) for the Timer Output alternate function. However, the Timer Output function is not required to be enabled.

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This only affects the first pass in COUNTER Mode. After the first timer Reload in COUNTER Mode, counting always begins at the reset value of 0001H. In COUNTER Mode the Timer High and Low Byte registers must be written with the value 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 7. Write to the Timer Control Register to enable the timer.

In COUNTER Mode, the number of Timer Input transitions since the timer start is computed via the following equation:

COUNTER Mode Timer Input Transitions = Current Count Value-Start Value

### COMPARATOR COUNTER Mode

In COMPARATOR COUNTER Mode, the timer counts input transitions from the analog comparator output. The TPOL bit in the Timer Control Register selects whether the count occurs on the rising edge or the falling edge of the comparator output signal. In COMPAR-ATOR COUNTER Mode, the prescaler is disabled.

The PWM period is represented by the following equation:

$PWM Period (s) = \frac{Reload Value \times Prescale}{System Clock Frequency (Hz)}$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, use the ONE-SHOT Mode equation to determine the first PWM time-out period.

If TPOL is set to 0, the ratio of the PWM output High time to the total period is represented by:

PWM Output High Time Ratio (%) =  $\frac{\text{Reload Value} - \text{PWM Value}}{\text{Reload Value}} \times 100$

If TPOL is set to 1, the ratio of the PWM output High time to the total period is represented by:

PWM Output High Time Ratio (%) =  $\frac{PWM Value}{Reload Value} \times 100$

### **PWM DUAL OUTPUT Mode**

In PWM DUAL OUTPUT Mode, the timer outputs a Pulse-Width Modulated (PWM) output signal pair (basic PWM signal and its complement) through two GPIO port pins. The timer input is the system clock. The timer first counts up to the 16-bit PWM match value stored in the Timer PWM High and Low Byte registers. When the timer count value matches the PWM value, the Timer Output toggles. The timer continues counting until it reaches the reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

If the TPOL bit in the Timer Control Register is set to 1, the Timer Output signal begins as a High (1) and transitions to a Low (0) when the timer value matches the PWM value. The Timer Output signal returns to a High (1) after the timer reaches the reload value and is reset to 0001H.

If the TPOL bit in the Timer Control Register is set to 0, the Timer Output signal begins as a Low (0) and transitions to a High (1) when the timer value matches the PWM value. The Timer Output signal returns to a Low (0) after the timer reaches the reload value and is reset to 0001H.

The timer also generates a second PWM output signal Timer Output Complement. The Timer Output Complement is the complement of the Timer Output PWM signal. A programmable deadband delay can be configured to time delay (0 to 128 system clock cycles) PWM output transitions on these two pins from a low to a high (inactive to active). This

- 5. Enable the timer interrupt, if appropriate and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input capture and reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the reload event by setting TICONFIG field of the TxCTL0 Register.

- 6. Configure the associated GPIO port pin for the Timer Input alternate function.

- 7. Write to the Timer Control Register to enable the timer and initiate counting.

In CAPTURE Mode, the elapsed time from timer start to Capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

### **CAPTURE RESTART Mode**

In CAPTURE RESTART Mode, the current timer count value is recorded when the acceptable external Timer Input transition occurs. The Capture count value is written to the Timer PWM High and Low Byte registers. The timer input is the system clock. The TPOL bit in the Timer Control Register determines if the Capture occurs on a rising edge or a falling edge of the Timer Input signal. When the Capture event occurs, an interrupt is generated and the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL0 Register is set to indicate the timer interrupt is because of an input capture event.

If no Capture event occurs, the timer counts up to the 16-bit Compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL0 Register is cleared to indicate the timer interrupt is not caused by an input capture event.

Observe the following steps for configuring a timer for CAPTURE RESTART Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE RESTART Mode by writing the TMODE bits in the TxCTL1 Register and the TMODEHI bit in TxCTL0 Register

- Set the prescale value

- Set the Capture edge (rising or falling) for the Timer Input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- Set the initial logic level (High or Low) for the Timer Output alternate function, if appropriate

- 2. Write to the Timer High and Low Byte registers to set the starting count value.

- 3. Write to the Timer Reload High and Low Byte registers to set the Compare value.

- 4. Enable the timer interrupt, if appropriate and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 6. Write to the Timer Control Register to enable the timer and initiate counting.

In COMPARE Mode, the system clock always provides the timer input. The Compare time can be calculated by the following equation:

COMPARE Mode Time (s) = (Compare Value – Start Value) × Prescale System Clock Frequency (Hz)

### GATED Mode

In GATED Mode, the timer counts only when the Timer Input signal is in its active state (asserted), as determined by the TPOL bit in the Timer Control Register. When the Timer Input signal is asserted, counting begins. A timer interrupt is generated when the Timer Input signal is deasserted or a timer reload occurs. To determine if a Timer Input signal deassertion generated the interrupt, read the associated GPIO input value and compare to the value stored in the TPOL bit.

The timer counts up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. When reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes (assuming the Timer Input signal remains asserted). Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer reset.

Observe the following steps for configuring a timer for GATED Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

#### Bit Description (Continued)

### [6] **GATED Mode**

- TPOL (cont'd)

- 0 = Timer counts when the Timer Input signal is High (1) and interrupts are generated on the falling edge of the Timer Input.

- 1 = Timer counts when the Timer Input signal is Low (0) and interrupts are generated on the rising edge of the Timer Input.

#### CAPTURE/COMPARE Mode

- 0 = Counting is started on the first rising edge of the Timer Input signal. The current count is captured on subsequent rising edges of the Timer Input signal.

- 1 = Counting is started on the first falling edge of the Timer Input signal. The current count is captured on subsequent falling edges of the Timer Input signal.

#### **PWM DUAL OUTPUT Mode**

- 0 = Timer Output is forced Low (0) and Timer Output Complement is forced High (1) when the timer is disabled. When enabled, the Timer Output is forced High (1) upon PWM count match and forced Low (0) upon reload. When enabled, the Timer Output Complement is forced Low (0) upon PWM count match and forced High (1) upon reload. The PWMD field in TxCTL0 Register is a programmable delay to control the number of cycles time delay before the Timer Output and the Timer Output Complement is forced to High (1).

- 1 = Timer Output is forced High (1) and Timer Output Complement is forced Low (0) when the timer is disabled. When enabled, the Timer Output is forced Low (0) upon PWM count match and forced High (1) upon reload. When enabled, the Timer Output Complement is forced High (1) upon PWM count match and forced Low (0) upon reload. The PWMD field in TxCTL0 Register is a programmable delay to control the number of cycles time delay before the Timer Output and the Timer Output Complement is forced to Low (0).

#### **CAPTURE RESTART Mode**

- 0 = Count is captured on the rising edge of the Timer Input signal.

- 1 = Count is captured on the falling edge of the Timer Input signal.

#### **COMPARATOR COUNTER Mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload. Also:

0 =Count is captured on the rising edge of the comparator output.

1 = Count is captured on the falling edge of the comparator output.

**Caution:** When the Timer Output alternate function TxOUT on a GPIO port pin is enabled, TxOUT changes to whatever state the TPOL bit is in. The timer does not need to be enabled for that to happen. Also, the Port Data Direction Subregister is not required to be set to output on TxOUT. Changing the TPOL bit with the timer enabled and running does not immediately change the TxOUT.

Figure 11. UART Asynchronous Data Format without Parity

Figure 12. UART Asynchronous Data Format with Parity

# **Transmitting Data using the Polled Method**

Observe the following steps to transmit data using the polled method of operation:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the required baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Write to the UART Control 1 Register, if MULTIPROCESSOR Mode is appropriate, to enable MULTIPROCESSOR (9-bit) Mode functions.

- 4. Set the Multiprocessor Mode Select (MPEN) bit to enable MULTIPROCESSOR Mode.

- 5. Write to the UART Control 0 Register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission

- Set the parity enable bit (PEN), if parity is appropriate and MULTIPROCESSOR Mode is not enabled and select either even or odd parity (PSEL)

- Write to BUFMODE[2:0] to select SINGLE-ENDED or DIFFERENTIAL mode, plus unbuffered or buffered mode.

- Write the REFSELH bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELL bit is contained in the ADC Control Register 0.

- 3. Write to the ADC Control Register 0 to configure the ADC for continuous conversion. The bit fields in the ADC Control Register may be written simultaneously:

- Write to the ANAIN[3:0] field to select from the available analog input sources (different input pins available depending on the device).

- Set CONT to 1 to select continuous conversion.

- If the internal VREF must be output to a pin, set the REFEXT bit to 1. The internal voltage reference must be enabled in this case.

- Write the REFSELL bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELH bit is contained in ADC Control/Status Register 1.

- Set CEN to 1 to start the conversions.

- 4. When the first conversion in continuous operation is complete (after 5129 system clock cycles, plus the 40 cycles for power-up, if necessary), the ADC control logic performs the following operations:

- CEN resets to 0 to indicate the first conversion is complete. CEN remains 0 for all subsequent conversions in continuous operation

- An interrupt request is sent to the Interrupt Controller to indicate the conversion is complete

- 5. The ADC writes a new data result every 256 system clock cycles. For each completed conversion, the ADC control logic performs the following operations:

- Writes the 13-bit two's complement result to {ADCD\_H[7:0], ADCD\_L[7:3]}

- Sends an interrupt request to the Interrupt Controller denoting conversion complete

- 6. To disable continuous conversion, clear the CONT bit in the ADC Control Register to 0.

### Interrupts

The ADC is able to interrupt the CPU when a conversion has been completed. When the ADC is disabled, no new interrupts are asserted; however, an interrupt pending when the ADC is disabled is not cleared.

These serial numbers are stored in the Flash information page and are unaffected by mass erasure of the device's Flash memory. See the Reading the Flash Information Page section below and the <u>Serialization Data section on page 173</u> for more details.

### **Randomized Lot Identification Bits**

As an optional feature, Zilog is able to provide a factory-programmed random lot identifier. With this feature, all devices in a given production lot are programmed with the same random number. This random number is uniquely regenerated for each successive production lot and is not likely to be repeated.

The randomized lot identifier is a 32 byte binary value, stored in the Flash information page and is unaffected by mass erasure of the device's Flash memory. See Reading the Flash Information Page, below, and the <u>Randomized Lot Identifier section on page 174</u> for more details.

# **Reading the Flash Information Page**

The following code example shows how to read data from the Flash information area.

; get value at info address 60 (FE60h) ldx FPS, #%80 ; enable access to flash info page ld R0, #%FE ld R1, #%60 ldc R2, @RR0 ; R2 now contains the calibration value

# **Flash Option Bit Control Register Definitions**

This section briefly describes the features of the Trim Bit Address and Data registers.

# **Trim Bit Address Register**

The Trim Bit Address (TRMADR) Register contains the target address for an access to the trim option bits (Table 86).

| Bit     | 7   | 6                                     | 5 | 4  | 3  | 2 | 1 | 0 |

|---------|-----|---------------------------------------|---|----|----|---|---|---|

| Field   |     | TRMADR: Trim Bit Address (00H to 1FH) |   |    |    |   |   |   |

| RESET   | 0   | 0                                     | 0 | 0  | 0  | 0 | 0 | 0 |

| R/W     | R/W | R/W R/W R/W R/W R/W R/W R/W           |   |    |    |   |   |   |

| Address |     |                                       |   | FF | 6H |   |   |   |

Table 86. Trim Bit Address Register (TRMADR)

# **Temperature Sensor Calibration Data**

### Table 98. Temperature Sensor Calibration High Byte at 003A (TSCALH)

| Bit                                             | 7                            | 6      | 5   | 4   | 3   | 2   | 1   | 0   |

|-------------------------------------------------|------------------------------|--------|-----|-----|-----|-----|-----|-----|

| Field                                           |                              | TSCALH |     |     |     |     |     |     |

| RESET                                           | U                            | U      | U   | U   | U   | U   | U   | U   |

| R/W                                             | R/W                          | R/W    | R/W | R/W | R/W | R/W | R/W | R/W |

| Address                                         | Information Page Memory 003A |        |     |     |     |     |     |     |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                              |        |     |     |     |     |     |     |

#### Bit Description [7:0] **Temperature Sensor Calibration High Byte** TSCALH The TSCALH and TSCALL bytes combine to form the 12-bit temperature sensor offset calibra-

tion value. For more details, see Temperature Sensor Operation on page 139.

### Table 99. Temperature Sensor Calibration Low Byte at 003B (TSCALL)

| Bit       | 7                                               | 6      | 5   | 4   | 3   | 2   | 1   | 0   |

|-----------|-------------------------------------------------|--------|-----|-----|-----|-----|-----|-----|

| Field     |                                                 | TSCALL |     |     |     |     |     |     |

| RESET     | U                                               | U      | U   | U   | U   | U   | U   | U   |

| R/W       | R/W                                             | R/W    | R/W | R/W | R/W | R/W | R/W | R/W |

| Address   | Information Page Memory 003B                    |        |     |     |     |     |     |     |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |        |     |     |     |     |     |     |

#### Bit Description

| [7:0]  | Temperature Sensor Calibration Low Byte                                                   |

|--------|-------------------------------------------------------------------------------------------|

| TSCALL | The TSCALH and TSCALL bytes combine to form the 12-bit temperature sensor offset calibra- |

|        | tion value. For usage details, see the Temperature Sensor Operation section on page 144.  |

| Notation | Description    | Operand | Range                                                                                                                     |

|----------|----------------|---------|---------------------------------------------------------------------------------------------------------------------------|

| Vector   | Vector address | Vector  | Vector represents a number in the range of 00H to FFH.                                                                    |

| Х        | Indexed        | #Index  | The register or register pair to be indexed is off-<br>set by the signed Index value (#Index) in a +127<br>to –128 range. |

#### Table 118. Notational Shorthand (Continued)

Table 119 lists additional symbols that are used throughout the Instruction Summary and Instruction Set Description sections.

| Symbol | Definition                |

|--------|---------------------------|

| dst    | Destination Operand       |

| src    | Source Operand            |

| @      | Indirect Address Prefix   |

| SP     | Stack Pointer             |

| PC     | Program Counter           |

| FLAGS  | Flags Register            |

| RP     | Register Pointer          |

| #      | Immediate Operand Prefix  |

| В      | Binary Number Suffix      |

| %      | Hexadecimal Number Prefix |

| Н      | Hexadecimal Number Suffix |

|        |                           |

Table 119. Additional Symbols

Assignment of a value is indicated by an arrow, as shown in the following example.

$dst \leftarrow dst + src$

This example indicates that the source data is added to the destination data; the result is stored in the destination location.

# eZ8 CPU Instruction Classes

eZ8 CPU instructions can be divided functionally into the following groups:

- Arithmetic

- Bit Manipulation

| Assembly         |                                                                                           | Address<br>Mode |     | _ Opcode(s) | Flags |   |   |   |   |   | Fetch<br>Cycle | Instr.<br>Cycle |

|------------------|-------------------------------------------------------------------------------------------|-----------------|-----|-------------|-------|---|---|---|---|---|----------------|-----------------|

| Mnemonic         | Symbolic Operation                                                                        | dst             | src | (Hex)       | С     | Ζ | S | V | D | Н | S              | S               |

| AND dst, src     | $dst \gets dst \ AND \ src$                                                               | r               | r   | 52          | _     | * | * | 0 | _ | _ | 2              | 3               |

|                  |                                                                                           | r               | Ir  | 53          |       |   |   |   |   |   | 2              | 4               |

|                  |                                                                                           | R               | R   | 54          |       |   |   |   |   |   | 3              | 3               |

|                  |                                                                                           | R               | IR  | 55          |       |   |   |   |   |   | 3              | 4               |

|                  |                                                                                           | R               | IM  | 56          |       |   |   |   |   |   | 3              | 3               |

|                  |                                                                                           | IR              | IM  | 57          |       |   |   |   |   |   | 3              | 4               |

| ANDX dst, src    | $dst \gets dst \ AND \ src$                                                               | ER              | ER  | 58          | -     | * | * | 0 | - | - | 4              | 3               |

|                  |                                                                                           | ER              | IM  | 59          |       |   |   |   |   |   | 4              | 3               |

| ATM              | Block all interrupt and<br>DMA requests during<br>execution of the next<br>3 instructions |                 |     | 2F          | -     | - | _ | _ | _ | _ | 1              | 2               |

| BCLR bit, dst    | dst[bit] ← 0                                                                              | r               |     | E2          | -     | _ | _ | _ | _ | _ | 2              | 2               |

| BIT p, bit, dst  | dst[bit] ← p                                                                              | r               |     | E2          | -     | _ | - | - | - | - | 2              | 2               |

| BRK              | Debugger Break                                                                            |                 |     | 00          | -     | _ | - | - | - | - | 1              | 1               |

| BSET bit, dst    | dst[bit] ← 1                                                                              | r               |     | E2          | -     | _ | - | - | - | - | 2              | 2               |

| BSWAP dst        | $dst[7:0] \leftarrow dst[0:7]$                                                            | R               |     | D5          | Х     | * | * | 0 | - | - | 2              | 2               |

| BTJ p, bit, src, | if src[bit] = p                                                                           |                 | r   | F6          | -     | _ | - | - | - | - | 3              | 3               |

| dst              | $PC \leftarrow PC + X$                                                                    |                 | lr  | F7          |       |   |   |   |   |   | 3              | 4               |

| BTJNZ bit, src,  | if src[bit] = 1                                                                           |                 | r   | F6          | -     | _ | - | - | - | - | 3              | 3               |

| dst              | $PC \leftarrow PC + X$                                                                    |                 | lr  | F7          |       |   |   |   |   |   | 3              | 4               |

| BTJZ bit, src,   | if src[bit] = 0                                                                           |                 | r   | F6          | -     | _ | - | - | - | - | 3              | 3               |

| dst              | $PC \leftarrow PC + X$                                                                    |                 | lr  | F7          |       |   |   |   |   |   | 3              | 4               |

### Table 128. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

### Z8 Encore! XP<sup>®</sup> F082A Series **Product Specification**

|   |             |             |                    |                  |                     |                | Lo                                     | ower Nil                               | ble (He         | x)               |              |            |             |             |           |             |

|---|-------------|-------------|--------------------|------------------|---------------------|----------------|----------------------------------------|----------------------------------------|-----------------|------------------|--------------|------------|-------------|-------------|-----------|-------------|

|   | 0           | 1           | 2                  | 3                | 4                   | 5              | 6                                      | 7                                      | 8               | 9                | А            | В          | С           | D           | Е         | F           |

|   | 1.1         | 2.2         | 2.3                | 2.4              | 3.3                 | 3.4            | 3.3                                    | 3.4                                    | 4.3             | 4.3              | 2.3          | 2.2        | 2.2         | 3.2         | 1.2       | 1.2         |

| 0 | BRK         | SRP<br>IM   | ADD<br>r1,r2       | ADD<br>r1,lr2    | <b>ADD</b><br>R2,R1 | ADD<br>IR2,R1  | ADD<br>R1,IM                           | ADD<br>IR1,IM                          | ADDX<br>ER2,ER1 | ADDX<br>IM,ER1   | DJNZ<br>r1,X | JR<br>cc,X | LD<br>r1,IM | JP<br>cc,DA | INC<br>r1 | NOP         |

|   | 2.2         | 2.3         | 2.3                | 2.4              | 3.3                 | 3.4            | 3.3                                    | 3.4                                    | 4.3             | 4.3              | 11,∧         | UU, A      | 11,111      | CC,DA       |           | See 2nd     |

| 1 | RLC         | RLC         | ADC                | ADC              | ADC                 | ADC            | ADC                                    | ADC                                    | ADCX            |                  |              |            |             |             |           | Opcode      |

|   | R1          | IR1         | r1,r2              | r1,lr2           | R2,R1               | IR2,R1         | R1,IM                                  | IR1,IM                                 | ER2,ER1         | IM,ER1           |              |            |             |             |           | Мар         |

| - | 2.2         | 2.3         | 2.3                | 2.4              | 3.3                 | 3.4            | 3.3                                    | 3.4                                    | 4.3             | 4.3              |              |            |             |             |           | 1           |

| 2 | INC<br>R1   | INC<br>IR1  | SUB<br>r1,r2       | SUB<br>r1,lr2    | <b>SUB</b><br>R2,R1 | SUB<br>IR2,R1  | SUB<br>R1,IM                           | SUB<br>IR1,IM                          | SUBX<br>ER2,ER1 | SUBX<br>IM,ER1   |              |            |             |             |           | _           |

|   | 2.2         | 2.3         | 2.3                | 2.4              | 3.3                 | 3.4            | 3.3                                    | 3.4                                    | 4.3             | 4.3              |              |            |             |             |           |             |

| 3 | DEC         | DEC         | SBC                | SBC              | SBC                 | SBC            | SBC                                    | SBC                                    | SBCX            | SBCX             |              |            |             |             |           |             |

|   | R1          | IR1         | r1,r2              | r1,lr2           | R2,R1               | IR2,R1         | R1,IM                                  | IR1,IM                                 | ER2,ER1         | IM,ER1           |              |            |             |             |           |             |

|   | 2.2         | 2.3         | 2.3                | 2.4              | 3.3                 | 3.4            | 3.3                                    | 3.4                                    | 4.3             | 4.3              |              |            |             |             |           |             |

| 4 | DA<br>R1    | DA<br>IR1   | OR<br>r1,r2        | OR<br>r1,lr2     | <b>OR</b><br>R2,R1  | OR<br>IR2,R1   | OR<br>R1,IM                            | OR<br>IR1,IM                           | ORX<br>ER2,ER1  | ORX<br>IM,ER1    |              |            |             |             |           |             |

|   | 2.2         | 2.3         | 2.3                | 2.4              | 3.3                 | 3.4            | 3.3                                    | 3.4                                    | 4.3             | 4.3              |              |            |             |             |           | 1.2         |

| 5 | POP         | POP         | AND                | AND              | AND                 | AND            | AND                                    | AND                                    | ANDX            | ANDX             |              |            |             |             |           | WDT         |

|   | R1          | IR1         | r1,r2              | r1,lr2           | R2,R1               | IR2,R1         | R1,IM                                  | IR1,IM                                 | ER2,ER1         |                  |              |            |             |             |           |             |

| 6 | 2.2<br>COM  | 2.3<br>COM  | 2.3<br>TCM         | 2.4<br>TCM       | 3.3<br>TCM          | 3.4<br>TCM     | 3.3<br>TCM                             | 3.4<br>TCM                             | 4.3<br>TCMX     | 4.3<br>TCMX      |              |            |             |             |           | 1.2<br>STOP |

| 0 | R1          | IR1         | r1,r2              | r1,lr2           | R2,R1               | IR2,R1         | R1,IM                                  | IR1,IM                                 | ER2,ER1         | IM,ER1           |              |            |             |             |           | 3105        |

|   | 2.2         | 2.3         | 2.3                | 2.4              | 3.3                 | 3.4            | 3.3                                    | 3.4                                    | 4.3             | 4.3              |              |            |             |             |           | 1.2         |

| 7 | PUSH        | PUSH        | тм                 | тм               | тм                  | тм             | тм                                     | тм                                     | тмх             | тмх              |              |            |             |             |           | HALT        |

|   | R2          | IR2         | r1,r2              | r1,lr2           | R2,R1               | IR2,R1         | R1,IM                                  | IR1,IM                                 | ER2,ER1         | IM,ER1           |              |            |             |             |           |             |

| 8 | 2.5<br>DECW | 2.6<br>DECW | 2.5<br>LDE         | 2.9<br>LDEI      | 3.2<br>LDX          | 3.3<br>LDX     | 3.4<br>LDX                             | 3.5<br><b>LDX</b>                      | 3.4<br>LDX      | 3.4<br>LDX       |              |            |             |             |           | 1.2<br>DI   |

| 0 | RR1         | IRR1        | r1,Irr2            | lr1,lrr2         | r1,ER2              | Ir1,ER2        | IRR2,R1                                | IRR2,IR1                               | r1,rr2,X        | rr1,r2,X         |              |            |             |             |           | 5.          |

|   | 2.2         | 2.3         | 2.5                | 2.9              | 3.2                 | 3.3            | 3.4                                    | 3.5                                    | 3.3             | 3.5              |              |            |             |             |           | 1.2         |

| 9 | RL          | RL          | LDE                | LDEI             | LDX                 | LDX            | LDX                                    | LDX                                    | LEA             | LEA              |              |            |             |             |           | EI          |

|   | R1<br>2.5   | IR1<br>2.6  | r2,Irr1<br>2.3     | lr2,Irr1<br>2.4  | r2,ER1<br>3.3       | Ir2,ER1<br>3.4 | R2,IRR1<br>3.3                         | IR2,IRR1<br>3.4                        | r1,r2,X<br>4.3  | rr1,rr2,X<br>4.3 |              |            |             |             |           | 1.4         |

| А | INCW        | INCW        | CP                 | CP               | CP                  | 3.4<br>CP      | CP                                     | 3.4<br>CP                              | CPX             | CPX              |              |            |             |             |           | RET         |

|   | RR1         | IRR1        | r1,r2              | r1,lr2           | R2,R1               | IR2,R1         | R1,IM                                  | IR1,IM                                 | ER2,ER1         | IM,ER1           |              |            |             |             |           |             |

| _ | 2.2         | 2.3         | 2.3                | 2.4              | 3.3                 | 3.4            | 3.3                                    | 3.4                                    | 4.3             | 4.3              |              |            |             |             |           | 1.5         |

| В | CLR<br>R1   | IR1         | XOR<br>r1,r2       | XOR              | <b>XOR</b><br>R2,R1 | XOR<br>IR2,R1  | XOR<br>R1,IM                           | XOR<br>IR1,IM                          | XORX<br>ER2,ER1 | XORX<br>IM,ER1   |              |            |             |             |           | IRET        |

|   | 2.2         | 2.3         | 2.5                | r1,lr2<br>2.9    | 2.3                 | 2.9            | K I,IIVI                               | 3.4                                    | 3.2             | IIVI,EKI         |              |            |             |             |           | 1.2         |

| С | RRC         | RRC         | LDC                | LDCI             | JP                  | LDC            |                                        | LD                                     | PUSHX           |                  |              |            |             |             |           | RCF         |

|   | R1          | IR1         | r1,Irr2            | lr1,lrr2         | IRR1                | lr1,lrr2       |                                        | r1,r2,X                                | ER2             |                  |              |            |             |             |           |             |

| - | 2.2         | 2.3         | 2.5                | 2.9              | 2.6                 | 2.2            | 3.3                                    | 3.4                                    | 3.2             |                  |              |            |             |             |           | 1.2         |

| D | SRA<br>R1   | SRA<br>IR1  | LDC<br>r2,Irr1     | LDCI<br>Ir2,Irr1 | CALL<br>IRR1        | BSWAP<br>R1    | DA                                     | LD<br>r2,r1,X                          | POPX<br>ER1     |                  |              |            |             |             |           | SCF         |

|   | 2.2         | 2.3         | 2.2                | 2.3              | 3.2                 | 3.3            | 3.2                                    | 3.3                                    | 4.2             | 4.2              |              |            |             |             |           | 1.2         |

| Е | RR          | RR          | BIT                | LD               | LD                  | LD             | LD                                     | LD                                     | LDX             | LDX              |              |            |             |             | i I       | CCF         |

|   | R1          | IR1         | p,b,r1             | r1,lr2           | R2,R1               | IR2,R1         | R1,IM                                  |                                        | ER2,ER1         | IM,ER1           |              |            |             |             |           |             |

| - | 2.2<br>SWAP | 2.3<br>SWAP | 2.6<br><b>TRAP</b> | 2.3<br>LD        | 2.8<br>MULT         | 3.3<br>LD      | 3.3<br><b>BTJ</b>                      | 3.4<br><b>BTJ</b>                      |                 |                  |              | <b>_</b>   |             |             |           |             |

| F | R1          | IR1         | Vector             | LD<br>lr1,r2     | RR1                 | LD<br>R2,IR1   | BIJ<br>p,b,r1,X                        |                                        |                 |                  | V            |            |             |             |           |             |

|   | 131         |             | 100101             |                  | 13131               |                | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                 |                  | -            |            |             |             |           |             |

Lower Nibble (Hex)

Figure 31. First Opcode Map

|                   |                                       |         | -40°C to +<br>otherwise s |            |       |                                                                                 |

|-------------------|---------------------------------------|---------|---------------------------|------------|-------|---------------------------------------------------------------------------------|

| Symbol            | Parameter                             | Minimum | Typical                   | Maximum    | Units | Conditions                                                                      |

| V <sub>OH1</sub>  | High Level Output<br>Voltage          | 2.4     | -                         | -          | V     | I <sub>OH</sub> = -2 mA; V <sub>DD</sub> = 3.0 V<br>High Output Drive disabled. |

| V <sub>OL2</sub>  | Low Level Output<br>Voltage           | _       | -                         | 0.6        | V     | $I_{OL} = 20 \text{ mA}; V_{DD} = 3.3 \text{ V}$<br>High Output Drive enabled.  |

| V <sub>OH2</sub>  | High Level Output<br>Voltage          | 2.4     | _                         | _          | V     | I <sub>OH</sub> = -20 mA; V <sub>DD</sub> = 3.3V<br>High Output Drive enabled.  |

| I <sub>IH</sub>   | Input Leakage Cur-<br>rent            | -       | <u>+</u> 0.002            | <u>+</u> 5 | μA    | $V_{IN} = V_{DD}$<br>$V_{DD} = 3.3 V;$                                          |

| IIL               | Input Leakage Cur-<br>rent            | -       | <u>+</u> 0.007            | <u>+</u> 5 | μA    | $V_{IN} = V_{SS}$<br>$V_{DD} = 3.3V;$                                           |

| I <sub>TL</sub>   | Tristate Leakage<br>Current           | -       | -                         | <u>+</u> 5 | μA    |                                                                                 |

| I <sub>LED</sub>  | Controlled Current                    | 1.8     | 3                         | 4.5        | mA    | $\{AFS2, AFS1\} = \{0, 0\}$                                                     |

|                   | Drive                                 | 2.8     | 7                         | 10.5       | mA    | $\{AFS2, AFS1\} = \{0, 1\}$                                                     |

|                   |                                       | 7.8     | 13                        | 19.5       | mA    | ${AFS2,AFS1} = {1,0}$                                                           |

|                   |                                       | 12      | 20                        | 30         | mA    | ${AFS2,AFS1} = {1,1}$                                                           |

| C <sub>PAD</sub>  | GPIO Port Pad<br>Capacitance          | -       | 8.0 <sup>2</sup>          | -          | pF    |                                                                                 |

| C <sub>XIN</sub>  | XIN Pad Capaci-<br>tance              | -       | 8.0 <sup>2</sup>          | -          | pF    |                                                                                 |

| C <sub>XOUT</sub> | X <sub>OUT</sub> Pad Capaci-<br>tance | -       | 9.5 <sup>2</sup>          | _          | pF    |                                                                                 |

| I <sub>PU</sub>   | Weak Pull-up Cur-<br>rent             | 30      | 100                       | 350        | μA    | V <sub>DD</sub> = 3.0 V–3.6 V                                                   |

| V <sub>RAM</sub>  | RAM Data Reten-<br>tion Voltage       | TBD     |                           |            | V     | Voltage at which RAM retains static values; no reading or writing is allowed.   |

### Table 131. DC Characteristics (Continued)

Notes:

1. This condition excludes all pins that have on-chip pull-ups, when driven Low.

2. These values are provided for design guidance only and are not tested in production.

|                    |                                               |         | o = 2.7 V to<br>−40°C to |                    |       |                                 |  |

|--------------------|-----------------------------------------------|---------|--------------------------|--------------------|-------|---------------------------------|--|

| Symbol             | Parameter                                     | Minimum | Typical                  | Maximum            | Units | Conditions                      |  |

| Av                 | Open loop voltage gain                        |         | 80                       |                    | dB    |                                 |  |

| GBW                | Gain/Bandwidth product                        |         | 500                      |                    | kHz   |                                 |  |

| РМ                 | Phase Margin                                  |         | 50                       |                    | deg   | Assuming 13pF load capacitance. |  |

| V <sub>osLPO</sub> | Input Offset Voltage                          |         | <u>+</u> 1               | <u>+</u> 4         | mV    |                                 |  |

| V <sub>osLPO</sub> | Input Offset Voltage (Tem-<br>perature Drift) |         | 1                        | 10                 | μV/C  |                                 |  |

| V <sub>IN</sub>    | Input Voltage Range                           | 0.3     |                          | V <sub>DD</sub> -1 | V     |                                 |  |

| V <sub>OUT</sub>   | Output Voltage Range                          | 0.3     |                          | V <sub>DD</sub> -1 | V     | Ι <sub>ΟUT</sub> = 45μΑ.        |  |

### Table 140. Low Power Operational Amplifier Electrical Characteristics

### Table 141. Comparator Electrical Characteristics

|                   |                                            |                 | = 2.7 V to<br>-40°C to + |                    |       |                         |

|-------------------|--------------------------------------------|-----------------|--------------------------|--------------------|-------|-------------------------|

| Symbol            | Parameter                                  | Minimum         | Typical                  | Maximum            | Units | Conditions              |

| V <sub>OS</sub>   | Input DC Offset                            |                 | 5                        |                    | mV    |                         |

| V <sub>CREF</sub> | Programmable Internal<br>Reference Voltage |                 | <u>+</u> 5               |                    | %     | 20- and 28-pin devices. |

|                   |                                            |                 | <u>+</u> 3               |                    | %     | 8-pin devices.          |

| T <sub>PROP</sub> | Propagation Delay                          |                 | 200                      |                    | ns    |                         |

| V <sub>HYS</sub>  | Input Hysteresis                           |                 | 4                        |                    | mV    |                         |

| V <sub>IN</sub>   | Input Voltage Range                        | V <sub>SS</sub> |                          | V <sub>DD</sub> -1 | V     |                         |