# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 17                                                           |

| Program Memory Size        | 2KB (2K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 64 x 8                                                       |

| RAM Size                   | 512 x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 7x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 105°C (TA)                                           |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                               |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f022ash020eg    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

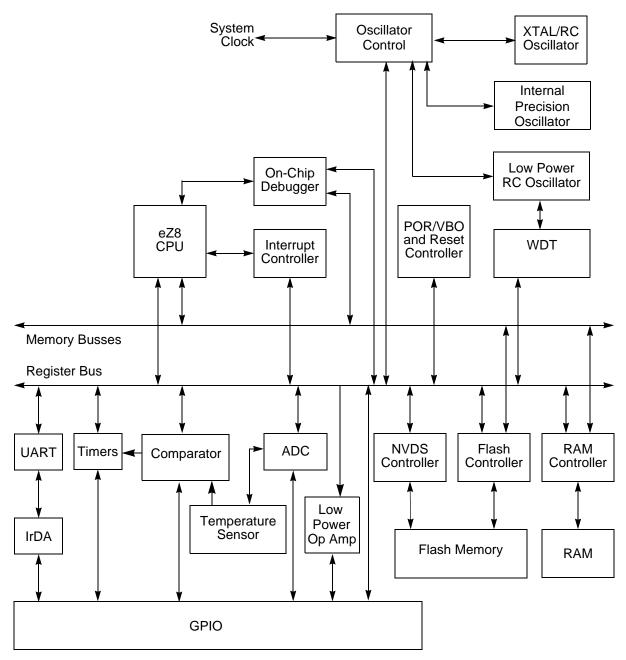

# **Block Diagram**

Figure 1 displays the block diagram of the architecture of the Z8 Encore! XP F082A Series devices.

7

warning signal. The  $\overline{\text{RESET}}$  pin is bidirectional, that is, it functions as reset source and as a reset indicator.

| Address (Hex)    | Register Description                 | Mnemonic      | Reset (Hex) | Page       |

|------------------|--------------------------------------|---------------|-------------|------------|

| Timer 1          |                                      |               |             |            |

| F08              | Timer 1 High Byte                    | T1H           | 00          | <u>90</u>  |

| F09              | Timer 1 Low Byte                     | T1L           | 01          | <u>90</u>  |

| F0A              | Timer 1 Reload High Byte             | T1RH          | FF          | <u>91</u>  |

| Timer 1 (cont'd) |                                      |               |             |            |

| F0B              | Timer 1 Reload Low Byte              | T1RL          | FF          | <u>91</u>  |

| F0C              | Timer 1 PWM High Byte                | T1PWMH        | 00          | <u>92</u>  |

| F0D              | Timer 1 PWM Low Byte                 | T1PWML        | 00          | <u>92</u>  |

| F0E              | Timer 1 Control 0                    | T1CTL0        | 00          | <u>85</u>  |

| F0F              | Timer 1 Control 1                    | T1CTL1        | 00          | <u>86</u>  |

| F10–F6F          | Reserved                             | —             | XX          |            |

| UART             |                                      |               |             |            |

| F40              | UART Transmit/Receive Data registers | TXD, RXD      | XX          | <u>115</u> |

| F41              | UART Status 0 Register               | U0STAT0       | 00          | <u>114</u> |

| F42              | UART Control 0 Register              | U0CTL0        | 00          | <u>110</u> |

| F43              | UART Control 1 Register              | U0CTL1        | 00          | <u>110</u> |

| F44              | UART Status 1 Register               | U0STAT1       | 00          | <u>115</u> |

| F45              | UART Address Compare Register        | <b>U0ADDR</b> | 00          | <u>116</u> |

| F46              | UART Baud Rate High Byte Register    | U0BRH         | FF          | <u>117</u> |

| F47              | UART Baud Rate Low Byte Register     | U0BRL         | FF          | <u>117</u> |

| Analog-to-Digita | al Converter (ADC)                   |               |             |            |

| F70              | ADC Control 0                        | ADCCTL0       | 00          | <u>134</u> |

| F71              | ADC Control 1                        | ADCCTL1       | 80          | <u>136</u> |

| F72              | ADC Data High Byte                   | ADCD_H        | XX          | <u>137</u> |

| F73              | ADC Data Low Byte                    | ADCD_L        | XX          | 137        |

| F74–F7F          | Reserved                             |               | XX          |            |

| Low Power Con    | trol                                 |               |             |            |

| F80              | Power Control 0                      | PWRCTL0       | 80          | <u>34</u>  |

| F81              | Reserved                             | —             | XX          |            |

| LED Controller   |                                      |               |             |            |

| F82              | LED Drive Enable                     | LEDEN         | 00          | <u>53</u>  |

| F83              | LED Drive Level High Byte            | LEDLVLH       | 00          | <u>53</u>  |

| F84              | LED Drive Level Low Byte             | LEDLVLL       | 00          | <u>54</u>  |

### Table 7. Register File Address Map (Continued)

1. XX = Undefined.

2. Refer to the eZ8 CPU Core User Manual (UM0128).

| Address (Hex)           | Register Description    | Mnemonic | Reset (Hex) | Page       |

|-------------------------|-------------------------|----------|-------------|------------|

| F85                     | Reserved                | —        | XX          |            |

| <b>Oscillator Contr</b> | ol                      |          |             |            |

| F86                     | Oscillator Control      | OSCCTL   | A0          | <u>196</u> |

| F87–F8F                 | Reserved                | _        | XX          |            |

| Comparator 0            |                         |          |             |            |

| F90                     | Comparator 0 Control    | CMP0     | 14          | <u>141</u> |

| F91–FBF                 | Reserved                | —        | XX          |            |

| Interrupt Contro        | oller                   |          |             |            |

| FC0                     | Interrupt Request 0     | IRQ0     | 00          | <u>60</u>  |

| FC1                     | IRQ0 Enable High Bit    | IRQ0ENH  | 00          | <u>63</u>  |

| FC2                     | IRQ0 Enable Low Bit     | IRQ0ENL  | 00          | <u>63</u>  |

| FC3                     | Interrupt Request 1     | IRQ1     | 00          | <u>61</u>  |

| FC4                     | IRQ1 Enable High Bit    | IRQ1ENH  | 00          | <u>65</u>  |

| FC5                     | IRQ1 Enable Low Bit     | IRQ1ENL  | 00          | <u>65</u>  |

| FC6                     | Interrupt Request 2     | IRQ2     | 00          | <u>62</u>  |

| FC7                     | IRQ2 Enable High Bit    | IRQ2ENH  | 00          | <u>66</u>  |

| FC8                     | IRQ2 Enable Low Bit     | IRQ2ENL  | 00          | <u>67</u>  |

| FC9–FCC                 | Reserved                | —        | XX          |            |

| FCD                     | Interrupt Edge Select   | IRQES    | 00          | <u>68</u>  |

| FCE                     | Shared Interrupt Select | IRQSS    | 00          | <u>68</u>  |

| FCF                     | Interrupt Control       | IRQCTL   | 00          | <u>69</u>  |

| GPIO Port A             |                         |          |             |            |

| FD0                     | Port A Address          | PAADDR   | 00          | <u>44</u>  |

| FD1                     | Port A Control          | PACTL    | 00          | <u>46</u>  |

| FD2                     | Port A Input Data       | PAIN     | XX          | <u>46</u>  |

| FD3                     | Port A Output Data      | PAOUT    | 00          | <u>46</u>  |

| GPIO Port B             |                         |          |             |            |

| FD4                     | Port B Address          | PBADDR   | 00          | <u>44</u>  |

| FD5                     | Port B Control          | PBCTL    | 00          | <u>46</u>  |

| FD6                     | Port B Input Data       | PBIN     | XX          | <u>46</u>  |

| FD7                     | Port B Output Data      | PBOUT    | 00          | <u>46</u>  |

| GPIO Port C             |                         |          |             |            |

| FD8                     | Port C Address          | PCADDR   | 00          | 44         |

### Table 7. Register File Address Map (Continued)

1. XX = Undefined.

2. Refer to the eZ8 CPU Core User Manual (UM0128).

# HALT Mode

Executing the eZ8 CPU's HALT instruction places the device into HALT Mode, which powers down the CPU but leaves all other peripherals active. In HALT Mode, the operating characteristics are:

- Primary oscillator is enabled and continues to operate

- System clock is enabled and continues to operate

- eZ8 CPU is stopped

- Program counter (PC) stops incrementing

- Watchdog Timer's internal RC oscillator continues to operate

- If enabled, the Watchdog Timer continues to operate

- All other on-chip peripherals continue to operate, if enabled

The eZ8 CPU can be brought out of HALT Mode by any of the following operations:

- Interrupt

- Watchdog Timer time-out (interrupt or reset)

- Power-On Reset

- Voltage Brown-Out reset

- External **RESET** pin assertion

To minimize current in HALT Mode, all GPIO pins that are configured as inputs must be driven to one of the supply rails ( $V_{CC}$  or GND).

# **Peripheral-Level Power Control**

In addition to the STOP and HALT modes, it is possible to disable each peripheral on each of the Z8 Encore! XP F082A Series devices. Disabling a given peripheral minimizes its power consumption.

# **Power Control Register Definitions**

The following sections define the Power Control registers.

### **Power Control Register 0**

Each bit of the following registers disables a peripheral block, either by gating its system clock input or by removing power from the block. The default state of the low-power

# **LED Drive Enable Register**

The LED Drive Enable Register, shown in Table 31, activates the controlled current drive. The Alternate Function Register has no control over the LED function; therefore, setting the Alternate Function Register to select the LED function is not required. LEDEN bits [7:0] correspond to Port C bits [7:0], respectively.

| Bit     | 7   | 6          | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|---------|-----|------------|-----|-----|-----|-----|-----|-----|--|--|

| Field   |     | LEDEN[7:0] |     |     |     |     |     |     |  |  |

| RESET   | 0   | 0          | 0   | 0   | 0   | 0   | 0   | 0   |  |  |

| R/W     | R/W | R/W        | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Address |     |            |     | F8  | 2H  |     |     |     |  |  |

| Table 31. LED Drive Enable | (LEDEN) |

|----------------------------|---------|

|                            | ,       |

#### Bit Description

[7:0] LED Drive Enable

LEDENx These bits determine which Port C pins are connected to an internal current sink.

0 = Tristate the Port C pin.

1 = Enable controlled current sink on the Port C pin.

**Note:** *x* indicates the specific GPIO port pin number (7–0).

# LED Drive Level High Register

The LED Drive Level registers contain two control bits for each Port C pin, as shown in Table 32. These two bits select between four programmable drive levels. Each pin is individually programmable.

| Bit               | 7       | 6                                                                                                                                     | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

|-------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|--|--|--|

| Field             |         | LEDLVLH[7:0]                                                                                                                          |     |     |     |     |     |     |  |  |  |

| RESET             | 0       | 0 0 0 0 0 0 0 0                                                                                                                       |     |     |     |     |     |     |  |  |  |

| R/W               | R/W     | R/W                                                                                                                                   | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |

| Address           |         | -                                                                                                                                     |     | F8  | 3H  |     |     |     |  |  |  |

| Bit               | Descrip | tion                                                                                                                                  |     |     |     |     |     |     |  |  |  |

| [7:0]<br>LEDLVLH> | (LEDLVL | <b>LED Level High Bit</b><br>{LEDLVLH, LEDLVLL} select one of four programmable current drive levels for each Port C pin.<br>00 = 3mA |     |     |     |     |     |     |  |  |  |

| Table 32. LED | Drive Level | <b>High Register</b> | (LEDLVLH) |

|---------------|-------------|----------------------|-----------|

|               |             | ingii itogiotoi      |           |

01 = 7mA 10 = 13mA

11 = 20 mA

Note: x indicates the specific GPIO port pin number (7–0).

### **Shared Interrupt Select Register**

The Shared Interrupt Select (IRQSS) Register, shown in Table 48, determines the source of the PADxS interrupts. The Shared Interrupt Select Register selects between Port A and alternate sources for the individual interrupts.

Because these shared interrupts are edge-triggered, it is possible to generate an interrupt just by switching from one shared source to another. For this reason, an interrupt must be disabled before switching between sources.

| Bit          | 7                                                                                                                                                                                                       | 6                    | 5                               | 4   | 3   | 2   | 1   | 0   |  |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------------------------|-----|-----|-----|-----|-----|--|--|--|

| Field        | PA7VS                                                                                                                                                                                                   | PA7VS PA6CS Reserved |                                 |     |     |     |     |     |  |  |  |

| RESET        | 0                                                                                                                                                                                                       | 0 0 0 0 0 0 0 0      |                                 |     |     |     |     |     |  |  |  |

| R/W          | R/W                                                                                                                                                                                                     | R/W                  | R/W                             | R/W | R/W | R/W | R/W | R/W |  |  |  |

| Address      |                                                                                                                                                                                                         |                      |                                 | FC  | EH  |     |     |     |  |  |  |

| Bit          | Description                                                                                                                                                                                             |                      |                                 |     |     |     |     |     |  |  |  |

| [7]<br>PA7VS |                                                                                                                                                                                                         | used for the         | interrupt for<br>r the interrup |     |     |     |     |     |  |  |  |

| [6]<br>PA6CS | <ul> <li>PA6/Comparator Selection</li> <li>0 = PA6 is used for the interrupt for PA6CS interrupt request.</li> <li>1 = The Comparator is used for the interrupt for PA6CS interrupt request.</li> </ul> |                      |                                 |     |     |     |     |     |  |  |  |

| [5:0]        | Reserved                                                                                                                                                                                                | Reserved             |                                 |     |     |     |     |     |  |  |  |

#### Table 48. Shared Interrupt Select Register (IRQSS)

These bits are reserved and must be programmed to 000000.

### **Interrupt Control Register**

The Interrupt Control (IRQCTL) Register, shown in Table 49, contains the master enable bit for all interrupts.

| Bit     | 7             | 6                        | 5            | 4             | 3             | 2            | 1           | 0            |  |  |

|---------|---------------|--------------------------|--------------|---------------|---------------|--------------|-------------|--------------|--|--|

| Field   | IRQE          |                          | Reserved     |               |               |              |             |              |  |  |

| RESET   | 0             | 0                        | 0            | 0             | 0             | 0            | 0           | 0            |  |  |

| R/W     | R/W           | R                        | R            | R             | R             | R            | R           | R            |  |  |

| Address |               |                          |              | FC            | FH            |              |             |              |  |  |

| Bit     | Descriptio    | n                        |              |               |               |              |             |              |  |  |

| [7]     | Interrupt R   | Interrupt Request Enable |              |               |               |              |             |              |  |  |

| IRQE    | This bit is s | et to 1 by ex            | ecuting an E | El (Enable Ir | nterrupts) or | IRET (Interr | upt Return) | instruction, |  |  |

### Table 49. Interrupt Control Register (IRQCTL)

| ЫІ    | Description                                                                                                                                                                                                                                                                                                                                    |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]   | Interrupt Request Enable                                                                                                                                                                                                                                                                                                                       |

| IRQE  | This bit is set to 1 by executing an EI (Enable Interrupts) or IRET (Interrupt Return) instruction, or by a direct register write of a 1 to this bit. It is reset to 0 by executing a DI instruction, eZ8 CPU acknowledgement of an interrupt request, Reset or by a direct register write of a 0 to this bit.<br>0 = Interrupts are disabled. |

|       | 1 = Interrupts are enabled.                                                                                                                                                                                                                                                                                                                    |

| [6:0] | <b>Reserved</b><br>These bits are reserved and must be programmed to 0000000.                                                                                                                                                                                                                                                                  |

|       |                                                                                                                                                                                                                                                                                                                                                |

#### Bit Description (Continued)

#### [6] Timer Input/Output Polarity

TPOL Operation of this bit is a function of the current operating mode of the timer.

#### **ONE-SHOT Mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### **CONTINUOUS Mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### **COUNTER Mode**

If the timer is enabled the Timer Output signal is complemented after timer reload.

- 0 = Count occurs on the rising edge of the Timer Input signal.

- 1 = Count occurs on the falling edge of the Timer Input signal.

#### PWM SINGLE OUTPUT Mode

- 0 = Timer Output is forced Low (0) when the timer is disabled. When enabled, the Timer Output is forced High (1) upon PWM count match and forced Low (0) upon reload.

- 1 = Timer Output is forced High (1) when the timer is disabled. When enabled, the Timer Output is forced Low (0) upon PWM count match and forced High (1) upon reload.

#### CAPTURE Mode

0 = Count is captured on the rising edge of the Timer Input signal.

1 = Count is captured on the falling edge of the Timer Input signal.

#### COMPARE Mode

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

### **WDT Reset in Normal Operation**

If configured to generate a Reset when a time-out occurs, the Watchdog Timer forces the device into the System Reset state. The WDT status bit in the Reset Status (RSTSTAT) Register is set to 1. For more information about system reset, see the <u>Reset, Stop Mode</u> <u>Recovery and Low Voltage Detection</u> chapter on page 22.

### WDT Reset in STOP Mode

If configured to generate a Reset when a time-out occurs and the device is in STOP Mode, the Watchdog Timer initiates a Stop Mode Recovery. Both the WDT status bit and the STOP bit in the Reset Status (RSTSTAT) Register are set to 1 following WDT time-out in STOP Mode.

### Watchdog Timer Reload Unlock Sequence

Writing the unlock sequence to the Watchdog Timer (WDTCTL) Control Register address unlocks the three Watchdog Timer Reload Byte registers (WDTU, WDTH and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL Register address produce no effect on the bits in the WDTCTL Register. The locking mechanism prevents spurious writes to the Reload registers. Observe the following steps to unlock the Watchdog Timer Reload Byte registers (WDTU, WDTH and WDTL) for write access.

- 1. Write 55H to the Watchdog Timer Control Register (WDTCTL).

- 2. Write AAH to the Watchdog Timer Control Register (WDTCTL).

- 3. Write the Watchdog Timer Reload Upper Byte Register (WDTU) with the appropriate time-out value.

- 4. Write the Watchdog Timer Reload High Byte Register (WDTH) with the appropriate time-out value.

- 5. Write the Watchdog Timer Reload Low Byte Register (WDTL) with the appropriate time-out value.

All three Watchdog Timer Reload registers must be written in the order just listed. There must be no other register writes between each of these operations. If a register write occurs, the lock state machine resets and no further writes can occur unless the sequence is restarted. The value in the Watchdog Timer Reload registers is loaded into the counter when the Watchdog Timer is first enabled and every time a WDT instruction is executed.

# Watchdog Timer Calibration

Due to its extremely low operating current, the Watchdog Timer oscillator is somewhat inaccurate. This variation can be corrected using the calibration data stored in the Flash Information Page; see Tables 100 and 101 on page 173 for details. Loading these values

PRELIMINARY

# **UART Status 0 Register**

The UART Status 0 (UxSTAT0) and Status 1(UxSTAT1) registers, shown in Tables 65 and 66, identify the current UART operating configuration and status.

| Table 65. | UART | Status 0 | Register | (U0STAT0) |

|-----------|------|----------|----------|-----------|

|-----------|------|----------|----------|-----------|

| Bit         | 7                                                                                                                                                                                                                                                                                                                    | 6                                                                                                                                                                                                                                                                        | 5                                     | 4  | 3           | 2    | 1                          | 0   |  |  |  |  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----|-------------|------|----------------------------|-----|--|--|--|--|

| Field       | RDA                                                                                                                                                                                                                                                                                                                  | PE                                                                                                                                                                                                                                                                       | OE                                    | FE | BRKD        | TDRE | TXE                        | CTS |  |  |  |  |

| RESET       | 0                                                                                                                                                                                                                                                                                                                    | 0                                                                                                                                                                                                                                                                        | 0                                     | 0  | 0           | 1    | 1                          | Х   |  |  |  |  |

| R/W         | R                                                                                                                                                                                                                                                                                                                    | R                                                                                                                                                                                                                                                                        | R                                     | R  | R           | R    | R                          | R   |  |  |  |  |

| Address     |                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                          |                                       | F4 | 1H          |      |                            |     |  |  |  |  |

| Bit         | Descriptio                                                                                                                                                                                                                                                                                                           | Description                                                                                                                                                                                                                                                              |                                       |    |             |      |                            |     |  |  |  |  |

| [7]<br>RDA  | This bit indi<br>Receive Da<br>0 = The UA                                                                                                                                                                                                                                                                            | Receive Data Available<br>This bit indicates that the UART Receive Data Register has received data. Reading the UART<br>Receive Data Register clears this bit.<br>0 = The UART Receive Data Register is empty.<br>1 = There is a byte in the UART Receive Data Register. |                                       |    |             |      |                            |     |  |  |  |  |

| [6]<br>PE   | Parity Error<br>This bit indicates that a parity error has occurred. Reading the UART Receive Data Register<br>clears this bit.<br>0 = No parity error has occurred.<br>1 = A parity error has occurred.                                                                                                             |                                                                                                                                                                                                                                                                          |                                       |    |             |      |                            |     |  |  |  |  |

| [5]<br>OE   | received an<br>reading the<br>0 = No over                                                                                                                                                                                                                                                                            | cates that a<br>d the UART<br>UART Rece<br>rrun error oc                                                                                                                                                                                                                 | Receive Da<br>eive Data Re<br>curred. |    | has not bee |      | s when new<br>e RDA bit is |     |  |  |  |  |

| [4]<br>FE   | <ul> <li>1 = An overrun error occurred.</li> <li>Framing Error This bit indicates that a framing error (no Stop bit following data reception) was detected. Reading the UART Receive Data Register clears this bit. 0 = No framing error occurred. 1 = A framing error occurred. </li> </ul>                         |                                                                                                                                                                                                                                                                          |                                       |    |             |      |                            |     |  |  |  |  |

| [3]<br>BRKD | <ul> <li>1 = A framing error occurred.</li> <li>Break Detect This bit indicates that a break occurred. If the data bits, parity/multiprocessor bit and Stop bit(s) are all 0s this bit is set to 1. Reading the UART Receive Data Register clears this bit. 0 = No break occurred. 1 = A break occurred. </li> </ul> |                                                                                                                                                                                                                                                                          |                                       |    |             |      |                            |     |  |  |  |  |

Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

125

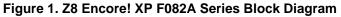

Figure 19. Analog-to-Digital Converter Block Diagram

# Operation

In both SINGLE-ENDED and DIFFERENTIAL modes, the effective output of the ADC is an 11-bit, signed, two's complement digital value. In DIFFERENTIAL Mode, the ADC can output values across the entire 11-bit range, from -1024 to +1023. In SINGLE-ENDED Mode, the output generally ranges from 0 to +1023, but offset errors can cause small negative values.

# Flash Option Bits

Programmable Flash option bits allow user configuration of certain aspects of Z8 Encore! XP F082A Series operation. The feature configuration data is stored in Flash program memory and loaded into holding registers during Reset. The features available for control through the Flash option bits include:

- Watchdog Timer time-out response selection-interrupt or system reset

- Watchdog Timer always on (enabled at Reset)

- The ability to prevent unwanted read access to user code in Program Memory

- The ability to prevent accidental programming and erasure of all or a portion of the user code in Program Memory

- Voltage Brown-Out configuration-always enabled or disabled during STOP Mode to reduce STOP Mode power consumption

- Oscillator mode selection-for high, medium and low power crystal oscillators, or external RC oscillator

- Factory trimming information for the internal precision oscillator and low voltage detection

- Factory calibration values for ADC, temperature sensor and Watchdog Timer compensation

- Factory serialization and randomized lot identifier (optional)

# Operation

This section describes the type and configuration of the programmable Flash option bits.

### **Option Bit Configuration By Reset**

Each time the Flash option bits are programmed or erased, the device must be Reset for the change to take effect. During any reset operation (System Reset, Power-On Reset, or Stop Mode Recovery), the Flash option bits are automatically read from Flash program memory and written to the Option Configuration registers. The Option Configuration registers control the operation of the devices within the Z8 Encore! XP F082A Series. Option bit control is established before the device exits Reset and the eZ8 CPU begins code execution. The Option Configuration registers are not part of the Register File and are not accessible for read or write access.

| Operation              | Minimum<br>Latency | Maximum<br>Latency |

|------------------------|--------------------|--------------------|

| Read (16 byte array)   | 875                | 9961               |

| Read (64 byte array)   | 876                | 8952               |

| Read (128 byte array)  | 883                | 7609               |

| Write (16 byte array)  | 4973               | 5009               |

| Write (64 byte array)  | 4971               | 5013               |

| Write (128 byte array) | 4984               | 5023               |

| Illegal Read           | 43                 | 43                 |

| Illegal Write          | 31                 | 31                 |

|                        |                    |                    |

#### Table 107. NVDS Read Time

If NVDS read performance is critical to your software architecture, you can optimize your code for speed. Try the first suggestion below before attempting the second.

- 1. Periodically refresh all addresses that are used. The optimal use of NVDS in terms of speed is to rotate the writes evenly among all addresses planned to use, bringing all reads closer to the minimum read time. Because the minimum read time is much less than the write time, however, actual speed benefits are not always realized.

- 2. Use as few unique addresses as possible to optimize the impact of refreshing, plus minimize the requirement for it.

If the PA2/RESET pin is held Low while a 32-bit key sequence is issued to the PA0/ DBG pin, the DBG feature is unlocked. After releasing PA2/RESET, it is pulled High. At this point, the PA0/DBG pin may be used to autobaud and cause the device to enter DEBUG Mode. See the <u>OCD Unlock Sequence (8-Pin Devices Only) section on</u> page 185.

### **Exiting DEBUG Mode**

The device exits DEBUG Mode following any of these operations:

- Clearing the DBGMODE bit in the OCD Control Register to 0

- Power-On Reset

- Voltage Brown-Out reset

- Watchdog Timer reset

- Asserting the RESET pin Low to initiate a Reset

- Driving the DBG pin Low while the device is in STOP Mode initiates a System Reset

### OCD Data Format

The OCD interface uses the asynchronous data format defined for RS-232. Each character transmitted and received by the OCD consists of 1 Start bit, 8 data bits (least-significant bit first) and 1 Stop bit as displayed in Figure 26.

| <br>START | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | STOP |

|-----------|----|----|----|----|----|----|----|----|------|

|           |    |    |    |    |    |    |    |    | 1    |

Figure 26. OCD Data Format

**Note:** When responding to a request for data, the OCD may commence transmitting immediately after receiving the stop bit of an incoming frame. Therefore, when sending the stop bit, the host must not actively drive the DBG pin High for more than 0.5 bit times. Zilog recommends that, if possible, the host drives the DBG pin using an open drain output to avoid this issue.

### **OCD Auto-Baud Detector/Generator**

To run over a range of baud rates (data bits per second) with various system clock frequencies, the On-Chip Debugger contains an Auto-Baud Detector/Generator. After a reset, the OCD is idle until it receives data. The OCD requires that the first character sent from the

Unlock and write Oscillator Control

Register (OSCCTL) to enable and

select oscillator at either 5.53MHz or

• Configure Flash option bits for correct

Unlock and write OSCCTL to enable

crystal oscillator, wait for it to stabilize and select as system clock (if the XTLDIS option bit has been deasserted, no waiting is required)

Configure Flash option bits for correct

Unlock and write OSCCTL to enable crystal oscillator and select as system

• Write GPIO registers to configure PB3

Unlock and write OSCCTL to select

Apply external clock signal to GPIO

· Enable WDT if not enabled and wait

until WDT Oscillator is operating Unlock and write Oscillator Control

pin for external clock function

external system clock

external oscillator mode

external oscillator mode

| Very low power consumption                                                                                                                        | Register (OSCCTL) to enable and select oscillator |

|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

|                                                                                                                                                   |                                                   |

| <b>Caution:</b> Unintentional accesses to the Oscillator C switching to a nonfunctioning oscillator. T block employs a register unlocking/locking | To prevent this condition, the oscillator con     |

| OSC Control Register Unlocking/L                                                                                                                  | _ocking                                           |

| To write the Oscillator Control Register, unl<br>Register with the values E7H followed by 11<br>changes the value of the actual register and r    | 8H. A third write to the OSCCTL Register          |

**Required Setup**

32.8kHz

clock

> s to the OSCCTL CTL Register ed state. Any other sequence of Oscillator Control Register writes has no effect. The values written to unlock the register must be ordered correctly, but are not necessarily consecutive. It is possible to write to or read from other registers within the unlocking/locking operation.

**Clock Source**

**RC** Oscillator

Internal Precision

External Crystal/

External Clock

Internal Watchdog

Timer Oscillator

Resonator

tor

Drive

Characteristics

High accuracy

• 32kHz to 20MHz

ponents

0 to 20MHz

• 10kHz nominal

nents required

source

•

External RC Oscilla- • 32kHz to 4MHz

• 32.8kHz or 5.53MHz

No external components required

Very high accuracy (dependent on

· Accuracy dependent on external com-

Accuracy dependent on external clock

Low accuracy; no external compo-

crystal or resonator used)

Requires external components

| Assembly        |                                     | Address<br>Mode<br>dst src (Hex) |       | Oncode(s) | Flags  |   |   |   |   |   | Fetch<br>Cycle<br>s | Instr.<br>Cycle<br>s |

|-----------------|-------------------------------------|----------------------------------|-------|-----------|--------|---|---|---|---|---|---------------------|----------------------|

| Mnemonic        | Symbolic Operation                  |                                  |       |           | CZSVDH |   |   |   |   |   |                     |                      |

| LDX dst, src    | $dst \leftarrow src$                | r                                | ER    | 84        | -      | - | - | - | _ | - | 3                   | 2                    |

|                 |                                     | lr                               | ER    | 85        |        |   |   |   |   |   | 3                   | 3                    |

|                 |                                     | R                                | IRR   | 86        | -      |   |   |   |   |   | 3                   | 4                    |

|                 |                                     | IR                               | IRR   | 87        |        |   |   |   |   |   | 3                   | 5                    |

|                 |                                     | r                                | X(rr) | 88        |        |   |   |   |   |   | 3                   | 4                    |

|                 |                                     | X(rr)                            | r     | 89        |        |   |   |   |   |   | 3                   | 4                    |

|                 |                                     | ER                               | r     | 94        |        |   |   |   |   |   | 3                   | 2                    |

|                 |                                     | ER                               | lr    | 95        |        |   |   |   |   |   | 3                   | 3                    |

|                 |                                     | IRR                              | R     | 96        |        |   |   |   |   |   | 3                   | 4                    |

|                 |                                     | IRR                              | IR    | 97        | -      |   |   |   |   |   | 3                   | 5                    |

|                 |                                     | ER                               | ER    | E8        | -      |   |   |   |   |   | 4                   | 2                    |

|                 |                                     | ER                               | IM    | E9        | -      |   |   |   |   |   | 4                   | 2                    |

| LEA dst, X(src) | $dst \gets src + X$                 | r                                | X(r)  | 98        | _      | - | _ | - | - | _ | 3                   | 3                    |

|                 |                                     | rr                               | X(rr) | 99        |        |   |   |   |   |   | 3                   | 5                    |

| MULT dst        | dst[15:0] ←<br>dst[15:8] * dst[7:0] | RR                               |       | F4        | _      | - | _ | - | - | _ | 2                   | 8                    |

| NOP             | No operation                        |                                  |       | 0F        | -      | - | - | - | - | - | 1                   | 2                    |

| OR dst, src     | $dst \gets dst  OR  src$            | r                                | r     | 42        | _      | * | * | 0 | - | _ | 2                   | 3                    |

|                 |                                     | r                                | lr    | 43        | -      |   |   |   |   |   | 2                   | 4                    |

|                 |                                     | R                                | R     | 44        |        |   |   |   |   |   | 3                   | 3                    |

|                 |                                     | R                                | IR    | 45        |        |   |   |   |   |   | 3                   | 4                    |

|                 |                                     | R                                | IM    | 46        | -      |   |   |   |   |   | 3                   | 3                    |

|                 |                                     | IR                               | IM    | 47        | -      |   |   |   |   |   | 3                   | 4                    |

### Table 128. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation: \* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 =Set to 1.

### Z8 Encore! XP<sup>®</sup> F082A Series **Product Specification**

|   |             |             |                    |                  |                     |                | Lo                                     | ower Nil                               | ble (He         | x)               |              |            |             |             |           |             |

|---|-------------|-------------|--------------------|------------------|---------------------|----------------|----------------------------------------|----------------------------------------|-----------------|------------------|--------------|------------|-------------|-------------|-----------|-------------|

|   | 0           | 1           | 2                  | 3                | 4                   | 5              | 6                                      | 7                                      | 8               | 9                | А            | В          | С           | D           | Е         | F           |

|   | 1.1         | 2.2         | 2.3                | 2.4              | 3.3                 | 3.4            | 3.3                                    | 3.4                                    | 4.3             | 4.3              | 2.3          | 2.2        | 2.2         | 3.2         | 1.2       | 1.2         |

| 0 | BRK         | SRP<br>IM   | ADD<br>r1,r2       | ADD<br>r1,lr2    | <b>ADD</b><br>R2,R1 | ADD<br>IR2,R1  | ADD<br>R1,IM                           | ADD<br>IR1,IM                          | ADDX<br>ER2,ER1 | ADDX<br>IM,ER1   | DJNZ<br>r1,X | JR<br>cc,X | LD<br>r1,IM | JP<br>cc,DA | INC<br>r1 | NOP         |

|   | 2.2         | 2.3         | 2.3                | 2.4              | 3.3                 | 3.4            | 3.3                                    | 3.4                                    | 4.3             | 4.3              | 11,∧         | UU, A      | 11,111      | CC,DA       |           | See 2nd     |

| 1 | RLC         | RLC         | ADC                | ADC              | ADC                 | ADC            | ADC                                    | ADC                                    | ADCX            |                  |              |            |             |             |           | Opcode      |

|   | R1          | IR1         | r1,r2              | r1,lr2           | R2,R1               | IR2,R1         | R1,IM                                  | IR1,IM                                 | ER2,ER1         | IM,ER1           |              |            |             |             |           | Мар         |

| - | 2.2         | 2.3         | 2.3                | 2.4              | 3.3                 | 3.4            | 3.3                                    | 3.4                                    | 4.3             | 4.3              |              |            |             |             |           | 1           |

| 2 | INC<br>R1   | INC<br>IR1  | SUB<br>r1,r2       | SUB<br>r1,lr2    | <b>SUB</b><br>R2,R1 | SUB<br>IR2,R1  | SUB<br>R1,IM                           | SUB<br>IR1,IM                          | SUBX<br>ER2,ER1 | SUBX<br>IM,ER1   |              |            |             |             |           | _           |

|   | 2.2         | 2.3         | 2.3                | 2.4              | 3.3                 | 3.4            | 3.3                                    | 3.4                                    | 4.3             | 4.3              |              |            |             |             |           |             |

| 3 | DEC         | DEC         | SBC                | SBC              | SBC                 | SBC            | SBC                                    | SBC                                    | SBCX            | SBCX             |              |            |             |             |           |             |

|   | R1          | IR1         | r1,r2              | r1,lr2           | R2,R1               | IR2,R1         | R1,IM                                  | IR1,IM                                 | ER2,ER1         | IM,ER1           |              |            |             |             |           |             |

|   | 2.2         | 2.3         | 2.3                | 2.4              | 3.3                 | 3.4            | 3.3                                    | 3.4                                    | 4.3             | 4.3              |              |            |             |             |           |             |

| 4 | DA<br>R1    | DA<br>IR1   | OR<br>r1,r2        | OR<br>r1,lr2     | <b>OR</b><br>R2,R1  | OR<br>IR2,R1   | OR<br>R1,IM                            | OR<br>IR1,IM                           | ORX<br>ER2,ER1  | ORX<br>IM,ER1    |              |            |             |             |           |             |

|   | 2.2         | 2.3         | 2.3                | 2.4              | 3.3                 | 3.4            | 3.3                                    | 3.4                                    | 4.3             | 4.3              |              |            |             |             |           | 1.2         |

| 5 | POP         | POP         | AND                | AND              | AND                 | AND            | AND                                    | AND                                    | ANDX            | ANDX             |              |            |             |             |           | WDT         |

|   | R1          | IR1         | r1,r2              | r1,lr2           | R2,R1               | IR2,R1         | R1,IM                                  | IR1,IM                                 | ER2,ER1         |                  |              |            |             |             |           |             |

| 6 | 2.2<br>COM  | 2.3<br>COM  | 2.3<br>TCM         | 2.4<br>TCM       | 3.3<br>TCM          | 3.4<br>TCM     | 3.3<br>TCM                             | 3.4<br>TCM                             | 4.3<br>TCMX     | 4.3<br>TCMX      |              |            |             |             |           | 1.2<br>STOP |

| 0 | R1          | IR1         | r1,r2              | r1,lr2           | R2,R1               | IR2,R1         | R1,IM                                  | IR1,IM                                 | ER2,ER1         | IM,ER1           |              |            |             |             |           | 3105        |

|   | 2.2         | 2.3         | 2.3                | 2.4              | 3.3                 | 3.4            | 3.3                                    | 3.4                                    | 4.3             | 4.3              |              |            |             |             |           | 1.2         |

| 7 | PUSH        | PUSH        | тм                 | тм               | тм                  | тм             | тм                                     | тм                                     | тмх             | тмх              |              |            |             |             |           | HALT        |

|   | R2          | IR2         | r1,r2              | r1,lr2           | R2,R1               | IR2,R1         | R1,IM                                  | IR1,IM                                 | ER2,ER1         | IM,ER1           |              |            |             |             |           |             |

| 8 | 2.5<br>DECW | 2.6<br>DECW | 2.5<br>LDE         | 2.9<br>LDEI      | 3.2<br>LDX          | 3.3<br>LDX     | 3.4<br>LDX                             | 3.5<br><b>LDX</b>                      | 3.4<br>LDX      | 3.4<br>LDX       |              |            |             |             |           | 1.2<br>DI   |

| 0 | RR1         | IRR1        | r1,Irr2            | lr1,lrr2         | r1,ER2              | Ir1,ER2        | IRR2,R1                                | IRR2,IR1                               | r1,rr2,X        | rr1,r2,X         |              |            |             |             |           | 5.          |

|   | 2.2         | 2.3         | 2.5                | 2.9              | 3.2                 | 3.3            | 3.4                                    | 3.5                                    | 3.3             | 3.5              |              |            |             |             |           | 1.2         |

| 9 | RL          | RL          | LDE                | LDEI             | LDX                 | LDX            | LDX                                    | LDX                                    | LEA             | LEA              |              |            |             |             |           | EI          |

|   | R1<br>2.5   | IR1<br>2.6  | r2,Irr1<br>2.3     | lr2,Irr1<br>2.4  | r2,ER1<br>3.3       | Ir2,ER1<br>3.4 | R2,IRR1<br>3.3                         | IR2,IRR1<br>3.4                        | r1,r2,X<br>4.3  | rr1,rr2,X<br>4.3 |              |            |             |             |           | 1.4         |

| А | INCW        | INCW        | CP                 | CP               | CP                  | 3.4<br>CP      | CP                                     | 3.4<br>CP                              | CPX             | CPX              |              |            |             |             |           | RET         |

|   | RR1         | IRR1        | r1,r2              | r1,lr2           | R2,R1               | IR2,R1         | R1,IM                                  | IR1,IM                                 | ER2,ER1         | IM,ER1           |              |            |             |             |           |             |

| _ | 2.2         | 2.3         | 2.3                | 2.4              | 3.3                 | 3.4            | 3.3                                    | 3.4                                    | 4.3             | 4.3              |              |            |             |             |           | 1.5         |

| В | CLR<br>R1   | IR1         | XOR<br>r1,r2       | XOR              | <b>XOR</b><br>R2,R1 | XOR<br>IR2,R1  | XOR<br>R1,IM                           | XOR<br>IR1,IM                          | XORX<br>ER2,ER1 | XORX<br>IM,ER1   |              |            |             |             |           | IRET        |

|   | 2.2         | 2.3         | 2.5                | r1,lr2<br>2.9    | 2.3                 | 2.9            | K I,IIVI                               | 3.4                                    | 3.2             | IIVI,EKI         |              |            |             |             |           | 1.2         |

| С | RRC         | RRC         | LDC                | LDCI             | JP                  | LDC            |                                        | LD                                     | PUSHX           |                  |              |            |             |             |           | RCF         |

|   | R1          | IR1         | r1,Irr2            | lr1,lrr2         | IRR1                | lr1,lrr2       |                                        | r1,r2,X                                | ER2             |                  |              |            |             |             |           |             |

| - | 2.2         | 2.3         | 2.5                | 2.9              | 2.6                 | 2.2            | 3.3                                    | 3.4                                    | 3.2             |                  |              |            |             |             |           | 1.2         |

| D | SRA<br>R1   | SRA<br>IR1  | LDC<br>r2,Irr1     | LDCI<br>Ir2,Irr1 | CALL<br>IRR1        | BSWAP<br>R1    | DA                                     | LD<br>r2,r1,X                          | POPX<br>ER1     |                  |              |            |             |             |           | SCF         |

|   | 2.2         | 2.3         | 2.2                | 2.3              | 3.2                 | 3.3            | 3.2                                    | 3.3                                    | 4.2             | 4.2              |              |            |             |             |           | 1.2         |

| Е | RR          | RR          | BIT                | LD.              | LD                  | LD             | LD                                     | LD                                     | LDX             | LDX              |              |            |             |             | i I       | CCF         |

|   | R1          | IR1         | p,b,r1             | r1,lr2           | R2,R1               | IR2,R1         | R1,IM                                  |                                        | ER2,ER1         | IM,ER1           |              |            |             |             |           |             |

| - | 2.2<br>SWAP | 2.3<br>SWAP | 2.6<br><b>TRAP</b> | 2.3<br>LD        | 2.8<br>MULT         | 3.3<br>LD      | 3.3<br><b>BTJ</b>                      | 3.4<br><b>BTJ</b>                      |                 |                  |              | <b>_</b>   |             |             |           |             |

| F | R1          | IR1         | Vector             | LD<br>lr1,r2     | RR1                 | LD<br>R2,IR1   | BIJ<br>p,b,r1,X                        |                                        |                 |                  |              |            |             |             |           |             |

|   | 131         |             | 100101             |                  | 13131               |                | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                 |                  | -            |            |             |             |           |             |

Lower Nibble (Hex)

Figure 31. First Opcode Map

|                                                        | V <sub>DE</sub>                                                                                                                                                                                          | ) = 2.7 V to 3                                                                                                                                                                                                      | 3.6 V                                                                                                                                                                                                                                                   |                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                              | Typical <sup>1</sup>                                                                                                                                                                                     |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                         | Units                                                                                                                                                                                            | Conditions                                                                                                                                                                                                                                                                                                                      |

| ADC Internal Ref-<br>erence Supply Cur-<br>rent        | 0                                                                                                                                                                                                        |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                         | μA                                                                                                                                                                                               | See Note 4.                                                                                                                                                                                                                                                                                                                     |

| Comparator sup-<br>ply Current                         | 150                                                                                                                                                                                                      | 180                                                                                                                                                                                                                 | 190                                                                                                                                                                                                                                                     | μA                                                                                                                                                                                               | See Note 4.                                                                                                                                                                                                                                                                                                                     |

| Low-Power Opera-<br>tional Amplifier<br>Supply Current | 3                                                                                                                                                                                                        | 5                                                                                                                                                                                                                   | 5                                                                                                                                                                                                                                                       | μA                                                                                                                                                                                               | Driving a high-impedance load                                                                                                                                                                                                                                                                                                   |

| Temperature Sen-<br>sor Supply Current                 | 60                                                                                                                                                                                                       |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                         | μA                                                                                                                                                                                               | See Note 4.                                                                                                                                                                                                                                                                                                                     |

| Band Gap Supply                                        | 320                                                                                                                                                                                                      | 480                                                                                                                                                                                                                 | 500                                                                                                                                                                                                                                                     | μA                                                                                                                                                                                               | For 20-/28-pin devices.                                                                                                                                                                                                                                                                                                         |

| Current                                                |                                                                                                                                                                                                          |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                         |                                                                                                                                                                                                  | For 8-pin devices.                                                                                                                                                                                                                                                                                                              |

|                                                        | ADC Internal Ref-<br>erence Supply Cur-<br>rent<br>Comparator sup-<br>ply Current<br>Low-Power Opera-<br>tional Amplifier<br>Supply Current<br>Temperature Sen-<br>sor Supply Current<br>Band Gap Supply | ParameterTypical1ADC Internal Ref-<br>erence Supply Cur-<br>rent0Comparator sup-<br>ply Current150Low-Power Opera-<br>tional Amplifier<br>Supply Current3Temperature Sen-<br>sor Supply Current60Band Gap Supply320 | ParameterTypical1Maximum<br>Std Temp2ADC Internal Ref-<br>erence Supply Cur-<br>rent0150180Comparator sup-<br>ply Current150180Low-Power Opera-<br>tional Amplifier<br>Supply Current35Temperature Sen-<br>sor Supply Current60180Band Gap Supply320480 | ADC Internal Ref-<br>erence Supply Cur-<br>rent<br>Comparator sup-<br>ply Current<br>Low-Power Opera-<br>Supply Current<br>Temperature Sen-<br>sor Supply Current<br>Band Gap Supply 320 480 500 | ParameterTypical <sup>1</sup> Maximum<br>Std Temp <sup>2</sup> Maximum<br>Ext Temp <sup>3</sup> UnitsADC Internal Ref-<br>erence Supply Cur-<br>rent0μAComparator sup-<br>ply Current150180190μALow-Power Opera-<br>tional Amplifier<br>Supply Current355μATemperature Sen-<br>sor Supply Current60μABand Gap Supply320480500μA |

#### Table 132. Power Consumption (Continued)

Notes:

1. Typical conditions are defined as  $V_{DD} = 3.3 V$  and  $+30^{\circ}C$ .

2. Standard temperature is defined as  $T_A = 0^{\circ}C$  to +70°C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

3. Extended temperature is defined as  $T_A = -40^{\circ}$ C to +105°C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

4. For this block to operate, the bandgap circuit is automatically turned on and must be added to the total supply current. This bandgap current is only added once, regardless of how many peripherals are using it.

CONTINUOUS mode 72, 87 COUNTER mode 73, 74 **COUNTER** modes 87 GATED mode 82, 88 ONE-SHOT mode 71, 87 operating mode 71 PWM mode 76, 77, 87, 88 reading the timer count values 84 reload high and low byte registers 91 timer control register definitions 85 timer output signal operation 84 timers 0-3 control registers 85, 86 high and low byte registers 89, 92 TM 209 TMX 209 transmit IrDA data 121 transmitting UART data-polled method 101 transmitting UART dat-interrupt-driven method 102 **TRAP 211**

# U

UART 6 architecture 99 baud rate generator 110 baud rates table 118 control register definitions 110 controller signals 10 interrupts 108 multiprocessor mode 105 receiving data using interrupt-driven method 104 receiving data using the polled method 103 transmitting data usin the interrupt-driven method 102 transmitting data using the polled method 101 x baud rate high and low registers 117 x control 0 and control 1 registers 110 x status 0 and status 1 registers 114, 115 UxBRH register 117 UxBRL register 117

UxCTL0 register 111, 117 UxCTL1 register 112 UxRXD register 116 UxSTAT0 register 114 UxSTAT1 register 115 UxTXD register 116

# V

vector 207 Voltage Brownout reset (VBR) 25

# W

Watchdog Timer approximate time-out delay 93 approximate time-out delays 140 CNTL 25 control register 96 electrical characteristics and timing 235, 238 interrupt in normal operation 94 interrupt in STOP mode 94 operation 140 refresh 94, 210 reload unlock sequence 95 reload upper, high and low registers 97 reset 26 reset in normal operation 95 reset in STOP mode 95 time-out response 94 WDTCTL register 30, 96, 141, 196 WDTH register 97 WDTL register 98 working register 206 working register pair 206 WTDU register 97

### Χ