Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 23                                                           |

| Program Memory Size        | 2KB (2K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 64 x 8                                                       |

| RAM Size                   | 512 x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 8x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 105°C (TA)                                           |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                               |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f022asj020eg    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Overview**

Zilog's Z8 Encore! MCU family of products are the first in a line of Zilog microcontroller products based upon the 8-bit eZ8 CPU. Zilog's Z8 Encore! XP F082A Series products expand upon Zilog's extensive line of 8-bit microcontrollers. The Flash in-circuit programming capability allows for faster development time and program changes in the field. The new eZ8 CPU is upward compatible with existing Z8 instructions. The rich peripheral set of the Z8 Encore! XP F082A Series makes it suitable for a variety of applications including motor control, security systems, home appliances, personal electronic devices and sensors.

## Features

The key features of Z8 Encore! XP F082A Series products include:

- 20MHz eZ8 CPU

- 1KB, 2KB, 4KB, or 8KB Flash memory with in-circuit programming capability

- 256B, 512B, or 1KB register RAM

- Up to 128B nonvolatile data storage (NVDS)

- Internal precision oscillator trimmed to  $\pm 1\%$  accuracy

- External crystal oscillator, operating up to 20MHz

- Optional 8-channel, 10-bit analog-to-digital converter (ADC)

- Optional on-chip temperature sensor

- On-chip analog comparator

- Optional on-chip low-power operational amplifier (LPO)

- Full-duplex UART

- The UART baud rate generator (BRG) can be configured and used as a basic 16-bit timer

- Infrared Data Association (IrDA)-compliant infrared encoder/decoders, integrated with the UART

- Two enhanced 16-bit timers with capture, compare and PWM capability

- Watchdog Timer (WDT) with dedicated internal RC oscillator

- Up to 20 vectored interrupts

- 6 to 25 I/O pins depending upon package

- Up to thirteen 5 V-tolerant input pins

- Up to 8 ports capable of direct LED drive with no current limit resistor required

- On-Chip Debugger (OCD)

- Voltage Brown-Out (VBO) protection

- Programmable low battery detection (LVD) (8-pin devices only)

- Bandgap generated precision voltage references available for the ADC, comparator, VBO and LVD

- Power-On Reset (POR)

- 2.7V to 3.6V operating voltage

- 8-, 20- and 28-pin packages

- $0^{\circ}$ C to  $+70^{\circ}$ C and  $-40^{\circ}$ C to  $+105^{\circ}$ C for operating temperature ranges

## **Part Selection Guide**

Table 1 identifies the basic features and package styles available for each device within the Z8 Encore! XP F082A Series product line.

| Part<br>Number | Flash<br>(KB) | RAM<br>(B) | NVDS <sup>1</sup><br>(B) | I/O  | Comparator | Advanced<br>Analog <sup>2</sup> | ADC<br>Inputs | Packages           |

|----------------|---------------|------------|--------------------------|------|------------|---------------------------------|---------------|--------------------|

| Z8F082A        | 8             | 1024       | 0                        | 6–23 | Yes        | Yes                             | 4–8           | 8-, 20- and 28-pin |

| Z8F081A        | 8             | 1024       | 0                        | 6–25 | Yes        | No                              | 0             | 8-, 20- and 28-pin |

| Z8F042A        | 4             | 1024       | 128                      | 6–23 | Yes        | Yes                             | 4–8           | 8-, 20- and 28-pin |

| Z8F041A        | 4             | 1024       | 128                      | 6–25 | Yes        | No                              | 0             | 8-, 20- and 28-pin |

| Z8F022A        | 2             | 512        | 64                       | 6–23 | Yes        | Yes                             | 4–8           | 8-, 20- and 28-pin |

| Z8F021A        | 2             | 512        | 64                       | 6–25 | Yes        | No                              | 0             | 8-, 20- and 28-pin |

| Z8F012A        | 1             | 256        | 16                       | 6–23 | Yes        | Yes                             | 4–8           | 8-, 20- and 28-pin |

| Z8F011A        | 1             | 256        | 16                       | 6–25 | Yes        | No                              | 0             | 8-, 20- and 28-pin |

| Mateau         |               |            |                          |      |            |                                 |               |                    |

#### Table 1. Z8 Encore! XP F082A Series Family Part Selection Guide

Notes:

1. Non-volatile data storage.

2. Advanced Analog includes ADC, temperature sensor and low-power operational amplifier.

|                                                       | Reset Characteristics and Latency                      |            |                                                               |  |  |  |  |

|-------------------------------------------------------|--------------------------------------------------------|------------|---------------------------------------------------------------|--|--|--|--|

| Reset Type                                            | Control Registers                                      | eZ8<br>CPU | Reset Latency (Delay)                                         |  |  |  |  |

| System Reset                                          | Reset (as applicable)                                  | Reset      | 66 Internal Precision Oscillator Cycles                       |  |  |  |  |

| System Reset with Crystal Oscillator Enabled          | Reset (as applicable)                                  | Reset      | 5000 Internal Precision Oscillator Cycles                     |  |  |  |  |

| Stop Mode Recovery                                    | Unaffected, except<br>WDT_CTL and<br>OSC_CTL registers | Reset      | 66 Internal Precision Oscillator Cycles<br>+ IPO startup time |  |  |  |  |

| Stop Mode Recovery with<br>Crystal Oscillator Enabled | Unaffected, except<br>WDT_CTL and<br>OSC_CTL registers | Reset      | 5000 Internal Precision Oscillator Cycles                     |  |  |  |  |

#### Table 8. Reset and Stop Mode Recovery Characteristics and Latency

During a System Reset or Stop Mode Recovery, the Internal Precision Oscillator requires 4  $\mu$ s to start up. Then the Z8 Encore! XP F082A Series device is held in Reset for 66 cycles of the Internal Precision Oscillator. If the crystal oscillator is enabled in the Flash option bits, this reset period is increased to 5000 IPO cycles. When a reset occurs because of a low voltage condition or Power-On Reset (POR), this delay is measured from the time that the supply voltage first exceeds the POR level. If the external pin reset remains asserted at the end of the reset period, the device remains in reset until the pin is deasserted.

At the beginning of Reset, all GPIO pins are configured as inputs with pull-up resistor disabled, except PD0 (or PA2 on 8-pin devices) which is shared with the reset pin. On reset, the PD0 is configured as a bidirectional open-drain reset. The pin is internally driven low during port reset, after which the user code may reconfigure this pin as a general purpose output.

During Reset, the eZ8 CPU and on-chip peripherals are idle; however, the on-chip crystal oscillator and Watchdog Timer oscillator continue to run.

Upon Reset, control registers within the Register File that have a defined Reset value are loaded with their reset values. Other control registers (including the Stack Pointer, Register Pointer and Flags) and general-purpose RAM are undefined following Reset. The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset vector address.

As the control registers are reinitialized by a system reset, the system clock after reset is always the IPO. The software must reconfigure the oscillator control block, such that the correct system clock source is enabled and selected.

|          | Program        |                                                                                                                        |  |  |  |  |  |

|----------|----------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|          | Memory         |                                                                                                                        |  |  |  |  |  |

| Priority | Vector Address | Interrupt or Trap Source                                                                                               |  |  |  |  |  |

| Highest  | 0002H          | Reset (not an interrupt)                                                                                               |  |  |  |  |  |

|          | 0004H          | Watchdog Timer (see Watchdog Timer)                                                                                    |  |  |  |  |  |

|          | 003AH          | Primary Oscillator Fail Trap (not an interrupt)                                                                        |  |  |  |  |  |

|          | 003CH          | Watchdog Oscillator Fail Trap (not an interrupt)                                                                       |  |  |  |  |  |

|          | 0006H          | Illegal Instruction Trap (not an interrupt)                                                                            |  |  |  |  |  |

| _        | 0008H          | Reserved                                                                                                               |  |  |  |  |  |

|          | 000AH          | Timer 1                                                                                                                |  |  |  |  |  |

|          | 000CH          | Timer 0                                                                                                                |  |  |  |  |  |

|          | 000EH          | UART 0 receiver                                                                                                        |  |  |  |  |  |

|          | 0010H          | UART 0 transmitter                                                                                                     |  |  |  |  |  |

|          | 0012H          | Reserved                                                                                                               |  |  |  |  |  |

|          | 0014H          | Reserved                                                                                                               |  |  |  |  |  |

|          | 0016H          | ADC                                                                                                                    |  |  |  |  |  |

|          | 0018H          | Port A Pin 7, selectable rising or falling input edge or LVD (see Reset, Stop Mode Recovery and Low Voltage Detection) |  |  |  |  |  |

|          | 001AH          | Port A Pin 6, selectable rising or falling input edge or Comparator Output                                             |  |  |  |  |  |

|          | 001CH          | Port A Pin 5, selectable rising or falling input edge                                                                  |  |  |  |  |  |

|          | 001EH          | Port A Pin 4, selectable rising or falling input edge                                                                  |  |  |  |  |  |

|          | 0020H          | Port A Pin 3, selectable rising or falling input edge                                                                  |  |  |  |  |  |

|          | 0022H          | Port A Pin 2, selectable rising or falling input edge                                                                  |  |  |  |  |  |

|          | 0024H          | Port A Pin 1, selectable rising or falling input edge                                                                  |  |  |  |  |  |

|          | 0026H          | Port A Pin 0, selectable rising or falling input edge                                                                  |  |  |  |  |  |

|          | 0028H          | Reserved                                                                                                               |  |  |  |  |  |

|          | 002AH          | Reserved                                                                                                               |  |  |  |  |  |

|          | 002CH          | Reserved                                                                                                               |  |  |  |  |  |

|          | 002EH          | Reserved                                                                                                               |  |  |  |  |  |

|          | 0030H          | Port C Pin 3, both input edges                                                                                         |  |  |  |  |  |

|          | 0032H          | Port C Pin 2, both input edges                                                                                         |  |  |  |  |  |

|          | 0034H          | Port C Pin 1, both input edges                                                                                         |  |  |  |  |  |

| Lowest   | 0036H          | Port C Pin 0, both input edges                                                                                         |  |  |  |  |  |

|          | 0038H          | Reserved                                                                                                               |  |  |  |  |  |

|          |                |                                                                                                                        |  |  |  |  |  |

### Table 34. Trap and Interrupt Vectors in Order of Priority

# **Caution:** The frequency of the comparator output signal must not exceed one-fourth the system clock frequency. Further, the high or low state of the comparator output signal pulse must be no less than twice the system clock period. A shorter pulse may not be captured.

After reaching the reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer Reload.

Observe the following steps for configuring a timer for COMPARATOR COUNTER Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer.

- Configure the timer for COMPARATOR COUNTER Mode.

- Select either the rising edge or falling edge of the comparator output signal for the count. This also sets the initial logic level (High or Low) for the Timer Output alternate function. However, the Timer Output function is not required to be enabled.

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This action only affects the first pass in COMPARATOR COUNTER Mode. After the first timer Reload in COMPARATOR COUNTER Mode, counting always begins at the reset value of 0001H. Generally, in COMPARATOR COUNTER Mode the Timer High and Low Byte registers must be written with the value 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 6. Write to the Timer Control Register to enable the timer.

In COMPARATOR COUNTER Mode, the number of comparator output transitions since the timer start is computed via the following equation:

Comparator Output Transitions = Current Count Value – Start Value

- 5. Enable the timer interrupt, if appropriate and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input capture and reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the reload event by setting TICONFIG field of the TxCTL0 Register.

- 6. Configure the associated GPIO port pin for the Timer Input alternate function.

- 7. Write to the Timer Control Register to enable the timer and initiate counting.

In CAPTURE Mode, the elapsed time from timer start to Capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

### **CAPTURE RESTART Mode**

In CAPTURE RESTART Mode, the current timer count value is recorded when the acceptable external Timer Input transition occurs. The Capture count value is written to the Timer PWM High and Low Byte registers. The timer input is the system clock. The TPOL bit in the Timer Control Register determines if the Capture occurs on a rising edge or a falling edge of the Timer Input signal. When the Capture event occurs, an interrupt is generated and the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL0 Register is set to indicate the timer interrupt is because of an input capture event.

If no Capture event occurs, the timer counts up to the 16-bit Compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL0 Register is cleared to indicate the timer interrupt is not caused by an input capture event.

Observe the following steps for configuring a timer for CAPTURE RESTART Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE RESTART Mode by writing the TMODE bits in the TxCTL1 Register and the TMODEHI bit in TxCTL0 Register

- Set the prescale value

- Set the Capture edge (rising or falling) for the Timer Input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- Configure the timer for GATED Mode

- Set the prescale value

- 2. Write to the Timer High and Low Byte registers to set the starting count value. Writing these registers only affects the first pass in GATED Mode. After the first timer reset in GATED Mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. Enable the timer interrupt, if appropriate and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input deassertion and reload events. If appropriate, configure the timer interrupt to be generated only at the input deassertion event or the reload event by setting TICONFIG field of the TxCTL0 Register.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control Register to enable the timer.

- 7. Assert the Timer Input signal to initiate the counting.

#### CAPTURE/COMPARE Mode

In CAPTURE/COMPARE Mode, the timer begins counting on the first external Timer Input transition. The acceptable transition (rising edge or falling edge) is set by the TPOL bit in the Timer Control Register. The timer input is the system clock.

Every subsequent acceptable transition (after the first) of the Timer Input signal captures the current count value. The Capture value is written to the Timer PWM High and Low Byte registers. When the Capture event occurs, an interrupt is generated, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL0 Register is set to indicate the timer interrupt is caused by an input capture event.

If no Capture event occurs, the timer counts up to the 16-bit Compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the Compare value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL0 Register is cleared to indicate the timer interrupt is not because of an input capture event.

Observe the following steps for configuring a timer for CAPTURE/COMPARE Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE/COMPARE Mode

- Set the prescale value

## Timer 0–1 PWM High and Low Byte Registers

The Timer 0–1 PWM High and Low Byte (TxPWMH and TxPWML) registers, shown in Tables 56 and 57, control Pulse-Width Modulator (PWM) operations. These registers also store the Capture values for the CAPTURE and CAPTURE/COMPARE modes.

| Bit     | 7          | 6    | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|------------|------|-----|-----|-----|-----|-----|-----|

| Field   |            | PWMH |     |     |     |     |     |     |

| RESET   | 0          | 0    | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W        | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | F04H, F0CH |      |     |     |     |     |     |     |

#### Table 56. Timer 0–1 PWM High Byte Register (TxPWMH)

#### Table 57. Timer 0–1 PWM Low Byte Register (TxPWML)

| Bit     | 7          | 6    | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|------------|------|-----|-----|-----|-----|-----|-----|

| Field   |            | PWML |     |     |     |     |     |     |

| RESET   | 0          | 0    | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W        | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |

| Address | F05H, F0DH |      |     |     |     |     |     |     |

#### Bit Description

| [7:0] | Pulse-Width Modulator High and Low Bytes                                                     |

|-------|----------------------------------------------------------------------------------------------|

| PWMH, | These two bytes, {PWMH[7:0], PWML[7:0]}, form a 16-bit value that is compared to the current |

| PWML  | 16-bit timer count. When a match occurs, the PWM output changes state. The PWM output        |

|       | value is set by the TPOL bit in the Timer Control Register (TxCTL1) Register.                |

The TxPWMH and TxPWML registers also store the 16-bit captured timer value when operating in CAPTURE or CAPTURE/COMPARE modes.

## Watchdog Timer

The Watchdog Timer (WDT) protects against corrupt or unreliable software, power faults and other system-level problems which may place the Z8 Encore! XP F082A Series devices into unsuitable operating states. The features of Watchdog Timer include:

- On-chip RC oscillator

- A selectable time-out response: reset or interrupt

- 24-bit programmable time-out value

## Operation

The Watchdog Timer is a one-shot timer that resets or interrupts the Z8 Encore! XP F082A Series devices when the WDT reaches its terminal count. The Watchdog Timer uses a dedicated on-chip RC oscillator as its clock source. The Watchdog Timer operates in only two modes: ON and OFF. Once enabled, it always counts and must be refreshed to prevent a time-out. Perform an enable by executing the WDT instruction or by setting the WDT\_AO Flash option bit. The WDT\_AO bit forces the Watchdog Timer to operate immediately upon reset, even if a WDT instruction has not been executed.

The Watchdog Timer is a 24-bit reloadable downcounter that uses three 8-bit registers in the eZ8 CPU register space to set the reload value. The nominal WDT time-out period is described by the following equation:

WDT Time-out Period (ms) =  $\frac{\text{WDT Reload Value}}{10}$

where the WDT reload value is the decimal value of the 24-bit value given by {WDTU[7:0], WDTH[7:0], WDTL[7:0]} and the typical Watchdog Timer RC oscillator frequency is 10kHz. The Watchdog Timer cannot be refreshed after it reaches 000002H. The WDT reload value must not be set to values below 000004H. Table 58 provides information about approximate time-out delays for the minimum and maximum WDT reload values.

| WDT Reload Value | WDT Reload Value | Approximate Time-Out Delay<br>(with 10kHz typical WDT oscillator frequency) |                        |  |  |

|------------------|------------------|-----------------------------------------------------------------------------|------------------------|--|--|

| (Hex)            | (Decimal)        | Typical                                                                     | Description            |  |  |

| 000004           | 4                | 400 μs                                                                      | Minimum time-out delay |  |  |

| FFFFF            | 16,777,215       | 28 minutes                                                                  | Maximum time-out delay |  |  |

#### Table 58. Watchdog Timer Approximate Time-Out Delays

## Watchdog Timer Reload Upper, High and Low Byte Registers

The Watchdog Timer Reload Upper, High and Low Byte (WDTU, WDTH, WDTL) registers, shown in Tables 60 through 62, form the 24-bit reload value that is loaded into the Watchdog Timer when a WDT instruction executes. The 24-bit reload value ranges across bits [23:0] to encompass the three bytes {WDTU[7:0], WDTH[7:0], WDTL[7:0]}. Writing to these registers sets the appropriate reload value. Reading from these registers returns the current Watchdog Timer count value.

**Caution:** The 24-bit WDT reload value must not be set to a value less than 000004H.

| Bit        | 7                                                                                            | 6    | 5 | 4 | 3 | 2 | 1 | 0 |  |

|------------|----------------------------------------------------------------------------------------------|------|---|---|---|---|---|---|--|

| Field      |                                                                                              | WDTU |   |   |   |   |   |   |  |

| RESET      |                                                                                              | 00H  |   |   |   |   |   |   |  |

| R/W        |                                                                                              | R/W* |   |   |   |   |   |   |  |

| Address    | FF1H                                                                                         |      |   |   |   |   |   |   |  |

| Note: A re | Note: A read returns the current WDT count value; a write sets the appropriate reload value. |      |   |   |   |   |   |   |  |

#### Table 60. Watchdog Timer Reload Upper Byte Register (WDTU)

| Bit   | Description                                                              |

|-------|--------------------------------------------------------------------------|

| [7:0] | WDT Reload Upper Byte                                                    |

| WDTU  | Most-significant byte (MSB); bits[23:16] of the 24-bit WDT reload value. |

#### Table 61. Watchdog Timer Reload High Byte Register (WDTH)

| Bit        | 7                                                                                            | 6    | 5 | 4 | 3 | 2 | 1 | 0 |

|------------|----------------------------------------------------------------------------------------------|------|---|---|---|---|---|---|

| Field      |                                                                                              | WDTH |   |   |   |   |   |   |

| RESET      |                                                                                              | 04H  |   |   |   |   |   |   |

| R/W        | R/W*                                                                                         |      |   |   |   |   |   |   |

| Address    | FF2H                                                                                         |      |   |   |   |   |   |   |

| Note: A re | Note: A read returns the current WDT count value; a write sets the appropriate reload value. |      |   |   |   |   |   |   |

| Bit   | Description                                             |

|-------|---------------------------------------------------------|

| [7:0] | WDT Reload High Byte                                    |

| WDTH  | Middle byte; bits[15:8] of the 24-bit WDT reload value. |

The UART is now configured for interrupt-driven data reception. When the UART Receiver interrupt is detected, the associated interrupt service routine (ISR) performs the following:

- 1. Checks the UART Status 0 Register to determine the source of the interrupt error, break, or received data.

- 2. Reads the data from the UART Receive Data Register if the interrupt was because of data available. If operating in MULTIPROCESSOR (9-bit) Mode, further actions may be required depending on the MULTIPROCESSOR Mode bits MPMD[1:0].

- 3. Clears the UART Receiver interrupt in the applicable Interrupt Request Register.

- 4. Executes the IRET instruction to return from the interrupt-service routine and await more data.

## Clear To Send (CTS) Operation

The CTS pin, if enabled by the CTSE bit of the UART Control 0 Register, performs flow control on the outgoing transmit datastream. The Clear To Send ( $\overline{\text{CTS}}$ ) input pin is sampled one system clock before beginning any new character transmission. To delay transmission of the next data character, an external receiver must deassert  $\overline{\text{CTS}}$  at least one system clock cycle before a new data transmission begins. For multiple character transmissions, this action is typically performed during Stop Bit transmission. If  $\overline{\text{CTS}}$  deasserts in the middle of a character transmission, the current character is sent completely.

## MULTIPROCESSOR (9-bit) Mode

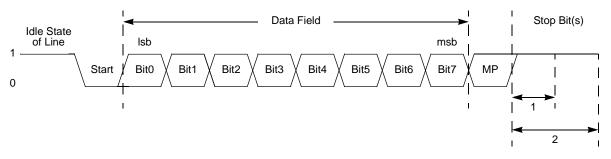

The UART features a MULTIPROCESSOR (9-bit) Mode that uses an extra (9th) bit for selective communication when a number of processors share a common UART bus. In MULTIPROCESSOR Mode (also referred to as *9-bit Mode*), the multiprocessor bit (MP) is transmitted immediately following the 8-bits of data and immediately preceding the Stop bit(s) as displayed in Figure 13. The character format is:

Figure 13. UART Asynchronous MULTIPROCESSOR Mode Data Format

## **UART Interrupts**

The UART features separate interrupts for the transmitter and the receiver. In addition, when the UART primary functionality is disabled, the Baud Rate Generator can also function as a basic timer with interrupt capability.

#### **Transmitter Interrupts**

The transmitter generates a single interrupt when the Transmit Data Register Empty bit (TDRE) is set to 1. This indicates that the transmitter is ready to accept new data for transmission. The TDRE interrupt occurs after the Transmit Shift Register has shifted the first bit of data out. The Transmit Data Register can now be written with the next character to send. This action provides 7 bit periods of latency to load the Transmit Data Register before the Transmit Shift Register completes shifting the current character. Writing to the UART Transmit Data Register clears the TDRE bit to 0.

### **Receiver Interrupts**

The receiver generates an interrupt when any of the following actions occur:

• A data byte is received and is available in the UART Receive Data Register. This interrupt can be disabled independently of the other receiver interrupt sources. The received data interrupt occurs after the receive character has been received and placed in the Receive Data Register. To avoid an overrun error, software must respond to this received data available condition before the next character is completely received.

**Note:** In MULTIPROCESSOR Mode (MPEN=1), the receive data interrupts are dependent on the multiprocessor configuration and the most recent address byte.

- A break is received.

- An overrun is detected.

- A data framing error is detected.

### **UART Overrun Errors**

When an overrun error condition occurs the UART prevents overwriting of the valid data currently in the Receive Data Register. The Break Detect and Overrun status bits are not displayed until after the valid data has been read.

After the valid data has been read, the UART Status 0 Register is updated to indicate the overrun condition (and Break Detect, if applicable). The RDA bit is set to 1 to indicate that the Receive Data Register contains a data byte. However, because the overrun error occurred, this byte may not contain valid data and must be ignored. The BRKD bit indicates if the overrun was caused by a break condition on the line. After reading the status

| Bit              | 7                                             | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5    | 4     | 3   | 2   | 1         | 0   |  |  |  |

|------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-----|-----|-----------|-----|--|--|--|

| Field            | REFSELH                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Rese | erved |     | В   | UFMODE[2: | 0]  |  |  |  |

| RESET            | 1                                             | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0    | 0     | 0   | 0   | 0         | 0   |  |  |  |

| R/W              | R/W                                           | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W  | R/W   | R/W | R/W | R/W       | R/W |  |  |  |

| Address          |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      | F7    | 1H  |     |           |     |  |  |  |

| Bit              | Dese                                          | cription                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |       |     |     |           |     |  |  |  |

| [7]<br>REFSELH   | I In co<br>the le<br>REF<br>00=<br>01=<br>10= | Voltage Reference Level Select High Bit<br>In conjunction with the Low bit (REFSELL) in ADC Control Register 0, this determines<br>the level of the internal voltage reference; the following details the effects of {REFSELH,<br>REFSELL}; this reference is independent of the Comparator reference.<br>00= Internal Reference Disabled, reference comes from external pin.<br>01= Internal Reference set to 1.0V.<br>10= Internal Reference set to 2.0V (default).<br>11= Reserved. |      |       |     |     |           |     |  |  |  |

| [6:3]            |                                               | <b>Reserved</b> These bits are reserved and must be programmed to 0000.                                                                                                                                                                                                                                                                                                                                                                                                                |      |       |     |     |           |     |  |  |  |

| [2:0]<br>BUFMODI | E[2:0] 000<br>001<br>010                      | Input Buffer Mode Select<br>000 = Single-ended, unbuffered input.<br>001 = Single-ended, buffered input with unity gain.<br>010 = Reserved.<br>011 = Reserved.                                                                                                                                                                                                                                                                                                                         |      |       |     |     |           |     |  |  |  |

#### Table 74. ADC Control/Status Register 1 (ADCCTL1)

100 = Differential, unbuffered input.101 = Differential, buffered input with unity gain.

110 = Reserved. 111 = Reserved.

## ADC Data High Byte Register

The ADC Data High Byte (ADCD\_H) Register contains the upper eight bits of the ADC output. The output is an 13-bit two's complement value. During a single-shot conversion, this value is invalid. Access to the ADC Data High Byte Register is read-only. Reading the ADC Data High Byte Register latches data in the ADC Low Bits Register.

| 8KB Flash<br>Program Memor | y<br>Addresses (hex)<br>T 1FFF | 4KB Flash<br>Program Memory | /<br>Addresses (hex)<br>1 0FFF | 2KB Flash<br>Program Memory<br>Addresse | es (hex)                 |

|----------------------------|--------------------------------|-----------------------------|--------------------------------|-----------------------------------------|--------------------------|

| Sector 7                   | 1C00                           | Sector 7                    | 0E00                           | Sector 3                                | 07FF<br>0600<br>05FF     |

| Sector 6                   | 1BFF                           | Sector 6                    | 0DFF                           | Sector 2                                | 03FF<br>0400<br>03FF     |

|                            | 1800<br>17FF                   | October 5                   | 0C00<br>0BFF                   | Sector 1                                | 0200<br>01FF             |

| Sector 5                   | 1400<br>13FF                   | Sector 5                    | 0A00<br>09FF                   | Sector 0                                | 0000                     |

| Sector 4                   | 1000                           | Sector 4                    | 0800                           |                                         |                          |

| Sector 3                   | 0FFF<br>0C00                   | Sector 3                    | 07FF<br>0600                   | 1 KB Flash<br>Program Memory            | ,<br>// )                |

| Sector 2                   | 0BFF<br>0800                   | Sector 2                    | 05FF<br>0400                   | Address<br>Sector 1                     | es (nex)<br>03FF<br>0200 |

| Sector 1                   | 07FF<br>0400                   | Sector 1                    | 03FF<br>0200                   | Sector 0                                | 01FF                     |

| Sector 0                   | 03FF<br>0000                   | Sector 0                    | 01FF<br>0000                   |                                         |                          |

Figure 21. Flash Memory Arrangement

## **Flash Information Area**

The Flash information area is separate from Program Memory and is mapped to the address range FE00H to FFFFH. This area is readable but cannot be erased or overwritten. Factory trim values for the analog peripherals are stored here. Factory calibration data for the ADC is also stored here.

## Operation

The Flash Controller programs and erases Flash memory. The Flash Controller provides the proper Flash controls and timing for Byte Programming, Page Erase and Mass Erase of Flash memory.

The Flash Controller contains several protection mechanisms to prevent accidental programming or erasure. These mechanism operate on the page, sector and full-memory levels.

## Nonvolatile Data Storage

The Z8 Encore! XP F082A Series devices contain a nonvolatile data storage (NVDS) element of up to 128 bytes. This memory can perform over 100,000 write cycles.

## Operation

The NVDS is implemented by special purpose Zilog software stored in areas of program memory, which are not user-accessible. These special-purpose routines use the Flash memory to store the data. The routines incorporate a dynamic addressing scheme to maximize the write/erase endurance of the Flash.

Note: Different members of the Z8 Encore! XP F082A Series feature multiple NVDS array sizes; see the <u>Part Selection Guide</u> section on page 2 for details. Devices containing 8KB of Flash memory do not include the NVDS feature.

## **NVDS Code Interface**

Two routines are required to access the NVDS: a write routine and a read routine. Both of these routines are accessed with a CALL instruction to a predefined address outside of the user-accessible program memory. Both the NVDS address and data are single-byte values. Because these routines disturb the working register set, user code must ensure that any required working register values are preserved by pushing them onto the stack or by changing the working register pointer just prior to NVDS execution.

During both read and write accesses to the NVDS, interrupt service is NOT disabled. Any interrupts that occur during the NVDS execution must take care not to disturb the working register and existing stack contents or else the array may become corrupted. Disabling interrupts before executing NVDS operations is recommended.

Use of the NVDS requires 15 bytes of available stack space. Also, the contents of the working register set are overwritten.

For correct NVDS operation, the Flash Frequency registers must be programmed based on the system clock frequency (see **the** <u>Flash Operation Timing Using the Flash Frequency</u> <u>Registers</u> **section on page 149**).

## **Byte Write**

To write a byte to the NVDS array, the user code must first push the address, then the data byte onto the stack. The user code issues a CALL instruction to the address of the byte-write routine (0x10B3). At the return from the sub-routine, the write status byte resides in working register R0. The bit fields of this status byte are defined in Table 106. The contents of the status byte are undefined for write operations to illegal addresses. Also, user code must pop the address and data bytes off the stack.

The write routine uses 13 bytes of stack space in addition to the two bytes of address and data pushed by the user. Sufficient memory must be available for this stack usage.

Because of the Flash memory architecture, NVDS writes exhibit a nonuniform execution time. In general, a write takes  $251 \mu s$  (assuming a 20MHz system clock). Every 400 to 500 writes, however, a maintenance operation is necessary. In this rare occurrence, the write takes up to 61 ms to complete. Slower system clock speeds result in proportionally higher execution times.

NVDS byte writes to invalid addresses (those exceeding the NVDS array size) have no effect. Illegal write operations have a  $2\mu s$  execution time.

| Bit              | 7 | 6    | 5     | 4 | 3    | 2  | 1   | 0   |

|------------------|---|------|-------|---|------|----|-----|-----|

| Field            |   | Rese | erved |   | RCPY | PF | AWE | DWE |

| Default<br>Value | 0 | 0    | 0     | 0 | 0    | 0  | 0   | 0   |

#### Table 106. Write Status Byte

| Bit   | Description                                                                                                 |

|-------|-------------------------------------------------------------------------------------------------------------|

| [7:4] | Reserved<br>These bits are reserved and must be programmed to 0000.                                         |

| [3]   | <b>Recopy Subroutine Executed</b>                                                                           |

| RCPY  | A recopy subroutine was executed. These operations take significantly longer than a normal write operation. |

| [2]   | <b>Power Failure Indicator</b>                                                                              |

| PF    | A power failure or system reset occurred during the most recent attempted write to the NVDS array.          |

| [1]   | Address Write Error                                                                                         |

| AWE   | An address byte failure occurred during the most recent attempted write to the NVDS array.                  |

| [0]   | Data Write Error                                                                                            |

| DWE   | A data byte failure occurred during the most recent attempted write to the NVDS array.                      |

| Debug Command           | Command<br>Byte | Enabled when<br>Not in DEBUG<br>Mode? | Disabled by Flash Read Protect<br>Option Bit                                                                                                                              |

|-------------------------|-----------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Write Program Counter   | 06H             | _                                     | Disabled.                                                                                                                                                                 |

| Read Program Counter    | 07H             | -                                     | Disabled.                                                                                                                                                                 |

| Write Register          | 08H             | -                                     | Only writes of the Flash Memory Control<br>registers are allowed. Additionally, only<br>the Mass Erase command is allowed to<br>be written to the Flash Control Register. |

| Read Register           | 09H             | _                                     | Disabled.                                                                                                                                                                 |

| Write Program Memory    | 0AH             | -                                     | Disabled.                                                                                                                                                                 |

| Read Program Memory     | 0BH             | -                                     | Disabled.                                                                                                                                                                 |

| Write Data Memory       | 0CH             | -                                     | Yes.                                                                                                                                                                      |

| Read Data Memory        | 0DH             | _                                     | _                                                                                                                                                                         |

| Read Program Memory CRC | 0EH             | _                                     | -                                                                                                                                                                         |

| Reserved                | 0FH             | -                                     | _                                                                                                                                                                         |

| Step Instruction        | 10H             | _                                     | Disabled.                                                                                                                                                                 |

| Stuff Instruction       | 11H             | _                                     | Disabled.                                                                                                                                                                 |

| Execute Instruction     | 12H             | _                                     | Disabled.                                                                                                                                                                 |

| Reserved                | 13H–FFH         | _                                     | -                                                                                                                                                                         |

#### Table 109. Debug Command Enable/Disable (Continued)

In the list of OCD commands that follows, data and commands sent from the host to the On-Chip Debugger are identified by DBG  $\leftarrow$  Command/Data. Data sent from the On-Chip Debugger back to the host is identified by DBG  $\rightarrow$  Data.

**Read OCD Revision (00H).** The Read OCD Revision command determines the version of the On-Chip Debugger. If OCD commands are added, removed, or changed, this revision number changes.

```

DBG \leftarrow 00H

DBG \rightarrow OCDRev[15:8] (Major revision number)

DBG \rightarrow OCDRev[7:0] (Minor revision number)

```

**Read OCD Status Register (02H).** The Read OCD Status Register command reads the OCDSTAT Register.

DBG  $\leftarrow$  02H DBG  $\rightarrow$  OCDSTAT[7:0]

**Read Runtime Counter (03H).** The Runtime Counter counts system clock cycles in between Breakpoints. The 16-bit Runtime Counter counts up from 0000H and stops at the maximum count of FFFFH. The Runtime Counter is overwritten during the Write Memory,

## **Oscillator Control**

The Z8 Encore! XP F082A Series devices uses five possible clocking schemes, each user-selectable:

- Internal precision trimmed RC oscillator (IPO)

- On-chip oscillator using off-chip crystal or resonator

- On-chip oscillator using external RC network

- External clock drive

- On-chip low power Watchdog Timer oscillator

- Clock failure detection circuitry

In addition, Z8 Encore! XP F082A Series devices contain clock failure detection and recovery circuitry, allowing continued operation despite a failure of the system clock oscillator.

## Operation

This chapter discusses the logic used to select the system clock and handle primary oscillator failures.

## **System Clock Selection**

The oscillator control block selects from the available clocks. Table 112 details each clock source and its usage.

| Assembly      |                                         | Address<br>Mode<br>Opcode(s) |     | Flags |   |   |   |   |   | Fetch<br>Cycle | Instr<br>Cycle |   |

|---------------|-----------------------------------------|------------------------------|-----|-------|---|---|---|---|---|----------------|----------------|---|

| Mnemonic      | Symbolic Operation                      | dst                          | src | (Hex) | С | Ζ | S | V | D | Н              | S              | S |

| RRC dst       |                                         | R                            |     | C0    | * | * | * | * | _ | _              | 2              | 2 |

|               | ► <u>D7D6D5D4D3D2D1D0</u> ►_C<br>dst    | IR                           |     | C1    |   |   |   |   |   |                | 2              | 3 |

| SBC dst, src  | $dst \gets dst - src - C$               | r                            | r   | 32    | * | * | * | * | 1 | *              | 2              | 3 |

|               | =                                       | r                            | lr  | 33    |   |   |   |   |   |                | 2              | 4 |

|               | -                                       | R                            | R   | 34    |   |   |   |   |   |                | 3              | 3 |

|               | -                                       | R                            | IR  | 35    |   |   |   |   |   |                | 3              | 4 |

|               | -                                       | R                            | IM  | 36    |   |   |   |   |   |                | 3              | 3 |

|               | -                                       | IR                           | IM  | 37    |   |   |   |   |   |                | 3              | 4 |

| SBCX dst, src | $dst \gets dst - src - C$               | ER                           | ER  | 38    | * | * | * | * | 1 | *              | 4              | 3 |

|               | -                                       | ER                           | IM  | 39    |   |   |   |   |   |                | 4              | 3 |

| SCF           | C ← 1                                   |                              |     | DF    | 1 | - | _ | _ | _ | -              | 1              | 2 |

| SRA dst       |                                         | R                            |     | D0    | * | * | * | 0 | _ | -              | 2              | 2 |

|               | $- D7 D6 D5 D4 D3 D2 D1 D0 - C^{-}$ dst | IR                           |     | D1    |   |   |   |   |   |                | 2              | 3 |

| SRL dst       | 0 - D7D6D5D4D3D2D1D0 - C                | R                            |     | 1F C0 | * | * | 0 | * | _ | _              | 3              | 2 |

|               | dst                                     | IR                           |     | 1F C1 |   |   |   |   |   |                | 3              | 3 |

| SRP src       | RP ← src                                |                              | IM  | 01    | _ | _ | _ | _ | _ | _              | 2              | 2 |

| STOP          | STOP Mode                               |                              |     | 6F    | _ | _ | _ | _ | _ | _              | 1              | 2 |

## Table 128. eZ8 CPU Instruction Summary (Continued)

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

219

|                                                        | V <sub>DE</sub>                                                                                                                                                                                          | o = 2.7 V to 3                                                                                                                                                                                                      | 3.6 V                                                                                                                                                                                                                          |                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                              | Typical <sup>1</sup>                                                                                                                                                                                     |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                | Units                                                                                                                                                                                            | Conditions                                                                                                                                                                                                                                                                                                                      |

| ADC Internal Ref-<br>erence Supply Cur-<br>rent        | 0                                                                                                                                                                                                        |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                | μA                                                                                                                                                                                               | See Note 4.                                                                                                                                                                                                                                                                                                                     |

| Comparator sup-<br>ply Current                         | 150                                                                                                                                                                                                      | 180                                                                                                                                                                                                                 | 190                                                                                                                                                                                                                            | μA                                                                                                                                                                                               | See Note 4.                                                                                                                                                                                                                                                                                                                     |

| Low-Power Opera-<br>tional Amplifier<br>Supply Current | 3                                                                                                                                                                                                        | 5                                                                                                                                                                                                                   | 5                                                                                                                                                                                                                              | μA                                                                                                                                                                                               | Driving a high-impedance load                                                                                                                                                                                                                                                                                                   |

| Temperature Sen-<br>sor Supply Current                 | 60                                                                                                                                                                                                       |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                | μA                                                                                                                                                                                               | See Note 4.                                                                                                                                                                                                                                                                                                                     |

| Band Gap Supply                                        | 320                                                                                                                                                                                                      | 480                                                                                                                                                                                                                 | 500                                                                                                                                                                                                                            | μA                                                                                                                                                                                               | For 20-/28-pin devices.                                                                                                                                                                                                                                                                                                         |

| Current                                                |                                                                                                                                                                                                          |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                |                                                                                                                                                                                                  | For 8-pin devices.                                                                                                                                                                                                                                                                                                              |

|                                                        | ADC Internal Ref-<br>erence Supply Cur-<br>rent<br>Comparator sup-<br>ply Current<br>Low-Power Opera-<br>tional Amplifier<br>Supply Current<br>Temperature Sen-<br>sor Supply Current<br>Band Gap Supply | ParameterTypical1ADC Internal Ref-<br>erence Supply Cur-<br>rent0Comparator sup-<br>ply Current150Low-Power Opera-<br>tional Amplifier<br>Supply Current3Temperature Sen-<br>sor Supply Current60Band Gap Supply320 | ParameterTypical1Maximum<br>Std Temp2ADC Internal Ref-<br>erence Supply Cur-<br>rent0150180Comparator sup-<br>ply Current150180Low-Power Opera-<br>tional Amplifier<br>Supply Current35Supply Current6050Band Gap Supply320480 | ADC Internal Ref-<br>erence Supply Cur-<br>rent<br>Comparator sup-<br>ply Current<br>Low-Power Opera-<br>Supply Current<br>Temperature Sen-<br>sor Supply Current<br>Band Gap Supply 320 480 500 | ParameterTypical <sup>1</sup> Maximum<br>Std Temp <sup>2</sup> Maximum<br>Ext Temp <sup>3</sup> UnitsADC Internal Ref-<br>erence Supply Cur-<br>rent0μAComparator sup-<br>ply Current150180190μALow-Power Opera-<br>tional Amplifier<br>Supply Current355μATemperature Sen-<br>sor Supply Current60μABand Gap Supply320480500μA |

#### Table 132. Power Consumption (Continued)

Notes:

1. Typical conditions are defined as  $V_{DD} = 3.3 V$  and  $+30^{\circ}C$ .

2. Standard temperature is defined as  $T_A = 0^{\circ}C$  to +70°C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

3. Extended temperature is defined as  $T_A = -40^{\circ}$ C to +105°C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

4. For this block to operate, the bandgap circuit is automatically turned on and must be added to the total supply current. This bandgap current is only added once, regardless of how many peripherals are using it.