Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | eZ8                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 20MHz                                                        |

| Connectivity               | IrDA, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, Temp Sensor, WDT |

| Number of I/O              | 23                                                           |

| Program Memory Size        | 2KB (2K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 64 x 8                                                       |

| RAM Size                   | 512 x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 8x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | 0°C ~ 70°C (TA)                                              |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                               |

| Supplier Device Package    | -                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f022asj020sg    |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

operate in ONE-SHOT, CONTINUOUS, GATED, CAPTURE, CAPTURE RESTART, COMPARE, CAPTURE and COMPARE, PWM SINGLE OUTPUT and PWM DUAL OUTPUT modes.

### **General-Purpose Input/Output**

The Product Line MCUs feature 6 to 25 port pins (Ports A–D) for general- purpose input/ output (GPIO). The number of GPIO pins available is a function of package and each pin is individually programmable. 5 V tolerant input pins are available on all I/Os on 8-pin devices and most I/Os on other package types.

#### **Direct LED Drive**

The 20- and 28-pin devices support controlled current sinking output pins capable of driving LEDs without the need for a current limiting resistor. These LED drivers are independently programmable to four different intensity levels.

### **Flash Controller**

The Flash Controller programs and erases Flash memory. The Flash Controller supports several protection mechanisms against accidental program and erasure, plus factory serialization and read protection.

### Non-Volatile Data Storage

The nonvolatile data storage (NVDS) uses a hybrid hardware/software scheme to implement a byte programmable data memory and is capable of over 100,000 write cycles.

**Note:** Devices with 8KB of Flash memory do not include the NVDS feature.

#### Interrupt Controller

The Z8 Encore! XP F082A Series products support up to 20 interrupts. These interrupts consist of 8 internal peripheral interrupts and 12 general-purpose I/O pin interrupt sources. The interrupts have three levels of programmable interrupt priority.

#### **Reset Controller**

The Z8 Encore! XP F082A Series products can be reset using the RESET pin, Power-On Reset, Watchdog Timer (WDT) time-out, STOP Mode exit, or Voltage Brown-Out (VBO)

|                                                       | Reset Characteristics and Latency                      |            |                                                               |  |  |  |  |

|-------------------------------------------------------|--------------------------------------------------------|------------|---------------------------------------------------------------|--|--|--|--|

| Reset Type                                            | Control Registers                                      | eZ8<br>CPU | Reset Latency (Delay)                                         |  |  |  |  |

| System Reset                                          | Reset (as applicable)                                  | Reset      | 66 Internal Precision Oscillator Cycles                       |  |  |  |  |

| System Reset with Crystal Oscillator Enabled          | Reset (as applicable)                                  | Reset      | 5000 Internal Precision Oscillator Cycles                     |  |  |  |  |

| Stop Mode Recovery                                    | Unaffected, except<br>WDT_CTL and<br>OSC_CTL registers | Reset      | 66 Internal Precision Oscillator Cycles<br>+ IPO startup time |  |  |  |  |

| Stop Mode Recovery with<br>Crystal Oscillator Enabled | Unaffected, except<br>WDT_CTL and<br>OSC_CTL registers | Reset      | 5000 Internal Precision Oscillator Cycles                     |  |  |  |  |

#### Table 8. Reset and Stop Mode Recovery Characteristics and Latency

During a System Reset or Stop Mode Recovery, the Internal Precision Oscillator requires 4  $\mu$ s to start up. Then the Z8 Encore! XP F082A Series device is held in Reset for 66 cycles of the Internal Precision Oscillator. If the crystal oscillator is enabled in the Flash option bits, this reset period is increased to 5000 IPO cycles. When a reset occurs because of a low voltage condition or Power-On Reset (POR), this delay is measured from the time that the supply voltage first exceeds the POR level. If the external pin reset remains asserted at the end of the reset period, the device remains in reset until the pin is deasserted.

At the beginning of Reset, all GPIO pins are configured as inputs with pull-up resistor disabled, except PD0 (or PA2 on 8-pin devices) which is shared with the reset pin. On reset, the PD0 is configured as a bidirectional open-drain reset. The pin is internally driven low during port reset, after which the user code may reconfigure this pin as a general purpose output.

During Reset, the eZ8 CPU and on-chip peripherals are idle; however, the on-chip crystal oscillator and Watchdog Timer oscillator continue to run.

Upon Reset, control registers within the Register File that have a defined Reset value are loaded with their reset values. Other control registers (including the Stack Pointer, Register Pointer and Flags) and general-purpose RAM are undefined following Reset. The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset vector address.

As the control registers are reinitialized by a system reset, the system clock after reset is always the IPO. The software must reconfigure the oscillator control block, such that the correct system clock source is enabled and selected.

operational amplifier (LPO) is OFF. To use the LPO, clear the LPO bit, turning it ON. Clearing this bit might interfere with normal ADC measurements on ANA0 (the LPO output). This bit enables the amplifier even in STOP Mode. If the amplifier is not required in STOP Mode, disable it. Failure to perform this results in STOP Mode currents greater than specified.

**Note:** This register is only reset during a POR sequence. Other system reset events do not affect it.

| Bit         | 7                                                                                                                              | 6                                            | 5          | 4   | 3           | 2            | 1            | 0             |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|------------|-----|-------------|--------------|--------------|---------------|--|

| Field       | LPO                                                                                                                            | Rese                                         | erved      | VBO | TEMP        | ADC          | COMP         | Reserved      |  |

| RESET       | 1                                                                                                                              | 0                                            | 0          | 0   | 0           | 0            | 0            | 0             |  |

| R/W         | R/W                                                                                                                            | R/W                                          | R/W        | R/W | R/W         | R/W          | R/W          | R/W           |  |

| Address     |                                                                                                                                |                                              |            | F8  | ОH          |              | •            | ·             |  |

| Bit         | Description                                                                                                                    |                                              |            |     |             |              |              |               |  |

| [7]<br>LPO  | <b>Low-Power Operational Amplifier Disable</b><br>0 = LPO is enabled (this applies even in STOP Mode).<br>1 = LPO is disabled. |                                              |            |     |             |              |              |               |  |

| [6:5]       | <b>Reserved</b><br>These bits are reserved and must be programmed to 00.                                                       |                                              |            |     |             |              |              |               |  |

| [4]<br>VBO  |                                                                                                                                | nabled.                                      |            |     | both enable | e the VBO fo | or the VBO t | to be active. |  |

| [3]<br>TEMP | 0 = Temper                                                                                                                     | ature Sensor I<br>ature Senso<br>ature Senso | r enabled. |     |             |              |              |               |  |

| [2]<br>ADC  | Analog-to-Digital Converter Disable<br>0 = Analog-to-Digital Converter enabled.<br>1 = Analog-to-Digital Converter disabled.   |                                              |            |     |             |              |              |               |  |

| [1]<br>COMP | Comparator Disable<br>0 = Comparator is enabled.<br>1 = Comparator is disabled.                                                |                                              |            |     |             |              |              |               |  |

| [0]         | Reserved         This bit is reserved and must be programmed to 0.                                                             |                                              |            |     |             |              |              |               |  |

#### Table 13. Power Control Register 0 (PWRCTL0)

| Bit     | 7           | 6                                                                                     | 5    | 4    | 3    | 2    | 1    | 0    |  |

|---------|-------------|---------------------------------------------------------------------------------------|------|------|------|------|------|------|--|

| Field   | POC7        | POC6                                                                                  | POC5 | POC4 | POC3 | POC2 | POC1 | POC0 |  |

| RESET   |             | 00H (Ports A-C); 01H (Port D)                                                         |      |      |      |      |      |      |  |

| R/W     | R/W         | R/W                                                                                   | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |  |

| Address | If 03H ii   | If 03H in Port A–D Address Register, accessible through the Port A–D Control Register |      |      |      |      |      |      |  |

| D:4     | Decertation |                                                                                       |      |      |      |      |      |      |  |

#### Table 23. Port A–D Output Control Subregisters (PxOC)

| Bit   | Description                                                                                                                |

|-------|----------------------------------------------------------------------------------------------------------------------------|

| [7:0] | Port Output Control                                                                                                        |

| POCx  | These bits function independently of the alternate function bit and always disable the drains if set to 1.                 |

|       | 0 = The source current is enabled for any output mode unless overridden by the alternate func-<br>tion (push-pull output). |

|       | 1 = The source current for the associated pin is disabled (open-drain mode).                                               |

#### Port A–D High Drive Enable Subregisters

The Port A–D High Drive Enable Subregister, shown in Table 24, is accessed through the port A–D Control Register by writing 04H to the Port A–D Address Register. Setting the bits in the Port A–D High Drive Enable subregisters to 1 configures the specified port pins for high current output drive operation. The Port A–D High Drive Enable subregister affects the pins directly and, as a result, alternate functions are also affected.

| Bit     | 7         | 6                                                                                     | 5     | 4     | 3     | 2     | 1     | 0     |  |

|---------|-----------|---------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|--|

| Field   | PHDE7     | PHDE6                                                                                 | PHDE5 | PHDE4 | PHDE3 | PHDE2 | PHDE1 | PHDE0 |  |

| RESET   | 0         | 0                                                                                     | 0     | 0     | 0     | 0     | 0     | 0     |  |

| R/W     | R/W       | R/W                                                                                   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |  |

| Address | lf 04H ir | If 04H in Port A–D Address Register, accessible through the Port A–D Control Register |       |       |       |       |       |       |  |

Table 24. Port A–D High Drive Enable Subregisters (PxHDE)

| Bit        | Description                                                       |  |  |  |  |  |

|------------|-------------------------------------------------------------------|--|--|--|--|--|

| [7:0]      | Port High Drive Enabled                                           |  |  |  |  |  |

| PHDEx      | 0 = The port pin is configured for standard output current drive. |  |  |  |  |  |

|            | 1 = The port pin is configured for high output current drive.     |  |  |  |  |  |

| Note: x in | Note: x indicates the specific GPIO port pin number (7–0).        |  |  |  |  |  |

## LED Drive Level Low Register

The LED Drive Level registers contain two control bits for each Port C pin (Table 33). These two bits select between four programmable drive levels. Each pin is individually programmable.

| Bit     | 7            | 6    | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------|--------------|------|-----|-----|-----|-----|-----|-----|--|

| Field   | LEDLVLL[7:0] |      |     |     |     |     |     |     |  |

| RESET   | 0            | 0    | 0   | 0   | 0   | 0   | 0   | 0   |  |

| R/W     | R/W          | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address |              | F84H |     |     |     |     |     |     |  |

#### Table 33. LED Drive Level Low Register (LEDLVLL)

| Bit           | Description                                                                             |

|---------------|-----------------------------------------------------------------------------------------|

| [7:0]         | LED Level Low Bit                                                                       |

| LEDLVLLx      | {LEDLVLH, LEDLVLL} select one of four programmable current drive levels for each Port C |

|               | pin.                                                                                    |

|               | 00 = 3mA                                                                                |

|               | 01 = 7 mA                                                                               |

|               | 10 = 13mA                                                                               |

|               | 11 = 20mA                                                                               |

| Note: x indic | cates the specific GPIO port pin number (7–0).                                          |

# **GPIO Mode Interrupt Controller**

The interrupt controller on the Z8 Encore! XP F082A Series products prioritizes the interrupt requests from the on-chip peripherals and the GPIO port pins. The features of interrupt controller include:

- 20 possible interrupt sources with 18 unique interrupt vectors:

- Twelve GPIO port pin interrupt sources (two interrupt vectors are shared)

- Eight on-chip peripheral interrupt sources (two interrupt vectors are shared)

- Flexible GPIO interrupts:

- Eight selectable rising and falling edge GPIO interrupts

- Four dual-edge interrupts

- Three levels of individually programmable interrupt priority

- Watchdog Timer and LVD can be configured to generate an interrupt

- Supports vectored and polled interrupts

Interrupt requests (IRQs) allow peripheral devices to suspend CPU operation in an orderly manner and force the CPU to start an interrupt service routine (ISR). Usually this interrupt service routine is involved with the exchange of data, status information, or control information between the CPU and the interrupting peripheral. When the service routine is completed, the CPU returns to the operation from which it was interrupted.

The eZ8 CPU supports both vectored and polled interrupt handling. For polled interrupts, the interrupt controller has no effect on operation. For more information about interrupt servicing by the eZ8 CPU, refer to the <u>eZ8 CPU Core User Manual (UM0128)</u>, which is available for download on <u>www.zilog.com</u>.

## **Interrupt Vector Listing**

Table 34 lists all of the interrupts available in order of priority. The interrupt vector is stored with the most-significant byte (MSB) at the even Program Memory address and the least-significant byte (LSB) at the following odd Program Memory address.

**Note:** Some port interrupts are not available on the 8- and 20-pin packages. The ADC interrupt is unavailable on devices not containing an ADC.

## **Interrupt Request 2 Register**

The Interrupt Request 2 (IRQ2) Register, shown in Table 37, stores interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ2 Register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 2 Register to determine if any interrupt requests are pending.

| Bit     | 7        | 6    | 5   | 4   | 3    | 2    | 1    | 0    |

|---------|----------|------|-----|-----|------|------|------|------|

| Field   | Reserved |      |     |     | PC3I | PC2I | PC1I | PC0I |

| RESET   | 0        | 0    | 0   | 0   | 0    | 0    | 0    | 0    |

| R/W     | R/W      | R/W  | R/W | R/W | R/W  | R/W  | R/W  | R/W  |

| Address |          | FC6H |     |     |      |      |      |      |

| Table 37. | Interrupt | Request 2 | Register | (IRQ2) |

|-----------|-----------|-----------|----------|--------|

|-----------|-----------|-----------|----------|--------|

| Bit     | Description                                                          |  |

|---------|----------------------------------------------------------------------|--|

| [7:4]   | Reserved                                                             |  |

|         | These bits are reserved and must be programmed to 0000.              |  |

| [3:0]   | Port C Pin <i>x</i> Interrupt Request                                |  |

| PCxI    | 0 = No interrupt request is pending for GPIO Port C pin $x$ .        |  |

|         | 1 = An interrupt request from GPIO Port C pin x is awaiting service. |  |

| Note: x | c indicates the specific GPIO Port C pin number (0–3).               |  |

## **IRQ0 Enable High and Low Bit Registers**

Table 38 describes the priority control for IRQ0. The IRQ0 Enable High and Low Bit registers, shown in Tables 39 and 40, form a priority-encoded enabling for interrupts in the Interrupt Request 0 Register.

| IRQ0ENH[x]        | IRQ0ENL[x]        | Priority | Description |

|-------------------|-------------------|----------|-------------|

| 0                 | 0                 | Disabled | Disabled    |

| 0                 | 1                 | Level 1  | Low         |

| 1                 | 0                 | Level 2  | Medium      |

| 1                 | 1                 | Level 3  | High        |

| Note: x indicates | register bits 0-7 |          |             |

Table 38. IRQ0 Enable and Priority Encoding

| Bit     | 7       | 6       | 5      | 4      | 3             | 2      | 1      | 0      |  |  |  |

|---------|---------|---------|--------|--------|---------------|--------|--------|--------|--|--|--|

| Field   | PA7VENH | PA6CENH | PA5ENH | PA4ENH | <b>PA3ENH</b> | PA2ENH | PA1ENH | PA0ENH |  |  |  |

| RESET   | 0       | 0       | 0      | 0      | 0             | 0      | 0      | 0      |  |  |  |

| R/W     | R/W     | R/W     | R/W    | R/W    | R/W           | R/W    | R/W    | R/W    |  |  |  |

| Address |         | FC4H    |        |        |               |        |        |        |  |  |  |

| Bit             | Description                                                   |

|-----------------|---------------------------------------------------------------|

| [7]<br>PA7VENH  | Port A Bit[7] or LVD Interrupt Request Enable High Bit        |

| [6]<br>PA6CENH  | Port A Bit[7] or Comparator Interrupt Request Enable High Bit |

| [5:0]<br>PAxENH | Port A Bit[ <i>x</i> ] Interrupt Request Enable High Bit      |

See the <u>Shared Interrupt Select Register (IRQSS) Register</u> on page 68 for selection of either the LVD or the comparator as the interrupt source.

| Bit     | 7       | 6       | 5      | 4      | 3             | 2      | 1      | 0      |  |  |

|---------|---------|---------|--------|--------|---------------|--------|--------|--------|--|--|

| Field   | PA7VENL | PA6CENL | PA5ENL | PA4ENL | <b>PA3ENL</b> | PA2ENL | PA1ENL | PA0ENL |  |  |

| RESET   | 0       | 0       | 0      | 0      | 0             | 0      | 0      | 0      |  |  |

| R/W     | R/W     | R/W     | R/W    | R/W    | R/W           | R/W    | R/W    | R/W    |  |  |

| Address | FC5H    |         |        |        |               |        |        |        |  |  |

| Bit             | Description                                                  |

|-----------------|--------------------------------------------------------------|

| [7]<br>PA7VENL  | Port A Bit[7] or LVD Interrupt Request Enable Low Bit        |

| [6]<br>PA6CENL  | Port A Bit[6] or Comparator Interrupt Request Enable Low Bit |

| [5:0]<br>PAxENL | Port A Bit[x] Interrupt Request Enable Low Bit               |

### **IRQ2 Enable High and Low Bit Registers**

Table 44 describes the priority control for IRQ2. The IRQ2 Enable High and Low Bit registers, shown in Tables 44 and 45, form a priority-encoded enabling for interrupts in the Interrupt Request 2 Register.

66

| IRQ2ENH[ <i>x</i> ] | IRQ2ENL[x] | Priority | Description |

|---------------------|------------|----------|-------------|

| 0                   | 0          | Disabled | Disabled    |

| 0                   | 1          | Level 1  | Low         |

| 1                   | 0          | Level 2  | Medium      |

| 1                   | 1          | Level 3  | High        |

#### Table 44. IRQ2 Enable and Priority Encoding

#### Table 45. IRQ2 Enable High Bit Register (IRQ2ENH)

| Bit     | 7        | 6   | 5   | 4   | 3     | 2     | 1     | 0     |

|---------|----------|-----|-----|-----|-------|-------|-------|-------|

| Field   | Reserved |     |     |     | C3ENH | C2ENH | C1ENH | C0ENH |

| RESET   | 0        | 0   | 0   | 0   | 0     | 0     | 0     | 0     |

| R/W     | R/W      | R/W | R/W | R/W | R/W   | R/W   | R/W   | R/W   |

| Address |          |     |     | FC  | 7H    |       |       |       |

| Bit          | Description                                                                |

|--------------|----------------------------------------------------------------------------|

| [7:4]        | <b>Reserved</b><br>These bits are reserved and must be programmed to 0000. |

| [3]<br>C3ENH | Port C3 Interrupt Request Enable High Bit                                  |

| [2]<br>C2ENH | Port C2 Interrupt Request Enable High Bit                                  |

| [1]<br>C1ENH | Port C1 Interrupt Request Enable High Bit                                  |

| [0]<br>C0ENH | Port C0 Interrupt Request Enable High Bit                                  |

it is appropriate to have the Timer Output make a state change at a One-Shot time-out (rather than a single cycle pulse), first set the TPOL bit in the Timer Control Register to the start value before enabling ONE-SHOT Mode. After starting the timer, set TPOL to the opposite bit value.

Observe the following steps for configuring a timer for ONE-SHOT Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for ONE-SHOT Mode.

- Set the prescale value.

- Set the initial output level (High or Low) if using the Timer Output alternate function.

- 2. Write to the Timer High and Low Byte registers to set the starting count value.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 6. Write to the Timer Control Register to enable the timer and initiate counting.

In ONE-SHOT Mode, the system clock always provides the timer input. The timer period is computed via the following equation:

$ONE-SHOT \text{ Mode Time-Out Period } (s) = \frac{\text{Reload Value} - \text{Start Value} \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$

#### **CONTINUOUS Mode**

In CONTINUOUS Mode, the timer counts up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer Reload.

Observe the following steps for configuring a timer for CONTINUOUS Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CONTINUOUS Mode

| Bit               | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [6:5]<br>TICONFIG | <ul> <li>Timer Interrupt Configuration</li> <li>This field configures timer interrupt definition.</li> <li>0x = Timer Interrupt occurs on all defined Reload, Compare and Input Events.</li> <li>10 = Timer Interrupt only on defined Input Capture/Deassertion Events.</li> <li>11 = Timer Interrupt only on defined Reload/Compare Events.</li> </ul>                                                             |

| [4]               | <b>Reserved</b><br>This bit is reserved and must be programmed to 0.                                                                                                                                                                                                                                                                                                                                                |

| [3:1]<br>PWMD     | <b>PWM Delay Value</b><br>This field is a programmable delay to control the number of system clock cycles delay<br>before the Timer Output and the Timer Output Complement are forced to their active state.<br>000 = No delay.<br>001 = 2 cycles delay.<br>010 = 4 cycles delay.<br>011 = 8 cycles delay.<br>100 = 16 cycles delay.<br>101 = 32 cycles delay.<br>101 = 64 cycles delay.<br>111 = 128 cycles delay. |

| [0]<br>INPCAP     | <ul> <li>Input Capture Event</li> <li>This bit indicates if the most recent timer interrupt is caused by a Timer Input Capture Event.</li> <li>0 = Previous timer interrupt is not a result of Timer Input Capture Event.</li> <li>1 = Previous timer interrupt is a result of Timer Input Capture Event.</li> </ul>                                                                                                |

#### Timer 0–1 Control Register 1

The Timer 0–1 Control (TxCTL1) registers, shown in Table 51, enable and disable the timers, set the prescaler value and determine the timer operating mode.

| Bit     | 7          | 6    | 5          | 4   | 3   | 2   | 1   | 0   |  |  |

|---------|------------|------|------------|-----|-----|-----|-----|-----|--|--|

| Field   | TEN        | TPOL | PRES TMODE |     |     |     |     |     |  |  |

| RESET   | 0          | 0    | 0          | 0   | 0   | 0   | 0   | 0   |  |  |

| R/W     | R/W        | R/W  | R/W        | R/W | R/W | R/W | R/W | R/W |  |  |

| Address | F07H, F0FH |      |            |     |     |     |     |     |  |  |

| Table 51. Timer 0- | -1 Control | Register 1 | (TxCTL1) |

|--------------------|------------|------------|----------|

|--------------------|------------|------------|----------|

| Bit | Description |  |

|-----|-------------|--|

|     |             |  |

- Timer Enable [7] TEN

- 0 = Timer is disabled.

- 1 = Timer enabled to count.

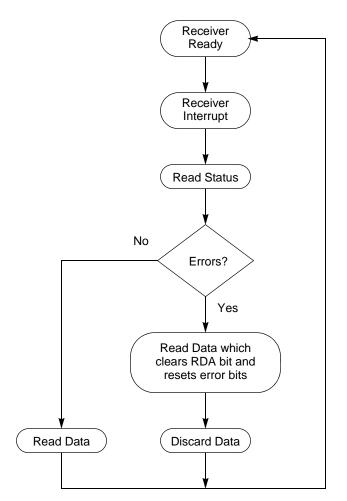

byte indicating an overrun error, the Receive Data Register must be read again to clear the error bits is the UART Status 0 Register. Updates to the Receive Data Register occur only when the next data word is received.

#### **UART Data and Error Handling Procedure**

Figure 15 displays the recommended procedure for use in UART receiver interrupt service routines.

Figure 15. UART Receiver Interrupt Service Routine Flow

#### **Baud Rate Generator Interrupts**

If the baud rate generator (BRG) interrupt enable is set, the UART Receiver interrupt asserts when the UART Baud Rate Generator reloads. This condition allows the Baud

## **UART Status 0 Register**

The UART Status 0 (UxSTAT0) and Status 1(UxSTAT1) registers, shown in Tables 65 and 66, identify the current UART operating configuration and status.

| Table 65. | UART | Status 0 | Register | (U0STAT0) |

|-----------|------|----------|----------|-----------|

|-----------|------|----------|----------|-----------|

| Bit         | 7                                                                                                                                                                                                                                                                                                                                              | 6 5 4 3 2 1                                                                                                                                                                                                                                                              |                                                                            |             |                                            |            |             | 0        |  |  |  |  |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------|--------------------------------------------|------------|-------------|----------|--|--|--|--|--|

| Field       | RDA                                                                                                                                                                                                                                                                                                                                            | PE                                                                                                                                                                                                                                                                       | OE                                                                         | FE          | BRKD                                       | TDRE       | TXE         | CTS      |  |  |  |  |  |

| RESET       | 0                                                                                                                                                                                                                                                                                                                                              | 0                                                                                                                                                                                                                                                                        | 0                                                                          | 0           | 0                                          | 1          | 1           | Х        |  |  |  |  |  |

| R/W         | R                                                                                                                                                                                                                                                                                                                                              | R                                                                                                                                                                                                                                                                        | R                                                                          | R           | R                                          | R          | R           | R        |  |  |  |  |  |

| Address     | F41H                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                          |                                                                            |             |                                            |            |             |          |  |  |  |  |  |

| Bit         | Description                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                          |                                                                            |             |                                            |            |             |          |  |  |  |  |  |

| [7]<br>RDA  | This bit indi<br>Receive Da<br>0 = The UA                                                                                                                                                                                                                                                                                                      | Receive Data Available<br>This bit indicates that the UART Receive Data Register has received data. Reading the UART<br>Receive Data Register clears this bit.<br>0 = The UART Receive Data Register is empty.<br>1 = There is a byte in the UART Receive Data Register. |                                                                            |             |                                            |            |             |          |  |  |  |  |  |

| [6]<br>PE   | clears this b<br>0 = No parit                                                                                                                                                                                                                                                                                                                  | cates that a<br>bit.                                                                                                                                                                                                                                                     | occurred.                                                                  | has occurre | d. Reading t                               | the UART R | eceive Data | Register |  |  |  |  |  |

| [5]<br>OE   | received an<br>reading the<br>0 = No over                                                                                                                                                                                                                                                                                                      | cates that a<br>d the UART<br>UART Rece                                                                                                                                                                                                                                  | Receive Date Receive Date Receive Data Receive Data Receive Data Received. |             | urred. An ov<br>has not bee<br>s this bit. |            |             |          |  |  |  |  |  |

| [4]<br>FE   | Framing Error<br>This bit indicates that a framing error (no Stop bit following data reception) was detected.<br>Reading the UART Receive Data Register clears this bit.<br>0 = No framing error occurred.<br>1 = A framing error occurred.                                                                                                    |                                                                                                                                                                                                                                                                          |                                                                            |             |                                            |            |             |          |  |  |  |  |  |

| [3]<br>BRKD | <ul> <li>1 = A framing error occurred.</li> <li>Break Detect</li> <li>This bit indicates that a break occurred. If the data bits, parity/multiprocessor bit and Stop bit(s) are all 0s this bit is set to 1. Reading the UART Receive Data Register clears this bit.</li> <li>0 = No break occurred.</li> <li>1 = A break occurred.</li> </ul> |                                                                                                                                                                                                                                                                          |                                                                            |             |                                            |            |             |          |  |  |  |  |  |

The ADC registers actually return 13 bits of data, but the two LSBs are intended for compensation use only. When the software compensation routine is performed on the 13 bit raw ADC value, two bits of resolution are lost because of a rounding error. As a result, the final value is an 11-bit number.

### Hardware Overflow

When the hardware overflow bit (OVF) is set in ADC Data Low Byte (ADCD\_L) Register, all other data bits are invalid. The hardware overflow bit is set for values greater than  $V_{REF}$  and less than  $-V_{REF}$  (DIFFERENTIAL Mode).

## Automatic Powerdown

If the ADC is idle (no conversions in progress) for 160 consecutive system clock cycles, portions of the ADC are automatically powered down. From this powerdown state, the ADC requires 40 system clock cycles to power up. The ADC powers up when a conversion is requested by the ADC Control Register.

## Single-Shot Conversion

When configured for single-shot conversion, the ADC performs a single analog-to-digital conversion on the selected analog input channel. After completion of the conversion, the ADC shuts down. Observe the following steps for setting up the ADC and initiating a single-shot conversion:

- 1. Enable the appropriate analog inputs by configuring the general-purpose I/O pins for alternate analog function. This configuration disables the digital input and output drivers.

- 2. Write the ADC Control/Status Register 1 to configure the ADC.

- Write to BUFMODE[2:0] to select SINGLE-ENDED or DIFFERENTIAL mode, plus unbuffered or buffered mode.

- Write the REFSELH bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELL bit is. contained in the ADC Control Register 0.

- 3. Write to the ADC Control Register 0 to configure the ADC and begin the conversion. The bit fields in the ADC Control Register can be written simultaneously (the ADC can be configured and enabled with the same write instruction):

- Write to the ANAIN[3:0] field to select from the available analog input sources (different input pins available depending on the device).

- Clear CONT to 0 to select a single-shot conversion.

**Caution:** The byte at each address of the Flash memory cannot be programmed (any bits written to 0) more than twice before an erase cycle occurs. Doing so may result in corrupted data at the target byte.

### **Page Erase**

The Flash memory can be erased one page (512 bytes) at a time. Page Erasing the Flash memory sets all bytes in that page to the value FFH. The Flash Page Select Register identifies the page to be erased. Only a page residing in an unprotected sector can be erased. With the Flash Controller unlocked and the active page set, writing the value 95h to the Flash Control Register initiates the Page Erase operation. While the Flash Controller executes the Page Erase operation, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. The eZ8 CPU resumes operation after the Page Erase operation completes. If the Page Erase operation is performed using the On-Chip Debugger, poll the Flash Status Register to determine when the Page Erase operation is complete. When the Page Erase is complete, the Flash Controller returns to its locked state.

#### **Mass Erase**

The Flash memory can also be Mass Erased using the Flash Controller, but only by using the On-Chip Debugger. Mass Erasing the Flash memory sets all bytes to the value FFH. With the Flash Controller unlocked and the Mass Erase successfully enabled, writing the value 63H to the Flash Control Register initiates the Mass Erase operation. While the Flash Controller executes the Mass Erase operation, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. Using the On-Chip Debugger, poll the Flash Status Register to determine when the Mass Erase operation is complete. When the Mass Erase is complete, the Flash Controller returns to its locked state.

### **Flash Controller Bypass**

The Flash Controller can be bypassed and the control signals for the Flash memory brought out to the GPIO pins. Bypassing the Flash Controller allows faster Row Programming algorithms by controlling the Flash programming signals directly.

Row programming is recommended for gang programming applications and large volume customers who do not require in-circuit initial programming of the Flash memory. Page Erase operations are also supported when the Flash Controller is bypassed.

For more information about bypassing the Flash Controller, refer to the <u>Third-Party Flash</u> <u>Programming Support for Z8 Encore! MCUs Application Note (AN0117)</u>, which is available for download on <u>www.zilog.com</u>.

## **Trim Bit Address Space**

All available Trim bit addresses and their functions are listed in Table 90 through Table 95.

## Trim Bit Address 0000H

| Bit                                             | 7          | 6                       | 5     | 4           | 3           | 2    | 1 | 0 |  |  |  |  |

|-------------------------------------------------|------------|-------------------------|-------|-------------|-------------|------|---|---|--|--|--|--|

| Field                                           | Reserved   |                         |       |             |             |      |   |   |  |  |  |  |

| RESET                                           |            |                         |       |             |             |      |   | U |  |  |  |  |

| R/W                                             | R/W        | 2/W R/W R/W R/W R/W R/W |       | R/W         | R/W         | R/W  |   |   |  |  |  |  |

| Address                                         |            |                         | Infor | mation Page | e Memory 00 | )20H |   |   |  |  |  |  |

| Note: U = Unchanged by Reset. R/W = Read/Write. |            |                         |       |             |             |      |   |   |  |  |  |  |

| Bit                                             | Descriptio | Description             |       |             |             |      |   |   |  |  |  |  |

| [7:0]                                           | Reserved   | Reserved                |       |             |             |      |   |   |  |  |  |  |

#### Table 90. Trim Options Bits at Address 0000H

These bits are reserved; altering this register may result in incorrect device operation.

## Trim Bit Address 0001H

#### Table 91. Trim Option Bits at 0001H

| Bit                                             | 7                             | 6   | 5       | 4   | 3   | 2   | 1   | 0   |  |  |  |  |

|-------------------------------------------------|-------------------------------|-----|---------|-----|-----|-----|-----|-----|--|--|--|--|

| Field                                           | Reserved                      |     |         |     |     |     |     |     |  |  |  |  |

| RESET                                           | U                             | U   | U U U U |     |     |     | U   | U   |  |  |  |  |

| R/W                                             | R/W                           | R/W | R/W     | R/W | R/W | R/W | R/W | R/W |  |  |  |  |

| Address                                         | Information Page Memory 0021H |     |         |     |     |     |     |     |  |  |  |  |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                               |     |         |     |     |     |     |     |  |  |  |  |

## Bit Description [7:0] Reserved These bits are reserved; altering this register may result in incorrect device operation.

Unlock and write Oscillator Control

Register (OSCCTL) to enable and

select oscillator at either 5.53MHz or

• Configure Flash option bits for correct

Unlock and write OSCCTL to enable

crystal oscillator, wait for it to stabilize and select as system clock (if the XTLDIS option bit has been deasserted, no waiting is required)

Configure Flash option bits for correct

Unlock and write OSCCTL to enable crystal oscillator and select as system

• Write GPIO registers to configure PB3

Unlock and write OSCCTL to select

Apply external clock signal to GPIO

· Enable WDT if not enabled and wait

until WDT Oscillator is operating Unlock and write Oscillator Control

pin for external clock function

external system clock

external oscillator mode

external oscillator mode

| Very low power consumption                                                                                                                        | Register (OSCCTL) to enable and select oscillator |

|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

|                                                                                                                                                   |                                                   |

| <b>Caution:</b> Unintentional accesses to the Oscillator C switching to a nonfunctioning oscillator. T block employs a register unlocking/locking | To prevent this condition, the oscillator con     |

| OSC Control Register Unlocking/L                                                                                                                  | _ocking                                           |

| To write the Oscillator Control Register, unl<br>Register with the values E7H followed by 11<br>changes the value of the actual register and r    | 8H. A third write to the OSCCTL Register          |

**Required Setup**

32.8kHz

clock

> s to the OSCCTL CTL Register ed state. Any other sequence of Oscillator Control Register writes has no effect. The values written to unlock the register must be ordered correctly, but are not necessarily consecutive. It is possible to write to or read from other registers within the unlocking/locking operation.

**Clock Source**

**RC** Oscillator

Internal Precision

External Crystal/

External Clock

Internal Watchdog

Timer Oscillator

Resonator

tor

Drive

Characteristics

High accuracy

• 32kHz to 20MHz

ponents

0 to 20MHz

• 10kHz nominal

nents required

source

•

External RC Oscilla- • 32kHz to 4MHz

• 32.8kHz or 5.53MHz

No external components required

Very high accuracy (dependent on

· Accuracy dependent on external com-

Accuracy dependent on external clock

Low accuracy; no external compo-

crystal or resonator used)

Requires external components

221

| Assembly<br>Mnemonic |                                                                                                                        | Address<br>Mode |        | _ Opcode(s) | Flags |   |   |   |   |   | Fetch<br>Cycle | Instr.<br>Cycle |

|----------------------|------------------------------------------------------------------------------------------------------------------------|-----------------|--------|-------------|-------|---|---|---|---|---|----------------|-----------------|

|                      | Symbolic Operation                                                                                                     | dst             | src    | (Hex)       | С     | Ζ | S | ۷ | D | Н | S              | S               |

| TMX dst, src         | dst AND src                                                                                                            | ER              | ER     | 78          | -     | * | * | 0 | - | - | 4              | 3               |

|                      |                                                                                                                        | ER              | IM     | 79          |       |   |   |   |   |   | 4              | 3               |

| TRAP Vector          | $SP \leftarrow SP - 2$<br>@SP \leftarrow PC<br>$SP \leftarrow SP - 1$<br>@SP \leftarrow FLAGS<br>PC \leftarrow @Vector |                 | Vector | F2          | _     | - | - | - | - | _ | 2              | 6               |

| WDT                  |                                                                                                                        |                 |        | 5F          | _     | _ | _ | _ | _ | _ | 1              | 2               |

| XOR dst, src         | $dst \gets dst \ XOR \ src$                                                                                            | r               | r      | B2          | _     | * | * | 0 | _ | _ | 2              | 3               |

|                      |                                                                                                                        | r               | lr     | B3          | -     |   |   |   |   |   | 2              | 4               |

|                      |                                                                                                                        | R               | R      | B4          |       |   |   |   |   |   | 3              | 3               |

|                      |                                                                                                                        | R               | IR     | B5          | -     |   |   |   |   |   | 3              | 4               |

|                      |                                                                                                                        | R               | IM     | B6          | -     |   |   |   |   |   | 3              | 3               |

|                      |                                                                                                                        | IR              | IM     | B7          |       |   |   |   |   |   | 3              | 4               |

| XORX dst, src        | $dst \gets dst \ XOR \ src$                                                                                            | ER              | ER     | B8          | _     | * | * | 0 | _ | _ | 4              | 3               |

|                      |                                                                                                                        | ER              | IM     | B9          |       |   |   |   |   |   | 4              | 3               |

#### Table 128. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

– = Unaffected.

X = Undefined.

0 = Reset to 0.

1 =Set to 1.

## Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

260

LEA 210 load 210 load constant 209 load constant to/from program memory 210 load constant with auto-increment addresses 210 load effective address 210 load external data 210 load external data to/from data memory and autoincrement addresses 209 load external to/from data memory and auto-increment addresses 210 load using extended addressing 210 logical AND 210 logical AND/extended addressing 210 logical exclusive OR 210 logical exclusive OR/extended addressing 210 logical instructions 210 logical OR 210 logical OR/extended addressing 210 low power modes 32

## Μ

master interrupt enable 57 memory data 17 program 15 mode **CAPTURE 87, 88 CAPTURE/COMPARE 88** CONTINUOUS 87 COUNTER 87 GATED 88 **ONE-SHOT 87** PWM 87, 88 modes 87 **MULT 208** multiply 208 multiprocessor mode, UART 105

## Ν

NOP (no operation) 209 notation

## 0

b 206

cc 206

DA 206

ER 206

IM 206

IR 206

Ir 206

**IRR 206**

Irr 206

p 206

R 206

r 206

**RA 206**

**RR 206**

vector 207

notational shorthand 206

rr 206

X 207

OCD architecture 180 auto-baud detector/generator 183 baud rate limits 184 block diagram 180 breakpoints 185 commands 186 control register 191 data format 183 DBG pin to RS-232 Interface 181 debug mode 182 debugger break 211 interface 181 serial errors 184 status register 192 timing 242 OCD commands execute instruction (12H) 190 read data memory (0DH) 190 read OCD control register (05H) 188 read OCD revision (00H) 187 read OCD status register (02H) 187 read program counter (07H) 188

## Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

## Ζ

Z8 Encore! block diagram 3 features 1 part selection guide 2