Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, LVD, POR, PWM, WDT           |

| Number of I/O              | 17                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | 128 x 8                                                   |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f041ahh020eg |

| Trim Bit Address 0000H                           | 165 |

|--------------------------------------------------|-----|

| Trim Bit Address 0001H                           | 165 |

| Trim Bit Address 0002H                           | 166 |

| Trim Bit Address 0003H                           | 166 |

| Trim Bit Address 0004H                           | 168 |

| Zilog Calibration Data                           | 168 |

| ADC Calibration Data                             | 169 |

| Temperature Sensor Calibration Data              | 171 |

| Watchdog Timer Calibration Data                  | 172 |

| Serialization Data                               | 173 |

| Randomized Lot Identifier                        | 174 |

| Nonvolatile Data Storage                         | 176 |

| Operation                                        |     |

| NVDS Code Interface                              |     |

| Byte Write                                       | 177 |

| Byte Read                                        | 178 |

| Power Failure Protection                         |     |

| Optimizing NVDS Memory Usage for Execution Speed | 178 |

| On-Chip Debugger                                 | 180 |

| Architecture                                     |     |

| Operation                                        |     |

| OCD Interface                                    |     |

| DEBUG Mode                                       |     |

| OCD Data Format                                  |     |

| OCD Auto-Baud Detector/Generator                 |     |

| OCD Serial Errors                                |     |

| OCD Unlock Sequence (8-Pin Devices Only)         |     |

| Breakpoints                                      |     |

| Runtime Counter                                  | 186 |

| On-Chip Debugger Commands                        | 186 |

| On-Chip Debugger Control Register Definitions    | 191 |

| OCD Control Register                             |     |

| OCD Status Register                              |     |

| Oscillator Control                               | 193 |

| Operation                                        |     |

| System Clock Selection                           |     |

| Clock Failure Detection and Recovery             |     |

| Oscillator Control Register Definitions          |     |

| Crystal Oscillator                               | 198 |

| VALVATOLA JASCALI (III UII                       | 190 |

# Z8 Encore! XP<sup>®</sup> F082A Series Product Specification

| ٦ | u | , | ۰ |  |

|---|---|---|---|--|

| 2 | ı | Ĺ |   |  |

|   |   |   |   |  |

| Operating Modes                                         | 198 |

|---------------------------------------------------------|-----|

| Crystal Oscillator Operation                            | 198 |

| Oscillator Operation with an External RC Network        | 201 |

| Internal Precision Oscillator                           | 203 |

| Operation                                               | 203 |

| eZ8 CPU Instruction Set                                 | 204 |

| Assembly Language Programming Introduction              | 204 |

| Assembly Language Syntax                                | 205 |

| eZ8 CPU Instruction Notation                            | 206 |

| eZ8 CPU Instruction Classes                             | 207 |

| eZ8 CPU Instruction Summary                             | 212 |

| Opcode Maps                                             | 222 |

| Electrical Characteristics                              | 226 |

| Absolute Maximum Ratings                                | 226 |

| DC Characteristics                                      | 227 |

| AC Characteristics                                      | 232 |

| On-Chip Peripheral AC and DC Electrical Characteristics | 233 |

| General Purpose I/O Port Input Data Sample Timing       | 240 |

| General Purpose I/O Port Output Timing                  | 241 |

| On-Chip Debugger Timing                                 | 242 |

| UART Timing                                             | 243 |

| Packaging                                               | 245 |

| Ordering Information                                    | 246 |

| Part Number Suffix Designations                         | 255 |

| Index                                                   | 256 |

| Customer Support                                        | 265 |

|                                                         |     |

| Table 89.  | Flash Options Bits at Program Memory Address 0001H                    | 164 |

|------------|-----------------------------------------------------------------------|-----|

| Table 90.  | Trim Options Bits at Address 0000H                                    | 165 |

| Table 91.  | Trim Option Bits at 0001H                                             | 165 |

| Table 92.  | Trim Option Bits at 0002H (TIPO)                                      | 166 |

| Table 93.  | Trim Option Bits at Address 0003H (TLVD)                              | 166 |

| Table 94.  | LVD Trim Values                                                       | 167 |

| Table 95.  | Trim Option Bits at 0004H                                             | 168 |

| Table 96.  | ADC Calibration Bits                                                  | 169 |

| Table 97.  | ADC Calibration Data Location                                         | 169 |

| Table 98.  | Temperature Sensor Calibration High Byte at 003A (TSCALH)             | 171 |

| Table 99.  | Temperature Sensor Calibration Low Byte at 003B (TSCALL)              | 171 |

| Table 100. | Watchdog Calibration High Byte at 007EH (WDTCALH)                     | 172 |

| Table 101. | Serial Number at 001C - 001F (S_NUM)                                  | 173 |

| Table 102. | Serialization Data Locations                                          | 173 |

| Table 103. | Watchdog Calibration Low Byte at 007FH (WDTCALL)                      | 173 |

| Table 104. | Lot Identification Number (RAND_LOT)                                  | 174 |

| Table 105. | Randomized Lot ID Locations                                           | 174 |

| Table 106. | Write Status Byte                                                     | 177 |

| Table 107. | NVDS Read Time                                                        | 179 |

| Table 108. | OCD Baud-Rate Limits                                                  | 184 |

| Table 109. | Debug Command Enable/Disable                                          | 186 |

| Table 110. | OCD Control Register (OCDCTL)                                         | 191 |

| Table 111. | OCD Status Register (OCDSTAT)                                         | 192 |

| Table 112. | Oscillator Configuration and Selection                                | 194 |

| Table 113. | Oscillator Control Register (OSCCTL)                                  | 196 |

| Table 114. | Recommended Crystal Oscillator Specifications                         | 200 |

| Table 115. | Transconductance Values for Low, Medium and High Gain Operating Modes | 200 |

| Table 116. | Assembly Language Syntax Example 1                                    | 205 |

| Table 117. | Assembly Language Syntax Example 2                                    | 205 |

| Table 118. | Notational Shorthand                                                  | 206 |

Table 3. Pin Characteristics (20- and 28-pin Devices)

| Symbol<br>Mnemonic | Direction | Reset<br>Direction            | Active<br>Low<br>or<br>Active<br>High | Tristate<br>Output   | Internal<br>Pull-up or<br>Pull-down                  | Schmitt-<br>Trigger<br>Input | Open Drain<br>Output                                 | 5 V<br>Tolerance                          |

|--------------------|-----------|-------------------------------|---------------------------------------|----------------------|------------------------------------------------------|------------------------------|------------------------------------------------------|-------------------------------------------|

| AVDD               | N/A       | N/A                           | N/A                                   | N/A                  | N/A                                                  | N/A                          | N/A                                                  | N/A                                       |

| AVSS               | N/A       | N/A                           | N/A                                   | N/A                  | N/A                                                  | N/A                          | N/A                                                  | NA                                        |

| DBG                | I/O       | I                             | N/A                                   | Yes                  | Yes                                                  | Yes                          | Yes                                                  | No                                        |

| PA[7:0]            | I/O       | I                             | N/A                                   | Yes                  | Programma-<br>ble<br>Pull-up                         | Yes                          | Yes,<br>Programma-<br>ble                            | PA[7:2]<br>unless pul-<br>lups<br>enabled |

| PB[7:0]            | I/O       | I                             | N/A                                   | Yes                  | Programma-<br>ble<br>Pull-up                         | Yes                          | Yes,<br>Programma-<br>ble                            | PB[7:6]<br>unless pul-<br>lups<br>enabled |

| PC[7:0]            | I/O       | I                             | N/A                                   | Yes                  | Programma-<br>ble<br>Pull-up                         | Yes                          | Yes,<br>Programma-<br>ble                            | PC[7:3]<br>unless pul-<br>lups<br>enabled |

| RESET/<br>PD0      | I/O       | I/O<br>(defaults to<br>RESET) | Low (in<br>Reset<br>mode)             | Yes<br>(PD0<br>only) | Programma-<br>ble for PD0;<br>always on for<br>RESET | Yes                          | Programma-<br>ble for PD0;<br>always on for<br>RESET | Yes,<br>unless pul-<br>lups<br>enabled    |

| VDD                | N/A       | N/A                           | N/A                                   | N/A                  |                                                      |                              | N/A                                                  | N/A                                       |

| VSS                | N/A       | N/A                           | N/A                                   | N/A                  |                                                      |                              | N/A                                                  | N/A                                       |

**Note:** PB6 and PB7 are available only in those devices without ADC.

Table 8. Reset and Stop Mode Recovery Characteristics and Latency

|                                                       | Reset Characteristics and Latency                      |            |                                                               |  |  |  |

|-------------------------------------------------------|--------------------------------------------------------|------------|---------------------------------------------------------------|--|--|--|

| Reset Type                                            | Control Registers                                      | eZ8<br>CPU | Reset Latency (Delay)                                         |  |  |  |

| System Reset                                          | Reset (as applicable)                                  | Reset      | 66 Internal Precision Oscillator Cycles                       |  |  |  |

| System Reset with Crystal Oscillator Enabled          | Reset (as applicable)                                  | Reset      | 5000 Internal Precision Oscillator Cycles                     |  |  |  |

| Stop Mode Recovery                                    | Unaffected, except<br>WDT_CTL and<br>OSC_CTL registers | Reset      | 66 Internal Precision Oscillator Cycles<br>+ IPO startup time |  |  |  |

| Stop Mode Recovery with<br>Crystal Oscillator Enabled | Unaffected, except WDT_CTL and OSC_CTL registers       | Reset      | 5000 Internal Precision Oscillator Cycles                     |  |  |  |

During a System Reset or Stop Mode Recovery, the Internal Precision Oscillator requires 4 µs to start up. Then the Z8 Encore! XP F082A Series device is held in Reset for 66 cycles of the Internal Precision Oscillator. If the crystal oscillator is enabled in the Flash option bits, this reset period is increased to 5000 IPO cycles. When a reset occurs because of a low voltage condition or Power-On Reset (POR), this delay is measured from the time that the supply voltage first exceeds the POR level. If the external pin reset remains asserted at the end of the reset period, the device remains in reset until the pin is deas-serted.

At the beginning of Reset, all GPIO pins are configured as inputs with pull-up resistor disabled, except PD0 (or PA2 on 8-pin devices) which is shared with the reset pin. On reset, the PD0 is configured as a bidirectional open-drain reset. The pin is internally driven low during port reset, after which the user code may reconfigure this pin as a general purpose output.

During Reset, the eZ8 CPU and on-chip peripherals are idle; however, the on-chip crystal oscillator and Watchdog Timer oscillator continue to run.

Upon Reset, control registers within the Register File that have a defined Reset value are loaded with their reset values. Other control registers (including the Stack Pointer, Register Pointer and Flags) and general-purpose RAM are undefined following Reset. The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset vector address.

As the control registers are reinitialized by a system reset, the system clock after reset is always the IPO. The software must reconfigure the oscillator control block, such that the correct system clock source is enabled and selected.

## **Shared Debug Pin**

On the 8-pin version of this device only, the Debug pin shares function with the PA0 GPIO pin. This pin performs as a general purpose input pin on power-up, but the debug logic monitors this pin during the reset sequence to determine if the unlock sequence occurs. If the unlock sequence is present, the debug function is unlocked and the pin no longer functions as a GPIO pin. If it is not present, the debug feature is disabled until/unless another reset event occurs. For more details, see the On-Chip Debugger chapter on page 180.

# **Crystal Oscillator Override**

For systems using a crystal oscillator, PA0 and PA1 are used to connect the crystal. When the crystal oscillator is enabled, the GPIO settings are overridden and PA0 and PA1 are disabled. See the Oscillator Control Register Definitions section on page 196 for details.

### **5V Tolerance**

All six I/O pins on the 8-pin devices are 5V-tolerant, unless the programmable pull-ups are enabled. If the pull-ups are enabled and inputs higher than  $V_{DD}$  are applied to these parts, excessive current flows through those pull-up devices and can damage the chip.

Note:

In the 20- and 28-pin versions of this device, any pin which shares functionality with an ADC, crystal or comparator port is not 5 V-tolerant, including PA[1:0], PB[5:0] and PC[2:0]. All other signal pins are 5 V-tolerant and can safely handle inputs higher than  $V_{DD}$  except when the programmable pull-ups are enabled.

## **External Clock Setup**

For systems using an external TTL drive, PB3 is the clock source for 20- and 28-pin devices. In this case, configure PB3 for alternate function CLKIN. Write the Oscillator Control (OSCCTL) Register such that the external oscillator is selected as the system clock. See the Oscillator Control Register Definitions section on page 196 for details. For 8-pin devices, use PA1 instead of PB3.

**Table 15. Port Alternate Function Mapping (Non 8-Pin Parts)**

| Port                  | Pin | Mnemonic   | Alternate Function Description          | Alternate Function<br>Set Register AFS1 |

|-----------------------|-----|------------|-----------------------------------------|-----------------------------------------|

| Port A <sup>1,2</sup> | PA0 | T0IN/T0OUT | Timer 0 Input/Timer 0 Output Complement | N/A                                     |

|                       |     | Reserved   |                                         | -                                       |

|                       | PA1 | T0OUT      | Timer 0 Output                          | -                                       |

|                       |     | Reserved   |                                         | -                                       |

|                       | PA2 | DE0        | UART 0 Driver Enable                    | -                                       |

|                       |     | Reserved   |                                         | -                                       |

|                       | PA3 | CTS0       | UART 0 Clear to Send                    | -                                       |

|                       |     | Reserved   |                                         |                                         |

|                       | PA4 | RXD0/IRRX0 | UART 0/IrDA 0 Receive Data              | -                                       |

|                       |     | Reserved   |                                         | -                                       |

|                       | PA5 | TXD0/IRTX0 | UART 0/IrDA 0 Transmit Data             | -                                       |

|                       |     | Reserved   |                                         | -                                       |

|                       | PA6 | T1IN/T1OUT | Timer 1 Input/Timer 1 Output Complement | -                                       |

|                       |     | Reserved   |                                         | -                                       |

|                       | PA7 | T1OUT      | Timer 1 Output                          | -                                       |

|                       |     | Reserved   |                                         | -                                       |

#### Notes:

- 1. Because there is only a single alternate function for each Port A pin, the Alternate Function Set registers are not implemented for Port A. Enabling alternate function selections automatically enables the associated alternate function. See the <a href="Port A-D Alternate Function Subregisters">Port A-D Alternate Function Subregisters</a> (PxAF) section on page 47 for details.

- 2. Whether PA0/PA6 takes on the timer input or timer output complement function depends on the timer configuration. See the <u>Timer Pin Signal Operation</u> section on page 84 for details.

- 3. Because there are at most two choices of alternate function for any pin of Port B, the Alternate Function Set Register AFS2 is not used to select the function. Alternate function selection must also be enabled. See the <a href="Port-A-D Alternate Function Subregisters">Port-A-D Alternate Function Subregisters</a> (PxAF) section on page 47 for details.

- 4.  $V_{REF}$  is available on PB5 in 28-pin products and on PC2 in 20-pin parts.

- 5. Because there are at most two choices of alternate function for any pin of Port C, the Alternate Function Set Register AFS2 is not used to select the function. Alternate function selection must also be enabled. See the Port A–D Alternate Function Subregisters (PxAF) section on page 47 for details.

- 6. Because there is only a single alternate function for the Port PD0 pin, the Alternate Function Set registers are not implemented for Port D. Enabling alternate function selections automatically enables the associated alternate function. See the Port A–D Alternate Function Subregisters (PxAF) section on page 47 for details.

If TPOL is set to 0, the ratio of the PWM output High time to the total period is represented by:

PWM Output High Time Ratio (%) =

$$\frac{\text{Reload Value} - \text{PWM Value}}{\text{Reload Value}} \times 100$$

If TPOL is set to 1, the ratio of the PWM output High time to the total period is represented by:

PWM Output High Time Ratio (%) =

$$\frac{PWM \ Value}{Reload \ Value} \times 100$$

#### **CAPTURE Mode**

In CAPTURE Mode, the current timer count value is recorded when the appropriate external Timer Input transition occurs. The Capture count value is written to the Timer PWM High and Low Byte registers. The timer input is the system clock. The TPOL bit in the Timer Control Register determines if the Capture occurs on a rising edge or a falling edge of the Timer Input signal. When the Capture event occurs, an interrupt is generated and the timer continues counting. The INPCAP bit in TxCTL0 Register is set to indicate the timer interrupt is because of an input capture event.

The timer continues counting up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt and continues counting. The INPCAP bit in TxCTL0 Register clears indicating the timer interrupt is not because of an input capture event.

Observe the following steps for configuring a timer for CAPTURE Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE Mode

- Set the prescale value

- Set the Capture edge (rising or falling) for the Timer Input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. Clear the Timer PWM High and Low Byte registers to 0000H. Clearing these registers allows the software to determine if interrupts were generated by either a capture event or a reload. If the PWM High and Low Byte registers still contain 0000H after the interrupt, the interrupt was generated by a Reload.

| Bit               | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [6:5]<br>TICONFIG | Timer Interrupt Configuration This field configures timer interrupt definition.  0x = Timer Interrupt occurs on all defined Reload, Compare and Input Events.  10 = Timer Interrupt only on defined Input Capture/Deassertion Events.  11 = Timer Interrupt only on defined Reload/Compare Events.                                                                                     |

| [4]               | Reserved This bit is reserved and must be programmed to 0.                                                                                                                                                                                                                                                                                                                             |

| [3:1]<br>PWMD     | PWM Delay Value This field is a programmable delay to control the number of system clock cycles delay before the Timer Output and the Timer Output Complement are forced to their active state.  000 = No delay.  001 = 2 cycles delay.  010 = 4 cycles delay.  011 = 8 cycles delay.  100 = 16 cycles delay.  101 = 32 cycles delay.  110 = 64 cycles delay.  111 = 128 cycles delay. |

| [0]<br>INPCAP     | Input Capture Event This bit indicates if the most recent timer interrupt is caused by a Timer Input Capture Event.  0 = Previous timer interrupt is not a result of Timer Input Capture Event.  1 = Previous timer interrupt is a result of Timer Input Capture Event.                                                                                                                |

### Timer 0-1 Control Register 1

The Timer 0–1 Control (TxCTL1) registers, shown in Table 51, enable and disable the timers, set the prescaler value and determine the timer operating mode.

Table 51. Timer 0-1 Control Register 1 (TxCTL1)

| Bit     | 7   | 6          | 5          | 4   | 3   | 2   | 1   | 0   |

|---------|-----|------------|------------|-----|-----|-----|-----|-----|

| Field   | TEN | TPOL       | PRES TMODE |     |     |     |     |     |

| RESET   | 0   | 0          | 0          | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W | R/W        | R/W        | R/W | R/W | R/W | R/W | R/W |

| Address |     | F07H, F0FH |            |     |     |     |     |     |

| Bit | Description                 |

|-----|-----------------------------|

| [7] | Timer Enable                |

| TEN | 0 = Timer is disabled.      |

|     | 1 = Timer enabled to count. |

Table 75. ADC Data High Byte Register (ADCD\_H)

| Bit       | 7              | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------|----------------|---|---|---|---|---|---|---|

| Field     | ADCDH          |   |   |   |   |   |   |   |

| RESET     | Χ              | Х | Х | Х | Χ | Х | Х | Х |

| R/W       | R              | R | R | R | R | R | R | R |

| Address   | s F72H         |   |   |   |   |   |   |   |

| X = Undef | X = Undefined. |   |   |   |   |   |   |   |

| Bit   | Description                                                                                       |

|-------|---------------------------------------------------------------------------------------------------|

| [7:0] | ADC Data High Byte                                                                                |

| ADCDH | This byte contains the upper eight bits of the ADC output. These bits are not valid during a sin- |

|       | gle-shot conversion. During a continuous conversion, the most recent conversion output is         |

|       | held in this register. These bits are undefined after a Reset.                                    |

### **ADC Data Low Byte Register**

The ADC Data Low Byte (ADCD\_L) Register contains the lower bits of the ADC output plus an overflow status bit. The output is a 13-bit two's complement value. During a single-shot conversion, this value is invalid. Access to the ADC Data Low Byte Register is read-only. Reading the ADC Data High Byte Register latches data in the ADC Low Bits Register.

Table 76. ADC Data Low Byte Register (ADCD\_L)

| Bit       | 7              | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-----------|----------------|---|---|---|---|---|---|---|--|--|--|

| Field     | ADCDL Reserved |   |   |   |   |   |   |   |  |  |  |

| RESET     | Х              | Х | Х | Х | Х | Х | Х | Х |  |  |  |

| R/W       | R              | R | R | R | R | R | R | R |  |  |  |

| Address   | F73H           |   |   |   |   |   |   |   |  |  |  |

| X = Undef | X = Undefined. |   |   |   |   |   |   |   |  |  |  |

| Bit            | Description                                                                                                                                 |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| [7:3]<br>ADCDL | ADC Data Low Bits  These bits are the least significant five bits of the 13-bits of the ADC output. These bits are undefined after a Reset. |

The following code example illustrates how to safely enable the comparator:

```

di

ld cmp0, r0 ; load some new configuration

nop

nop ; wait for output to settle

clr irq0 ; clear any spurious interrupts pending

ei

```

# **Comparator Control Register Definition**

The Comparator Control Register (CMP0) configures the comparator inputs and sets the value of the internal voltage reference.

Table 77. Comparator Control Register (CMP0)

| Bit     | 7      | 6      | 5    | 4   | 3                                       | 2   | 1 | 0 |  |  |  |  |

|---------|--------|--------|------|-----|-----------------------------------------|-----|---|---|--|--|--|--|

| Field   | INPSEL | INNSEL |      | REF | Reserved (20-/28-pin)<br>REFLVL (8-pin) |     |   |   |  |  |  |  |

| RESET   | 0      | 0      | 0    | 1   | 0                                       | 1   | 0 | 0 |  |  |  |  |

| R/W     | R/W    | R/W    | R/W  | R/W | R/W                                     | R/W |   |   |  |  |  |  |

| Address |        |        | F90H |     |                                         |     |   |   |  |  |  |  |

| Bit           | Description                                                                                                                                                                  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>INPSEL | Signal Select for Positive Input 0 = GPIO pin used as positive comparator input. 1 = Temperature sensor used as positive comparator input.                                   |

| [6]<br>INNSEL | Signal Select for Negative Input  0 = Internal reference disabled, GPIO pin used as negative comparator input.  1 = Internal reference enabled as negative comparator input. |

### **Byte Write**

To write a byte to the NVDS array, the user code must first push the address, then the data byte onto the stack. The user code issues a CALL instruction to the address of the byte-write routine (0x10B3). At the return from the sub-routine, the write status byte resides in working register R0. The bit fields of this status byte are defined in Table 106. The contents of the status byte are undefined for write operations to illegal addresses. Also, user code must pop the address and data bytes off the stack.

The write routine uses 13 bytes of stack space in addition to the two bytes of address and data pushed by the user. Sufficient memory must be available for this stack usage.

Because of the Flash memory architecture, NVDS writes exhibit a nonuniform execution time. In general, a write takes  $251\,\mu s$  (assuming a 20MHz system clock). Every 400 to 500 writes, however, a maintenance operation is necessary. In this rare occurrence, the write takes up to 61 ms to complete. Slower system clock speeds result in proportionally higher execution times.

NVDS byte writes to invalid addresses (those exceeding the NVDS array size) have no effect. Illegal write operations have a  $2\mu s$  execution time.

Table 106. Write Status Byte

| Bit              | 7 | 6    | 5     | 4 | 3    | 2  | 1   | 0   |

|------------------|---|------|-------|---|------|----|-----|-----|

| Field            |   | Rese | erved |   | RCPY | PF | AWE | DWE |

| Default<br>Value | 0 | 0    | 0     | 0 | 0    | 0  | 0   | 0   |

| Bit         | Description                                                                                                                            |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------|

| [7:4]       | Reserved These bits are reserved and must be programmed to 0000.                                                                       |

| [3]<br>RCPY | Recopy Subroutine Executed A recopy subroutine was executed. These operations take significantly longer than a normal write operation. |

| [2]<br>PF   | Power Failure Indicator A power failure or system reset occurred during the most recent attempted write to the NVDS array.             |

| [1]<br>AWE  | Address Write Error An address byte failure occurred during the most recent attempted write to the NVDS array.                         |

| [0]<br>DWE  | Data Write Error A data byte failure occurred during the most recent attempted write to the NVDS array.                                |

| Bit             | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [3]<br>WDFEN    | Watchdog Timer Oscillator Failure Detection Enable  1 = Failure detection of Watchdog Timer oscillator is enabled.  0 = Failure detection of Watchdog Timer oscillator is disabled.                                                                                                                                                                                                                                                       |

| [2:0]<br>SCKSEL | System Clock Oscillator Select  000 = Internal precision oscillator functions as system clock at 5.53MHz.  001 = Internal precision oscillator functions as system clock at 32kHz.  010 = Crystal oscillator or external RC oscillator functions as system clock.  011 = Watchdog Timer oscillator functions as system.  100 = External clock signal on PB3 functions as system clock.  101 = Reserved.  110 = Reserved.  111 = Reserved. |

Table 128. eZ8 CPU Instruction Summary (Continued)

| Assembly      |                      |     | ress<br>de | _ Opcode(s) |   |       | Fla | ags |   |   | Fetch<br>Cycle | Instr.<br>Cycle |

|---------------|----------------------|-----|------------|-------------|---|-------|-----|-----|---|---|----------------|-----------------|

| Mnemonic      | Symbolic Operation   | dst |            |             |   | ZSVDH |     |     |   |   | S              | S               |

| CALL dst      | SP ← SP -2           | IRR |            | D4          | - | -     | -   | -   | - | - | 2              | 6               |

|               | @SP ← PC<br>PC ← dst | DA  |            | D6          |   |       |     |     |   |   | 3              | 3               |

| CCF           | C ← ~C               |     |            | EF          | * | -     | -   | -   | - |   | 1              | 2               |

| CLR dst       | dst ← 00H            | R   |            | В0          | - | -     | -   | -   | - | - | 2              | 2               |

|               |                      | IR  |            | B1          | - |       |     |     |   |   | 2              | 3               |

| COM dst       | dst ← ~dst           | R   |            | 60          | - | *     | *   | 0   | - | _ | 2              | 2               |

|               |                      | IR  |            | 61          | - |       |     |     |   |   | 2              | 3               |

| CP dst, src   | dst - src            | r   | r          | A2          | * | *     | *   | *   | _ | - | 2              | 3               |

|               |                      | r   | lr         | А3          |   |       |     |     |   |   | 2              | 4               |

|               |                      | R   | R          | A4          |   |       |     |     |   |   | 3              | 3               |

|               |                      | R   | IR         | A5          | - |       |     |     |   |   | 3              | 4               |

|               |                      | R   | IM         | A6          |   |       |     |     |   |   | 3              | 3               |

|               |                      | IR  | IM         | A7          |   |       |     |     |   |   | 3              | 4               |

| CPC dst, src  | dst - src - C        | r   | r          | 1F A2       | * | *     | *   | *   | _ | _ | 3              | 3               |

|               |                      | r   | lr         | 1F A3       | - |       |     |     |   |   | 3              | 4               |

|               |                      | R   | R          | 1F A4       | - |       |     |     |   |   | 4              | 3               |

|               |                      | R   | IR         | 1F A5       | - |       |     |     |   |   | 4              | 4               |

|               |                      | R   | IM         | 1F A6       | - |       |     |     |   |   | 4              | 3               |

|               |                      | IR  | IM         | 1F A7       | - |       |     |     |   |   | 4              | 4               |

| CPCX dst, src | dst - src - C        | ER  | ER         | 1F A8       | * | *     | *   | *   | _ | - | 5              | 3               |

|               |                      | ER  | IM         | 1F A9       | - |       |     |     |   |   | 5              | 3               |

| CPX dst, src  | dst - src            | ER  | ER         | A8          | * | *     | *   | *   | _ | _ | 4              | 3               |

|               |                      | ER  | IM         | A9          |   |       |     |     |   |   | 4              | 3               |

Note: Flags Notation:

<sup>\* =</sup> Value is a function of the result of the operation.

<sup>-</sup> = Unaffected.

X = Undefined.

<sup>0 =</sup> Reset to 0.

<sup>1 =</sup> Set to 1.

Table 128. eZ8 CPU Instruction Summary (Continued)

| Assembly      |                                     |     | ress<br>ode | _ Opcode(s) |   |   | Fla | ags |   |   | Fetch<br>Cycle | Instr.<br>Cycle |

|---------------|-------------------------------------|-----|-------------|-------------|---|---|-----|-----|---|---|----------------|-----------------|

| Mnemonic      | Symbolic Operation                  | dst | src         | (Hex)       | С | Z | S   | ٧   | D | Н | S              | S               |

| SUB dst, src  | dst ← dst – src                     | r   | r           | 22          | * | * | *   | *   | 1 | * | 2              | 3               |

|               |                                     | r   | lr          | 23          | - |   |     |     |   |   | 2              | 4               |

|               |                                     | R   | R           | 24          | - |   |     |     |   |   | 3              | 3               |

|               |                                     | R   | IR          | 25          | - |   |     |     |   |   | 3              | 4               |

|               |                                     | R   | IM          | 26          | - |   |     |     |   |   | 3              | 3               |

|               |                                     | IR  | IM          | 27          | - |   |     |     |   |   | 3              | 4               |

| SUBX dst, src | dst ← dst – src                     | ER  | ER          | 28          | * | * | *   | *   | 1 | * | 4              | 3               |

|               |                                     | ER  | IM          | 29          | - |   |     |     |   |   | 4              | 3               |

| SWAP dst      | $dst[7:4] \leftrightarrow dst[3:0]$ | R   |             | F0          | Χ | * | *   | Χ   | - | - | 2              | 2               |

|               |                                     | IR  |             | F1          | - |   |     |     |   |   | 2              | 3               |

| TCM dst, src  | (NOT dst) AND src                   | r   | r           | 62          | - | * | *   | 0   | - | - | 2              | 3               |

|               |                                     | r   | lr          | 63          | - |   |     |     |   |   | 2              | 4               |

|               |                                     | R   | R           | 64          | - |   |     |     |   |   | 3              | 3               |

|               |                                     | R   | IR          | 65          | - |   |     |     |   |   | 3              | 4               |

|               |                                     | R   | IM          | 66          | - |   |     |     |   |   | 3              | 3               |

|               |                                     | IR  | IM          | 67          | - |   |     |     |   |   | 3              | 4               |

| TCMX dst, src | (NOT dst) AND src                   | ER  | ER          | 68          | _ | * | *   | 0   | - | _ | 4              | 3               |

|               |                                     | ER  | IM          | 69          | - |   |     |     |   |   | 4              | 3               |

| TM dst, src   | dst AND src                         | r   | r           | 72          | _ | * | *   | 0   | - | _ | 2              | 3               |

|               |                                     | r   | lr          | 73          | - |   |     |     |   |   | 2              | 4               |

|               |                                     | R   | R           | 74          | - |   |     |     |   |   | 3              | 3               |

|               |                                     | R   | IR          | 75          | - |   |     |     |   |   | 3              | 4               |

|               |                                     | R   | IM          | 76          | - |   |     |     |   |   | 3              | 3               |

|               |                                     | IR  | IM          | 77          | - |   |     |     |   |   | 3              | 4               |

Note: Flags Notation:

<sup>\* =</sup> Value is a function of the result of the operation.

<sup>-</sup> = Unaffected.

X = Undefined.

<sup>0 =</sup> Reset to 0.

<sup>1 =</sup> Set to 1.

**Table 132. Power Consumption**

|                         |                                                    | V <sub>DE</sub> | = 2.7 V to 3 | 3.6 V                            |       |                                                                   |

|-------------------------|----------------------------------------------------|-----------------|--------------|----------------------------------|-------|-------------------------------------------------------------------|

| Symbol                  | Parameter                                          |                 |              | Maximum<br>Ext Temp <sup>3</sup> | Units | Conditions                                                        |

| I <sub>DD</sub><br>Stop | Supply Current in STOP Mode                        | 0.1             |              |                                  | μA    | No peripherals enabled. All pins driven to $V_{DD}$ or $V_{SS}$ . |

| I <sub>DD</sub> Halt    | Supply Current in                                  | 35              | 55           | 65                               | μΑ    | 32kHz.                                                            |

|                         | HALT Mode (with all peripherals dis-               | 520             |              |                                  | μΑ    | 5.5MHz.                                                           |

|                         | abled)                                             | 2.1             | 2.85         | 2.85                             | mA    | 20MHz.                                                            |

| I <sub>DD</sub>         | Supply Current in                                  | 2.8             |              |                                  | mA    | 32kHz.                                                            |

|                         | ACTIVE Mode                                        | 4.5             | 5.2          | 5.2                              | mA    | 5.5MHz.                                                           |

|                         | (with all peripherals disabled)                    | 5.5             | 6.5          | 6.5                              | mΑ    | 10MHz.                                                            |

|                         | _                                                  | 7.9             | 11.5         | 11.5                             | mA    | 20MHz.                                                            |

| I <sub>DD</sub><br>WDT  | Watchdog Timer<br>Supply Current                   | 0.9             | 1.0          | 1.1                              | μΑ    |                                                                   |

| I <sub>DD</sub>         | Crystal Oscillator                                 | 40              |              |                                  | μΑ    | 32kHz.                                                            |

| XTAL                    | Supply Current                                     | 230             |              |                                  | μA    | 4MHz.                                                             |

|                         | -                                                  | 760             |              |                                  | μΑ    | 20MHz.                                                            |

| I <sub>DD</sub> IPO     | Internal Precision<br>Oscillator Supply<br>Current | 350             | 500          | 550                              | μA    |                                                                   |

| I <sub>DD</sub><br>VBO  | Voltage Brown-Out and Low-Voltage                  | 50              |              |                                  | μA    | For 20-/28-pin devices (VBO only); See Note 4.                    |

|                         | Detect Supply Current                              |                 |              |                                  |       | For 8-pin devices; See Note 4.                                    |

| I <sub>DD</sub>         | Analog to Digital                                  | 2.8             | 3.1          | 3.2                              | mA    | 32kHz.                                                            |

| ADC                     | Converter Supply                                   | 3.1             | 3.6          | 3.7                              | mA    | 5.5MHz.                                                           |

|                         | Current (with<br>External Refer-                   | 3.3             | 3.7          | 3.8                              | mA    | 10MHz.                                                            |

|                         | ence)                                              | 3.7             | 4.2          | 4.3                              | mA    | 20MHz.                                                            |

#### Notes:

- 1. Typical conditions are defined as  $V_{DD}$  = 3.3V and +30°C.

- 2. Standard temperature is defined as  $T_A = 0$ °C to +70°C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

- 3. Extended temperature is defined as  $T_A = -40$ °C to +105°C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

- 4. For this block to operate, the bandgap circuit is automatically turned on and must be added to the total supply current. This bandgap current is only added once, regardless of how many peripherals are using it.

Table 139. Analog-to-Digital Converter Electrical Characteristics and Timing

$V_{DD} = 3.0 \text{ V to } 3.6 \text{ V}$   $T_A = 0^{\circ}\text{C to } +70^{\circ}\text{C}$ (unless otherwise stated)

| Symbol                   | Parameter                                                 | Minimum    | Typical      | Maximum    | Units                          | Conditions                                                                          |

|--------------------------|-----------------------------------------------------------|------------|--------------|------------|--------------------------------|-------------------------------------------------------------------------------------|

|                          | Resolution                                                | 10         |              | _          | bits                           |                                                                                     |

|                          | Differential Nonlinearity (DNL)                           | -1.0       | -            | 1.0        | LSB <sup>3</sup>               | External $V_{REF}$ = 2.0 V;<br>$R_S \leftarrow 3.0 \text{ k}\Omega$                 |

|                          | Integral Nonlinearity (INL)                               | -3.0       | -            | 3.0        | LSB <sup>3</sup>               | External $V_{REF}$ = 2.0 V;<br>$R_S \leftarrow 3.0 \text{ k}\Omega$                 |

|                          | Offset Error with Calibration                             |            | <u>+</u> 1   |            | LSB <sup>3</sup>               |                                                                                     |

|                          | Absolute Accuracy with Calibration                        |            | <u>+</u> 3   |            | LSB <sup>3</sup>               |                                                                                     |

| V <sub>REF</sub>         | Internal Reference Voltage                                | 1.0<br>2.0 | 1.1<br>2.2   | 1.2<br>2.4 | V                              | REFSEL=01<br>REFSEL=10                                                              |

| V <sub>REF</sub>         | Internal Reference Variation with Temperature             |            | <u>+</u> 1.0 |            | %                              | Temperature variation with V <sub>DD</sub> = 3.0                                    |

| V <sub>REF</sub>         | Internal Reference Voltage Variation with V <sub>DD</sub> |            | <u>+</u> 0.5 |            | %                              | Supply voltage variation with T <sub>A</sub> = 30°C                                 |

| R <sub>RE-</sub><br>FOUT | Reference Buffer Output Impedance                         |            | 850          |            | W                              | When the internal reference is buffered and driven out to the VREF pin (REFOUT = 1) |

|                          | Single-Shot Conversion<br>Time                            | -          | 5129         | -          | Sys-<br>tem<br>clock<br>cycles | All measurements but temperature sensor                                             |

|                          |                                                           |            | 10258        |            |                                | Temperature sensor measurement                                                      |

#### Notes:

- 1. Analog source impedance affects the ADC offset voltage (because of pin leakage) and input settling time.

- 2. Devices are factory calibrated at  $V_{DD} = 3.3 \,\text{V}$  and  $T_A = +30 \,^{\circ}\text{C}$ , so the ADC is maximally accurate under these conditions.

- 3. LSBs are defined assuming 10-bit resolution.

- 4. This is the maximum recommended resistance seen by the ADC input pin.

- 5. The input impedance is inversely proportional to the system clock frequency.

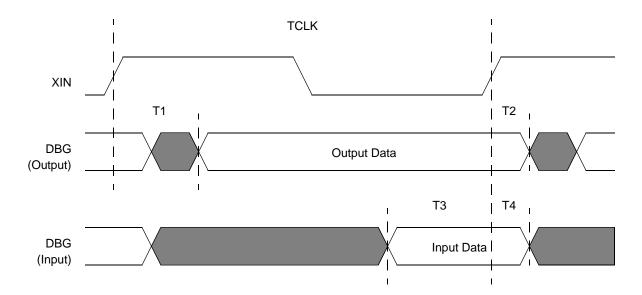

## **On-Chip Debugger Timing**

Figure 36 and Table 145 provide timing information for the DBG pin. The DBG pin timing specifications assume a 4 ns maximum rise and fall time.

Figure 36. On-Chip Debugger Timing

Table 145. On-Chip Debugger Timing

|                |                                              | Delay (ns) |         |

|----------------|----------------------------------------------|------------|---------|

| Parameter      | Abbreviation                                 | Minimum    | Maximum |

| DBG            |                                              |            |         |

| T <sub>1</sub> | X <sub>IN</sub> Rise to DBG Valid Delay      | _          | 15      |

| T <sub>2</sub> | X <sub>IN</sub> Rise to DBG Output Hold Time | 2          | _       |

| T <sub>3</sub> | DBG to XIN Rise Input Setup Time             | 5          | _       |

| T <sub>4</sub> | DBG to XIN Rise Input Hold Time              | 5          | _       |

| G                                            | indirect register pair 206                               |  |

|----------------------------------------------|----------------------------------------------------------|--|

|                                              | indirect register pair 200 indirect working register 206 |  |

| GATED mode 88                                | indirect working register pair 206                       |  |

| general-purpose I/O 36                       | infrared encoder/decoder (IrDA) 120                      |  |

| GPIO 6, 36                                   | Instruction Set 204                                      |  |

| alternate functions 37                       |                                                          |  |

| architecture 37                              | instruction set, eZ8 CPU 204 instructions                |  |

| control register definitions 44              | ADC 208                                                  |  |

| input data sample timing 240                 |                                                          |  |

| interrupts 44                                | ADCX 208                                                 |  |

| port A-C pull-up enable sub-registers 50, 51 | ADD 208                                                  |  |

| port A-H address registers 45                | ADDX 208                                                 |  |

| port A-H alternate function sub-registers 47 | AND 210                                                  |  |

| port A-H control registers 46                | ANDX 210                                                 |  |

| port A-H data direction sub-registers 46     | arithmetic 208                                           |  |

| port A-H high drive enable sub-registers 48  | BCLR 209                                                 |  |

| port A-H input data registers 52             | BIT 209                                                  |  |

| port A-H output control sub-registers 47     | bit manipulation 209                                     |  |

| port A-H output data registers 52, 53        | block transfer 209                                       |  |

| port A-H stop mode recovery sub-registers 49 | BRK 211                                                  |  |

| port availability by device 36               | BSET 209                                                 |  |

| port input timing 240                        | BSWAP 209, 211                                           |  |

| port output timing 241                       | BTJ 211                                                  |  |

|                                              | BTJNZ 211                                                |  |

|                                              | BTJZ 211                                                 |  |

| Н                                            | CALL 211                                                 |  |

| H 207                                        | CCF 209                                                  |  |

| HALT 209                                     | CLR 210                                                  |  |

| halt mode 33, 209                            | COM 210                                                  |  |

| hexadecimal number prefix/suffix 207         | CP 208                                                   |  |

| F                                            | CPC 208                                                  |  |

|                                              | CPCX 208                                                 |  |

| I                                            | CPU control 209                                          |  |

| I2C 6                                        | CPX 208                                                  |  |

| IM 206                                       | DA 208                                                   |  |

| immediate data 206                           | DEC 208                                                  |  |

| immediate operand prefix 207                 | DECW 208                                                 |  |

| INC 208                                      | DI 209                                                   |  |

| increment 208                                | DJNZ 211                                                 |  |

|                                              | EI 209                                                   |  |

| increment word 208                           | HALT 209                                                 |  |

| INCW 208                                     | INC 208                                                  |  |

| indexed 207                                  | INCW 208                                                 |  |

| indirect address prefix 207                  | IRET 211                                                 |  |

| indirect register 206                        | JP 211                                                   |  |

|                                              |                                                          |  |

| LEA 210                                           | b 206                               |

|---------------------------------------------------|-------------------------------------|

| load 210                                          | cc 206                              |

| load constant 209                                 | DA 206                              |

| load constant to/from program memory 210          | ER 206                              |

| load constant with auto-increment addresses 210   | IM 206                              |

| load effective address 210                        | IR 206                              |

| load external data 210                            | Ir 206                              |

| load external data to/from data memory and auto-  | IRR 206                             |

| increment addresses 209                           | Irr 206                             |

| load external to/from data memory and auto-incre- | p 206                               |

| ment addresses 210                                | R 206                               |

|                                                   | r 206                               |

| load using extended addressing 210                | RA 206                              |

| logical AND/aytanded addressing 210               | RR 206                              |

| logical AND/extended addressing 210               |                                     |

| logical exclusive OR 210                          | rr 206                              |

| logical exclusive OR/extended addressing 210      | vector 207                          |

| logical instructions 210                          | X 207                               |

| logical OR 210                                    | notational shorthand 206            |

| logical OR/extended addressing 210                |                                     |

| low power modes 32                                | 0                                   |

|                                                   |                                     |

| M                                                 | OCD                                 |

| •••                                               | architecture 180                    |

| master interrupt enable 57                        | auto-baud detector/generator 183    |

| memory                                            | baud rate limits 184                |

| data 17                                           | block diagram 180                   |

| program 15                                        | breakpoints 185                     |

| mode                                              | commands 186                        |

| CAPTURE 87, 88                                    | control register 191                |

| CAPTURE/COMPARE 88                                | data format 183                     |

| CONTINUOUS 87                                     | DBG pin to RS-232 Interface 181     |

| COUNTER 87                                        | debug mode 182                      |

| GATED 88                                          | debugger break 211                  |

| ONE-SHOT 87                                       | interface 181                       |

| PWM 87, 88                                        | serial errors 184                   |

| modes 87                                          | status register 192                 |

| MULT 208                                          | timing 242                          |

| multiply 208                                      | OCD commands                        |

| multiprocessor mode, UART 105                     | execute instruction (12H) 190       |

|                                                   | read data memory (0DH) 190          |

|                                                   | read OCD control register (05H) 188 |

| N                                                 | read OCD revision (00H) 187         |

| NOP (no operation) 209                            | read OCD status register (02H) 187  |

| notation                                          | read program counter (07H) 188      |

|                                                   |                                     |